# E·XFL

#### NXP USA Inc. - MKE16F512VLL16 Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4F                                                       |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 168MHz                                                                 |

| Connectivity               | CANbus, FlexIO, I <sup>2</sup> C, SPI, UART/USART                      |

| Peripherals                | DMA, LVD, PWM, WDT                                                     |

| Number of I/O              | 89                                                                     |

| Program Memory Size        | 512KB (512K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 68K x 8                                                                |

| RAM Size                   | 64K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 16x12b; D/A 1x12b                                                  |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 100-LQFP                                                               |

| Supplier Device Package    | 100-LQFP (14x14)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mke16f512vll16 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- The timing of the shifter's shift, load and store events are controlled by the highly flexible 16-bit timer assigned to the shifter

- Two or more shifters can be concatenated to support large data transfer sizes

- Each 16-bit timers operates independently, supports for reset, enable and disable on a variety of internal or external trigger conditions with programmable trigger polarity

- Flexible pin configuration supporting output disabled, open drain, bidirectional output data and output mode

- Supports interrupt, DMA or polled transmit/receive operation

## 2.2.16 Port control and GPIO

The Port Control and Interrupt (PORT) module provides support for port control, digital filtering, and external interrupt functions. The GPIO data direction and output data registers control the direction and output data of each pin when the pin is configured for the GPIO function. The GPIO input data register displays the logic value on each pin when the pin is configured for any digital function, provided the corresponding Port Control and Interrupt module for that pin is enabled.

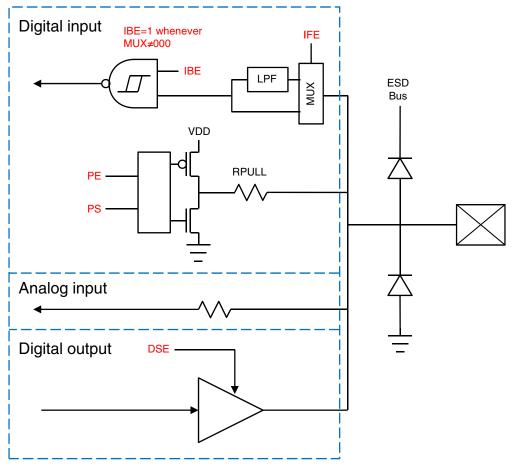

The following figure shows the basic I/O pad structure. Pseudo open-drain pins have the p-channel output driver disabled when configured for open-drain operation. None of the I/O pins, including open-drain and pseudo open-drain pins, are allowed to go above VDD.

## NOTE

The RESET\_b pin is also a normal I/O pad with pseudo opendrain.

Figure 5. I/O simplified block diagram

The PORT module has the following features:

- all PIN support interrupt enable

- Configurable edge (rising, falling, or both) or level sensitive interrupt type

- Support DMA request

- Asynchronous wake-up in low-power modes

- Configurable pullup, pulldown, and pull-disable on select pins

- Configurable high and low drive strength on selected pins

- Configurable passive filter on selected pins

- Individual mux control field supporting analog or pin disabled, GPIO, and up to chip-specific digital functions

- Pad configuration fields are functional in all digital pin muxing modes.

The GPIO module has the following features:

- Port Data Input register visible in all digital pin-multiplexing modes

- Port Data Output register with corresponding set/clear/toggle registers

- Port Data Direction register

- GPIO support single-cycle access via fast GPIO.

Pinouts

## 4.2 Port control and interrupt summary

The following table provides more information regarding the Port Control and Interrupt configurations.

| Feature                           | Port A                                    | Port B         | Port C                                    | Port D                           | Port E         |  |

|-----------------------------------|-------------------------------------------|----------------|-------------------------------------------|----------------------------------|----------------|--|

| Pull select control               | Yes                                       | Yes            | Yes                                       | Yes                              | Yes            |  |

| Pull select at reset              | PTA4/PTA5=Pull<br>up, Others=No           | No             | PTC5=Pull up,<br>Others=No                | PTD3=Pull up,<br>Others=No       | No             |  |

| Pull enable control               | Yes                                       | Yes            | Yes                                       | Yes                              | Yes            |  |

| Pull enable at reset              | PTA4/<br>PTA5=Enabled;<br>Others=Disabled | Disabled       | PTC4/<br>PTC5=Enabled;<br>Others=Disabled | PTD3=Enabled;<br>Others=Disabled | Disabled       |  |

| Passive filter<br>enable control  | PTA5=Yes;<br>Others=No                    | No             | No                                        | PTD3=Yes;<br>Others=No           | No             |  |

| Passive filter<br>enable at reset | PTA5=Enabled;<br>Others=Disabled          | Disabled       | Disabled                                  | Disabled                         | Disabled       |  |

| Open drain enable control         | Disabled                                  | Disabled       | Disabled                                  | Disabled                         | Disabled       |  |

| Open drain enable<br>at reset     | Disabled                                  | Disabled       | Disabled                                  | Disabled                         | Disabled       |  |

| Drive strength<br>enable control  | No                                        | PTB4/PTB5 only | No                                        | PTD0/PTD1/<br>PTD15/PTD16 only   | PTE0/PTE1 only |  |

| Drive strength enable at reset    | Disabled                                  | Disabled       | Disabled                                  | Disabled                         | Disabled       |  |

| Pin mux control                   | Yes                                       | Yes            | Yes                                       | Yes                              | Yes            |  |

| Pin mux at reset                  | PTA4/PTA5/<br>PTA10=ALT7;<br>Others=ALT0  | ALTO           | PTC4/PTC5=ALT7;<br>Others=ALT0            | PTD3=ALT7;<br>Others=ALT0        | ALTO           |  |

| Lock bit                          | Yes                                       | Yes            | Yes                                       | Yes                              | Yes            |  |

| Interrupt and DMA request         | Yes                                       | Yes            | Yes                                       | Yes                              | Yes            |  |

| Digital glitch filter             | Yes                                       | Yes            | Yes                                       | Yes                              | Yes            |  |

Table 6.Ports summary

# 4.3 Module Signal Description Tables

The following sections correlate the chip-level signal name with the signal name used in the module's chapter. They also briefly describe the signal function and direction.

| Chip signal name | Module signal<br>name | Description           | I/O |

|------------------|-----------------------|-----------------------|-----|

| ACMPn_IN[ 6:0]   | IN[ 6:0]              | Analog voltage inputs | I   |

| ACMPn_OUT        | CMPO                  | Comparator output     | 0   |

| Table 16. | ACMPn Signal | Descriptions |

|-----------|--------------|--------------|

|-----------|--------------|--------------|

## 4.3.5 Timer Modules

#### Table 17. LPTMR0 Signal Descriptions

| Chip signal name | Module signal<br>name | Description             | I/O |

|------------------|-----------------------|-------------------------|-----|

| LPTMR0_ALT[3:1]  | LPTMR_ALT <i>n</i>    | Pulse Counter Input pin | Ι   |

#### Table 18. RTC Signal Descriptions

| Chip signal name | Module signal<br>name | Description                             | I/O |

|------------------|-----------------------|-----------------------------------------|-----|

| RTC_CLKOUT       | RTC_CLKOUT            | 1 Hz square-wave output or 32 kHz clock | 0   |

#### Table 19. FTMn Signal Descriptions

| Chip signal name | Module signal name | Description                                                                  | I/O |

|------------------|--------------------|------------------------------------------------------------------------------|-----|

| FTMn_CH[7:0]     | CHn                | FTM channel (n), where n can be 7-0                                          | I/O |

| FTMn_FLT[3:0]    | FAULTj             | Fault input (j), where j can be 3-0                                          | I   |

| TCLK[2:0]        | EXTCLK             | External clock. FTM external clock can be selected to drive the FTM counter. | I   |

## 4.3.6 Communication Interfaces Table 20. CANn Signal Descriptions

| Chip signal name | Module signal<br>name | Description      | I/O |

|------------------|-----------------------|------------------|-----|

| CANn_RX          | CAN Rx                | CAN Receive Pin  | Ι   |

| CANn_TX          | CAN Tx                | CAN Transmit Pin | 0   |

## NOTE

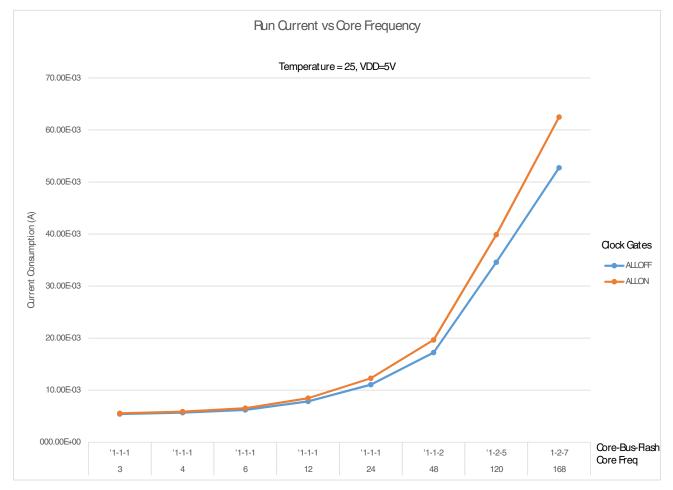

The maximum values stated in the following table represent characterized results equivalent to the mean plus three times the standard deviation (mean + 3 sigma).

| Mode  | Symbol                                                           | Clock<br>Configur<br>ation                                  | Description                                                                  | Temperat<br>ure | Min   | Тур   | Max <sup>1</sup> | Uni<br>ts |

|-------|------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------|-----------------|-------|-------|------------------|-----------|

| HSRUN | I <sub>DD_HSRUN</sub>                                            | PLL                                                         | Running CoreMark in Flash in <b>Compute</b><br><b>Operation</b> mode.        |                 | —     | 44.50 | 46.36            | mA        |

|       |                                                                  | Core@168MHz, bus @84MHz,flash<br>@24MHz VDD=5V              | 105 ℃                                                                        |                 | 51.88 | 59.46 |                  |           |

|       | PLL                                                              | PLL                                                         | 5                                                                            |                 |       | 50.49 | 52.35            | 1         |

|       |                                                                  |                                                             | peripheral clock disabled.<br>Core@168MHz, bus @84MHz,flash<br>@24MHz VDD=5V | 105 ℃           |       | 58.31 | 65.89            | -         |

|       |                                                                  | Running CoreMark in Flash, all                              | 25 °C                                                                        |                 | 60.51 | 62.37 | 1                |           |

|       |                                                                  |                                                             | peripheral clock enabled.                                                    | 105 ℃           |       | 68.62 | 76.20            | 1         |

|       |                                                                  |                                                             | Core@168MHz, bus @84MHz,flash<br>@24MHz VDD=5V                               |                 |       |       |                  |           |

|       | PLL                                                              | Running While(1) loop in Flash, all                         | 25 °C                                                                        | —               | 52.74 | 54.60 | 1                |           |

|       |                                                                  | peripheral clock disabled.<br>Core@168MHz, bus @84MHz,flash | 105 °C − 60.                                                                 | 60.76           | 68.34 |       |                  |           |

|       |                                                                  | @24MHz VDD=5V                                               |                                                                              |                 |       |       |                  |           |

|       | PLL Running While(1) loop in Flash all peripheral clock enabled. | 25 °C                                                       | —                                                                            | 62.48           | 64.34 |       |                  |           |

|       |                                                                  |                                                             | Core @ 168MHz, bus @ 84MHz,flash<br>@ 24MHz VDD=5V                           |                 | _     | 70.75 | 78.33            |           |

|       |                                                                  |                                                             |                                                                              | 05 %0           |       | 00.01 | 00.07            |           |

| RUN   | IDD_RUN                                                          | PLL                                                         | Running CoreMark in Flash in <b>Compute Operation</b> mode.                  | 25 ℃<br>105 ℃   | _     | 29.04 | 29.67            | mA        |

|       |                                                                  |                                                             | Core@120MHz, bus @60MHz,flash<br>@24MHz VDD=5V                               | 105 C           |       | 34.82 | 40.43            |           |

|       |                                                                  | PLL                                                         | Running CoreMark in Flash all                                                | 25 °C           |       | 33.29 | 33.92            | -         |

|       |                                                                  |                                                             | peripheral clock disabled.                                                   | 105 ℃           |       | 39.08 | 44.69            | 1         |

|       |                                                                  |                                                             | Core@120MHz, bus @60MHz,flash<br>@24MHz VDD=5V                               |                 |       |       |                  |           |

|       |                                                                  | PLL                                                         | Running CoreMark in Flash, all                                               | 25 °C           | _     | 41.00 | 41.63            | 1         |

|       |                                                                  |                                                             | peripheral clock enabled.                                                    | 105 °C          | —     | 47.00 | 52.61            | 1         |

|       |                                                                  |                                                             | Core@120MHz, bus @60MHz,flash<br>@24MHz VDD=5V                               |                 |       |       |                  |           |

|       |                                                                  | PLL                                                         | Running While(1) loop in Flash, all                                          | 25 ℃            |       | 34.59 | 35.22            |           |

|       |                                                                  |                                                             | peripheral clock disabled.<br>Core@120MHz, bus @60MHz,flash<br>@24MHz VDD=5V | 105 ℃           |       | 40.68 | 46.29            |           |

Table 32.

Power consumption operating behaviors

- Code execution from flash with cache enabled

- For the ALLOFF curve, all peripheral clocks are disabled except FTFE

Figure 14. Run mode supply current vs. core frequency

- AN2764: Improving the Transient Immunity Performance of Microcontroller-Based Applications

- AN1259: System Design and Layout Techniques for Noise Reduction in MCU-Based Systems

#### 5.3.1.7.1 EMC radiated emissions operating behaviors

EMC measurements to IC-level IEC standards are available from NXP on request.

#### 5.3.1.7.2 Designing with radiated emissions in mind

To find application notes that provide guidance on designing your system to minimize interference from radiated emissions.

- 1. Go to http://www.nxp.com.

- 2. Perform a keyword search for "EMC design".

- 3. Select the "Documents" category and find the application notes.

## 5.3.1.8 Capacitance attributes

#### Table 33. Capacitance attributes

| Symbol            | Description                     | Min. | Max. | Unit |

|-------------------|---------------------------------|------|------|------|

| C <sub>IN_A</sub> | Input capacitance: analog pins  | —    | 7    | pF   |

| C <sub>IN_D</sub> | Input capacitance: digital pins | —    | 7    | pF   |

## NOTE

Please refer to External Oscillator electrical specifications for EXTAL/XTAL pins.

## 5.3.2 Switching specifications

### 5.3.2.1 Device clock specifications

| Symbol              | Description           | Min. | Max. | Unit | Notes |

|---------------------|-----------------------|------|------|------|-------|

| High Speed RUN mode |                       |      |      |      |       |

| f <sub>SYS</sub>    | System and core clock | —    | 168  | MHz  |       |

| f <sub>BUS</sub>    | Bus clock             | _    | 84   | MHz  |       |

#### Table 34. Device clock specifications

#### NOTE:

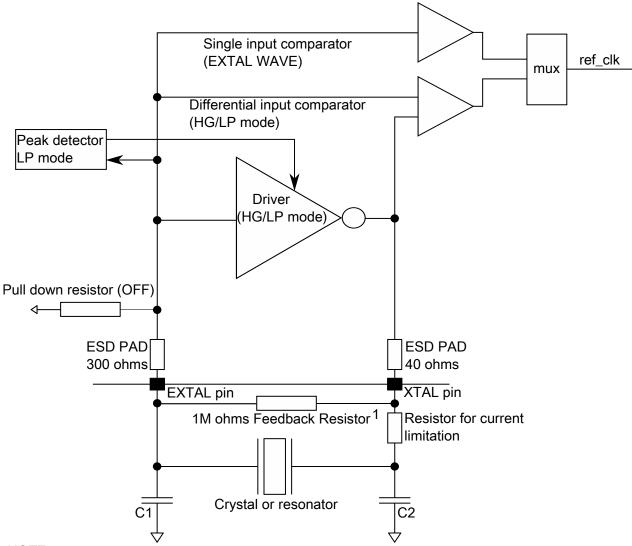

1. 1M Feedback resistor is needed only for HG mode.

#### Figure 18. Oscillator connections scheme (OSC)

#### NOTE

Data values in the following "External Oscillator electrical specifications" tables are from simulation.

#### Table 41. External Oscillator electrical specifications (OSC32)

| Symbol                    | Description                                 | Min. | Тур. | Max. | Unit | Notes |

|---------------------------|---------------------------------------------|------|------|------|------|-------|

| V <sub>DD</sub>           | Supply voltage                              | 2.7  | —    | 5.5  | V    |       |

| I <sub>DDOSC</sub>        | Supply current                              | —    | 25   | —    | μA   | 1     |

| <b>g</b> <sub>mXOSC</sub> | Oscillator transconductance                 | 6    | —    | 9    | μA/V |       |

| V <sub>EXTAL</sub>        | EXTAL32 input voltage — external clock mode | 0    | —    | 3.6  | V    |       |

| Symbol                | Parameter                                                                            | Min.   | Тур. | Max.                                       | Unit |

|-----------------------|--------------------------------------------------------------------------------------|--------|------|--------------------------------------------|------|

|                       | VCO @ 150 MHz ( $F_{pll\_ref} = 12$ MHz, VDIV multiplier<br>= 25, PRDIV divide = 2)  | —      | 2.8  | —                                          | mA   |

|                       | VCO @ 300 MHz ( $F_{pll_{ref}} = 12$ MHz, VDIV multiplier<br>= 50, PRDIV divide = 2) | —      | 3.6  | —                                          | mA   |

| J <sub>cyc_pll</sub>  | PLL Period Jitter (RMS) <sup>2</sup>                                                 |        |      |                                            |      |

|                       | at F <sub>vco</sub> 180 MHz                                                          | —      | 120  | —                                          | ps   |

|                       | at F <sub>vco</sub> 360 MHz                                                          | —      | 75   | —                                          | ps   |

| J <sub>acc_pll</sub>  | PLL accumulated jitter over 1µs (RMS) <sup>2</sup>                                   |        |      |                                            |      |

|                       | at F <sub>vco</sub> 180 MHz                                                          | —      | 1350 | —                                          | ps   |

|                       | at F <sub>vco</sub> 360 MHz                                                          | —      | 600  | —                                          | ps   |

| D <sub>unl</sub>      | Lock exit frequency tolerance                                                        | ± 4.47 | —    | ± 5.97                                     | %    |

| T <sub>pll_lock</sub> | Lock detector detection time <sup>3</sup>                                            | _      | _    | $100 \times 10^{-6} + 1075(1/F_{pll_ref})$ | S    |

# Table 48. PLL electrical specifications<br/>(continued)

1. Excludes any oscillator currents that are also consuming power while PLL is in operation.

2. This specification was obtained using a NXP developed PCB. PLL jitter is dependent on the noise characteristics of each PCB and results will vary

3. This specification applies to any time the PLL VCO divider or reference divider is changed, or changing from PLL disabled (BLPE, BLPI) to PLL enabled (PBE, PEE). If a crystal/resonator is being used as the reference, thisspecification assumes it is already running.

## 5.4.3 Memories and memory interfaces

## 5.4.3.1 Flash memory module (FTFE) electrical specifications

This section describes the electrical characteristics of the flash memory module (FTFE).

### 5.4.3.1.1 Flash timing specifications — program and erase

The following specifications represent the amount of time the internal charge pumps are active and do not include command overhead.

| Symbol                    | Description                                    | Min. | Тур. | Max. | Unit | Notes |

|---------------------------|------------------------------------------------|------|------|------|------|-------|

| t <sub>hvpgm8</sub>       | Program Phrase high-voltage time               | _    | 7.5  | 18   | μs   |       |

| t <sub>hversscr</sub>     | Erase Flash Sector high-voltage time           | _    | 13   | 113  | ms   | 1     |

| t <sub>hversblk64k</sub>  | Erase Flash Block high-voltage time for 64 KB  | _    | 52   | 452  | ms   | 1     |

| t <sub>hversblk512k</sub> | Erase Flash Block high-voltage time for 512 KB | _    | 416  | 3616 | ms   | 1     |

Table 49.

NVM program/erase timing specifications

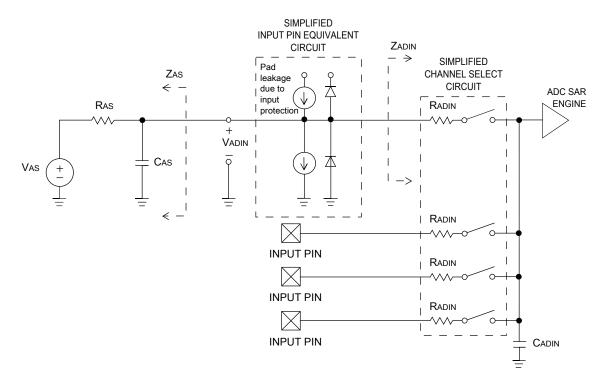

| Symbol            | Description                            | Conditions                                                                                                             | Min. | Typ. <sup>1</sup> | Max. | Unit | Notes |

|-------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------|------|-------------------|------|------|-------|

| R <sub>AS</sub>   | Analog source resistance<br>(external) |                                                                                                                        | _    | _                 | 5    | kΩ   | 4     |

| f <sub>ADCK</sub> | ADC conversion clock<br>frequency      |                                                                                                                        | 2    | 40                | 50   | MHz  | 5, 6  |

| C <sub>rate</sub> | ADC conversion rate                    | No ADC<br>hardware<br>averaging <sup>7</sup><br>Continuous<br>conversions<br>enabled,<br>subsequent<br>conversion time | 20   | _                 | 1200 | Ksps | 8     |

| Table 53. | 12-bit ADC operating conditions (continued) |

|-----------|---------------------------------------------|

|-----------|---------------------------------------------|

- 1. Typical values assume  $V_{DDA} = 5 V$ , Temp = 25 °C,  $f_{ADCK} = 40 MHz$ , unless otherwise stated. Typical values are for reference only, and are not tested in production.

- 2. DC potential difference.

- For packages without dedicated V<sub>REFH</sub> and V<sub>REFL</sub> pins, V<sub>REFH</sub> is internally tied to V<sub>DDA</sub>, and V<sub>REFL</sub> is internally tied to V<sub>SSA</sub>.

- 4. This resistance is external to MCU. To achieve the best results, the analog source resistance must be kept as low as possible. The results in this data sheet were derived from a system that had < 8 Ω analog source resistance. The R<sub>AS</sub>/C<sub>AS</sub> time constant should be kept to < 1 ns.</p>

- 5. Clock and compare cycle need to be set according the guidelines in the block guide.

- 6. ADC conversion will become less reliable above maximum frequency.

- 7. When using ADC hardware averaging, refer to the device *Reference Manual* to determine the most appropriate setting for AVGS.

- 8. Max ADC conversion rate of 1200 Ksps is with 10-bit mode

Figure 19. ADC input impedance equivalency diagram

#### 5.4.5.1.2 12-bit ADC electrical characteristics

#### NOTE

All the parameters in the table are given assuming system clock as the clocking source for ADC.

#### NOTE

For ADC signals adjacent to VDD/VSS or the XTAL pins some degradation in the ADC performance may be observed.

### NOTE

All values guarantee the performance of the ADC for the multiple ADC input channel pins. When using the ADC to monitor the internal analogue parameters, please assume minor degradation.

#### Table 54. 12-bit ADC characteristics ( $V_{REFH} = V_{DDA}$ , $V_{REFL} = V_{SSA}$ )

| Symbol               | Description                    | Conditions <sup>1</sup> | Min. | Typ. <sup>2</sup> | Max. <sup>3</sup> | Unit | Notes |

|----------------------|--------------------------------|-------------------------|------|-------------------|-------------------|------|-------|

| I <sub>DDA_ADC</sub> | Supply current at 2.7 to 5.5 V |                         | 621  | 658 μA @<br>5 V   | 696               | mA   | 4     |

|                     |                                                       |                                                          |       |                                   |                                                                  | -                |                                                                                                             |

|---------------------|-------------------------------------------------------|----------------------------------------------------------|-------|-----------------------------------|------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------|

| Symbol              | Description                                           | Conditions <sup>1</sup>                                  | Min.  | Typ. <sup>2</sup>                 | Max. <sup>3</sup>                                                | Unit             | Notes                                                                                                       |

|                     | Sample Time                                           |                                                          | 275   | _                                 | Refer to<br>the<br>device's<br><i>Reference</i><br><i>Manual</i> | ns               |                                                                                                             |

| TUE                 | Total unadjusted error at 2.7 to 5.5 V                |                                                          | _     | ±4.5                              | ±6.56                                                            | LSB <sup>5</sup> | 6                                                                                                           |

| DNL                 | Differential non-<br>linearity at 2.7 to 5.5 V        |                                                          | -     | ±0.8                              | ±1.07                                                            | LSB <sup>5</sup> | 6                                                                                                           |

| INL                 | Integral non-linearity at 2.7 to 5.5 V                |                                                          | -     | ±1.4                              | ±3.95                                                            | LSB <sup>5</sup> | 6                                                                                                           |

| E <sub>FS</sub>     | Full-scale error at 2.7<br>to 5.5 V                   |                                                          | -     | -2                                | -3.40                                                            | LSB <sup>5</sup> | $V_{ADIN} = V_{DDA}^6$                                                                                      |

| E <sub>ZS</sub>     | Zero-scale error at 2.7<br>to 5.5 V                   |                                                          | -     | -2.7                              | -4.14                                                            | LSB <sup>5</sup> |                                                                                                             |

| EQ                  | Quantization error at 2.7 to 5.5 V                    |                                                          | -     | _                                 | ±0.5                                                             | LSB <sup>5</sup> |                                                                                                             |

| ENOB                | Effective number of bits at 2.7 to 5.5 V              |                                                          | -     | 11.3                              | —                                                                | bits             | 7                                                                                                           |

| SINAD               | Signal-to-noise plus<br>distortion at 2.7 to 5.5<br>V | See ENOB                                                 | _     | 70                                | —                                                                | dB               | SINAD = 6.02 ×<br>ENOB + 1.76                                                                               |

| EIL                 | Input leakage error at<br>2.7 to 5.5 V                |                                                          |       | I <sub>In</sub> × R <sub>AS</sub> |                                                                  | mV               | I <sub>In</sub> = leakage<br>current (refer to<br>the MCU's<br>voltage and<br>current operating<br>ratings) |

| V <sub>TEMP_S</sub> | Temperature sensor slope at 2.7 to 5.5 V              | Across the full<br>temperature<br>range of the<br>device | 1.492 | 1.564                             | 1.636                                                            | mV/°C            | 8, 9                                                                                                        |

| V <sub>TEMP25</sub> | Temperatue sensor<br>voltage at 2.7 to 5.5 V          | 25 °C                                                    | 730   | 740.5                             | 751                                                              | mV               | 8, 9                                                                                                        |

Table 54. 12-bit ADC characteristics ( $V_{REFH} = V_{DDA}$ ,  $V_{REFL} = V_{SSA}$ ) (continued)

1. All accuracy numbers assume the ADC is calibrated with  $V_{REFH} = V_{DDA}$

- 2. Typical values assume  $V_{DDA}$  = 5.0 V, Temp = 25 °C,  $f_{ADCK}$  = 48 MHz unless otherwise stated.

- 3. These values are based on characterization but not covered by test limits in production.

- The ADC supply current depends on the ADC conversion clock speed, conversion rate and ADC\_CFG1[ADLPC] (low power). For lowest power operation, ADC\_CFG1[ADLPC] must be set, the ADC\_CFG2[ADHSC] bit must be clear with 1 MHz ADC conversion clock speed.

- 5. 1 LSB =  $(V_{REFH} V_{REFL})/2^N$

- 6. ADC conversion clock < 16 MHz, Max hardware averaging (AVGE = %1, AVGS = %11)

- 7. Input data is 100 Hz sine wave. ADC conversion clock < 40 MHz.

- 8. ADC conversion clock < 3 MHz

- 9. The sensor must be calibrated to gain good accuracy, so as to provide good linearity, see also AN3031 for more detailed application information of the temperature sensor.

## 5.4.5.2 CMP with 8-bit DAC electrical specifications Table 55. Comparator with 8-bit DAC electrical specifications

| Symbol             | Description                                             | Min. | Typ. <sup>1</sup>    | Max.             | Unit |  |

|--------------------|---------------------------------------------------------|------|----------------------|------------------|------|--|

| V <sub>DD</sub>    | Supply voltage                                          | 2.7  | —                    | 5.5              | V    |  |

| I <sub>DDHS</sub>  | Supply current, High-speed mode <sup>2</sup>            |      | 1 1                  |                  | μA   |  |

|                    | within ambient temperature range                        | _    | 145                  | 200              |      |  |

| I <sub>DDLS</sub>  | Supply current, Low-speed mode <sup>2</sup>             |      | -11                  |                  | μA   |  |

|                    | within ambient temperature range                        | —    | 5                    | 10               |      |  |

| V <sub>AIN</sub>   | Analog input voltage                                    | 0    | 0 - V <sub>DDX</sub> | V <sub>DDX</sub> | V    |  |

| V <sub>AIO</sub>   | Analog input offset voltage, High-speed mode            |      |                      |                  | mV   |  |

|                    | within ambient temperature range                        | -25  | ±1                   | 25               |      |  |

| V <sub>AIO</sub>   | Analog input offset voltage, Low-speed mode             |      |                      |                  | mV   |  |

|                    | within ambient temperature range                        | -40  | ±4                   | 40               |      |  |

| t <sub>DHSB</sub>  | Propagation delay, High-speed mode <sup>3</sup>         |      |                      |                  | ns   |  |

|                    | within ambient temperature range                        | _    | 30                   | 200              |      |  |

| t <sub>DLSB</sub>  | Propagation delay, Low-speed mode <sup>3</sup>          |      |                      |                  | μs   |  |

|                    | within ambient temperature range                        | —    | 0.5                  | 2                |      |  |

| t <sub>DHSS</sub>  | Propagation delay, High-speed mode <sup>4</sup>         |      |                      |                  | ns   |  |

|                    | within ambient temperature range                        | _    | 70                   | 400              |      |  |

| t <sub>DLSS</sub>  | Propagation delay, Low-speed mode <sup>4</sup>          |      |                      |                  | μs   |  |

|                    | within ambient temperature range                        | _    | 1                    | 5                |      |  |

| t <sub>IDHS</sub>  | Initialization delay, High-speed mode <sup>3</sup>      |      |                      |                  | μs   |  |

|                    | within ambient temperature range                        | —    | 1.5                  | 3                |      |  |

| t <sub>IDLS</sub>  | Initialization delay, Low-speed mode <sup>3</sup>       |      |                      | μs               |      |  |

|                    | within ambient temperature range                        | —    | 10                   | 30               |      |  |

| V <sub>HYST0</sub> | Analog comparator hysteresis, Hyst0 (V <sub>AIO</sub> ) |      |                      | mV               |      |  |

|                    | within ambient temperature range                        | —    | 0                    | _                |      |  |

| V <sub>HYST1</sub> | Analog comparator hysteresis, Hyst1, High-speed mode    |      | · · · ·              |                  | mV   |  |

|                    | within ambient temperature range                        | _    | 16                   | 53               |      |  |

|                    | Analog comparator hysteresis, Hyst1, Low-speed mode     |      |                      |                  |      |  |

|                    | within ambient temperature range                        | _    | 11                   | 30               |      |  |

| V <sub>HYST2</sub> | Analog comparator hysteresis, Hyst2, High-speed mode    |      | · · · ·              |                  | mV   |  |

|                    | within ambient temperature range                        | -    | 32                   | 90               |      |  |

|                    | Analog comparator hysteresis, Hyst2, Low-speed mode     |      |                      |                  |      |  |

|                    | within ambient temperature range                        | _    | 22                   | 53               |      |  |

| V <sub>HYST3</sub> | Analog comparator hysteresis, Hyst3, High-speed mode    |      |                      |                  | mV   |  |

| Symbol             | Description                                         | Min.                   | Typ. <sup>1</sup> | Max. | Unit             |

|--------------------|-----------------------------------------------------|------------------------|-------------------|------|------------------|

|                    | within ambient temperature range                    | —                      | 48                | 133  |                  |

|                    | Analog comparator hysteresis, Hyst3, Low-speed mode |                        |                   |      |                  |

|                    | within ambient temperature range - 33 80            |                        | 80                |      |                  |

| I <sub>DAC8b</sub> | 8-bit DAC current adder (enabled)                   | — 10 16 μA             |                   | μA   |                  |

| INL                | 8-bit DAC integral non-linearity                    | -0.6                   | —                 | 0.5  | LSB <sup>5</sup> |

| DNL                | 8-bit DAC differential non-linearity                | n-linearity -0.5 - 0.5 |                   |      | LSB              |

Table 55.

Comparator with 8-bit DAC electrical specifications (continued)

- 1. Typical values assumed at VDDA = 5.0 V, Temp = 25  $^{\circ}$ C, unless otherwise stated.

- 2. Difference at input > 200mV

- 3. Applied  $\pm$  (100 mV + Hyst) around switch point

- 4. Applied ± (30 mV + 2 × Hyst) around switch point

- 5.  $1 \text{ LSB} = V_{\text{reference}}/256$

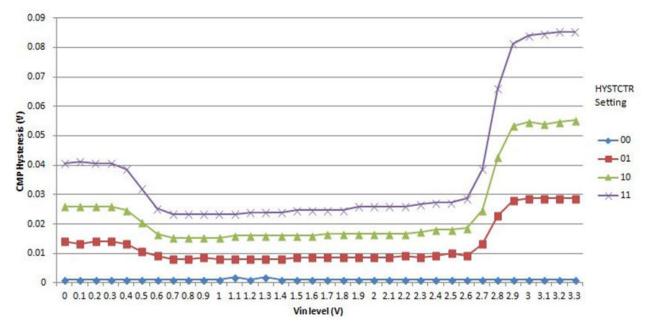

Figure 20. Typical hysteresis vs. Vin level (VDD = 3.3 V, PMODE = 0)

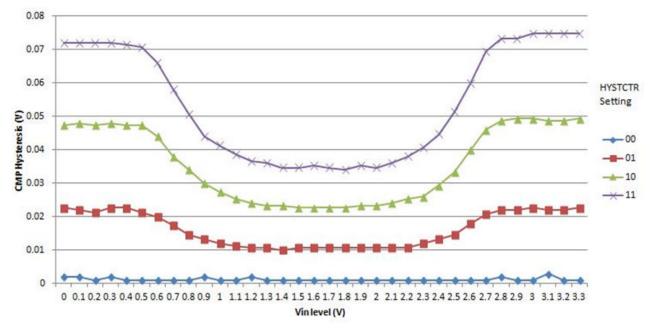

Figure 21. Typical hysteresis vs. Vin level (VDD = 3.3 V, PMODE = 1)

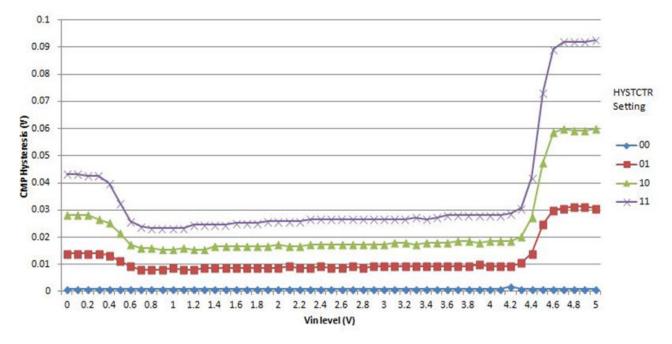

Figure 22. Typical hysteresis vs. Vin level (VDD = 5 V, PMODE = 0)

## 5.4.6.2 LPSPI electrical specifications

The Low Power Serial Peripheral Interface (LPSPI) provides a synchronous serial bus with master and slave operations. Many of the transfer attributes are programmable. The following tables provide timing characteristics for classic LPSPI timing modes.

All timing is shown with respect to 20%  $V_{DD}$  and 80%  $V_{DD}$  thresholds, unless noted, as well as input signal transitions of 3 ns and a 30 pF maximum load on all LPSPI pins.

| Num. | Symbol              | Description                    | Min.                      | Max.                          | Unit               | Note |

|------|---------------------|--------------------------------|---------------------------|-------------------------------|--------------------|------|

| 1    | f <sub>op</sub>     | Frequency of operation         | f <sub>periph</sub> /2048 | f <sub>periph</sub> /2        | Hz                 | 1    |

| 2    | t <sub>SPSCK</sub>  | SPSCK period                   | 2 x t <sub>periph</sub>   | 2048 x<br>t <sub>periph</sub> | ns                 | 2    |

| 3    | t <sub>Lead</sub>   | Enable lead time               | 1/2                       | —                             | t <sub>SPSCK</sub> | _    |

| 4    | t <sub>Lag</sub>    | Enable lag time                | 1/2                       | _                             | t <sub>SPSCK</sub> | —    |

| 5    | t <sub>WSPSCK</sub> | Clock (SPSCK) high or low time | t <sub>periph</sub> - 30  | 1024 x<br>t <sub>periph</sub> | ns                 | -    |

| 6    | t <sub>SU</sub>     | Data setup time (inputs)       | 18                        | _                             | ns                 | —    |

| 7    | t <sub>HI</sub>     | Data hold time (inputs)        | 0                         | _                             | ns                 | -    |

| 8    | t <sub>v</sub>      | Data valid (after SPSCK edge)  | _                         | 15                            | ns                 | _    |

| 9    | t <sub>HO</sub>     | Data hold time (outputs)       | 0                         |                               | ns                 | _    |

| 10   | t <sub>RI</sub>     | Rise time input                | _                         | t <sub>periph</sub> - 25      | ns                 | -    |

|      | t <sub>FI</sub>     | Fall time input                |                           |                               |                    |      |

| 11   | t <sub>RO</sub>     | Rise time output               | —                         | 25                            | ns                 | -    |

|      | t <sub>FO</sub>     | Fall time output               |                           |                               |                    |      |

Table 58. LPSPI master mode timing

1.  $f_{periph} = LPSPI peripheral clock$

2.  $t_{periph} = 1/f_{periph}$

## NOTE

High drive pin should be used for fast bit rate.

#### Design considerations

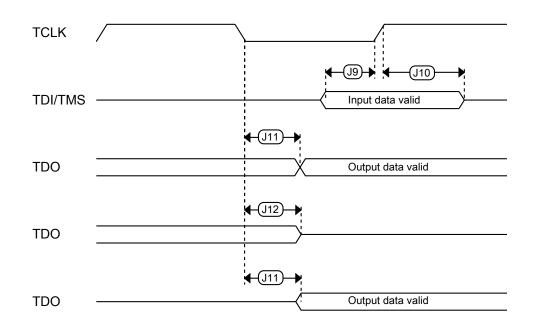

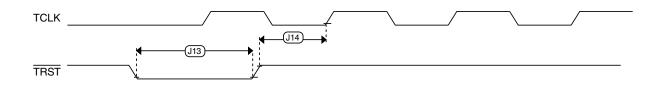

Figure 32. Test Access Port timing

# 6 Design considerations

# 6.1 Hardware design considerations

This device contains protective circuitry to guard against damage due to high static voltage or electric fields. However, take normal precautions to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit.

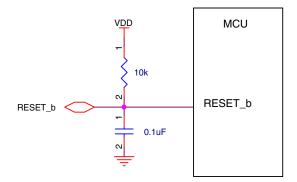

The RESET\_b pin is a pseudo open-drain I/O pin that has an internal pullup resistor. An external RC circuit is recommended to filter noise as shown in the following figure. The resistor value must be in the range of 4.7 k $\Omega$  to 10 k $\Omega$ ; the recommended capacitance value is 0.1  $\mu$ F. The RESET\_b pin also has a selectable digital filter to reject spurious noise.

Figure 36. Reset circuit

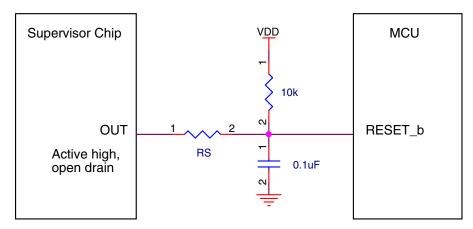

When an external supervisor chip is connected to the RESET\_b pin, a series resistor must be used to avoid damaging the supervisor chip or the RESET\_b pin, as shown in the following figure. The series resistor value (RS below) must be in the range of  $100 \Omega$  to  $1 k\Omega$  depending on the external reset chip drive strength. The supervisor chip must have an active high, open-drain output.

Figure 37. Reset signal connection to external reset chip

• NMI pin

# 7 Part identification

## 7.1 Description

Part numbers for the chip have fields that identify the specific part. You can use the values of these fields to determine the specific part you have received.

## 7.2 Format

Part numbers for this device have the following format:

```

Q KE## A FFF R T PP CC N

```

## 7.3 Fields

This table lists the possible values for each field in the part number (not all combinations are valid):

| Field | Description                 | Values                                                                                     |

|-------|-----------------------------|--------------------------------------------------------------------------------------------|

| Q     | Qualification status        | <ul> <li>M = Fully qualified, general market flow</li> <li>P = Prequalification</li> </ul> |

| KE##  | Kinetis family              | • KE18, KE16, KE14                                                                         |

| A     | Key attribute               | <ul> <li>D = Cortex-M4 with DSP</li> <li>F = Cortex-M4 with DSP and FPU</li> </ul>         |

| FFF   | Program flash memory size   | • 512 = 512 KB                                                                             |

| R     | Silicon revision            | <ul> <li>(Blank) = Main</li> <li>A = Revision after main</li> </ul>                        |

| т     | Temperature range (°C)      | • V = -40 to 105                                                                           |

| PP    | Package identifier          | <ul> <li>LH = 64 LQFP (10 mm x 10 mm)</li> <li>LL = 100 LQFP (14 mm x 14 mm)</li> </ul>    |

| CC    | Maximum CPU frequency (MHz) | • 16 = 168 MHz                                                                             |

| Ν     | Packaging type              | <ul> <li>R = Tape and reel</li> <li>(Blank) = Trays</li> </ul>                             |

Table 65. Part number fields description

## 7.4 Example

This is an example part number:

MKE18F512VLL16

# 8 Revision history

The following table provides a revision history for this document.

| Rev. No. | Date    | Substantial Changes     |

|----------|---------|-------------------------|

| 2        | 09/2016 | Initial public release. |

#### Table 66. Revision history