# E·XFL

#### NXP USA Inc. - MKE18F256VLH16 Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4F                                                       |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 168MHz                                                                 |

| Connectivity               | CANbus, FlexIO, I <sup>2</sup> C, SPI, UART/USART                      |

| Peripherals                | DMA, LVD, PWM, WDT                                                     |

| Number of I/O              | 58                                                                     |

| Program Memory Size        | 256KB (256K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 68K x 8                                                                |

| RAM Size                   | 64K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 16x12b; D/A 1x12b                                                  |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 64-LQFP                                                                |

| Supplier Device Package    | 64-LQFP (10x10)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mke18f256vlh16 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

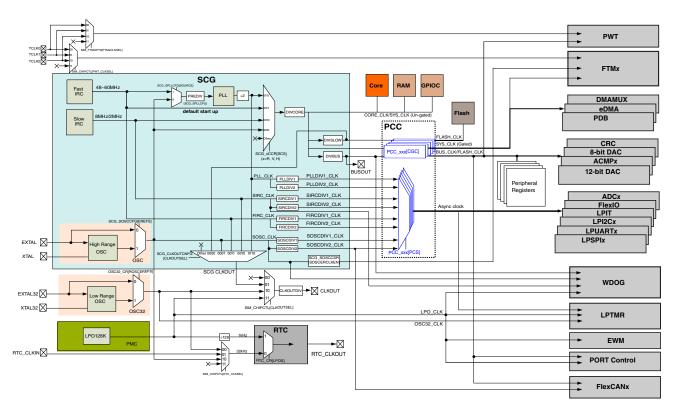

#### **Clock interfaces**

- 3 40 MHz fast external oscillator (OSC)

- 32 kHz slow external oscillator (OSC32)

- 48 60 MHz high-accuracy (up to 1%) fast internal reference clock (FIRC) for high-speed run

- 8 MHz / 2 MHz high-accuracy (up to 3%) slow internal reference clock (SIRC) for low-speed run

- 128 kHz low power oscillator (LPO)

- Phased lock loop (PLL)

- Up to 60 MHz DC external square wave input clock

- System clock generator (SCG)

- Real time counter (RTC)

#### **Power management**

- Low-power ARM Cortex-M4 core with excellent energy efficiency

- Power management controller (PMC) with multiple power modes: HSRun, Run, Wait, Stop, VLPR, VLPW and VLPS

- · Supports clock gating for unused modules, and specific peripherals remain working in low power modes

- POR, LVD/LVR

Type

#### **Operating Characteristics**

- Voltage range: 2.7 to 5.5 V

- Ambient temperature range: -40 to 105 °C

#### **Connectivity and communications interfaces**

- TriggerMUX: for module inter-connectivity

- 3× low-power universal asynchronous receiver/ transmitter (LPUART) modules with DMA support and working at Stop mode

- 2 low-power serial peripheral interface (LPSPI) modules with DMA support and working at Stop mode

- 2× low-power inter-integrated circuit (LPI2C) modules with DMA support and working at Stop mode

- Up to 2 ×FlexCAN modules, with flexible message buffers and mailboxes

- FlexIO module for flexible and high performance serial interfaces emulation

#### **Debug functionality**

- Serial Wire JTAG Debug Port (SWJ-DP) combines

- Debug Watchpoint and Trace (DWT)

- Instrumentation Trace Macrocell (ITM)

- Test Port Interface Unit (TPIU)

- Flash Patch and Breakpoints (FPB)

# Description Resource The Solution Advisor is a web-based tool that features interactive Solution Advisor

**Related Resources**

| Selector<br>Guide   | The Solution Advisor is a web-based tool that features interactive application wizards and a dynamic product selector.         | Solution Advisor                              |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Product Brief       | The Product Brief contains concise overview/summary information to enable quick evaluation of a device for design suitability. | KE1xF512PB <sup>1</sup>                       |

| Reference<br>Manual | The Reference Manual contains a comprehensive description of the structure and function (operation) of a device.               | KE1xFP100M168SF0RM <sup>1</sup>               |

| Data Sheet          | The Data Sheet includes electrical characteristics and signal connections.                                                     | This document:<br>KE1xFP100M168SF0            |

| Chip Errata         | The chip mask set Errata provides additional or corrective information for a particular device mask set.                       | Kinetis_E_0N79P <sup>1</sup>                  |

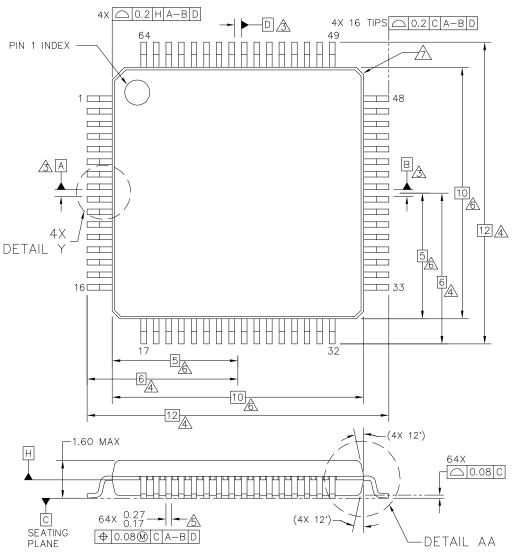

| Package<br>drawing  | Package dimensions are provided in package drawings.                                                                           | 100-LQFP: 98ASS23308W<br>64-LQFP: 98ASS23234W |

1. To find the associated resource, go to http://www.nxp.com and perform a search using this term.

# **1** Ordering information

The following chips are available for ordering.

| Due                | 4                        |               | Mama         |                             | Dee          | kana        | 10    | d ADC cł                           |                       | 0           |

|--------------------|--------------------------|---------------|--------------|-----------------------------|--------------|-------------|-------|------------------------------------|-----------------------|-------------|

| Pro                | duct                     |               | Memo         | ry                          | Pac          | kage        |       |                                    | Comm<br>unicat<br>ion |             |

| Part number        | Marking<br>(Line1/Line2) | Flash<br>(KB) | SRAM<br>(KB) | FlexNVM/<br>FlexRAM<br>(KB) | Pin<br>count | Packa<br>ge | GPIOs | GPIOs<br>(INT/H<br>D) <sup>1</sup> | ADC<br>chann<br>els   | FlexC<br>AN |

| MKE18F512VLL<br>16 | MKE18F512 /<br>VLL16     | 512           | 64           | 64/4                        | 100          | LQFP        | 89    | 89/8                               | 16                    | 2           |

| MKE18F512VL<br>H16 | MKE18F512 /<br>VLH16     | 512           | 64           | 64/4                        | 64           | LQFP        | 58    | 58/8                               | 16                    | 2           |

| MKE18F256VLL<br>16 | MKE18F256 /<br>VLL16     | 256           | 32           | 64/4                        | 100          | LQFP        | 89    | 89/8                               | 16                    | 2           |

| MKE18F256VL<br>H16 | MKE18F256 /<br>VLH16     | 256           | 32           | 64/4                        | 64           | LQFP        | 58    | 58/8                               | 16                    | 2           |

| MKE16F512VLL<br>16 | MKE16F512 /<br>VLL16     | 512           | 64           | 64/4                        | 100          | LQFP        | 89    | 89/8                               | 16                    | 1           |

| MKE16F512VL<br>H16 | MKE16F512 /<br>VLH16     | 512           | 64           | 64/4                        | 64           | LQFP        | 58    | 58/8                               | 16                    | 1           |

| MKE16F256VLL<br>16 | MKE16F256 /<br>VLL16     | 256           | 32           | 64/4                        | 100          | LQFP        | 89    | 89/8                               | 16                    | 1           |

| MKE16F256VL<br>H16 | MKE16F256 /<br>VLH16     | 256           | 32           | 64/4                        | 64           | LQFP        | 58    | 58/8                               | 16                    | 1           |

| MKE14F512VLL<br>16 | MKE14F512 /<br>VLL16     | 512           | 64           | 64/4                        | 100          | LQFP        | 89    | 89/8                               | 16                    | 0           |

| MKE14F512VL<br>H16 | MKE14F512 /<br>VLH16     | 512           | 64           | 64/4                        | 64           | LQFP        | 58    | 58/8                               | 16                    | 0           |

| MKE14F256VLL<br>16 | MKE14F256 /<br>VLL16     | 256           | 32           | 64/4                        | 100          | LQFP        | 89    | 89/8                               | 16                    | 0           |

| MKE14F256VL<br>H16 | MKE14F256 /<br>VLH16     | 256           | 32           | 64/4                        | 64           | LQFP        | 58    | 58/8                               | 16                    | 0           |

Table 1. Ordering information

1. INT: interrupt pin numbers; HD: high drive pin numbers

# 2 Overview

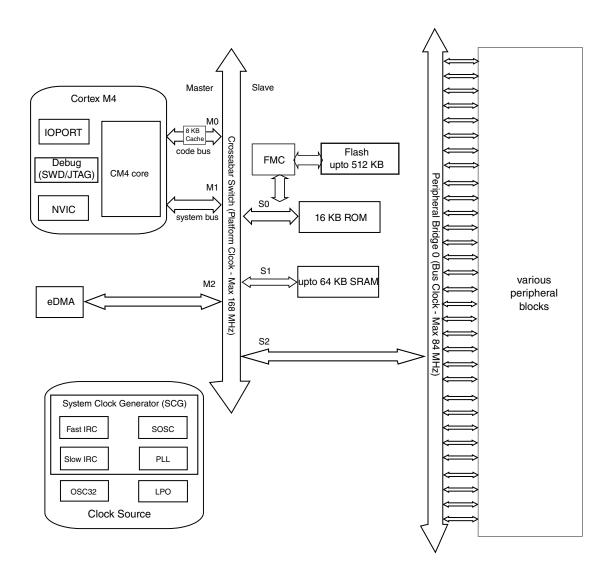

The following figure shows the system diagram of this device.

Overview

Figure 2. System diagram

The crossbar switch connects bus masters and slaves using a crossbar switch structure. This structure allows up to four bus masters to access different bus slaves simultaneously, while providing arbitration among the bus masters when they access the same slave.

# 2.1 System features

The following sections describe the high-level system features.

Figure 4. Clocking block diagram

# 2.1.7 Security

Security state can be enabled via programming flash configure field (0x40e). After enabling device security, the SWD/JTAG port cannot access the memory resources of the MCU.

| External interface | Security       | Unsecure                                                                                                                                                       |

|--------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SWD/JTAG port      | JTAG interface | the debugger can write to the Flash<br>Mass Erase in Progress field of the<br>MDM-AP Control register to trigger a<br>mass erase (Erase All Blocks)<br>command |

### 2.1.7.1 Flash Access Control (FAC)

The FAC is a native or third-party configurable memory protection scheme optimized to allow end users to utilize software libraries while offering programmable restrictions to these libraries. The flash memory is divided into equal size segments that provide protection to proprietary software libraries. The protection of these

# 2.2.3 ADC

This device contains three 12-bit SAR ADC modules. The ADC module supports hardware triggers from FTM, LPTMR, PIT, RTC, external trigger pin and CMP output. It supports wakeup of MCU in low power mode when using internal clock source or external crystal clock.

ADC module has the following features:

- Linear successive approximation algorithm with up to 12-bit resolution

- Up to 16 single-ended external analog inputs

- Support 12-bit, 10-bit, and 8-bit single-ended output modes

- Single or continuous conversion

- Configurable sample time and conversion speed/power

- Input clock selectable from up to four sources

- Operation in low-power modes for lower noise

- Selectable hardware conversion trigger

- Automatic compare with interrupt for less-than, greater-than or equal-to, within range, or out-of-range, programmable value

- Temperature sensor

- Hardware average function

- Selectable Voltage reference: from external or alternate

- Self-Calibration mode

# 2.2.3.1 Temperature sensor

This device contains one temperature sensor internally connected to the input channel of AD26, see ADC electrical characteristics for details of the linearity factor.

The sensor must be calibrated to gain good accuracy, so as to provide good linearity, see also AN3031 for more detailed application information of the temperature sensor.

# 2.2.4 DAC

The 12-bit digital-to-analog converter (DAC) is a low-power, general-purpose DAC. The output of the DAC can be placed on an external pin or set as one of the inputs to the analog comparator, or ADC.

DAC module has the following features:

- On-chip programmable reference generator output. The voltage output range is from 1/4096 Vin to V<sub>in</sub>, and the step is 1/4096 V<sub>in</sub>, where V<sub>in</sub> is the input voltage.

- V<sub>in</sub> can be selected from two reference sources

#### Overview

Each FlexCAN module contains 16 message buffers. Each message buffer is 16 bytes.

The FlexCAN module has the following features:

- Flexible mailboxes of zero to eight bytes data length

- Each mailbox configurable as receive or transmit, all supporting standard and extended messages

- Individual Rx Mask registers per mailbox

- Full-featured Rx FIFO with storage capacity for up to six frames and automatic internal pointer handling with DMA support

- Transmission abort capability

- Programmable clock source to the CAN Protocol Interface, either peripheral clock or oscillator clock

- RAM not used by reception or transmission structures can be used as general purpose RAM space

- Listen-Only mode capability

- Programmable Loop-Back mode supporting self-test operation

- Programmable transmission priority scheme: lowest ID, lowest buffer number, or highest priority

- Time stamp based on 16-bit free-running timer

- Global network time, synchronized by a specific message

- Maskable interrupts

- Independence from the transmission medium (an external transceiver is assumed)

- Short latency time due to an arbitration scheme for high-priority messages

- Low power modes, with programmable wake up on bus activity

- Remote request frames may be handled automatically or by software

- CAN bit time settings and configuration bits can only be written in Freeze mode

- Tx mailbox status (Lowest priority buffer or empty buffer)

- Identifier Acceptance Filter Hit Indicator (IDHIT) register for received frames

- SYNCH bit available in Error in Status 1 register to inform that the module is synchronous with CAN bus

- CRC status for transmitted message

- Rx FIFO Global Mask register

- Selectable priority between mailboxes and Rx FIFO during matching process

- Powerful Rx FIFO ID filtering, capable of matching incoming IDs against either 128 extended, 256 standard, or 512 partial (8 bit) IDs, with up to 32 individual masking capability

### 4.3.1 Core Modules

#### Table 7. JTAG Signal Descriptions

| Chip signal name | Module signal<br>name  | Description              | I/O |

|------------------|------------------------|--------------------------|-----|

| JTAG_TMS         | JTAG_TMS/<br>SWD_DIO   | JTAG Test Mode Selection | I/O |

| JTAG_TCLK        | JTAG_TCLK/<br>SWD_CLK  | JTAG Test Clock          | I   |

| JTAG_TDI         | JTAG_TDI               | JTAG Test Data Input     | I   |

| JTAG_TDO         | JTAG_TDO/<br>TRACE_SWO | JTAG Test Data Output    | 0   |

| JTAG_TRST_b      | JTAG_TRST_b            | JTAG Reset               | I   |

#### Table 8. SWD Signal Descriptions

| Chip signal name | Module signal<br>name | Description       | I/O |

|------------------|-----------------------|-------------------|-----|

| SWD_CLK          | JTAG_TCLK/<br>SWD_CLK | Serial Wire Clock | I   |

| SWD_DIO          | JTAG_TMS/<br>SWD_DIO  | Serial Wire Data  | I/O |

#### Table 9. TPIU Signal Descriptions

| Chip signal name | Module signal<br>name  | Description                                                            | I/O |

|------------------|------------------------|------------------------------------------------------------------------|-----|

| TRACE_SWO        | JTAG_TDO/<br>TRACE_SWO | Trace output data from the ARM CoreSight debug block over a single pin | 0   |

### 4.3.2 System Modules

#### Table 10. System Signal Descriptions

| Chip signal name | Module signal<br>name | Description                                                                                                                                              | I/O |

|------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| NMI_b            | _                     | Non-maskable interrupt NOTE: Driving the NMI signal low forces<br>a non-maskable interrupt, if the NMI function is selected on the<br>corresponding pin. | I   |

| RESET_b          |                       | Reset bidirectional signal                                                                                                                               | I/O |

| VDD              |                       | MCU power                                                                                                                                                | I   |

| VSS              | —                     | MCU ground                                                                                                                                               | I   |

#### Pinouts

Figure 11. 64-pin LQFP package dimensions 1

### 5.2.2 Moisture handling ratings

| Symbol | Description                | Min. | Max. | Unit | Notes |

|--------|----------------------------|------|------|------|-------|

| MSL    | Moisture sensitivity level | _    | 3    | _    | 1     |

1. Determined according to IPC/JEDEC Standard J-STD-020, Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices.

### 5.2.3 ESD handling ratings

| Symbol           | Description                                           | Min.   | Max. | Unit | Notes |

|------------------|-------------------------------------------------------|--------|------|------|-------|

| V <sub>HBM</sub> | Electrostatic discharge voltage, human body model     | - 6000 | 6000 | V    | 1     |

| V <sub>CDM</sub> | Electrostatic discharge voltage, charged-device model |        |      |      | 2     |

|                  | All pins except the corner pins                       | - 500  | 500  | V    |       |

|                  | Corner pins only                                      | - 750  | 750  | V    |       |

| I <sub>LAT</sub> | Latch-up current at ambient temperature upper limit   | - 100  | 100  | mA   | 3     |

1. Determined according to JEDEC Standard JESD22-A114, *Electrostatic Discharge (ESD) Sensitivity Testing Human Body Model (HBM)*.

2. Determined according to JEDEC Standard JESD22-C101, Field-Induced Charged-Device Model Test Method for Electrostatic-Discharge-Withstand Thresholds of Microelectronic Components.

3. Determined according to JEDEC Standard JESD78, IC Latch-Up Test.

### 5.2.4 Voltage and current operating ratings

| Symbol           | Description                                                               | Min.                  | Max.                  | Unit |

|------------------|---------------------------------------------------------------------------|-----------------------|-----------------------|------|

| V <sub>DD</sub>  | Supply voltage                                                            | 2.7                   | 5.5                   | V    |

| I <sub>DD</sub>  | Digital supply current                                                    | _                     | 80                    | mA   |

| V <sub>IO</sub>  | IO pin input voltage                                                      | V <sub>SS</sub> – 0.3 | V <sub>DD</sub> + 0.3 | V    |

| ۱ <sub>D</sub>   | Instantaneous maximum current single pin limit (applies to all port pins) | -25                   | 25                    | mA   |

| V <sub>DDA</sub> | Analog supply voltage                                                     | V <sub>DD</sub> – 0.1 | V <sub>DD</sub> + 0.1 | V    |

#### Table 26. Voltage and current operating ratings

### 5.3 General

# NOTE

The maximum values stated in the following table represent characterized results equivalent to the mean plus three times the standard deviation (mean + 3 sigma).

| Mode  | Symbol                                         | Clock<br>Configur<br>ation                                                                                                      | Description                                                                  | Temperat<br>ure | Min   | Тур   | Max <sup>1</sup> | Uni<br>ts |

|-------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------|-------|-------|------------------|-----------|

| HSRUN | I <sub>DD_HSRUN</sub>                          | PLL                                                                                                                             | Running CoreMark in Flash in <b>Compute</b><br><b>Operation</b> mode.        | 25 ℃<br>105 ℃   | —     | 44.50 | 46.36            | mA        |

|       | Core@168MHz, bus @84MHz,flash<br>@24MHz VDD=5V |                                                                                                                                 |                                                                              |                 | 51.88 | 59.46 |                  |           |

|       |                                                | PLL                                                                                                                             | Running CoreMark in Flash all                                                | 25 °C           |       | 50.49 | 52.35            | 1         |

|       |                                                |                                                                                                                                 | peripheral clock disabled.<br>Core@168MHz, bus @84MHz,flash<br>@24MHz VDD=5V | 105 ℃           |       | 58.31 | 65.89            | -         |

|       |                                                | PLL                                                                                                                             | Running CoreMark in Flash, all                                               | 25 °C           |       | 60.51 | 62.37            | 1         |

|       |                                                |                                                                                                                                 | peripheral clock enabled.                                                    | 105 ℃           |       | 68.62 | 76.20            | 1         |

|       |                                                | @24MHz VDI                                                                                                                      | Core@168MHz, bus @84MHz,flash<br>@24MHz VDD=5V                               |                 |       |       |                  |           |

|       |                                                | PLL                                                                                                                             | Running While(1) loop in Flash, all                                          | 25 °C           | —     | 52.74 | 54.60            | 1         |

|       |                                                | peripheral clock disabled.<br>Core@168MHz, bus @84MHz,flash                                                                     | 105 °C                                                                       | -               | 60.76 | 68.34 |                  |           |

|       |                                                |                                                                                                                                 | @24MHz VDD=5V                                                                |                 |       |       |                  |           |

|       | PLL Running While(1) loop in Flash all         |                                                                                                                                 | 25 °C                                                                        | —               | 62.48 | 64.34 |                  |           |

|       |                                                |                                                                                                                                 | peripheral clock enabled.<br>Core@168MHz, bus @84MHz,flash<br>@24MHz VDD=5V  | 105 °C          | _     | 70.75 | 78.33            |           |

|       |                                                |                                                                                                                                 |                                                                              | 05 %0           |       | 00.01 | 00.07            |           |

| RUN   | IDD_RUN                                        | RUN PLL Running CoreMark in Flash in <b>Compute</b><br><b>Operation</b> mode.<br>Core@120MHz, bus @60MHz,flash<br>@24MHz VDD=5V | 25 ℃<br>105 ℃                                                                | _               | 29.04 | 29.67 | mA               |           |

|       |                                                |                                                                                                                                 | Core@120MHz, bus @60MHz,flash                                                | 105 C           |       | 34.82 | 40.43            |           |

|       |                                                | PLL                                                                                                                             | Running CoreMark in Flash all                                                | 25 °C           |       | 33.29 | 33.92            | -         |

|       |                                                |                                                                                                                                 | peripheral clock disabled.                                                   | 105 ℃           |       | 39.08 | 44.69            | 1         |

|       |                                                |                                                                                                                                 | Core@120MHz, bus @60MHz,flash<br>@24MHz VDD=5V                               |                 |       |       |                  |           |

|       |                                                | PLL                                                                                                                             | Running CoreMark in Flash, all                                               | 25 °C           | _     | 41.00 | 41.63            | -         |

|       |                                                |                                                                                                                                 | peripheral clock enabled.                                                    | 105 °C          | —     | 47.00 | 52.61            |           |

|       |                                                |                                                                                                                                 | Core@120MHz, bus @60MHz,flash<br>@24MHz VDD=5V                               |                 |       |       |                  |           |

|       |                                                | PLL                                                                                                                             | Running While(1) loop in Flash, all                                          | 25 ℃            |       | 34.59 | 35.22            |           |

|       |                                                |                                                                                                                                 | peripheral clock disabled.<br>Core@120MHz, bus @60MHz,flash<br>@24MHz VDD=5V | 105 ℃           |       | 40.68 | 46.29            |           |

Table 32.

Power consumption operating behaviors

- AN2764: Improving the Transient Immunity Performance of Microcontroller-Based Applications

- AN1259: System Design and Layout Techniques for Noise Reduction in MCU-Based Systems

### 5.3.1.7.1 EMC radiated emissions operating behaviors

EMC measurements to IC-level IEC standards are available from NXP on request.

### 5.3.1.7.2 Designing with radiated emissions in mind

To find application notes that provide guidance on designing your system to minimize interference from radiated emissions.

- 1. Go to http://www.nxp.com.

- 2. Perform a keyword search for "EMC design".

- 3. Select the "Documents" category and find the application notes.

### 5.3.1.8 Capacitance attributes

#### Table 33. Capacitance attributes

| Symbol            | Description                     | Min. | Max. | Unit |

|-------------------|---------------------------------|------|------|------|

| C <sub>IN_A</sub> | Input capacitance: analog pins  | —    | 7    | pF   |

| C <sub>IN_D</sub> | Input capacitance: digital pins | —    | 7    | pF   |

### NOTE

Please refer to External Oscillator electrical specifications for EXTAL/XTAL pins.

### 5.3.2 Switching specifications

### 5.3.2.1 Device clock specifications

| Symbol              | Description           | Min. | Max. | Unit | Notes |

|---------------------|-----------------------|------|------|------|-------|

| High Speed RUN mode |                       |      |      |      |       |

| f <sub>SYS</sub>    | System and core clock | —    | 168  | MHz  |       |

| f <sub>BUS</sub>    | Bus clock             | _    | 84   | MHz  |       |

#### Table 34. Device clock specifications

| Symbol               | Description              | Min.            | Max. | Unit | Notes |  |

|----------------------|--------------------------|-----------------|------|------|-------|--|

| f <sub>FLASH</sub>   | Flash clock              |                 |      | MHz  |       |  |

|                      | Normal RUN mod           | le              | •    |      | •     |  |

| f <sub>SYS</sub>     | System and core clock    | _               | 120  | MHz  |       |  |

| f <sub>BUS</sub>     | Bus clock                | —               | 60   | MHz  |       |  |

| f <sub>FLASH</sub>   | Flash clock              | —               | 25   | MHz  |       |  |

| f <sub>LPTMR</sub>   | LPTMR clock              | —               | 50   | MHz  |       |  |

|                      | VLPR / VLPW mod          | de <sup>1</sup> |      |      |       |  |

| f <sub>SYS</sub>     | System and core clock    | _               | 4    | MHz  |       |  |

| f <sub>BUS</sub>     | Bus clock                | —               | 4    | MHz  |       |  |

| f <sub>FLASH</sub>   | Flash clock              | _               | 1    | MHz  |       |  |

| f <sub>ERCLK</sub>   | External reference clock | _               | 16   | MHz  |       |  |

| f <sub>LPTMR</sub>   | LPTMR clock              | _               | 13   | MHz  |       |  |

| f <sub>FlexCAN</sub> | FlexCAN clock            |                 | 4    | MHz  |       |  |

| Table 34. | <b>Device clock specifications</b> | (continued) |

|-----------|------------------------------------|-------------|

|-----------|------------------------------------|-------------|

1. The frequency limitations in VLPR / VLPW mode here override any frequency specification listed in the timing specification for any other module.

## 5.3.2.2 AC electrical characteristics

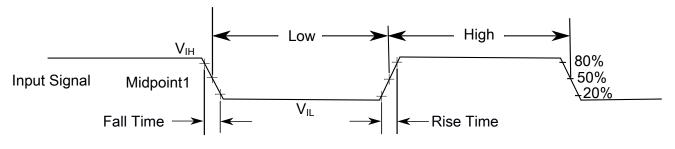

Unless otherwise specified, propagation delays are measured from the 50% to the 50% point, and rise and fall times are measured at the 20% and 80% points, as shown in the following figure.

The midpoint is V<sub>IL</sub> + (V<sub>IH</sub> - V<sub>IL</sub>) / 2

### Figure 16. Input signal measurement reference

All digital I/O switching characteristics, unless otherwise specified, assume that the output pins have the following characteristics.

- $C_L=30 \text{ pF loads}$

- Normal drive strength

1. Maximum time based on expectations at cycling end-of-life.

| Symbol                  | Description                                 | Min. | Тур. | Max. | Unit | Notes |

|-------------------------|---------------------------------------------|------|------|------|------|-------|

|                         | Read 1s Block execution time                |      |      |      |      |       |

| t <sub>rd1blk64k</sub>  | 64 KB data flash                            | _    | _    | 0.5  | ms   |       |

| t <sub>rd1blk512k</sub> | 512 KB program flash                        | _    | _    | 1.8  | ms   |       |

| t <sub>rd1sec2k</sub>   | Read 1s Section execution time (2 KB flash) | _    |      | 75   | μs   | 1     |

| t <sub>rd1sec4k</sub>   | Read 1s Section execution time (4 KB flash) | _    | _    | 100  | μs   | 1     |

| t <sub>pgmchk</sub>     | Program Check execution time                | —    | _    | 95   | μs   | 1     |

| t <sub>rdrsrc</sub>     | Read Resource execution time                | —    | _    | 40   | μs   | 1     |

| t <sub>pgm8</sub>       | Program Phrase execution time               | —    | 90   | 150  | μs   |       |

|                         | Erase Flash Block execution time            |      |      |      |      | 2     |

| t <sub>ersblk64k</sub>  | <ul> <li>64 KB data flash</li> </ul>        | _    | 55   | 475  | ms   |       |

| t <sub>ersblk512k</sub> | • 512 KB program flash                      | _    | 435  | 3700 | ms   |       |

| t <sub>ersscr</sub>     | Erase Flash Sector execution time           |      | 15   | 115  | ms   | 2     |

| t <sub>pgmsec1k</sub>   | Program Section execution time (1KB flash)  | _    | 5    | —    | ms   |       |

| t <sub>rd1all</sub>     | Read 1s All Blocks execution time           | _    | _    | 2.2  | ms   |       |

| t <sub>rdonce</sub>     | Read Once execution time                    | _    | —    | 30   | μs   | 1     |

| t <sub>pgmonce</sub>    | Program Once execution time                 | _    | 90   | —    | μs   |       |

| t <sub>ersall</sub>     | Erase All Blocks execution time             | _    | 500  | 4200 | ms   | 2     |

| t <sub>vfykey</sub>     | Verify Backdoor Access Key execution time   | —    | —    | 30   | μs   | 1     |

| t <sub>ersallu</sub>    | Erase All Blocks Unsecure execution time    | —    | 500  | 4200 | ms   | 2     |

|                         | Program Partition for EEPROM execution time |      |      |      |      |       |

| t <sub>pgmpart32k</sub> | 32 KB EEPROM backup                         | _    | 70   | —    | ms   |       |

| t <sub>pgmpart64k</sub> | 64 KB EEPROM backup                         | _    | 71   | —    | ms   |       |

|                         | Set FlexRAM Function execution time:        |      |      |      |      |       |

| t <sub>setramff</sub>   | Control Code 0xFF                           | _    | 70   | _    | μs   |       |

| t <sub>setram32k</sub>  | 32 KB EEPROM backup                         | _    | 0.8  | 1.2  | ms   |       |

| t <sub>setram48k</sub>  | 48 KB EEPROM backup                         | _    | 1.0  | 1.5  | ms   |       |

| t <sub>setram64k</sub>  | 64 KB EEPROM backup                         | _    | 1.3  | 1.9  | ms   |       |

|                         | Byte-write to FlexRAM execution time:       |      |      |      |      |       |

| t <sub>eewr8b32k</sub>  | 32 KB EEPROM backup                         | _    | 385  | 1700 | μs   |       |

| t <sub>eewr8b48k</sub>  | 48 KB EEPROM backup                         | _    | 430  | 1850 | μs   |       |

| t <sub>eewr8b64k</sub>  | 64 KB EEPROM backup                         | _    | 475  | 2000 | μs   |       |

|                         | 16-bit write to FlexRAM execution time:     |      |      |      |      |       |

### 5.4.3.1.2 Flash timing specifications — commands Table 50. Flash command timing specifications

| Symbol                  | Description                                                 | Min. | Тур. | Max. | Unit | Notes |

|-------------------------|-------------------------------------------------------------|------|------|------|------|-------|

| t <sub>eewr16b32k</sub> | 32 KB EEPROM backup                                         | —    | 385  | 1700 | μs   |       |

| t <sub>eewr16b48k</sub> | 48 KB EEPROM backup                                         | —    | 430  | 1850 | μs   |       |

| t <sub>eewr16b64k</sub> | 64 KB EEPROM backup                                         | —    | 475  | 2000 | μs   |       |

| t <sub>eewr32bers</sub> | area 32-bit write to erased FlexRAM location execution time |      | 360  | 1500 | μs   |       |

|                         | 32-bit write to FlexRAM execution time:                     |      |      |      |      |       |

| t <sub>eewr32b32k</sub> | 32 KB EEPROM backup                                         | —    | 630  | 2000 | μs   |       |

| t <sub>eewr32b48k</sub> | 48 KB EEPROM backup                                         | _    | 720  | 2125 | μs   |       |

| t <sub>eewr32b64k</sub> | 64 KB EEPROM backup                                         | —    | 810  | 2250 | μs   |       |

#### Table 50. Flash command timing specifications (continued)

1. Assumes 25MHz or greater flash clock frequency.

2. Maximum times for erase parameters based on expectations at cycling end-of-life.

#### 5.4.3.1.3 Flash high voltage current behaviors Table 51. Flash high voltage current behaviors

| Symbol              | Description                                                           | Min. | Тур. | Max. | Unit |

|---------------------|-----------------------------------------------------------------------|------|------|------|------|

| I <sub>DD_PGM</sub> | Average current adder during high voltage flash programming operation | _    | 3.5  | 7.5  | mA   |

| I <sub>DD_ERS</sub> | Average current adder during high voltage flash erase operation       | —    | 1.5  | 4.0  | mA   |

#### 5.4.3.1.4 Reliability specifications Table 52. NVM reliability specifications

| Symbol                   | Description                                  | Min.  | Typ. <sup>1</sup> | Max. | Unit   | Notes |  |  |  |  |

|--------------------------|----------------------------------------------|-------|-------------------|------|--------|-------|--|--|--|--|

|                          | Program Flash                                |       |                   |      |        |       |  |  |  |  |

| t <sub>nvmretp10k</sub>  | Data retention after up to 10 K cycles       | 5     | 50                | —    | years  |       |  |  |  |  |

| t <sub>nvmretp1k</sub>   | Data retention after up to 1 K cycles        | 20    | 100               | _    | years  |       |  |  |  |  |

| n <sub>nvmcycp</sub>     | Cycling endurance                            | 10 K  | 50 K              | _    | cycles | 2     |  |  |  |  |

|                          | Data Flas                                    | sh    | •                 |      |        |       |  |  |  |  |

| t <sub>nvmretd10k</sub>  | Data retention after up to 10 K cycles       | 5     | 50                | —    | years  |       |  |  |  |  |

| t <sub>nvmretd1k</sub>   | Data retention after up to 1 K cycles        | 20    | 100               | _    | years  |       |  |  |  |  |

| n <sub>nvmcycd</sub>     | Cycling endurance                            | 10 K  | 50 K              | _    | cycles | 2     |  |  |  |  |

|                          | FlexRAM as El                                | EPROM |                   |      |        |       |  |  |  |  |

| t <sub>nvmretee100</sub> | Data retention up to 100% of write endurance | 5     | 50                | —    | years  |       |  |  |  |  |

| t <sub>nvmretee10</sub>  | Data retention up to 10% of write endurance  | 20    | 100               | —    | years  |       |  |  |  |  |

| n <sub>nvmcycee</sub>    | Cycling endurance for EEPROM backup          | 20 K  | 50 K              | _    | cycles | 2     |  |  |  |  |

| Symbol                  | Description                                                | Min.   | Typ. <sup>1</sup> | Max. | Unit   | Notes |

|-------------------------|------------------------------------------------------------|--------|-------------------|------|--------|-------|

|                         | Write endurance                                            |        |                   |      |        | 3     |

| n <sub>nvmwree16</sub>  | <ul> <li>EEPROM backup to FlexRAM ratio = 16</li> </ul>    | 140 K  | 400 K             |      | writes |       |

| n <sub>nvmwree128</sub> | <ul> <li>EEPROM backup to FlexRAM ratio = 128</li> </ul>   | 1.26 M | 3.2 M             | —    | writes |       |

| n <sub>nvmwree512</sub> | <ul> <li>EEPROM backup to FlexRAM ratio = 512</li> </ul>   | 5 M    | 12.8 M            | —    | writes |       |

| n <sub>nvmwree2k</sub>  | <ul> <li>EEPROM backup to FlexRAM ratio = 2,048</li> </ul> | 20 M   | 50 M              | —    | writes |       |

Table 52. NVM reliability specifications (continued)

- Typical data retention values are based on measured response accelerated at high temperature and derated to a constant 25°C use profile. Engineering Bulletin EB618 does not apply to this technology. Typical endurance defined in Engineering Bulletin EB619.

- 2. Cycling endurance represents number of program/erase cycles at -40°C  $\leq$  T<sub>j</sub>  $\leq$  125°C.

- Write endurance represents the number of writes to each FlexRAM location at -40°C ≤Tj ≤ 125°C influenced by the cycling endurance of the FlexNVM and the allocated EEPROM backup. Minimum and typical values assume all 16-bit or 32-bit writes to FlexRAM; all 8-bit writes result in 50% less endurance.

### 5.4.4 Security and integrity modules

There are no specifications necessary for the device's security and integrity modules.

### 5.4.5 Analog

### 5.4.5.1 ADC electrical specifications

|                   | Table 55. 12-bit ADC operating conditions |                                                                   |                   |                   |                            |      |       |  |  |  |  |

|-------------------|-------------------------------------------|-------------------------------------------------------------------|-------------------|-------------------|----------------------------|------|-------|--|--|--|--|

| Symbol            | Description                               | Conditions                                                        | Min.              | Typ. <sup>1</sup> | Max.                       | Unit | Notes |  |  |  |  |

| $V_{DDA}$         | Supply voltage                            | Absolute                                                          | 2.7               | —                 | 5.5                        | V    |       |  |  |  |  |

| $\Delta V_{DDA}$  | Supply voltage                            | Delta to V <sub>DD</sub><br>(V <sub>DD</sub> – V <sub>DDA</sub> ) | -100              | 0                 | +100                       | mV   | 2     |  |  |  |  |

| $\Delta V_{SSA}$  | Ground voltage                            | Delta to V <sub>SS</sub> (V <sub>SS</sub><br>– V <sub>SSA</sub> ) | -100              | 0                 | +100                       | mV   | 2     |  |  |  |  |

| $V_{REFH}$        | ADC reference voltage high                |                                                                   | 2.5               | V <sub>DDA</sub>  | V <sub>DDA</sub> +<br>100m | V    | 3     |  |  |  |  |

| V <sub>REFL</sub> | ADC reference voltage low                 |                                                                   | - 100             | 0                 | 100                        | mV   | 3     |  |  |  |  |

| V <sub>ADIN</sub> | Input voltage                             |                                                                   | V <sub>REFL</sub> | _                 | V <sub>REFH</sub>          | V    |       |  |  |  |  |

| C <sub>ADIN</sub> | Input capacitance                         |                                                                   | _                 | 4                 | 5                          | pF   |       |  |  |  |  |

| R <sub>ADIN</sub> | Input series resistance                   |                                                                   | _                 | 2                 | 5                          | kΩ   |       |  |  |  |  |

#### 5.4.5.1.1 12-bit ADC operating conditions Table 53. 12-bit ADC operating conditions

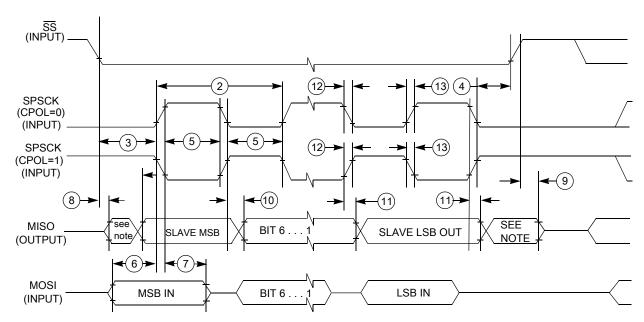

### 5.4.6.2 LPSPI electrical specifications

The Low Power Serial Peripheral Interface (LPSPI) provides a synchronous serial bus with master and slave operations. Many of the transfer attributes are programmable. The following tables provide timing characteristics for classic LPSPI timing modes.

All timing is shown with respect to 20%  $V_{DD}$  and 80%  $V_{DD}$  thresholds, unless noted, as well as input signal transitions of 3 ns and a 30 pF maximum load on all LPSPI pins.

| Num. | Symbol              | Description                    | Min.                      | Max.                          | Unit               | Note |

|------|---------------------|--------------------------------|---------------------------|-------------------------------|--------------------|------|

| 1    | f <sub>op</sub>     | Frequency of operation         | f <sub>periph</sub> /2048 | f <sub>periph</sub> /2        | Hz                 | 1    |

| 2    | t <sub>SPSCK</sub>  | SPSCK period                   | 2 x t <sub>periph</sub>   | 2048 x<br>t <sub>periph</sub> | ns                 | 2    |

| 3    | t <sub>Lead</sub>   | Enable lead time               | 1/2                       | —                             | t <sub>SPSCK</sub> | _    |

| 4    | t <sub>Lag</sub>    | Enable lag time                | 1/2                       | _                             | t <sub>SPSCK</sub> | —    |

| 5    | t <sub>WSPSCK</sub> | Clock (SPSCK) high or low time | t <sub>periph</sub> - 30  | 1024 x<br>t <sub>periph</sub> | ns                 | -    |

| 6    | t <sub>SU</sub>     | Data setup time (inputs)       | 18                        | _                             | ns                 | —    |

| 7    | t <sub>HI</sub>     | Data hold time (inputs)        | 0                         | _                             | ns                 | —    |

| 8    | t <sub>v</sub>      | Data valid (after SPSCK edge)  | _                         | 15                            | ns                 | _    |

| 9    | t <sub>HO</sub>     | Data hold time (outputs)       | 0                         |                               | ns                 | _    |

| 10   | t <sub>RI</sub>     | Rise time input                | _                         | t <sub>periph</sub> - 25      | ns                 | —    |

|      | t <sub>FI</sub>     | Fall time input                |                           |                               |                    |      |

| 11   | t <sub>RO</sub>     | Rise time output               | —                         | 25                            | ns                 | -    |

|      | t <sub>FO</sub>     | Fall time output               |                           |                               |                    |      |

Table 58. LPSPI master mode timing

1.  $f_{periph} = LPSPI peripheral clock$

2.  $t_{periph} = 1/f_{periph}$

### NOTE

High drive pin should be used for fast bit rate.

| Num. | Symbol              | Description                    | Min.                     | Max.                     | Unit                | Note |

|------|---------------------|--------------------------------|--------------------------|--------------------------|---------------------|------|

| 4    | t <sub>Lag</sub>    | Enable lag time                | 1                        | —                        | t <sub>periph</sub> | —    |

| 5    | t <sub>WSPSCK</sub> | Clock (SPSCK) high or low time | t <sub>periph</sub> - 30 | —                        | ns                  |      |

| 6    | t <sub>SU</sub>     | Data setup time (inputs)       | 2.5                      | —                        | ns                  | —    |

| 7    | t <sub>HI</sub>     | Data hold time (inputs)        | 3.5                      | _                        | ns                  | —    |

| 8    | t <sub>a</sub>      | Slave access time              | —                        | t <sub>periph</sub>      | ns                  | 3    |

| 9    | t <sub>dis</sub>    | Slave MISO disable time        | —                        | t <sub>periph</sub>      | ns                  | 4    |

| 10   | t <sub>v</sub>      | Data valid (after SPSCK edge)  | —                        | 31                       | ns                  | —    |

| 11   | t <sub>HO</sub>     | Data hold time (outputs)       | 0                        | _                        | ns                  | —    |

| 12   | t <sub>RI</sub>     | Rise time input                | —                        | t <sub>periph</sub> - 25 | ns                  | —    |

|      | t <sub>FI</sub>     | Fall time input                |                          |                          |                     |      |

| 13   | t <sub>RO</sub>     | Rise time output               | —                        | 25                       | ns                  | —    |

|      | t <sub>FO</sub>     | Fall time output               |                          |                          |                     |      |

| Table 59. | LPSPI slave | mode timing | (continued) |

|-----------|-------------|-------------|-------------|

|-----------|-------------|-------------|-------------|

1.  $f_{periph} = LPSPI$  peripheral clock

2.  $t_{periph} = 1/f_{periph}$

- 3. Time to data active from high-impedance state

- 4. Hold time to high-impedance state

#### Design considerations

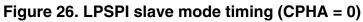

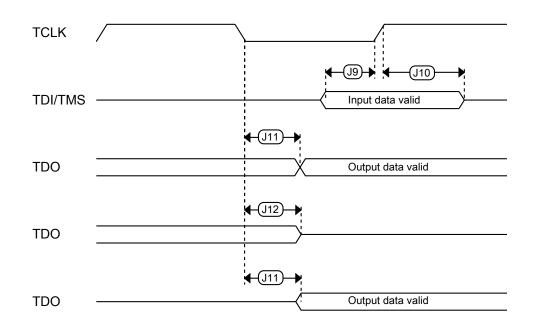

Figure 32. Test Access Port timing

# 6 Design considerations

# 6.1 Hardware design considerations

This device contains protective circuitry to guard against damage due to high static voltage or electric fields. However, take normal precautions to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit.

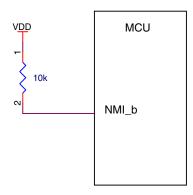

Do not add a pull-down resistor or capacitor on the NMI\_b pin, because a low level on this pin will trigger non-maskable interrupt. When this pin is enabled as the NMI function, an external pull-up resistor (10 k $\Omega$ ) as shown in the following figure is recommended for robustness.

If the NMI\_b pin is used as an I/O pin, the non-maskable interrupt handler is required to disable the NMI function by remapping to another function. The NMI function is disabled by programming the FOPT[NMI\_DIS] bit to zero.

Figure 38. NMI pin biasing

• Debug interface

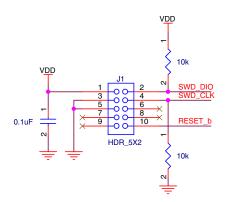

This MCU uses the standard ARM SWD interface protocol as shown in the following figure. While pull-up or pull-down resistors are not required (SWD\_DIO has an internal pull-up and SWD\_CLK has an internal pull-down), external 10 k $\Omega$  pull resistors are recommended for system robustness. The RESET\_b pin recommendations mentioned above must also be considered.

Figure 39. SWD debug interface

• Unused pin

#### How to Reach Us:

Home Page: nxp.com

Web Support: nxp.com/support Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals", must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/SalesTermsandConditions.

NXP, the NXP logo, Freescale, the Freescale logo and Kinetis are trademarks of NXP B.V. All other product or service names are the property of their respective owners. ARM and Cortex are registered trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved.

©2016 NXP B.V.

Document Number KE1xFP100M168SF0 Revision 2, 09/2016