Welcome to <u>E-XFL.COM</u>

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                        |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 84MHz                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC, SPI, SSC, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT           |

| Number of I/O              | 63                                                                     |

| Program Memory Size        | 512KB (512K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 96K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                           |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                  |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 100-TFBGA                                                              |

| Supplier Device Package    | 100-TFBGA (9x9)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/atmel/atsam3a8ca-cu               |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 7.2.3.3 Enhanced Embedded Flash Controller

The Enhanced Embedded Flash Controller (EEFC) manages accesses performed by the masters of the system. It enables reading the Flash and writing the write buffer. It also contains a User Interface, mapped within the Memory Controller on the APB.

The EEFC ensures the interface of the Flash block with the 32-bit internal bus. Its 128-bit wide memory interface increases performance.

The user can choose between high performance or lower current consumption by selecting either 128-bit or 64-bit access. It also manages the programming, erasing, locking and unlocking sequences of the Flash using a full set of commands.

One of the commands returns the embedded Flash descriptor definition that informs the system about the Flash organization, thus making the software generic.

#### 7.2.3.4 Lock Regions

Several lock bits are used to protect write and erase operations on lock regions. A lock region is composed of several consecutive pages, and each lock region has its associated lock bit.

| Product | Number of Lock Bits | Lock Region Size     |  |  |

|---------|---------------------|----------------------|--|--|

| SAM3X8  |                     |                      |  |  |

| SAM3A8  | 32                  | 16 Kbytes (64 pages) |  |  |

| SAM3X4  | 10                  |                      |  |  |

| SAM3A4  | 16                  | 16 Kbytes (64 pages) |  |  |

#### Table 7-3. Number of Lock Bits

If a locked-region's erase or program command occurs, the command is aborted and the EEFC triggers an interrupt.

The lock bits are software programmable through the EEFC User Interface. The "Set Lock Bit" command enables the protection. The "Clear Lock Bit" command unlocks the lock region.

Asserting the ERASE pin clears the lock bits, thus unlocking the entire Flash.

#### 7.2.3.5 Security Bit Feature

The SAM3X/A series features a security bit, based on a specific General Purpose NVM bit (GPNVM bit 0). When the security is enabled, any access to the Flash, either through the ICE interface or through the Fast Flash Programming Interface (FFPI), is forbidden. This ensures the confidentiality of the code programmed in the Flash.

This security bit can only be enabled through the "Set General Purpose NVM Bit 0" command of the EEFC0 User Interface. Disabling the security bit can only be achieved by asserting the ERASE pin at 1, and after a full Flash erase is performed. When the security bit is deactivated, all accesses to the Flash are permitted.

It is important to note that the assertion of the ERASE pin should always be longer than 200 ms.

As the ERASE pin integrates a permanent pull-down, it can be left unconnected during normal operation. However, it is safer to connect it directly to GND for the final application.

#### 7.2.3.6 Calibration Bits

NVM bits are used to calibrate the brownout detector and the voltage regulator. These bits are factory configured and cannot be changed by the user. The ERASE pin has no effect on the calibration bits.

#### 7.2.3.7 Unique Identifier

Each device integrates its own 128-bit unique identifier. These bits are factory configured and cannot be changed by the user. The ERASE pin has no effect on the unique identifier.

## 10.4.3.6 Application Program Status Register

The APSR contains the current state of the condition flags from previous instruction executions. See the register summary in Table 10-2 on page 51 for its attributes. The bit assignments are:

#### • N

Negative or less than flag:

0 = operation result was positive, zero, greater than, or equal

1 = operation result was negative or less than.

## • Z

Zero flag:

0 = operation result was not zero

1 = operation result was zero.

## • C

Carry or borrow flag:

0 = add operation did not result in a carry bit or subtract operation resulted in a borrow bit

1 = add operation resulted in a carry bit or subtract operation did not result in a borrow bit.

## • V

Overflow flag:

0 = operation did not result in an overflow

1 = operation resulted in an overflow.

## • Q

Sticky saturation flag:

0 = indicates that saturation has not occurred since reset or since the bit was last cleared to zero

1 = indicates when an SSAT or USAT instruction results in saturation.

This bit is cleared to zero by software using an MRS instruction.

#### 10.4.3.7 Interrupt Program Status Register

The IPSR contains the exception type number of the current *Interrupt Service Routine* (ISR). See the register summary in Table 10-2 on page 51 for its attributes. The bit assignments are:

#### • ISR\_NUMBER

This is the number of the current exception:

- 0 = Thread mode

- 1 = Reserved

- 2 = NMI

- 3 = Hard fault

- 4 = Memory management fault

- 5 = Bus fault

- 6 = Usage fault

#### 10.18.11 WFE

Wait For Event.

#### 10.18.11.1 Syntax

WFE{cond}

where:

cond is an optional condition code, see "Conditional execution" on page 91.

## 10.18.11.2 Operation

WFE is a hint instruction.

If the event register is 0, WFE suspends execution until one of the following events occurs:

- an exception, unless masked by the exception mask registers or the current priority level

- an exception enters the Pending state, if SEVONPEND in the System Control Register is set

- a Debug Entry request, if Debug is enabled

- an event signaled by a peripheral or another processor in a multiprocessor system using the SEV instruction.

If the event register is 1, WFE clears it to 0 and returns immediately.

For more information see "Power management" on page 80.

#### 10.18.11.3 Condition flags

This instruction does not change the flags.

#### 10.18.11.4 Examples

WFE ; Wait for event

## • UNDEFINSTR

Undefined instruction usage fault:

- 0: no undefined instruction usage fault

- 1: the processor has attempted to execute an undefined instruction.

When this bit is set to 1, the PC value stacked for the exception return points to the undefined instruction.

An undefined instruction is an instruction that the processor cannot decode.

The UFSR bits are sticky. This means as one or more fault occurs, the associated bits are set to 1. A bit that is set to 1 is cleared to 0 only by writing 1 to that bit, or by a reset.

#### Thread-safe

In a multi-tasking environment, thread-safe functions use safeguard mechanisms when accessing shared resources, to ensure correct operation without the risk of shared access conflicts.

#### Thumb instruction

One or two halfwords that specify an operation for a processor to perform. Thumb instructions must be halfwordaligned.

#### Unaligned

A data item stored at an address that is not divisible by the number of bytes that defines the data size is said to be unaligned. For example, a word stored at an address that is not divisible by four.

#### Undefined

Indicates an instruction that generates an Undefined instruction exception.

#### Unpredictable (UNP)

You cannot rely on the behavior. Unpredictable behavior must not represent security holes. Unpredictable behavior must not halt or hang the processor, or any parts of the system.

#### Warm reset

Also known as a core reset. Initializes the majority of the processor excluding the debug controller and debug logic. This type of reset is useful if you are using the debugging features of a processor.

## Word

A 32-bit data item.

#### Write

Writes are defined as operations that have the semantics of a store. Writes include the Thumb instructions STM, STR, STRH, STRB, and PUSH.

## 14.6.9 RTC Interrupt Enable Register

| Name:<br>Address:<br>Access: | RTC_IER<br>0x400E1A80<br>Write-only |    |       |       |       |       |       |

|------------------------------|-------------------------------------|----|-------|-------|-------|-------|-------|

| 31                           | 30                                  | 29 | 28    | 27    | 26    | 25    | 24    |

| —                            | _                                   | -  | -     | -     | -     | _     | -     |

| 23                           | 22                                  | 21 | 20    | 19    | 18    | 17    | 16    |

| _                            | -                                   | _  | _     | _     | _     | _     | -     |

| 15                           | 14                                  | 13 | 12    | 11    | 10    | 9     | 8     |

| _                            | -                                   | —  | —     | —     | —     | —     | -     |

| 7                            | 6                                   | 5  | 4     | 3     | 2     | 1     | 0     |

| -                            | _                                   | -  | CALEN | TIMEN | SECEN | ALREN | ACKEN |

#### • ACKEN: Acknowledge Update Interrupt Enable

0: No effect.

1: The acknowledge for update interrupt is enabled.

## • ALREN: Alarm Interrupt Enable

0: No effect.

1: The alarm interrupt is enabled.

## • SECEN: Second Event Interrupt Enable

0: No effect.

1: The second periodic interrupt is enabled.

## • TIMEN: Time Event Interrupt Enable

0: No effect.

1: The selected time event interrupt is enabled.

## • CALEN: Calendar Event Interrupt Enable

0: No effect.

1: The selected calendar event interrupt is enabled.

# 22.7 AHB DMA Controller (DMAC) User Interface

## Table 22-5.Register Mapping

| Offset                     | Register                                                                                                             | Name        | Access     | Reset      |

|----------------------------|----------------------------------------------------------------------------------------------------------------------|-------------|------------|------------|

| 0x000                      | DMAC Global Configuration Register                                                                                   | DMAC_GCFG   | Read-write | 0x10       |

| 0x004                      | DMAC Enable Register                                                                                                 | DMAC_EN     | Read-write | 0x0        |

| 0x008                      | DMAC Software Single Request Register                                                                                | DMAC_SREQ   | Read-write | 0x0        |

| 0x00C                      | DMAC Software Chunk Transfer Request Register                                                                        | DMAC_CREQ   | Read-write | 0x0        |

| 0x010                      | DMAC Software Last Transfer Flag Register                                                                            | DMAC_LAST   | Read-write | 0x0        |

| 0x014                      | Reserved                                                                                                             |             |            |            |

| 0x018                      | DMAC Error, Chained Buffer Transfer Completed Interrupt and Buffer Transfer Completed Interrupt Enable register.     | DMAC_EBCIER | Write-only | -          |

| 0x01C                      | DMAC Error, Chained Buffer Transfer Completed Interrupt and<br>Buffer Transfer Completed Interrupt Disable register. | DMAC_EBCIDR | Write-only | -          |

| 0x020                      | DMAC Error, Chained Buffer Transfer Completed Interrupt and Buffer transfer completed Mask Register.                 | DMAC_EBCIMR | Read-only  | 0x0        |

| 0x024                      | DMAC Error, Chained Buffer Transfer Completed Interrupt and Buffer transfer completed Status Register.               | DMAC_EBCISR | Read-only  | 0x0        |

| 0x028                      | DMAC Channel Handler Enable Register                                                                                 | DMAC_CHER   | Write-only | -          |

| 0x02C                      | DMAC Channel Handler Disable Register                                                                                | DMAC_CHDR   | Write-only | -          |

| 0x030                      | DMAC Channel Handler Status Register                                                                                 | DMAC_CHSR   | Read-only  | 0x00FF0000 |

| 0x034                      | Reserved                                                                                                             | -           | -          | -          |

| 0x038                      | Reserved                                                                                                             | -           | -          | -          |

| 0x03C+ch_num*(0x28)+(0x0)  | DMAC Channel Source Address Register                                                                                 | DMAC_SADDR  | Read-write | 0x0        |

| 0x03C+ch_num*(0x28)+(0x4)  | DMAC Channel Destination Address Register                                                                            | DMAC_DADDR  | Read-write | 0x0        |

| 0x03C+ch_num*(0x28)+(0x8)  | DMAC Channel Descriptor Address Register                                                                             | DMAC_DSCR   | Read-write | 0x0        |

| 0x03C+ch_num*(0x28)+(0xC)  | DMAC Channel Control A Register                                                                                      | DMAC_CTRLA  | Read-write | 0x0        |

| 0x03C+ch_num*(0x28)+(0x10) | DMAC Channel Control B Register                                                                                      | DMAC_CTRLB  | Read-write | 0x0        |

| 0x03C+ch_num*(0x28)+(0x14) | DMAC Channel Configuration Register                                                                                  | DMAC_CFG    | Read-write | 0x01000000 |

| 0x03C+ch_num*(0x28)+(0x18) | Reserved                                                                                                             | -           | -          | -          |

| 0x03C+ch_num*(0x28)+(0x1C) | Reserved                                                                                                             | -           | -          | -          |

| 0x03C+ch_num*(0x28)+(0x20) | Reserved                                                                                                             | -           | -          | -          |

| 0x03C+ch_num*(0x28)+(0x24) | Reserved                                                                                                             | -           | -          | -          |

| 0x1E4                      | DMAC Write Protect Mode Register                                                                                     | DMAC_WPMR   | Read-write | 0x0        |

| 0x1E8                      | DMAC Write Protect Status Register                                                                                   | DMAC_WPSR   | Read-only  | 0x0        |

| 0x01EC- 0x1FC              | Reserved                                                                                                             | -           | -          | _          |

## 31.7.9 PIO Controller Input Filter Status Register

## Name: PIO\_IFSR

Address: 0x400E0E28 (PIOA), 0x400E1028 (PIOB), 0x400E1228 (PIOC), 0x400E1428 (PIOD), 0x400E1628 (PIOE), 0x400E1828 (PIOF)

## Access: Read-only

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

| P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

| P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

# • P0-P31: Input Filer Status

0: The input glitch filter is disabled on the I/O line.

1: The input glitch filter is enabled on the I/O line.

## 31.7.21 PIO Pull Up Disable Register

## Name: PIO\_PUDR

Address: 0x400E0E60 (PIOA), 0x400E1060 (PIOB), 0x400E1260 (PIOC), 0x400E1460 (PIOD), 0x400E1660 (PIOE), 0x400E1860 (PIOF)

## Access: Write-only

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

| P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

| P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

This register can only be written if the WPEN bit is cleared in "PIO Write Protect Mode Register" .

## • P0-P31: Pull Up Disable.

0: No effect.

1: Disables the pull up resistor on the I/O line.

## 36.7.14 TC Block Mode Register

| Name:    | TC_BMR                                         |      |        |         |         |        |      |  |  |

|----------|------------------------------------------------|------|--------|---------|---------|--------|------|--|--|

| Address: | 0x400800C4 (0), 0x400840C4 (1), 0x400880C4 (2) |      |        |         |         |        |      |  |  |

| Access:  | Read/Write                                     |      |        |         |         |        |      |  |  |

| 31       | 30                                             | 29   | 28     | 27      | 26      | 25     | 24   |  |  |

| _        | -                                              | _    | -      | -       | -       | MAX    | FILT |  |  |

| 23       | 22                                             | 21   | 20     | 19      | 18      | 17     | 16   |  |  |

|          | MAX                                            | FILT | -      | _       | _       | IDXPHB | SWAP |  |  |

| 15       | 14                                             | 13   | 12     | 11      | 10      | 9      | 8    |  |  |

| INVIDX   | INVB                                           | INVA | EDGPHA | QDTRANS | SPEEDEN | POSEN  | QDEN |  |  |

| 7        | 6                                              | 5    | 4      | 3       | 2       | 1      | 0    |  |  |

| -        | -                                              | TC2X | XC2S   | TC1)    | XC1S    | TC0>   | KC0S |  |  |

This register can only be written if the WPEN bit is cleared in the TC Write Protection Mode Register.

## TC0XC0S: External Clock Signal 0 Selection

| Value | Name  | Description                    |  |  |  |

|-------|-------|--------------------------------|--|--|--|

| 0     | TCLK0 | Signal connected to XC0: TCLK0 |  |  |  |

| 1     | _     | Reserved                       |  |  |  |

| 2     | TIOA1 | Signal connected to XC0: TIOA1 |  |  |  |

| 3     | TIOA2 | Signal connected to XC0: TIOA2 |  |  |  |

## TC1XC1S: External Clock Signal 1 Selection

| Value | Name  | Description                    |  |  |  |

|-------|-------|--------------------------------|--|--|--|

| 0     | TCLK1 | Signal connected to XC1: TCLK1 |  |  |  |

| 1     | -     | Reserved                       |  |  |  |

| 2     | TIOA0 | Signal connected to XC1: TIOA0 |  |  |  |

| 3     | TIOA2 | Signal connected to XC1: TIOA2 |  |  |  |

## TC2XC2S: External Clock Signal 2 Selection

| Value | Name  | Description                    |  |  |

|-------|-------|--------------------------------|--|--|

| 0     | TCLK2 | Signal connected to XC2: TCLK2 |  |  |

| 1     | _     | Reserved                       |  |  |

| 2     | TIOA0 | Signal connected to XC2: TIOA0 |  |  |

| 3     | TIOA1 | Signal connected to XC2: TIOA1 |  |  |

## QDEN: Quadrature Decoder Enabled

0: Disabled.

1: Enables the QDEC (filter, edge detection and quadrature decoding).

Quadrature decoding (direction change) can be disabled using QDTRANS bit.

One of the POSEN or SPEEDEN bits must be also enabled.

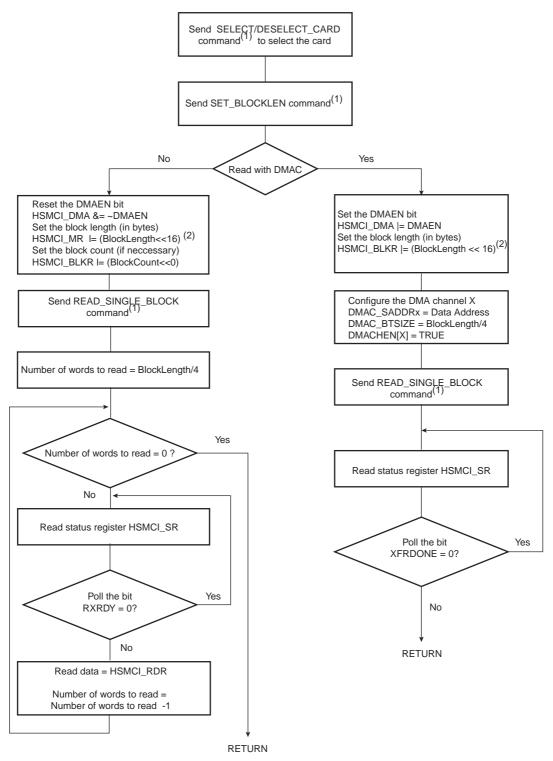

- Notes: 1. It is assumed that this command has been correctly sent (see Figure 37-8).

- 2. This field is also accessible in the HSMCI Block Register (HSMCI\_BLKR).

## 37.14.15 HSMCI Interrupt Mask Register

| Name:    | HSMCI_IMR  |         |          |         |           |                        |                        |

|----------|------------|---------|----------|---------|-----------|------------------------|------------------------|

| Address: | 0x4000004C |         |          |         |           |                        |                        |

| Access:  | Read-only  |         |          |         |           |                        |                        |

| 31       | 30         | 29      | 28       | 27      | 26        | 25                     | 24                     |

| UNRE     | OVRE       | ACKRCVE | ACKRCV   | XFRDONE | FIFOEMPTY | DMADONE                | BLKOVRE                |

| 23       | 22         | 21      | 20       | 19      | 18        | 17                     | 16                     |

| CSTOE    | DTOE       | DCRCE   | RTOE     | RENDE   | RCRCE     | RDIRE                  | RINDE                  |

| 15       | 14         | 13      | 12       | 11      | 10        | 9                      | 8                      |

| _        | -          | CSRCV   | SDIOWAIT | _       | _         | SDIO IRQ for<br>Slot B | SDIO IRQ for<br>Slot A |

| 7        | 6          | 5       | 4        | 3       | 2         | 1                      | 0                      |

| -        | -          | NOTBUSY | DTIP     | BLKE    | TXRDY     | RXRDY                  | CMDRDY                 |

• CMDRDY: Command Ready Interrupt Mask

- RXRDY: Receiver Ready Interrupt Mask

- TXRDY: Transmit Ready Interrupt Mask

- BLKE: Data Block Ended Interrupt Mask

- DTIP: Data Transfer in Progress Interrupt Mask

- NOTBUSY: Data Not Busy Interrupt Mask

- SDIOIRQA: SDIO Interrupt for Slot A Interrupt Mask

- SDIOIRQB: SDIO Interrupt for Slot B Interrupt Mask

- SDIOWAIT: SDIO Read Wait Operation Status Interrupt Mask

- CSRCV: Completion Signal Received Interrupt Mask

- RINDE: Response Index Error Interrupt Mask

- RDIRE: Response Direction Error Interrupt Mask

- RCRCE: Response CRC Error Interrupt Mask

- RENDE: Response End Bit Error Interrupt Mask

- RTOE: Response Time-out Error Interrupt Mask

- DCRCE: Data CRC Error Interrupt Mask

- DTOE: Data Time-out Error Interrupt Mask

- CSTOE: Completion Signal Time-out Error Interrupt Mask

- BLKOVRE: DMA Block Overrun Error Interrupt Mask

Atmel

## 38.7.24 PWM Fault Status Register

| Name:    | PWM_FSR    |    |    |    |    |    |    |  |

|----------|------------|----|----|----|----|----|----|--|

| Address: | 0x40094060 |    |    |    |    |    |    |  |

| Access:  | Read-only  |    |    |    |    |    |    |  |

| 31       | 30         | 29 | 28 | 27 | 26 | 25 | 24 |  |

|          |            |    | _  | -  |    |    |    |  |

| 23       | 22         | 21 | 20 | 19 | 18 | 17 | 16 |  |

|          |            |    | _  | -  |    |    |    |  |

| 15       | 14         | 13 | 12 | 11 | 10 | 9  | 8  |  |

|          | FS         |    |    |    |    |    |    |  |

| 7        | 6          | 5  | 4  | 3  | 2  | 1  | 0  |  |

|          |            |    | FI | V  |    |    |    |  |

#### • FIV: Fault Input Value (fault input bit varies from 0 to 5)

For each field bit y (fault input number):

0 = The current sampled value of the fault input y is 0 (after filtering if enabled).

1 = The current sampled value of the fault input y is 1 (after filtering if enabled).

#### • FS: Fault Status (fault input bit varies from 0 to 5)

For each field bit y (fault input number):

- 0 = The fault y is not currently active.

- 1 = The fault y is currently active.

## • CES: Counter Event Selection

The bit CES defines when the channel counter event occurs when the period is center aligned (flag CHIDx in the "PWM Interrupt Status Register 1" on page 1013).

CALG = 0 (Left Alignment):

0/1 = The channel counter event occurs at the end of the PWM period.

CALG = 1 (Center Alignment):

0 = The channel counter event occurs at the end of the PWM period.

1 = The channel counter event occurs at the end of the PWM period and at half the PWM period.

# • DTE: Dead-Time Generator Enable

0 = The dead-time generator is disabled.

1 = The dead-time generator is enabled.

# • DTHI: Dead-Time PWMHx Output Inverted

- 0 = The dead-time PWMHx output is not inverted.

- 1 = The dead-time PWMHx output is inverted.

# • DTLI: Dead-Time PWMLx Output Inverted

0 = The dead-time PWMLx output is not inverted.

1 = The dead-time PWMLx output is inverted.

## • PBK: Pipe Banks

| Value | Name   | Description      |

|-------|--------|------------------|

| 0     | 1 BANK | Single-bank pipe |

| 0     | _      | • • • •          |

| 1     | 2_BANK | Double-bank pipe |

| 2     | 3_BANK | Triple-bank pipe |

| 3     |        | Reserved         |

This field contains the number of banks for the pipe.

For control endpoints, a single-bank pipe (0b00) should be selected. This field is cleared upon sending a USB reset.

#### • ALLOC: Pipe Memory Allocate

Writing a one to this bit will allocate the pipe memory.

Writing a zero to this bit will free the pipe memory.

This bit is cleared when a USB Reset is requested.

Refer to the DPRAM Management chapter for more details.

## 40.9.9 CAN Error Counter Register

| Name:    | CAN_ECR         |              |    |    |    |    |    |

|----------|-----------------|--------------|----|----|----|----|----|

| Address: | 0x400B4020 (0), | 0x400B8020 ( | 1) |    |    |    |    |

| Access:  | Read-only       |              |    |    |    |    |    |

| 31       | 30              | 29           | 28 | 27 | 26 | 25 | 24 |

| -        | -               | _            | -  | -  | _  | _  | -  |

| 23       | 22              | 21           | 20 | 19 | 18 | 17 | 16 |

|          |                 |              | TI | EC |    |    |    |

| 15       | 14              | 13           | 12 | 11 | 10 | 9  | 8  |

| -        | -               | -            | _  | -  | -  | _  | -  |

| 7        | 6               | 5            | 4  | 3  | 2  | 1  | 0  |

|          |                 |              | R  | EC |    |    |    |

| 7        | 6               | 5            | •  |    | 2  | 1  | l  |

#### • REC: Receive Error Counter

When a receiver detects an error, REC will be increased by one, except when the detected error is a BIT ERROR while sending an ACTIVE ERROR FLAG or an OVERLOAD FLAG.

When a receiver detects a dominant bit as the first bit after sending an ERROR FLAG, REC is increased by 8.

When a receiver detects a BIT ERROR while sending an ACTIVE ERROR FLAG, REC is increased by 8.

Any node tolerates up to 7 consecutive dominant bits after sending an ACTIVE ERROR FLAG, PASSIVE ERROR FLAG or OVERLOAD FLAG. After detecting the 14th consecutive dominant bit (in case of an ACTIVE ERROR FLAG or an OVER-LOAD FLAG) or after detecting the 8th consecutive dominant bit following a PASSIVE ERROR FLAG, and after each sequence of additional eight consecutive dominant bits, each receiver increases its REC by 8.

After successful reception of a message, REC is decreased by 1 if it was between 1 and 127. If REC was 0, it stays 0, and if it was greater than 127, then it is set to a value between 119 and 127.

## • TEC: Transmit Error Counter

When a transmitter sends an ERROR FLAG, TEC is increased by 8 except when

- the transmitter is error passive and detects an ACKNOWLEDGMENT ERROR because of not detecting a dominant ACK and does not detect a dominant bit while sending its PASSIVE ERROR FLAG.

- the transmitter sends an ERROR FLAG because a STUFF ERROR occurred during arbitration and should have been recessive and has been sent as recessive but monitored as dominant.

When a transmitter detects a BIT ERROR while sending an ACTIVE ERROR FLAG or an OVERLOAD FLAG, the TEC will be increased by 8.

Any node tolerates up to 7 consecutive dominant bits after sending an ACTIVE ERROR FLAG, PASSIVE ERROR FLAG or OVERLOAD FLAG. After detecting the 14th consecutive dominant bit (in case of an ACTIVE ERROR FLAG or an OVER-LOAD FLAG) or after detecting the 8th consecutive dominant bit following a PASSIVE ERROR FLAG, and after each sequence of additional eight consecutive dominant bits every transmitter increases its TEC by 8.

After a successful transmission the TEC is decreased by 1 unless it was already 0.

## 40.9.11 CAN Abort Command Register

| Name:<br>Address: | CAN_ACR<br>0x400B4028 (0) | 0v400B8028 (   | 1)  |     |     |     |     |

|-------------------|---------------------------|----------------|-----|-----|-----|-----|-----|

|                   |                           | , 0740000020 ( | ,   |     |     |     |     |

| Access:           | Write-only                |                |     |     |     |     |     |

| 31                | 30                        | 29             | 28  | 27  | 26  | 25  | 24  |

| -                 | -                         | -              | -   | -   | -   | _   | -   |

| 23                | 22                        | 21             | 20  | 19  | 18  | 17  | 16  |

| -                 | -                         | -              | -   | -   | _   | -   | -   |

| 15                | 14                        | 13             | 12  | 11  | 10  | 9   | 8   |

| -                 | —                         | —              | -   | —   | _   | -   | -   |

| 7                 | 6                         | 5              | 4   | 3   | 2   | 1   | 0   |

| MB7               | MB6                       | MB5            | MB4 | MB3 | MB2 | MB1 | MB0 |

This register initializes several abort requests at the same time.

# • MBx: Abort Request for Mailbox x

| Mailbox Object Type    | Description                                                                              |

|------------------------|------------------------------------------------------------------------------------------|

| Receive                | No action                                                                                |

| Receive with overwrite | No action                                                                                |

| Transmit               | Cancels transfer request if the message has not been transmitted to the CAN transceiver. |

| Consumer               | Cancels the current transfer before the remote frame has been sent.                      |

| Producer               | Cancels the current transfer. The next remote frame is not serviced.                     |

It is possible to set MACR field (in the CAN\_MCRx register) for each mailbox.

## 43.7.20 ADC Write Protect Mode Register

| Name:    | ADC_WPMR   |    |    |     |    |    |      |

|----------|------------|----|----|-----|----|----|------|

| Address: | 0x400C00E4 |    |    |     |    |    |      |

| Access:  | Read-write |    |    |     |    |    |      |

| 31       | 30         | 29 | 28 | 27  | 26 | 25 | 24   |

|          |            |    | WP | KEY |    |    |      |

| 23       | 22         | 21 | 20 | 19  | 18 | 17 | 16   |

|          |            |    | WP | KEY |    |    |      |

| 15       | 14         | 13 | 12 | 11  | 10 | 9  | 8    |

|          |            |    | WP | KEY |    |    |      |

| 7        | 6          | 5  | 4  | 3   | 2  | 1  | 0    |

| -        | -          | —  | —  | _   | —  | —  | WPEN |

## • WPEN: Write Protect Enable

0 = Disables the Write Protect if WPKEY corresponds to 0x414443 ("ADC" in ASCII).

1 = Enables the Write Protect if WPKEY corresponds to 0x414443 ("ADC" in ASCII).

Protects the registers:

"ADC Mode Register" on page 1333

"ADC Channel Sequence 1 Register" on page 1336

"ADC Channel Sequence 2 Register" on page 1337

"ADC Channel Enable Register" on page 1338

"ADC Channel Disable Register" on page 1339

"ADC Extended Mode Register" on page 1347

"ADC Compare Window Register" on page 1348

"ADC Channel Gain Register" on page 1349

"ADC Channel Offset Register" on page 1350

"ADC Analog Control Register" on page 1352

## • WPKEY: Write Protect KEY

Should be written at value 0x414443 ("ADC" in ASCII). Writing any other value in this field aborts the write operation of the WPEN bit. Always reads as 0.

Atmel

#### Table 50-1. SAM3X/SAM3A Datasheet Rev. 11057C Revision History (Continued)

| ction 45. "Electrical Characteristics"<br>dated and harmonized parameter symbols<br>ble 45-1 Absolute Maximum Ratings*:<br>dded "(except VBUS)" to description "Voltage on Input Pins with Respect to Ground"<br>dded "Voltage on VBUS Pin with Respect to Ground"<br>ble 45-2 DC Characteristics: removed parameter "Input Capacitance"<br>ble 45-3 1.8V Voltage Regulator Characteristics: updated conditions for CD <sub>IN</sub> and CD <sub>OUT</sub><br>ble 45-4 Core Power Supply Brownout Detector Characteristics: added parameter "Reset Period"<br>ded Table 45-6 "Threshold Selection"<br>ble 45-7 Backup Power Supply Zero-Power-on Reset Characteristics: modified parameter name "Reset Time-out<br>riod" to "Reset Period" |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ble 45-1 Absolute Maximum Ratings*:<br>dded "(except VBUS)" to description "Voltage on Input Pins with Respect to Ground"<br>dded "Voltage on VBUS Pin with Respect to Ground"<br>ble 45-2 DC Characteristics: removed parameter "Input Capacitance"<br>ble 45-3 1.8V Voltage Regulator Characteristics: updated conditions for CD <sub>IN</sub> and CD <sub>OUT</sub><br>ble 45-4 Core Power Supply Brownout Detector Characteristics: added parameter "Reset Period"<br>ded Table 45-6 "Threshold Selection"<br>ble 45-7 Backup Power Supply Zero-Power-on Reset Characteristics: modified parameter name "Reset Time-out                                                                                                                |

| dded "(except VBUS)" to description "Voltage on Input Pins with Respect to Ground"<br>dded "Voltage on VBUS Pin with Respect to Ground"<br>ble 45-2 DC Characteristics: removed parameter "Input Capacitance"<br>ble 45-3 1.8V Voltage Regulator Characteristics: updated conditions for CD <sub>IN</sub> and CD <sub>OUT</sub><br>ble 45-4 Core Power Supply Brownout Detector Characteristics: added parameter "Reset Period"<br>ded Table 45-6 "Threshold Selection"<br>ble 45-7 Backup Power Supply Zero-Power-on Reset Characteristics: modified parameter name "Reset Time-out                                                                                                                                                       |

| dded "Voltage on VBUS Pin with Respect to Ground"<br>ble 45-2 DC Characteristics: removed parameter "Input Capacitance"<br>ble 45-3 1.8V Voltage Regulator Characteristics: updated condtions for CD <sub>IN</sub> and CD <sub>OUT</sub><br>ble 45-4 Core Power Supply Brownout Detector Characteristics: added parameter "Reset Period"<br>ded Table 45-6 "Threshold Selection"<br>ble 45-7 Backup Power Supply Zero-Power-on Reset Characteristics: modified parameter name "Reset Time-out                                                                                                                                                                                                                                              |

| ble 45-2 DC Characteristics: removed parameter "Input Capacitance"<br>ble 45-3 1.8V Voltage Regulator Characteristics: updated conditions for CD <sub>IN</sub> and CD <sub>OUT</sub><br>ble 45-4 Core Power Supply Brownout Detector Characteristics: added parameter "Reset Period"<br>ded Table 45-6 "Threshold Selection"<br>ble 45-7 Backup Power Supply Zero-Power-on Reset Characteristics: modified parameter name "Reset Time-out                                                                                                                                                                                                                                                                                                  |

| ble 45-3 1.8V Voltage Regulator Characteristics: updated condtions for CD <sub>IN</sub> and CD <sub>OUT</sub><br>ble 45-4 Core Power Supply Brownout Detector Characteristics: added parameter "Reset Period"<br>ded Table 45-6 "Threshold Selection"<br>ble 45-7 Backup Power Supply Zero-Power-on Reset Characteristics: modified parameter name "Reset Time-out                                                                                                                                                                                                                                                                                                                                                                         |

| ble 45-4 Core Power Supply Brownout Detector Characteristics: added parameter "Reset Period"<br>ded Table 45-6 "Threshold Selection"<br>ble 45-7 Backup Power Supply Zero-Power-on Reset Characteristics: modified parameter name "Reset Time-out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ded Table 45-6 "Threshold Selection"<br>ble 45-7 Backup Power Supply Zero-Power-on Reset Characteristics: modified parameter name "Reset Time-out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ble 45-7 Backup Power Supply Zero-Power-on Reset Characteristics: modified parameter name "Reset Time-out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ction 45.3.1 "Backup Mode Current Consumption": deleted instances of "Configuration A"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ction 45.4.3 "32.768 kHz Crystal Oscillator Characteristics": added parameter "Allowed Crystal Capacitance Load"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ble 45-17 "32.768 kHz Crystal Oscillator Characteristics": updated conditions for parameters "Startup Time" and<br>urrent Consumption"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ble 45-19 "XIN32 Clock Electrical Characteristics (In Bypass Mode)": in table footnote, corrected "32768 kHz" to<br>2.768 kHz"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| dated Figure 45-13 "XIN32 Clock Timing"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ble 45-20 "3 to 20 MHz Crystal Oscillator Characteristics": added parameter "Allowed Crystal Capacitance Load";<br>eted all footnotes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| dated Figure 45-15 "XIN Clock Timing"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ction 45.4.9.1 "Choosing a Crystal": under 'Load Capacitance', changed "This is the equivalent capacitor" to "C <sub>crystal</sub> he equivalent capacitor"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ction 45.4.9.2 "Printed Circuit Board (PCB)": deleted sentence "A board design example is given on Atmel's website he MCU Technical Center Section."                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ble 45-24 "PLLA Characteristics":                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| pdated Input Frequency values (was 8 MHz min/16 MHz max; is 1 MHz min/40 MHz max)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| pdated Output Frequency values (was 96 MHz min/192 MHz max; is 80 MHz min/240 MHz max)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ble 45-25 "UPLL Characteristics for USB High Speed Device Port": added max value for Current Consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ble 45-30 "Channel Conversion Time and ADC Clock": changed max value of ADC Clock Frequency from 20 MHz to MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ction 45.6 "USB On-the-Go High Speed Port": removed section 46.6.5 "USB High Speed Design Guidelines"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ded Section 45.6.2.2 "VBUS Pin Characteristics"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ction 45.7.1 "Static Performance Characteristics": updated conditions at beginning of section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| erted new heading Section 45.7.2 "Dynamic Performance Characteristics" and updated content                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ure 45-18 "Simplified Acquisition Path": inserted correct diagram (was previously graph of offset and gain<br>initions)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ction 45.8 "Temperature Sensor": specified instances of "27°C" as ambient temperature (T <sub>A</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ded Table 45-44 "Analog Outputs"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ure 45-21 "SPI Slave Mode with (CPOL = 0 and NCPHA = 1) or (CPOL = 1 and NCPHA = 0)": added 'MOSI'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ction 45.10.3.1 "Maximum SPI Frequency": updated description under "Master Write Mode" and "Master Read de"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ble 45-49 "SSC Timings": deleted footnote "Timings SSC4 and SSC7 dependadded to timings"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ction 45.10.6 "SMC Timings": updated conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

# Atmel Enabling Unlimited Possibilities

Т

Atmel Corporation 1600 Technology Drive, San Jose, CA 95110 USA T: (+1)(408) 441.0311 F: (+1)(408) 436.4200

www.atmel.com

© 2015 Atmel Corporation. / Rev.: Atmel-11057C-ATARM-SAM3X-SAM3A-Datasheet\_23-Mar-15.

Atmel<sup>®</sup>, Atmel logo and combinations thereof, Enabling Unlimited Possibilities<sup>®</sup>, and others are registered trademarks or trademarks of Atmel Corporation in U.S. and other countries. ARM<sup>®</sup>, ARM Connected<sup>®</sup> logo, and others are the registered trademarks or trademarks of ARM Ltd. Windows<sup>®</sup> is a registered trademark of Microsoft Corporation in U.S. and/or other countries. Other terms and product names may be trademarks of others.

DISCLAIMER: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL MEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LASS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

SAFETY-CRITICAL, MILITARY, AND AUTOMOTIVE APPLICATIONS DISCLAIMER: Atmel products are not designed for and will not be used in connection with any applications where the failure of such products would reasonably be expected to result in significant personal injury or death ("Safety-Critical Applications") without an Atmel officer's specific written consent. Safety-Critical Applications include, without limitation, life support devices and systems, equipment or systems for the operation of nuclear facilities and weapons systems. Atmel products are not designed nor intended for use in military or aerospace applications or environments unless specifically designated by Atmel as military-grade. Atmel products are not designed nor intended for use in automotive applications unless specifically designated by Atmel as automotive-grade.