Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                            |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 180MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                     |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 145                                                                        |

| Program Memory Size        | 256KB (256K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 16K x 8                                                                    |

| RAM Size                   | 136K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                               |

| Data Converters            | A/D 12x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 180-TFBGA                                                                  |

| Supplier Device Package    | 180-TFBGA (12x12)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc54605j256et180e |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

LPC546xx

| Symbol             | 100-pin, TFBGA | 180-pin, TFBGA | 208-pin, LQFP | 100-pin, LQFP |            | Reset state [1] | Type       | Description                                                                                                                                                     |

|--------------------|----------------|----------------|---------------|---------------|------------|-----------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIO0_9             | E10            | G12            | 136           | 65            | [2]        | PU              | I/O        | <b>PIO0_9</b> — General-purpose digital input/output pin.                                                                                                       |

|                    |                |                |               |               |            |                 | I/O        | FC3_SSEL2 — Flexcomm 3: SPI slave select 2.                                                                                                                     |

|                    |                |                |               |               |            |                 | 0          | <b>SD_POW_EN</b> — SD/MMC card power enable.                                                                                                                    |

|                    |                |                |               |               |            |                 | I/O        | <b>FC5_TXD_SCL_MISO</b> — Flexcomm 5: USART transmitter, I2C clock, SPI master-in/slave-out data.                                                               |

|                    |                |                |               |               |            |                 |            | R — Reserved.                                                                                                                                                   |

|                    |                |                |               |               |            |                 | I/O        | SCI1_IO — SmartCard Interface 1 data I/O.                                                                                                                       |

|                    |                |                |               |               |            |                 | I/O        | EMC_D[7] — External Memory interface data [7].                                                                                                                  |

| PIO0_10/<br>ADC0_0 | J1             | P2             | 50            | 23            | [4]        | PU              | I/O;<br>AI | <b>PIO0_10/ADC0_0</b> — General-purpose digital input/output pin.<br>ADC input channel 0 if the DIGIMODE bit is set to 0 in the<br>IOCON register for this pin. |

|                    |                |                |               |               |            |                 | I/O        | FC6_SCK — Flexcomm 6: USART, SPI, or I2S clock.                                                                                                                 |

|                    |                |                |               |               |            |                 | I          | CT2_CAP2 — Capture input 2 to Timer 2.                                                                                                                          |

|                    |                |                |               |               |            |                 | 0          | CT2_MAT0 — Match output 0 from Timer 2.                                                                                                                         |

|                    |                |                |               |               |            |                 | I/O        | <b>FC1_TXD_SCL_MISO</b> — Flexcomm 1: USART transmitter, I2C clock, SPI master-in/slave-out data.                                                               |

|                    |                |                |               |               |            |                 |            | R — Reserved.                                                                                                                                                   |

|                    |                |                |               |               |            |                 | 0          | SWO — Serial Wire Debug trace output.                                                                                                                           |

| PIO0_11/<br>ADC0_1 | K1             | L3             | 51            | 24            | <u>[4]</u> | PU              | I/O;<br>AI | <b>PIO0_11/ADC0_1</b> — General-purpose digital input/output pin.<br>ADC input channel 1 if the DIGIMODE bit is set to 0 in the<br>IOCON register for this pin. |

|                    |                |                |               |               |            |                 | I/O        | FC6_RXD_SDA_MOSI_DATA — Flexcomm 6: USART receiver, I2C data I/O, SPI master-out/slave-in data, I2S data I/O.                                                   |

|                    |                |                |               |               |            |                 | 0          | CT2_MAT2 — Match output 2 from Timer 2.                                                                                                                         |

|                    |                |                |               |               |            |                 | I          | <b>FREQME_GPIO_CLK_A</b> — Frequency Measure pin clock input A.                                                                                                 |

|                    |                |                |               |               |            |                 |            | R — Reserved.                                                                                                                                                   |

|                    |                |                |               |               |            |                 |            | R — Reserved.                                                                                                                                                   |

|                    |                |                |               |               |            |                 | I          | <b>SWCLK</b> — Serial Wire Debug clock. This is the default function after booting.                                                                             |

LPC546xx

|         | Fin desc | -              |                |               |               |         |                 |          | Description                                                                                                                     |

|---------|----------|----------------|----------------|---------------|---------------|---------|-----------------|----------|---------------------------------------------------------------------------------------------------------------------------------|

| Symbol  |          | 100-pin, TFBGA | 180-pin, TFBGA | 208-pin, LQFP | 100-pin, LQFP |         | Reset state [1] | Type     | Description                                                                                                                     |

| PIO0_18 |          | C9             | C14            | 150           | 72            | [2]     | PU              | I/O      | PIO0_18 — General-purpose digital input/output pin.                                                                             |

|         |          |                |                |               |               |         |                 | I/O      | FC4_CTS_SDA_SSEL0 — Flexcomm 4: USART                                                                                           |

|         |          |                |                |               |               |         |                 |          | clear-to-send, I2C data I/O, SPI Slave Select 0.                                                                                |

|         |          |                |                |               |               |         |                 | י<br>0   | SD_WR_PRT — SD/MMC write protect.<br>CT1_MAT0 — Match output 0 from Timer 1.                                                    |

|         |          |                |                |               |               |         |                 | 0        | SCT0_OUT1 — SCTimer/PWM output 1.                                                                                               |

|         |          |                |                |               |               |         |                 | 0        | SCI0_OUT — SCIIIIe//FWW output 1.<br>SCI1_SCLK — SmartCard Interface 1 clock.                                                   |

|         |          |                |                |               |               |         |                 | 0        | <b>EMC_A[0]</b> — External memory interface address 0.                                                                          |

| PIO0_19 |          | C5             | C6             | 193           | 91            | [2]     | PU              | 0<br>1/0 | PIO0_19 — General-purpose digital input/output pin.                                                                             |

| FIO0_19 |          | 05             | 0              | 195           | 91            | <u></u> | FU              | 1/O      | FC4_RTS_SCL_SSEL1 — Flexcomm 4: USART                                                                                           |

|         |          |                |                |               |               |         |                 | 1/0      | request-to-send, I2C clock, SPI slave select 1.                                                                                 |

|         |          |                |                |               |               |         |                 | I        | <b>UTICK_CAP0</b> — Micro-tick timer capture input 0.                                                                           |

|         |          |                |                |               |               |         |                 | 0        | CT0_MAT2 — Match output 2 from Timer 0.                                                                                         |

|         |          |                |                |               |               |         |                 | 0        | SCT0_OUT2 — SCTimer/PWM output 2.                                                                                               |

|         |          |                |                |               |               |         |                 |          | R — Reserved.                                                                                                                   |

|         |          |                |                |               |               |         |                 | 0        | <b>EMC_A[1]</b> — External memory interface address 1.                                                                          |

|         |          |                |                |               |               |         |                 | I/O      | <b>FC7_TXD_SCL_MISO_WS</b> — Flexcomm 7: USART transmitter, I2C clock, SPI master-in/slave-out data I/O, I2S word-select/frame. |

| PIO0_20 |          | C8             | D13            | 153           | 74            | [2]     | PU              | I/O      | PIO0_20 — General-purpose digital input/output pin.                                                                             |

|         |          |                |                |               |               |         |                 | I/O      | FC3_CTS_SDA_SSEL0 — Flexcomm 3: USART clear-to-send, I2C data I/O, SPI Slave Select 0.                                          |

|         |          |                |                |               |               |         |                 | 0        | CT1_MAT1 — Match output 1 from Timer 1.                                                                                         |

|         |          |                |                |               |               |         |                 | I        | CT3_CAP3 — Capture input 3 to Timer 3.                                                                                          |

|         |          |                |                |               |               |         |                 | I        | SCT0_GPI2 — Pin input 2 to SCTimer/PWM.                                                                                         |

|         |          |                |                |               |               |         |                 | I/O      | SCI0_IO — SmartCard Interface 0 data I/O.                                                                                       |

|         |          |                |                |               |               |         |                 | 0        | EMC_A[2] — External memory interface address 2.                                                                                 |

|         |          |                |                |               |               |         |                 | I/O      | FC7_RXD_SDA_MOSI_DATA — Flexcomm 7: USART receiver, I2C data I/O, SPI master-out/slave-in data, I2S data I/O.                   |

| PIO0_21 |          | B9             | C13            | 158           | 77            | [2]     | PU              | I/O      | PIO0_21 — General-purpose digital input/output pin.                                                                             |

|         |          |                |                |               |               |         |                 | I/O      | FC3_RTS_SCL_SSEL1 — Flexcomm 3: USART request-to-send, I2C clock, SPI slave select 1.                                           |

|         |          |                |                |               |               |         |                 | I        | UTICK_CAP3 — Micro-tick timer capture input 3.                                                                                  |

|         |          |                |                |               |               |         |                 | 0        | CT3_MAT3 — Match output 3 from Timer 3.                                                                                         |

|         |          |                |                |               |               |         |                 | I        | SCT0_GPI3 — Pin input 3 to SCTimer/PWM.                                                                                         |

|         |          |                |                |               |               |         |                 | 0        | SCI0_SCLK — SmartCard Interface 0 clock.                                                                                        |

|         |          |                |                |               |               |         |                 | 0        | EMC_A[3] — External memory interface address 3.                                                                                 |

|         |          |                |                |               |               |         |                 | I/O      | FC7_SCK — Flexcomm 7: USART, SPI, or I2S clock.                                                                                 |

LPC546xx

| Symbol  | 100-pin, TFBGA | 180-pin, TFBGA | 208-pin, LQFP | 100-pin, LQFP |            | Reset state [1] | Type | Description                                                                                                                     |

|---------|----------------|----------------|---------------|---------------|------------|-----------------|------|---------------------------------------------------------------------------------------------------------------------------------|

| PIO2_19 | -              | P12            | 93            | -             | <u>[2]</u> | PU              | 1/0  | PIO2_19 — General-purpose digital input/output pin.                                                                             |

|         |                |                |               |               |            |                 | 0    | LCD_VD[1] — LCD Data [1].                                                                                                       |

|         |                |                |               |               |            |                 | I/O  | FC3_TXD_SCL_MISO — Flexcomm 3: USART transmitter,<br>I2C clock, SPI master-in/slave-out data.                                   |

|         |                |                |               |               |            |                 | I/O  | FC7_RXD_SDA_MOSI_DATA — Flexcomm 7: USART receiver, I2C data I/O, SPI master-out/slave-in data, I2S data I/O.                   |

|         |                |                |               |               |            |                 | 0    | CT3_MAT1 — Match output 1 from Timer 3.                                                                                         |

| PIO2_20 | -              | P13            | 95            | -             | [2]        | PU              | I/O  | PIO2_20 — General-purpose digital input/output pin.                                                                             |

|         |                |                |               |               |            |                 | 0    | LCD_VD[2] — LCD Data [2].                                                                                                       |

|         |                |                |               |               |            |                 | I/O  | FC3_RTS_SCL_SSEL1 — Flexcomm 3: USART request-to-send, I2C clock, SPI slave select 1.                                           |

|         |                |                |               |               |            |                 | I/O  | <b>FC7_TXD_SCL_MISO_WS</b> — Flexcomm 7: USART transmitter, I2C clock, SPI master-in/slave-out data I/O, I2S word-select/frame. |

|         |                |                |               |               |            |                 | 0    | CT3_MAT2 — Match output 2 from Timer 3.                                                                                         |

|         |                |                |               |               |            |                 | I    | CT4_CAP0 — Capture input 4 to Timer 0.                                                                                          |

| PIO2_21 | -              | L10            | 99            | -             | [2]        | PU              | I/O  | PIO2_21 — General-purpose digital input/output pin.                                                                             |

|         |                |                |               |               |            |                 | 0    | LCD_VD[3] — LCD Data [3].                                                                                                       |

|         |                |                |               |               |            |                 | I/O  | FC3_CTS_SDA_SSEL0 — Flexcomm 3: USART clear-to-send, I2C data I/O, SPI Slave Select 0.                                          |

|         |                |                |               |               |            |                 | I/O  | <b>MCLK</b> — MCLK input or output for I2S and/or digital microphone.                                                           |

|         |                |                |               |               |            |                 | 0    | CT3_MAT3 — Match output 3 from Timer 3.                                                                                         |

| PIO2_22 | -              | K10            | 113           | -             | [2]        | PU              | I/O  | PIO2_22 — General-purpose digital input/output pin.                                                                             |

|         |                |                |               |               |            |                 | 0    | LCD_VD[4] — LCD Data [4].                                                                                                       |

|         |                |                |               |               |            |                 | 0    | SCT0_OUT7 — SCTimer/PWM output 7.                                                                                               |

|         |                |                |               |               |            |                 |      | R — Reserved.                                                                                                                   |

|         |                |                |               |               |            |                 | I    | CT2_CAP0 — Capture input 0 to Timer 2.                                                                                          |

| PIO2_23 | -              | M14            | 115           | -             | [2]        | PU              | I/O  | PIO2_23 — General-purpose digital input/output pin.                                                                             |

|         |                |                |               |               |            |                 | 0    | LCD_VD[5] — LCD Data [5].                                                                                                       |

|         |                |                |               |               |            |                 | 0    | SCT0_OUT8 — SCTimer/PWM output 8.                                                                                               |

| PIO2_24 | -              | K14            | 118           | -             | [2]        | PU              | I/O  | PIO2_24 — General-purpose digital input/output pin.                                                                             |

|         |                |                |               |               |            |                 | 0    | LCD_VD[6] — LCD Data [6].                                                                                                       |

|         |                |                |               |               |            |                 | 0    | SCT0_OUT9 — SCTimer/PWM output 9.                                                                                               |

| PIO2_25 | -              | J11            | 121           | -             | [2][8]     | PU              | I/O  | PIO2_25 — General-purpose digital input/output pin.                                                                             |

|         |                |                |               |               |            |                 | 0    | LCD_VD[7] — LCD Data [7].                                                                                                       |

|         |                |                |               |               |            |                 | I    | USB0_VBUS — Monitors the presence of USB0 bus power.                                                                            |

LPC546xx

| Symbol  | 100-pin, TFBGA | 180-pin, TFBGA | 208-pin, LQFP | 100-pin, LQFP |     | Reset state [1] | Type | Description                                                                                |

|---------|----------------|----------------|---------------|---------------|-----|-----------------|------|--------------------------------------------------------------------------------------------|

| PIO2_26 | -              | H11            | 124           | -             | [2] | PU              | 1/O  | PIO2_26 — General-purpose digital input/output pin.                                        |

|         |                |                |               |               |     |                 | 0    | LCD_VD[8] — LCD Data [8].<br>R — Reserved.                                                 |

|         |                |                |               |               |     |                 | I/O  | FC3_SCK — Flexcomm 3: USART or SPI clock.                                                  |

|         |                |                |               |               |     |                 | "O   | CT2_CAP1 — Capture input 1 to Timer 2.                                                     |

| PIO2_27 | _              | H14            | 130           | _             | [2] | PU              | I/O  | <b>PIO2_27</b> — General-purpose digital input/output pin.                                 |

|         |                |                |               |               |     |                 | 0    | LCD_VD[9] — LCD Data [9].                                                                  |

|         |                |                |               |               |     |                 | 1/O  | FC9_SCK — Flexcomm 9: USART or SPI clock.                                                  |

|         |                |                |               |               |     |                 | I/O  | FC3_SSEL2 — Flexcomm 3: SPI slave select 2.                                                |

| PIO2_28 | -              | G13            | 134           | -             | [2] | PU              | I/O  | PIO2_28 — General-purpose digital input/output pin.                                        |

| _       |                |                |               |               |     |                 | 0    | LCD_VD[10]) — LCD Data [10].                                                               |

|         |                |                |               |               |     |                 | I/O  | FC7_CTS_SDA_SSEL0 — Flexcomm 7: USART clear-to-send, I2C data I/O, SPI Slave Select 0.     |

|         |                |                |               |               |     |                 |      | R — Reserved                                                                               |

|         |                |                |               |               |     |                 | I    | CT2_CAP2 — Capture input 2 to Timer 2.                                                     |

| PIO2_29 | -              | G11            | 137           | -             | [2] | PU              | I/O  | PIO2_29 — General-purpose digital input/output pin.                                        |

|         |                |                |               |               |     |                 | 0    | LCD_VD[11] — LCD Data [11].                                                                |

|         |                |                |               |               |     |                 | I/O  | FC7_RTS_SCL_SSEL1 — Flexcomm 7: USART request-to-send, I2C clock, SPI slave select 1.      |

|         |                |                |               |               |     |                 | I/O  | FC8_TXD_SCL_MISO — Flexcomm 8: USART transmitter, I2C clock, SPI master-in/slave-out data. |

|         |                |                |               |               |     |                 | I    | CT2_CAP3 — Capture 3 input to Timer 2.                                                     |

|         |                |                |               |               |     |                 | 0    | <b>CLKOUT</b> — Output of the CLKOUT function.                                             |

| PIO2_30 | -              | F12            | 143           | -             | [2] | PU              | I/O  | PIO2_30 — General-purpose digital input/output pin.                                        |

|         |                |                |               |               |     |                 | 0    | LCD_VD[12] — LCD Data [12].                                                                |

|         |                |                |               |               |     |                 |      | R — Reserved.                                                                              |

|         |                |                |               |               |     |                 |      | R — Reserved.                                                                              |

|         |                |                |               |               |     |                 | 0    | CT2_MAT2 — Match output 2 from Timer 2.                                                    |

| PIO2_31 | -              | D14            | 149           | -             | [2] | PU              | I/O  | PIO2_31 — General-purpose digital input/output pin.                                        |

|         |                |                |               |               | [0] |                 | 0    | LCD_VD[13] — LCD Data [13].                                                                |

| PIO3_0  | -              | D12            | 155           | -             | [2] | PU              | I/O  | PIO3_0 — General-purpose digital input/output pin.                                         |

|         |                |                |               |               |     |                 | 0    | LCD_VD[14] — LCD Data [14].                                                                |

|         |                |                |               |               |     |                 | 0    | <b>PDM0_CLK</b> — Clock for PDM interface 0, for digital microphone.                       |

|         |                |                |               |               |     |                 |      | R — Reserved.                                                                              |

|         |                |                |               |               |     |                 | 0    | CT1_MAT0 — Match output 0 from Timer 1.                                                    |

LPC546xx

| (reserved)                        | 0xFFFF FFFF      |                      |                               | 0.4040 5555                |

|-----------------------------------|------------------|----------------------|-------------------------------|----------------------------|

| private peripheral bus            | 0xE010 0000      | ſ                    | EPROM (16 kB)                 | 0x4010 BFFF                |

| (EMC)                             | 0×E000 0000      |                      | (reserved)                    | 0x4010 8000                |

| (reserved)                        | 0x8000 0000      |                      | USB SRAM (8 kB)               | 0x4010 2000<br>0x4010 0000 |

| . , ,                             | 0x4400 0000      |                      | (reserved)                    | 0x4010 0000<br>0x400A 5000 |

| peripheral<br>bit-band addressing |                  |                      | (reserved)                    | 0x400A 3000                |

| (reserved)                        | 0x4200 0000      |                      | HS USB host registers         | 0x400A 3000                |

| AHB                               | 0x400C 0000      |                      | FS USB host registers         | 0x400A 2000                |

| peripheral                        | 4                |                      | SHA registers                 | 0x400A 1000                |

| (reserved)                        | 0x4008 0000      |                      | ADC                           | 0x400A 0000                |

| Asynchronous                      | 0x4006 0000      |                      | CAN 1                         | 0x4009 E000                |

| APB peripherals                   | •<br>0x4004 0000 |                      | CAN 0                         | 0x4009 D000                |

| APB peripherals on                | 0,4004 0000      | see APB { memory     | ISP-AP interface              | 0x4009 C000                |

| APB bridge 1                      | 0x4002 0000      | map figure           | SDIO                          | 0x4009 B000                |

| APB peripherals on                | 4                |                      | Flexcomm 9                    | 0x4009 A000                |

| APB bridge 0                      | 0x4000 0000      |                      | Flexcomm 8                    | 0x4009 9000                |

| (reserved)                        | 0x2400 0000      |                      | Flexcomm 7                    | 0x4009 8000                |

| SRAM bit-band                     |                  |                      | Flexcomm 6                    | 0x4009 7000                |

| addressing                        | 0x2200 0000      |                      | Flexcomm 5                    | 0x4009 6000                |

| (reserved)                        | 0x2002 0000      |                      | CRC engine                    | 0x4009 5000                |

| SRAM2                             |                  |                      | HS USB device                 | 0x4009 4000                |

| (up to 32 kB)                     | 0x2002 0000      |                      | Ethernet                      | 0x4009 2000                |

| SRAM1<br>(up to 64 kB)            |                  |                      | (reserved)<br>D-Mic interface | 0x4009 1000                |

| SRAMO                             | 0x2001 0000      |                      | High Speed GPIO               | 0x4009 0000                |

| (up to 64 kB)                     |                  |                      | (reserved)                    | 0x4008 C000                |

| (reserved)                        | 0x2000 0000      |                      | Flexcomm 4                    | 0x4008 B000                |

| SPIFI Flash Interface             | 0x1800 0000      |                      | Flexcomm 3                    | 0x4008 A000                |

| memory mapped space               | 0x1000 0000      |                      | Flexcomm 2                    | 0x4008 9000                |

| (reserved)                        |                  |                      | Flexcomm 1                    | 0x4008 8000                |

| SRAMX                             | 0x0401 0000      |                      | Flexcomm 0                    | 0x4008 7000                |

| (32 kB)                           | 0x0400 0000      |                      | SC Timer / PWM                | 0x4008 6000                |

| (reserved)                        |                  |                      | FS USB device registers       | 0x4008 5000                |

| Boot ROM                          | 0x0300 0000      |                      | LCD registers                 | 0x4008 4000                |

| (reserved)                        | 0x0300 0000      |                      | DMA registers                 | 0x4008 3000                |

| Flash memory                      | 0x0008 0000      |                      | EMC registers                 | 0x4008 2000                |

| (up to 512 kB)                    |                  |                      | SPIFI registers               | 0x4008 1000                |

| <u> </u>                          | → 0x0000 0000    |                      |                               | 0x4008 0000                |

| L                                 | ]                |                      |                               |                            |

| active inte                       |                  | 000 00C0<br>000 0000 |                               | aaa-029365                 |

|                                   |                  |                      |                               | aaa-029300                 |

| The private peripheral be         | us includes CPU  | peripherals such     | n as the NVIC, SysTick, an    | d the core contro          |

# 7.19.6 Repetitive Interrupt Timer (RIT)

The repetitive interrupt timer provides a free-running 48-bit counter which is compared to a selectable value, generating an interrupt when a match occurs. Any bits of the timer/compare can be masked such that they do not contribute to the match detection. The repetitive interrupt timer can be used to create an interrupt that repeats at predetermined intervals.

## 7.19.6.1 Features

- 48-bit counter running from the main clock. Counter can be free-running or can be reset when an RIT interrupt is generated.

- 48-bit compare value.

- 48-bit compare mask. An interrupt is generated when the counter value equals the compare value, after masking. This allows for combinations not possible with a simple compare.

- Can be used for ETM debug time stamping.

# 7.20 12-bit Analog-to-Digital Converter (ADC)

The ADC supports a resolution of 12-bit and fast conversion rates of up to 5 Msamples/s. Sequences of analog-to-digital conversions can be triggered by multiple sources. Possible trigger sources are the SCTimer/PWM, external pins, and the ARM TXEV interrupt.

The ADC supports a variable clocking scheme with clocking synchronous to the system clock or independent, asynchronous clocking for high-speed conversions

The ADC includes a hardware threshold compare function with zero-crossing detection. The threshold crossing interrupt is connected internally to the SCTimer/PWM inputs for tight timing control between the ADC and the SCTimer/PWM.

# 7.20.1 Features

- 12-bit successive approximation analog to digital converter.

- Input multiplexing among up to 12 pins.

- Two configurable conversion sequences with independent triggers.

- Optional automatic high/low threshold comparison and "zero crossing" detection.

- Measurement range VREFN to VREFP (typically 3 V; not to exceed VDDA voltage level).

- 12-bit conversion rate of 5.0 Msamples/s. Options for reduced resolution at higher conversion rates.

- Burst conversion mode for single or multiple inputs.

- Synchronous or asynchronous operation. Asynchronous operation maximizes flexibility in choosing the ADC clock frequency, Synchronous mode minimizes trigger latency and can eliminate uncertainty and jitter in response to a trigger.

| Table 20. | Typical AHB/APB peripheral power consumption [3][4][5] |  |

|-----------|--------------------------------------------------------|--|

|-----------|--------------------------------------------------------|--|

$T_{amb} = 25 \ ^{\circ}C, \ V_{DD} = 3.3 \ V;$

| Peripheral           | I <sub>DD</sub> in uA/MHz                | I <sub>DD</sub> in uA/MHz                              | I <sub>DD</sub> in uA/MHz                               | I <sub>DD</sub> in uA/MHz                                | I <sub>DD</sub> in uA/MHz                                |

|----------------------|------------------------------------------|--------------------------------------------------------|---------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|

| Async APB peripheral | CPU: 12 MHz,<br>Async APB<br>bus: 12 MHz | CPU: 48 MHz,<br>sync APB bus:<br>12 MHz <sup>[2]</sup> | CPU: 96 MHz,<br>Async APB<br>bus: 12 MHz <sup>[2]</sup> | CPU: 180 MHz,<br>Async APB bus:<br>12 MHz <sup>[2]</sup> | CPU: 220 MHz,<br>Async APB bus:<br>12 MHz <sup>[2]</sup> |

| Timer3               | 0.9                                      | 0.9                                                    | 0.9                                                     | 0.9                                                      | 1.2                                                      |

| Timer4               | 0.9                                      | 0.9                                                    | 0.9                                                     | 0.9                                                      | 1.2                                                      |

[1] Turn off the peripheral when the configuration is done.

- [2] For optimal system power consumption, use fixed low frequency Async APB bus when the CPU is at a higher frequency.

- [3] The supply current per peripheral is measured as the difference in supply current between the peripheral block enabled and the peripheral block disabled using ASYNCAPBCLKCTRL, AHBCLKCTRL0/1, and PDRUNCFG0/1 registers. All other blocks are disabled and no code accessing the peripheral is executed.

- [4] The supply currents are shown for system clock frequencies of 12 MHz, 48 MHz, 96 MHz, 180 MHz, and 220 MHz.

- [5] Typical ratings are not guaranteed. Characterized through bench measurements using typical samples.

# 10.5 Pin characteristics

### Table 21. Static characteristics: pin characteristics

$T_{amb} = -40$  °C to +105 °C, unless otherwise specified. 1.71 V  $\leq V_{DD} \leq$  3.6 V unless otherwise specified. Values tested in production unless otherwise specified.

| Symbol           | Parameter                | Conditions                                                |      | Min                  | Typ <u>[1]</u> | Max                | Unit |

|------------------|--------------------------|-----------------------------------------------------------|------|----------------------|----------------|--------------------|------|

| RESET p          | in                       |                                                           | 1    | 1                    |                |                    |      |

| V <sub>IH</sub>  | HIGH-level input voltage |                                                           |      | $0.8\times V_{DD}$   | -              | 5.0                | V    |

| V <sub>IL</sub>  | LOW-level input voltage  |                                                           |      | -0.5                 | -              | $0.3\times V_{DD}$ | V    |

| V <sub>hys</sub> | hysteresis voltage       |                                                           | [14] | $0.05 \times V_{DD}$ | -              | -                  | V    |

| Standard         | I/O pins                 |                                                           |      |                      |                |                    |      |

| Input cha        | racteristics             |                                                           |      |                      |                |                    |      |

| IIL              | LOW-level input current  | V <sub>I</sub> = 0 V; on-chip pull-up resistor disabled.  |      | -                    | 3.0            | 180                | nA   |

| IIH              | HIGH-level input current | $V_{I} = V_{DD}$ ; $V_{DD} = 3.6$ V; for RESETN pin.      |      |                      | 3.0            | 180                | nA   |

| I <sub>IH</sub>  | HIGH-level input current | $V_{I} = V_{DD}$ ; on-chip pull-down resistor disabled    |      | -                    | 3.0            | 180                | nA   |

| VI               | input voltage            | pin configured to provide a digital function;             | [3]  |                      |                |                    |      |

|                  |                          | $V_{DD} > 1.8 \text{ V}$                                  |      |                      |                |                    |      |

|                  |                          |                                                           |      | 0                    | -              | 5.0                | V    |

|                  |                          | $V_{DD} = 0 V$                                            |      | 0                    | -              | 3.6                | V    |

| V <sub>IH</sub>  | HIGH-level input voltage | $1.71 \text{ V} \le \text{V}_{\text{DD}} < 2.7 \text{ V}$ |      | 1.5                  | -              | 5.0                | V    |

|                  |                          | $2.7~V \leq ~V_{DD} \leq ~3.6~V$                          |      | 2.0                  | -              | 5.0                | V    |

| V <sub>IL</sub>  | LOW-level input voltage  | $1.71 \text{ V} \le \text{V}_{\text{DD}} < 2.7 \text{ V}$ |      | -0.5                 | -              | +0.4               | V    |

|                  |                          | $2.7~V \leq V_{DD} \leq 3.6~V$                            |      | -0.5                 | -              | +0.8               | V    |

| V <sub>hys</sub> | hysteresis voltage       |                                                           | [14] | $0.1 \times V_{DD}$  | -              | -                  | V    |

| Output ch        | aracteristics            |                                                           |      |                      |                | •                  |      |

LPC546xx

**Table 28.** Dynamic characteristics: Dynamic external memory interface, read strategy bits (RD bits) = 01 <sup>[2]</sup>  $C_L = 10 \text{ pF}$  balanced loading on all pins,  $T_{amb} = -40 \text{ °C}$  to 105 °C,  $V_{DD} = 2.7 \text{ V}$  to 3.6 V. Max EMC clock = 100 MHz. Input slew = 1 ns; SLEW set to fast-mode. Parameters sampled at the 90 % and 10 % level of the rising or falling edge. Excluding delays introduced by external device and PCB. Values based on simulation.  $t_{cmddly}$  is programmable delay value for EMC command outputs in command delayed mode;  $t_{fbdly}$  is programmable delay value for the feedback clock that controls input data sampling.

| Symbol               | Parameter                              |     | Min                       | Тур | Max                       | Unit     |

|----------------------|----------------------------------------|-----|---------------------------|-----|---------------------------|----------|

| For RD = 1           |                                        |     | I                         | I   |                           |          |

| Common to            | o read and write cycles                |     |                           |     |                           |          |

| T <sub>cy(clk)</sub> | clock cycle time                       | [1] | 10                        | -   | -                         | ns       |

| t <sub>d(SV)</sub>   | chip select valid delay time           |     | -                         | -   | t <sub>cmddly</sub> + 3.7 | ns       |

| t <sub>h(S)</sub>    | chip select hold time                  |     | t <sub>cmddly</sub> + 1.7 | -   | -                         | ns       |

| t <sub>d(RASV)</sub> | row address strobe valid delay time    |     | -                         | -   | t <sub>cmddly</sub> + 4.1 | ns       |

| t <sub>h(RAS)</sub>  | row address strobe hold time           |     | t <sub>cmddly</sub> + 1.8 | -   | -                         | ns       |

| t <sub>d(CASV)</sub> | column address strobe valid delay time |     | -                         | -   | t <sub>cmddly</sub> + 4.4 | ns       |

| t <sub>h(CAS)</sub>  | column address strobe hold time        |     | t <sub>cmddly</sub> + 1.9 | -   | -                         | ns       |

| t <sub>d(WV)</sub>   | write valid delay time                 |     | -                         | -   | t <sub>cmddly</sub> + 5.1 | ns       |

| t <sub>h(W)</sub>    | write hold time                        |     | t <sub>cmddly</sub> + 2.4 | -   | -                         | ns       |

| t <sub>d(AV)</sub>   | address valid delay time               |     | -                         | -   | t <sub>cmddly</sub> + 4.8 | ns       |

| t <sub>h(A)</sub>    | address hold time                      |     | t <sub>cmddly</sub> + 1.7 | -   | -                         | ns       |

| Read cycle           | parameters                             |     |                           |     |                           | <b>i</b> |

| t <sub>su(D)</sub>   | data input set-up time                 |     | 0.5                       | -   | -                         | ns       |

| t <sub>h(D)</sub>    | data input hold time                   |     | 2.1                       | -   | -                         | ns       |

| Write cycle          | parameters                             |     |                           |     |                           |          |

| t <sub>d(QV)</sub>   | data output valid delay time           |     | -                         | -   | 8.1                       | ns       |

| t <sub>h(Q)</sub>    | data output hold time                  |     | -1.7                      | -   | -                         | ns       |

[1] Refers to SDRAM clock signal EMC\_CLKOUTn where n = 0 and 1.

[2] See Table 30 for internal programmable delay.

# 11.14 I<sup>2</sup>S-bus interface

### Table 42. Dynamic characteristics: I<sup>2</sup>S-bus interface pins [1][4]

$T_{amb} = -40$  °C to 105 °C;  $V_{DD} = 1.71$  V to 3.6 V;  $C_L = 30$  pF balanced loading on all pins; Input slew = 1.0 ns, SLEW setting = standard mode for all pins; Parameters sampled at the 50 % level of the rising or falling edge.

| Symbol             | Parameter              | Conditions                    |      | Min                     | Typ <u>[3]</u> | Max                      | Unit |

|--------------------|------------------------|-------------------------------|------|-------------------------|----------------|--------------------------|------|

| Commor             | to master and slave    |                               |      |                         |                |                          |      |

| t <sub>WH</sub>    | pulse width HIGH       | on pins I2Sx_TX_SCK and I2S   | Sx_R | X_SCK <sup>[5]</sup>    |                |                          |      |

|                    |                        | CCLK ≤ 100 MHz                |      | (T <sub>cyc</sub> /2)-1 | -              | (T <sub>cyc</sub> /2) +1 | ns   |

|                    |                        | 100 MHz < CCLK $\leq$ 180 MHz |      | (T <sub>cyc</sub> /2)-1 | -              | (T <sub>cyc</sub> /2) +1 | ns   |

| t <sub>WL</sub>    | pulse width LOW        | on pins I2Sx_TX_SCK and I2    | Sx_R | X_SCK <sup>[5]</sup>    |                |                          |      |

|                    |                        | CCLK ≤ 100 MHz                |      | (T <sub>cyc</sub> /2)-1 | -              | (T <sub>cyc</sub> /2) +1 | ns   |

|                    |                        | 100 MHz < CCLK $\leq$ 180 MHz |      | (T <sub>cyc</sub> /2)-1 | -              | (T <sub>cyc</sub> /2) +1 | ns   |

| Master; *          | 1.71 V ≤ VDD < 2.7 V   |                               |      | <u> </u>                |                |                          |      |

| t <sub>v(Q)</sub>  | data output valid time | on pin I2Sx_TX_SDA            | [2]  |                         |                |                          |      |

|                    |                        | CCLK ≤ 100 MHz                |      | 26.0                    | -              | 40.3                     | ns   |

|                    |                        | 100 MHz < CCLK $\leq$ 180 MHz |      | 25.0                    | -              | 39.0                     | ns   |

|                    |                        | on pin I2Sx_WS                |      |                         |                | -                        | 1    |

|                    |                        | CCLK ≤ 100 MHz                |      | 26.0                    | -              | 41.0                     | ns   |

|                    |                        | 100 MHz < CCLK $\leq$ 180 MHz |      | 25.0                    | -              | 39.6                     | ns   |

| t <sub>su(D)</sub> | data input set-up time | on pin I2Sx_RX_SDA            | [2]  |                         |                |                          |      |

|                    |                        | CCLK ≤ 100 MHz                |      | 0                       | -              | -                        | ns   |

|                    |                        | 100 MHz < CCLK $\leq$ 180 MHz |      | 0                       | -              | -                        | ns   |

| t <sub>h(D)</sub>  | data input hold time   | on pin I2Sx_RX_SDA            | [2]  |                         |                |                          |      |

|                    |                        | $CCLK \le 100 \text{ MHz}$    |      | 6.1                     | -              | -                        | ns   |

|                    |                        | 100 MHz < CCLK $\leq$ 180 MHz |      | 6.4                     | -              | -                        | ns   |

| Slave; 1.          | 71 V ≤ VDD < 2.7 V     |                               |      | <u> </u>                |                |                          |      |

| t <sub>v(Q)</sub>  | data output valid time | on pin I2Sx_TX_SDA            | [2]  |                         |                |                          |      |

|                    |                        | CCLK ≤ 100 MHz                |      | 18.8                    | -              | 37.1                     | ns   |

|                    |                        | 100 MHz < CCLK $\leq$ 180 MHz |      | 18.0                    | -              | 35.5                     | ns   |

| t <sub>su(D)</sub> | data input set-up time | on pin I2Sx_RX_SDA            | [2]  |                         |                |                          |      |

|                    |                        | CCLK ≤ 100 MHz                |      | 4.8                     | -              | -                        | ns   |

|                    |                        | 100 MHz < CCLK $\leq$ 180 MHz |      | 4.4                     | -              | -                        | ns   |

|                    |                        | on pin I2Sx_WS                |      | <u> </u>                |                |                          |      |

|                    |                        | CCLK ≤ 100 MHz                |      | 0                       | -              | -                        | ns   |

|                    |                        | 100 MHz < CCLK $\leq$ 180 MHz |      | 0                       | -              | -                        | ns   |

| t <sub>h(D)</sub>  | data input hold time   | on pin I2Sx_RX_SDA            | [2]  |                         |                |                          |      |

|                    |                        | CCLK ≤ 100 MHz                |      | 0                       | -              | -                        | ns   |

|                    |                        | 100 MHz < CCLK $\leq$ 180 MHz |      | 0                       | -              | -                        | ns   |

|                    |                        | on pin I2Sx_WS                |      | - ·                     |                |                          |      |

|                    |                        | CCLK ≤ 100 MHz                |      | 3.2                     | -              | -                        | ns   |

|                    |                        | 100 MHz < CCLK ≤ 180 MHz      | 1    | 3.2                     |                |                          | ns   |

# LPC546xx

# 32-bit ARM Cortex-M4 microcontroller

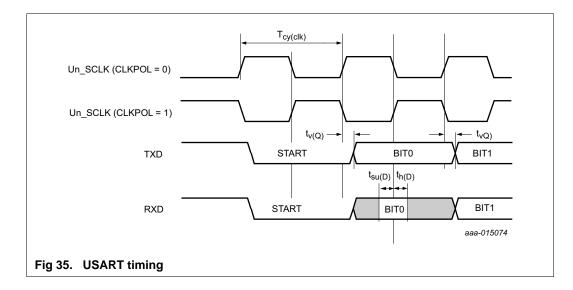

# 11.19 USART interface

The actual USART bit rate depends on the delays introduced by the external trace, the external device, system clock (CCLK), and capacitive loading. Excluding delays introduced by external device and PCB, the maximum supported bit rate for USART master synchronous mode is 24 Mbit/s, and the maximum supported bit rate for USART slave synchronous mode is 12.5 Mbit/s.

### Table 47. USART dynamic characteristics<sup>[1]</sup>

$T_{amb} = -40$  °C to 105 °C;  $V_{DD} = 1.71$  V to 3.6 V;  $C_L = 30$  pF balanced loading on all pins; Input slew = 1 ns, SLEW setting = standard mode for all pins; Parameters sampled at the 50 % level of the rising or falling edge.

| Symbol                                    | Parameter                     | Conditions                          | Min  | Тур      | Max      | Unit |

|-------------------------------------------|-------------------------------|-------------------------------------|------|----------|----------|------|

| USART r                                   | naster (in synchronous r      | node) 1.71 V ≤ VDD ≤ 2.7 V          |      | <b>I</b> | I        | I    |

| t <sub>su(D)</sub>                        | data input set-up time        | CCLK ≤ 100 MHz                      | 21.2 | -        | -        | ns   |

|                                           |                               | 100 MHz < CCLK ≤ 180 MHz            | 19.7 | -        | -        | ns   |

| t <sub>h(D)</sub>                         | data input hold time          | CCLK ≤ 100 MHz                      | 0    | -        | -        | ns   |

|                                           |                               | 100 MHz < CCLK $\leq$ 180 MHz       | 0    | -        | -        | ns   |

| t <sub>v(Q)</sub>                         | data output valid time        | CCLK ≤ 100 MHz                      | 0    | -        | 4.9      | ns   |

|                                           |                               | 100 MHz < CCLK $\leq$ 180 MHz       | 0    | -        | 4.5      | ns   |

| USART s                                   | slave (in synchronous mo      | ode)1.71 V ≤ VDD ≤ 2.7 V            |      | ·        | <u> </u> | L    |

| t <sub>su(D)</sub> data input set-up time |                               | $CCLK \le 100 \text{ MHz}$          | 1.7  | -        | -        | ns   |

|                                           |                               | 100 MHz < CCLK $\leq$ 180 MHz       | 1.5  | -        | -        | ns   |

| t <sub>h(D)</sub>                         | data input hold time          | $CCLK \le 100 \text{ MHz}$          | 1.2  | -        | -        | ns   |

|                                           |                               | 100 MHz < CCLK $\leq$ 180 MHz       | 1.4  | -        | -        | ns   |

| $t_{v(Q)}$ data output valid time         | data output valid time        | $CCLK \le 100 \text{ MHz}$          | 20.2 | -        | 39.5     | ns   |

|                                           | 100 MHz < CCLK $\leq$ 180 MHz | 19.3                                | -    | 37.7     | ns       |      |

| USART r                                   | naster (in synchronous r      | node) 2.7 V $\leq$ VDD $\leq$ 3.6 V |      |          |          |      |

| t <sub>su(D)</sub>                        | data input set-up time        | $CCLK \le 100 \text{ MHz}$          | 20.5 | -        | -        | ns   |

|                                           |                               | 100 MHz < CCLK $\leq$ 180 MHz       | 18.9 | -        | -        | ns   |

| t <sub>h(D)</sub>                         | data input hold time          | $CCLK \le 100 \text{ MHz}$          | 0    | -        | -        | ns   |

|                                           |                               | 100 MHz < CCLK $\leq$ 180 MHz       | 0    | -        | -        | ns   |

| t <sub>v(Q)</sub>                         | data output valid time        | $CCLK \le 100 \text{ MHz}$          | 1.5  | -        | 3.6      | ns   |

|                                           |                               | 100 MHz < CCLK $\leq$ 180 MHz       | 1.3  | -        | 3.2      | ns   |

| USART s                                   | slave (in synchronous m       | ode) 2.7 V $\leq$ VDD $\leq$ 3.6 V  |      |          |          |      |

| t <sub>su(D)</sub>                        | data input set-up time        | $CCLK \le 100 \text{ MHz}$          | 1.2  | -        | -        | ns   |

|                                           |                               | 100 MHz < CCLK $\leq$ 180 MHz       | 1    | -        | -        | ns   |

| t <sub>h(D)</sub>                         | data input hold time          | $CCLK \le 100 \text{ MHz}$          | 0    | -        | -        | ns   |

|                                           |                               | 100 MHz < CCLK $\leq$ 180 MHz       | 0    | -        | -        | ns   |

| t <sub>v(Q)</sub>                         | data output valid time        | $CCLK \le 100 \text{ MHz}$          | 15.2 | -        | 26.1     | ns   |

|                                           |                               | 100 MHz < CCLK $\leq$ 180 MHz       | 14.3 | -        | 24.2     | ns   |

[1] Based on characterization; not tested in production.

# LPC546xx

### 32-bit ARM Cortex-M4 microcontroller

# 11.20 SCTimer/PWM output timing

### Table 48. SCTimer/PWM output dynamic characteristics

$T_{amb} = -40 \text{ }^{\circ}\text{C}$  to 105  $^{\circ}\text{C}$ ; 1.71 V  $\leq$  V<sub>DD</sub>  $\leq$  3.6 V C<sub>L</sub> = 30 pF. Simulated skew (over process, voltage, and temperature) of any two SCT fixed-pin output signals; sampled at the 90 % and 10 % level of the rising or falling edge; values guaranteed by design.

| Symbol             | Parameter        | Conditions | Min | Тур | Мах | Unit |

|--------------------|------------------|------------|-----|-----|-----|------|

| t <sub>sk(o)</sub> | output skew time | -          | 3.4 | -   | 4.5 | ns   |

# 11.21 USB interface characteristics

### Table 49. Dynamic characteristics: USB0 pins (full-speed)

$C_L = 50 \text{ pF}$ ;  $R_{pu} = 1.5 \text{ k}\Omega \text{ on } D$ + to  $V_{DD}$ , unless otherwise specified;  $3.0 \text{ V} \le V_{DD} \le 3.6 \text{ V}$ .

| Symbol             | Parameter                                                   | Conditions                              |            | Min   | Тур | Max    | Unit |

|--------------------|-------------------------------------------------------------|-----------------------------------------|------------|-------|-----|--------|------|

| t <sub>r</sub>     | rise time                                                   | 10 % to 90 %                            |            | 4.0   |     | 20     | ns   |

| t <sub>f</sub>     | fall time                                                   | 10 % to 90 %                            |            | 4.0   |     | 20     | ns   |

| t <sub>FRFM</sub>  | differential rise and fall time matching                    | t <sub>r</sub> / t <sub>f</sub>         |            | 90    |     | 111.11 | %    |

| V <sub>CRS</sub>   | output signal crossover voltage                             |                                         |            | 1.3   |     | 2.0    | V    |

| t <sub>FEOPT</sub> | source SE0 interval of EOP                                  | see Figure 36                           |            | 160   |     | 175    | ns   |

| t <sub>FDEOP</sub> | source jitter for differential transition to SE0 transition | see <u>Figure 36</u>                    |            | -2    |     | +5     | ns   |

| t <sub>JR1</sub>   | receiver jitter to next transition                          |                                         |            | -18.5 |     | +18.5  | ns   |

| t <sub>JR2</sub>   | receiver jitter for paired transitions                      | 10 % to 90 %                            |            | -9    | -   | +9     | ns   |

| t <sub>EOPR1</sub> | EOP width at receiver                                       | must reject as<br>EOP; see<br>Figure 36 | [1]        | 40    | -   |        | ns   |

| t <sub>EOPR2</sub> | EOP width at receiver                                       | must accept as<br>EOP; see<br>Figure 36 | <u>[1]</u> | 82    | -   | -      | ns   |

[1] Characterized but not implemented as production test. Guaranteed by design.

LPC546xx

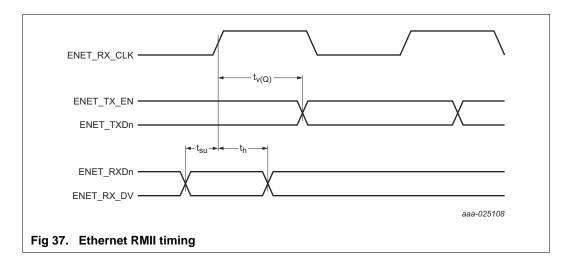

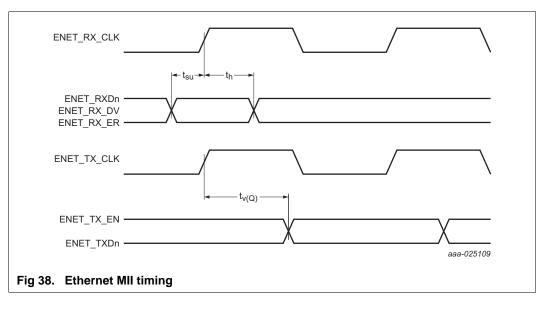

### Table 50. Dynamic characteristics: Ethernet

$T_{amb} = -40$  °C to 105 °C,  $V_{DD} = 2.7$  V to 3.6 V.  $C_L = 30$  pF balanced loading on all pins; Input slew = 1 ns, SLEW setting = standard mode for all pins; Parameters sampled at the 90 % and 10 % level of the rising or falling edge. Based on simulation.

| Symbol            | Parameter                 | Conditions                                      |               | Min  | Тур | Max  | Unit |

|-------------------|---------------------------|-------------------------------------------------|---------------|------|-----|------|------|

| t <sub>h</sub>    | data input hold time      | for ENET_RXDn, ENET_RX_ER, [1][2]<br>ENET_RX_DV |               |      |     |      |      |

|                   |                           | CCLK ≤ 100 MHz                                  |               | -1.2 | -   | 0    | ns   |

|                   |                           | 100 MHz < CCLK $\leq$ 180 MHz                   |               | -1.2 | -   | 0    | ns   |

| t <sub>v(Q)</sub> | data output valid<br>time | for ENET_TXDn, ENET_TX_EN,<br>ENET_TX_ER        | <u>[1][2]</u> |      |     |      |      |

|                   |                           | CCLK ≤ 100 MHz                                  |               | 10.0 | -   | 18.2 | ns   |

|                   |                           | 100 MHz < CCLK $\leq$ 180 MHz                   |               | 10.0 | -   | 18.2 | ns   |

[1] Output drivers can drive a load ≥ 25 pF accommodating over 12 inch of PCB trace and the input capacitance of the receiving device.

[2] Timing values are given from the point at which the clock signal waveform crosses 1.4 V to the valid input or output level.

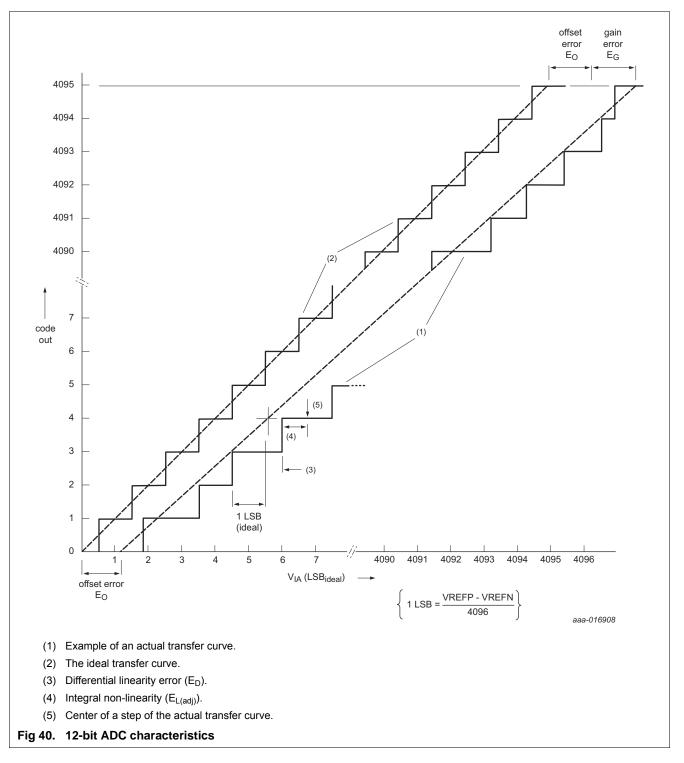

# 12.2 12-bit ADC characteristics

# Table 54. 12-bit ADC static characteristics

$T_{amb} = -40 \text{ }^{\circ}\text{C} \text{ to } +105 \text{ }^{\circ}\text{C}; 1.71 \text{ V} \le V_{DD} \le 3.6 \text{ V}; V_{SSA} = VREFN = GND. ADC calibrated at <math>T_{amb} = 25 \text{ }^{\circ}\text{C}.$

| Symbol                | Parameter                       | Conditions                                                                                                                                                                                        |               | Min  | Typ <u>[2]</u> | Max              | Unit       |

|-----------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------|----------------|------------------|------------|

|                       |                                 |                                                                                                                                                                                                   |               |      |                |                  |            |

| V <sub>IA</sub>       | analog input<br>voltage         |                                                                                                                                                                                                   | [3]           | 0    | -              | V <sub>DDA</sub> | V          |

| C <sub>ia</sub>       | analog input capacitance        |                                                                                                                                                                                                   | [4]           | -    | 5.0            | -                | pF         |

| f <sub>clk(ADC)</sub> | ADC clock<br>frequency          |                                                                                                                                                                                                   |               |      | -              | 80               | MHz        |

| f <sub>s</sub>        | sampling<br>frequency           |                                                                                                                                                                                                   |               | -    | -              | 5.0              | Msamples/s |

| -                     | differential linearity<br>error | $\begin{array}{l} 2.0 \ V < V_{DDA} \leq 3.6 \ V \\ 2.0 \ V < VREFP \leq 3.6 \ V \\ f_{clk(ADC)} = 80 \ MHz \end{array}$                                                                          | <u>[1][5]</u> | -    | <±3.0          | -                | LSB        |

|                       |                                 | $\label{eq:constraint} \begin{array}{l} 1.71 \ V \leq V_{DDA} \leq 2.0 \ V \\ 1.71 \ V \leq VREFP \leq 2.0 \ V \\ f_{clk(ADC)} = 80 \ MHz \end{array}$                                            | [1][5]        | -    | <±4.5          | -                | LSB        |

|                       |                                 |                                                                                                                                                                                                   | [1][5]        | -    |                | -                | LSB        |

|                       | integral<br>non-linearity       | $\begin{array}{l} 2.0 \ V < V_{DDA} \leq 3.6 \ V \\ 2.0 \ V < VREFP \leq 3.6 \ V \\ f_{clk(ADC)} = 80 \ MHz \end{array}$                                                                          | <u>[1][6]</u> | -    | <±4.0          | -                | LSB        |

|                       |                                 | $\begin{array}{l} 1.71 \text{ V} \leq \text{V}_{\text{DDA}} \leq 2.0 \text{ V} \\ 1.71 \text{ V} \leq \text{VREFP} \leq 2.0 \text{ V} \\ f_{\text{clk}(\text{ADC})} = 80 \text{ MHz} \end{array}$ | <u>[1][6]</u> | -    | <±7.5          | -                | LSB        |

|                       |                                 |                                                                                                                                                                                                   | [1][6]        | -    |                | -                | LSB        |

| Eo                    | offset error                    | calibration enabled                                                                                                                                                                               | <u>[1][7]</u> | -    | <±2.2          | -                | mV         |

| V <sub>err(FS)</sub>  | full-scale error<br>voltage     | $\begin{array}{l} 2.0 \ V < V_{DDA} \leq 3.6 \ V \\ 2.0 \ V < VREFP \leq 3.6 \ V \\ f_{clk(ADC)} = 80 \ MHz \end{array}$                                                                          | <u>[1][8]</u> | -    | <±3.0          | -                | LSB        |

|                       |                                 | $\label{eq:VDDA} \begin{array}{l} 1.71 \ V \leq V_{DDA} \leq 2.0 \ V \\ 1.71 \ V \leq VREFP \leq 2.0 \ V \\ f_{clk(ADC)} = 80 \ MHz \end{array}$                                                  |               | -    | < ±2.5         | -                | LSB        |

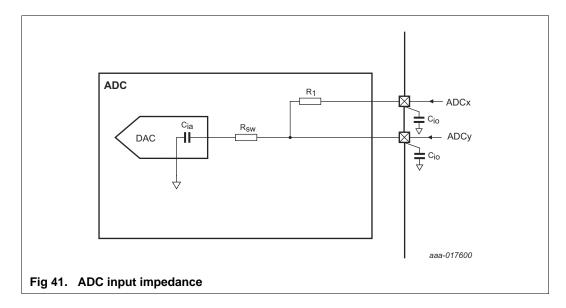

| Zi                    | input impedance                 | f <sub>s</sub> = 5.0 Msamples/s                                                                                                                                                                   | [9][10]       | 17.0 | -              | -                | kΩ         |

[1] Based on characterization; not tested in production.

- [2] Typical ratings are not guaranteed. The values listed are at room temperature (25 °C), nominal supply voltages.

- [3] The input resistance of ADC channels 6 to 11 is higher than ADC channels 0 to 5.

- [4] C<sub>ia</sub> represents the external capacitance on the analog input channel for sampling speeds of 5.0 Msamples/s. No parasitic capacitances included.

- [5] The differential linearity error ( $E_D$ ) is the difference between the actual step width and the ideal step width. See <u>Figure 40</u>.

- [6] The integral non-linearity (E<sub>L(adj)</sub>) is the peak difference between the center of the steps of the actual and the ideal transfer curve after appropriate adjustment of gain and offset errors. See Figure 40.

- [7] The offset error ( $E_0$ ) is the absolute difference between the straight line which fits the actual curve and the straight line which fits the ideal curve. See <u>Figure 40</u>.

LPC546xx

- [8] The full-scale error voltage or gain error (E<sub>G</sub>) is the difference between the straight-line fitting the actual transfer curve after removing offset error, and the straight line which fits the ideal transfer curve. See Figure 40.

- [9]  $T_{amb} = 25 \text{ °C}$ ; maximum sampling frequency  $f_s = 5.0$  Msamples/s and analog input capacitance  $C_{ia} = 5 \text{ pF}$ .

- [10] Input impedance  $Z_i$  is inversely proportional to the sampling frequency and the total input capacity including  $C_{ia}$  and  $C_{io}$ :  $Z_i \propto 1 / (f_s \times C_i)$ . See <u>Table 21</u> for  $C_{io}$ . See <u>Figure 41</u>.

Product data sheet

# 12.3 Temperature sensor

# Table 56. Temperature sensor static and dynamic characteristics

| Symbol             | Parameter                         | Conditions                                |     | Min | Тур  | Max  | Unit |

|--------------------|-----------------------------------|-------------------------------------------|-----|-----|------|------|------|

| DT <sub>sen</sub>  | sensor<br>temperature<br>accuracy | $T_{amb}$ = -40 °C to +105 °C             | [1] | -   |      | 3.7  | °C   |

| EL                 | linearity error                   | $T_{amb}$ = -40 °C to +105 °C             |     | -   | -    | 3.7  | °C   |

| t <sub>s(pu)</sub> | power-up<br>settling time         | to 99% of temperature sensor output value | [2] | -   | 10.0 | 15.0 | μS   |

[1] Absolute temperature accuracy.

[2] Based on simulation.

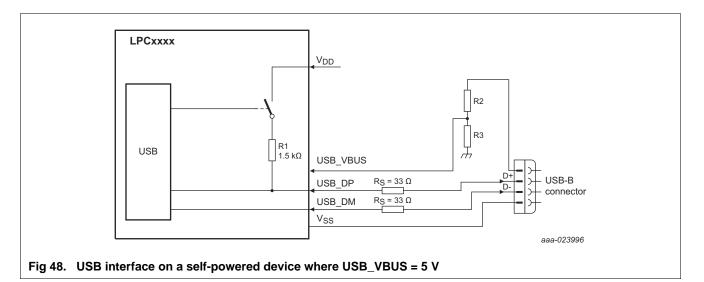

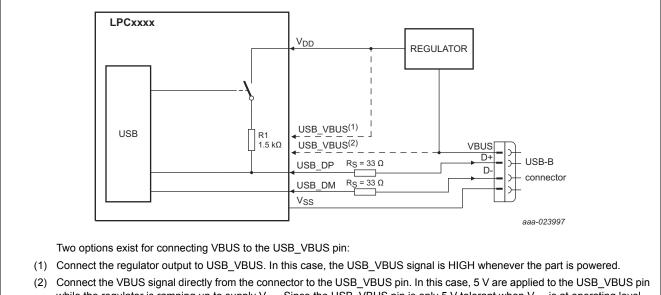

The internal pull-up  $(1.5 \text{ k}\Omega)$  can be enabled by setting the DCON bit in the DEVCMDSTAT register to prevent the USB from timing out when there is a significant delay between power-up and handling USB traffic. External circuitry is not required.