# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                            |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 180MHz                                                                     |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB                   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 64                                                                         |

| Program Memory Size        | 512KB (512K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 16K x 8                                                                    |

| RAM Size                   | 200K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                               |

| Data Converters            | A/D 12x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 100-LQFP                                                                   |

| Supplier Device Package    | 100-LQFP (14x14)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc54606j512bd100e |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

LPC546xx

|         | · .            |                |               |               |     |                 |      |                                                                                                                                 |

|---------|----------------|----------------|---------------|---------------|-----|-----------------|------|---------------------------------------------------------------------------------------------------------------------------------|

| Symbol  | 100-pin, TFBGA | 180-pin, TFBGA | 208-pin, LQFP | 100-pin, LQFP |     | Reset state [1] | Type | Description                                                                                                                     |

| PIO1_14 | A9             | C12            | 160           | 78            | [2] | PU              | I/O  | PIO1_14 — General-purpose digital input/output pin.                                                                             |

|         |                |                |               |               |     |                 | I    | <b>ENET_RX_DV</b> — Ethernet receive data valid.                                                                                |

|         |                |                |               |               |     |                 | I    | UTICK_CAP2 — Micro-tick timer capture input 2.                                                                                  |

|         |                |                |               |               |     |                 | 0    | CT1_MAT2 — Match output 2 from Timer 1.                                                                                         |

|         |                |                |               |               |     |                 | I/O  | FC5_CTS_SDA_SSEL0 — Flexcomm 5: USART clear-to-send, I2C data I/O, SPI Slave Select 0.                                          |

|         |                |                |               |               |     |                 | 0    | <b>USB0_LEDN</b> — USB0-configured LED indicator (active low).                                                                  |

|         |                |                |               |               |     |                 | 0    | EMC_DQM[1] — External memory interface data mask 0.                                                                             |

| PIO1_15 | C7             | A11            | 176           | 84            | [2] | PU              | I/O  | PIO1_15 — General-purpose digital input/output pin.                                                                             |

|         |                |                |               |               |     |                 | I    | <b>ENET_RX_CLK</b> — Ethernet Receive Clock (MII interface) or Ethernet Reference Clock (RMII interface).                       |

|         |                |                |               |               |     |                 | I    | UTICK_CAP3 — Micro-tick timer capture input 3.                                                                                  |

|         |                |                |               |               |     |                 | I    | CT1_CAP3 — Capture 3 input to Timer 1.                                                                                          |

|         |                |                |               |               |     |                 | I/O  | FC5_RTS_SCL_SSEL1 — Flexcomm 5: USART request-to-send, I2C clock, SPI slave select 1.                                           |

|         |                |                |               |               |     |                 | I/O  | FC4_RTS_SCL_SSEL1 — Flexcomm 4: USART request-to-send, I2C clock, SPI slave select 1.                                           |

|         |                |                |               |               |     |                 | 0    | <b>EMC_CKE[0]</b> — External memory interface SDRAM clock enable 0.                                                             |

| PIO1_16 | B5             | B7             | 187           | 88            | [2] | PU              | I/O  | PIO1_16 — General-purpose digital input/output pin.                                                                             |

|         |                |                |               |               |     |                 | 0    | ENET_MDC — Ethernet management data clock.                                                                                      |

|         |                |                |               |               |     |                 | I/O  | <b>FC6_TXD_SCL_MISO_WS</b> — Flexcomm 6: USART transmitter, I2C clock, SPI master-in/slave-out data I/O, I2S word-select/frame. |

|         |                |                |               |               |     |                 | 0    | CT1_MAT3 — Match output 3 from Timer 1.                                                                                         |

|         |                |                |               |               |     |                 | I/O  | <b>SD_CMD</b> — SD/MMC card command I/O.                                                                                        |

|         |                |                |               |               |     |                 |      | R — Reserved.                                                                                                                   |

|         |                |                |               |               |     |                 | 0    | EMC_A[10] — External memory interface address 10.                                                                               |

| PIO1_17 | H8             | N12            | 98            | 47            | [2] | PU              | I/O  | PIO1_17 — General-purpose digital input/output pin.                                                                             |

|         |                |                |               |               |     |                 | I/O  | ENET_MDIO — Ethernet management data I/O.                                                                                       |

|         |                |                |               |               |     |                 | I/O  | FC8_RXD_SDA_MOSI — Flexcomm 8: USART receiver, I2C data I/O, SPI master-out/slave-in data.                                      |

|         |                |                |               |               |     |                 |      | R — Reserved.                                                                                                                   |

|         |                |                |               |               |     |                 | 0    | SCT0_OUT4 — SCTimer/PWM output 4.                                                                                               |

|         |                |                |               |               |     |                 | 0    | CAN1_TD — Transmitter output for CAN 1.                                                                                         |

|         |                |                |               |               |     |                 | 0    | <b>EMC_BLSN[0]</b> — External memory interface byte lane select 0 (active low).                                                 |

|         |                |                |               |               |     |                 |      |                                                                                                                                 |

# Table 4. Pin description ...continued

LPC546xx

#### Table 4. Pin description ...continued

| Symbol  | 100-pin, TFBGA | 180-pin, TFBGA | 208-pin, LQFP | 100-pin, LQFP |     | Reset state [1] | Type | Description                                                                                                                   |

|---------|----------------|----------------|---------------|---------------|-----|-----------------|------|-------------------------------------------------------------------------------------------------------------------------------|

| PIO2_8  | -              | F4             | 32            | -             | [2] | PU              | I/O  | <b>PIO2_8</b> — General-purpose digital input/output pin.                                                                     |

|         |                |                |               |               |     |                 | I    | <b>ENET_RXD2</b> — Ethernet Receive Data 2 (MII interface).                                                                   |

|         |                |                |               |               |     |                 | I/O  | <b>SD_D[2] —</b> SD/MMC data 2.                                                                                               |

|         |                |                |               |               |     |                 |      | R — Reserved.                                                                                                                 |

|         |                |                |               |               |     |                 | 0    | <b>CT0_MAT0</b> — Match output 0 from Timer 0.                                                                                |

| PIO2_9  | -              | K2             | 36            | -             | [2] | PU              | I/O  | PIO2_9 — General-purpose digital input/output pin.                                                                            |

|         |                |                |               |               |     |                 | I    | <b>ENET_RXD3</b> — Ethernet Receive Data 3 (MII interface).                                                                   |

|         |                |                |               |               |     |                 | I/O  | <b>SD_D[3] —</b> SD/MMC data 3.                                                                                               |

|         |                |                |               |               |     |                 |      | R — Reserved.                                                                                                                 |

|         |                |                |               |               |     |                 | 0    | CT0_MAT1 — Match output 0 from Timer 1.                                                                                       |

| PIO2_10 | -              | P1             | 39            | -             | [2] | PU              | I/O  | PIO2_10 — General-purpose digital input/output pin.                                                                           |

|         |                |                |               |               |     |                 | I    | ENET_RX_ER — Ethernet receive error (RMII/MII interface).                                                                     |

|         |                |                |               |               |     |                 | I    | SD_CARD_DET_N — SD/MMC card detect (active low).                                                                              |

| PIO2_11 | -              | K3             | 43            | -             | [2] | PU              | I/O  | PIO2_11 — General-purpose digital input/output pin.                                                                           |

|         |                |                |               |               |     |                 | 0    | LCD_PWR — LCD panel power enable.                                                                                             |

|         |                |                |               |               |     |                 | 0    | <b>SD_VOLT[0]</b> — SD/MMC card regulator voltage control [0].                                                                |

|         |                |                |               |               |     |                 |      | R — Reserved.                                                                                                                 |

|         |                |                |               |               |     |                 |      | R — Reserved.                                                                                                                 |

|         |                |                |               |               |     |                 | I/O  | FC5_SCK — Flexcomm 5: USART or SPI clock.                                                                                     |

| PIO2_12 | -              | M2             | 45            | -             | [2] | PU              | I/O  | PIO2_12 — General-purpose digital input/output pin.                                                                           |

|         |                |                |               |               |     |                 | 0    | LCD_LE — LCD line end signal.                                                                                                 |

|         |                |                |               |               |     |                 | 0    | <b>SD_VOLT[1]</b> — SD/MMC card regulator voltage control [1].                                                                |

|         |                |                |               |               |     |                 | I    | <b>USB0_IDVALUE</b> — Indicates to the transceiver whether connected as an A-device (USB0_ID LOW) or B-device (USB0_ID HIGH). |

|         |                |                |               |               |     |                 |      | R — Reserved.                                                                                                                 |

|         |                |                |               |               |     |                 | I/O  | <b>FC5_RXD_SDA_MOSI</b> — Flexcomm 5: USART receiver, I2C data I/O, SPI master-out/slave-in data.                             |

| PIO2_13 | -              | P7             | 70            | -             | [2] | PU              | I/O  | PIO2_13 — General-purpose digital input/output pin.                                                                           |

|         |                |                |               |               |     |                 | 0    | LCD_DCLK — LCD panel clock.                                                                                                   |

|         |                |                |               |               |     |                 | 0    | <b>SD_VOLT[2]</b> — SD/MMC card regulator voltage control [2].                                                                |

|         |                |                |               |               |     |                 |      | R — Reserved.                                                                                                                 |

|         |                |                |               |               |     |                 |      | R — Reserved.                                                                                                                 |

|         |                |                |               |               |     |                 | I/O  | <b>FC5_TXD_SCL_MISO</b> — Flexcomm 5: USART transmitter,<br>I2C clock, SPI master-in/slave-out data.                          |

| Table 4. | Pin description continued |

|----------|---------------------------|

|----------|---------------------------|

| Symbol  | 100-pin, TFBGA | 180-pin, TFBGA | 208-pin, LQFP | 100-pin, LQFP |     | Reset state [1] | Type | Description                                                                                   |

|---------|----------------|----------------|---------------|---------------|-----|-----------------|------|-----------------------------------------------------------------------------------------------|

| PIO3_13 | -              | H4             | 75            | -             | [2] | PU              | I/O  | PIO3_13 — General-purpose digital input/output pin.                                           |

|         |                |                |               |               |     |                 | 0    | SCT0_OUT9 — SCTimer/PWM output 9.                                                             |

|         |                |                |               |               |     |                 | I/O  | FC9_CTS_SDA_SSEL0 — Flexcomm 9: USART clear-to-send, I2C data I/O, SPI Slave Select 0.        |

|         |                |                |               |               |     |                 | I    | CT3_CAP1 — Capture input 1 to Timer 3.                                                        |

|         |                |                |               |               |     |                 |      | R — Reserved.                                                                                 |

|         |                |                |               |               |     |                 |      | R — Reserved.                                                                                 |

|         |                |                |               |               |     |                 | I    | <b>EMC_FBCK</b> — External memory interface feedback clock.                                   |

|         |                |                |               |               |     |                 | 0    | TRACEDATA[1] — Trace data bit 1.                                                              |

| PIO3_14 | -              | E3             | 13            | -             | [2] | PU              | I/O  | PIO3_14 — General-purpose digital input/output pin.                                           |

|         |                |                |               |               |     |                 | 0    | SCT0_OUT4 — SCTimer/PWM output 4.                                                             |

|         |                |                |               |               |     |                 | I/O  | FC9_RTS_SCL_SSEL1 — Flexcomm 9: USART request-to-send, I2C clock, SPI slave select 1.         |

|         |                |                |               |               |     |                 | 0    | CT3_MAT1 — Match output 1 from Timer 3.                                                       |

|         |                |                |               |               |     |                 |      | R — Reserved.                                                                                 |

|         |                |                |               |               |     |                 |      | R — Reserved.                                                                                 |

|         |                |                |               |               |     |                 |      | R — Reserved.                                                                                 |

|         |                |                |               |               |     |                 | 0    | TRACEDATA[2] — Trace data bit 2.                                                              |

| PIO3_15 | -              | D2             | 11            | -             | [2] | PU              | I/O  | <b>PIO3_15</b> — General-purpose digital input/output pin.                                    |

|         |                |                |               |               |     |                 | I/O  | FC8_SCK — Flexcomm 8: USART or SPI clock.                                                     |

|         |                |                |               |               |     |                 | I    | SD_WR_PRT — SD/MMC write protect.                                                             |

| PIO3_16 | -              | E1             | 19            | -             | [2] | PU              | I/O  | <b>PIO3_16</b> — General-purpose digital input/output pin.                                    |

|         |                |                |               |               |     |                 | I/O  | FC8_RXD_SDA_MOSI — Flexcomm 8: USART receiver, I2C data I/O, SPI master-out/slave-in data.    |

|         |                |                |               |               |     |                 | I/O  | <b>SD_D[4]</b> — SD/MMC data 4.                                                               |

| PIO3_17 | -              | K1             | 31            | -             | [2] | PU              | I/O  | <b>PIO3_17</b> — General-purpose digital input/output pin.                                    |

|         |                |                |               |               |     |                 | I/O  | FC8_TXD_SCL_MISO — Flexcomm 8: USART transmitter,<br>I2C clock, SPI master-in/slave-out data. |

|         |                |                |               |               |     |                 | I/O  | <b>SD_D[5] —</b> SD/MMC data 5.                                                               |

| PIO3_18 | -              | M6             | 68            | -             | [2] | PU              | I/O  | PIO3_18 — General-purpose digital input/output pin.                                           |

|         |                |                |               |               |     |                 | I/O  | FC8_CTS_SDA_SSEL0 — Flexcomm 8: USART clear-to-send, I2C data I/O, SPI Slave Select 0.        |

|         |                |                |               |               |     |                 | I/O  | <b>SD_D[6]</b> — SD/MMC data 6.                                                               |

|         |                |                |               |               |     |                 | 0    | CT4_MAT0 — Match output 0 from Timer 4.                                                       |

|         |                |                |               |               |     |                 | 0    | <b>CAN0_TD</b> — Transmitter output for CAN 0.                                                |

|         |                |                |               |               |     |                 | 0    | SCT0_OUT5 — SCTimer/PWM output 5.                                                             |

- [1] PU = input mode, pull-up enabled (pull-up resistor pulls up pin to V<sub>DD</sub>). Z = high impedance; pull-up or pull-down disabled, AI = analog input, I = input, O = output, F = floating. Reset state reflects the pin state at reset without boot code operation. For pin states in the different power modes, see Section 6.2.2 "Pin states in different power modes". For termination on unused pins, see Section 6.2.1 "Termination of unused pins".

- [2] 5 V tolerant pad with programmable glitch filter (5 V tolerant if V<sub>DD</sub> present; if V<sub>DD</sub> not present, do not exceed 3.6 V); provides digital I/O functions with TTL levels and hysteresis; normal drive strength. See <u>Figure 44</u>. Pulse width of spikes or glitches suppressed by input filter is from 3 ns to 16 ns (simulated value).

- [3] True open-drain pin. I2C-bus pins compliant with the I2C-bus specification for I2C standard mode, I2C Fast-mode, and I2C Fast-mode Plus. The pin requires an external pull-up to provide output functionality. When power is switched off, this pin is floating and does not disturb the I2C lines. Open-drain configuration applies to all functions on this pin.

- [4] 5 V tolerant pin providing standard digital I/O functions with configurable modes, configurable hysteresis, and analog input. When configured as an analog input, the digital section of the pin is disabled, and the pin is not 5 V tolerant.

- [5] Reset pad.5 V tolerant pad with glitch filter with hysteresis. Pulse width of spikes or glitches suppressed by input filter is from 3 ns to 20 ns (simulated value)

- [6] 5 V tolerant transparent analog pad.

- [7] The oscillator input pin (XTALIN) cannot be driven by an external clock. Must connect a crystal between XTALIN and XTALOUT.

- [8] VBUS must be connected to supply voltage when using the USB peripheral.

# 6.2.1 Termination of unused pins

<u>Table 5</u> shows how to terminate pins that are **not** used in the application. In many cases, unused pins should be connected externally or configured correctly by software to minimize the overall power consumption of the part.

Unused pins with GPIO function should be configured as outputs set to LOW with their internal pull-up disabled. To configure a GPIO pin as output and drive it LOW, select the GPIO function in the IOCON register, select output in the GPIO DIR register, and write a 0 to the GPIO PORT register for that pin. Disable the pull-up in the pin's IOCON register.

In addition, it is recommended to configure all GPIO pins that are not bonded out on smaller packages as outputs driven LOW with their internal pull-up disabled.

| Pin                         | Default<br>state <sup>[1]</sup> | Recommended termination of unused pins                                                                                                                                                                         |

|-----------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET                       | I; PU                           | The RESET pin can be left unconnected if the application does not use it.                                                                                                                                      |

| all PIOn_m (not open-drain) | I; PU                           | Can be left unconnected if driven LOW and configured as GPIO output with pull-up disabled by software.                                                                                                         |

| PIOn_m (I2C open-drain)     | IA                              | Can be left unconnected if driven LOW and configured as GPIO output by software.                                                                                                                               |

| RTCXIN                      | -                               | Connect to ground. When grounded, the RTC oscillator is disabled.                                                                                                                                              |

| RTCXOUT                     | -                               | Can be left unconnected.                                                                                                                                                                                       |

| XTALIN                      | -                               | Connect to ground. When grounded, the RTC oscillator is disabled.                                                                                                                                              |

| XTALOUT                     | -                               | Can be left unconnected.                                                                                                                                                                                       |

| VREFP                       | -                               | Tie to VDD.                                                                                                                                                                                                    |

| VREFN                       | -                               | Tie to VSS.                                                                                                                                                                                                    |

| VDDA                        | -                               | Tie to VDD.                                                                                                                                                                                                    |

| VSSA                        | -                               | Tie to VSS.                                                                                                                                                                                                    |

| VBAT                        | -                               | Tie to VDD.                                                                                                                                                                                                    |

| USBn_DP                     | F                               | Can be left unconnected. If USB interface is not used, pin can be left unconnected except in deep power-down mode where it must be externally pulled low. When the USB PHY is disabled, the pins are floating. |

Table 5. Termination of unused pins

# 7.12.1.3 Crystal oscillator

The LPC546xx include four independent oscillators. These are the main oscillator, the FRO, the watchdog oscillator, and the RTC oscillator.

Following reset, the LPC546xx will operate from the Internal FRO until switched by software. This allows systems to operate without any external crystal and the boot loader code to operate at a known frequency. See <u>Figure 11</u> and <u>Figure 12</u> for an overview of the LPC546xx clock generation.

# 7.12.2 System PLL (PLL0)

The system PLL accepts an input clock frequency in the range of 32.768 kHz to 25 MHz. The input frequency is multiplied up to a high frequency with a Current Controlled Oscillator (CCO).

The PLL can be enabled or disabled by software.

# 7.12.3 USB PLL (PLL1)

The USB PLL accepts an input clock frequency in the range of 1 MHz to 25 MHz. The input frequency is multiplied up to a high frequency with a Current Controlled Oscillator (CCO).

The PLL can be enabled or disabled by software.

# 7.12.4 Audio PLL (PLL2)

The audio PLL accepts an input clock frequency in the range of 1 MHz to 25 MHz. The input frequency is multiplied up to a high frequency with a Current Controlled Oscillator (CCO).

The PLL can be enabled or disabled by software.

# 7.17.3 Ethernet AVB

The Ethernet block enables a host to transmit and receive data over Ethernet in compliance with the IEEE 802.3-2008 standard. The Ethernet interface contains a full featured 10 Mbps or 100 Mbps Ethernet MAC (Media Access Controller) designed to provide optimized performance through the use of DMA hardware acceleration.

# 7.17.3.1 Features

- 10/100 Mbit/s

- DMA support

- Power management remote wake-up frame and magic packet detection

- Supports both full-duplex and half-duplex operation

- Supports CSMA/CD Protocol for half-duplex operation.

- Supports IEEE 802.3x flow control for full-duplex operation.

- Optional forwarding of received pause control frames to the user application in full-duplex operation.

- Supports IEEE 802.1AS-2011 and 802.1-Qav-2009 for Audio Video (AV) traffic.

- Software support for AVB feature is available from NXP Professional Services. See nxp.com for more details.

- Back-pressure support for half-duplex operation.

- Automatic transmission of zero-quanta pause frame on deassertion of flow control input in full-duplex operation.

- Supports IEEE1588 time stamping and IEEE 1588 advanced time stamping (IEEE 1588-2008 v2).

# 7.17.4 SPI Flash Interface (SPIFI)

The SPI Flash Interface allows low-cost serial flash memories to be connected to the LPC546xx microcontroller with little performance penalty compared to parallel flash devices with higher pin count.

After a few commands configure the interface at startup, the entire flash content is accessible as normal memory using byte, halfword, and word accesses by the processor and/or DMA channels. Simple sequences of commands handle erasure and programming.

Many serial flash devices use a half-duplex command-driven SPI protocol for device setup and initialization and then move to a half-duplex, command-driven 4-bit protocol for normal operation. Different serial flash vendors and devices accept or require different commands and command formats. SPIFI provides sufficient flexibility to be compatible with common flash devices and includes extensions to help insure compatibility with future devices.

#### 7.17.4.1 Features

- Interfaces to serial flash memory in the main memory map.

- Supports classic and 4-bit bidirectional serial protocols.

- Half-duplex protocol compatible with various vendors and devices.

- Quad SPI Flash Interface with 1-, 2-, or 4-bit data at rates of up to 52 MB per second.

© NXP Semiconductors N.V. 2018. All rights reserved.

# 7.17.8.4 USART

### Features

- Maximum bit rates of 6.25 Mbit/s in asynchronous mode.

- The maximum supported bit rate for USART master synchronous mode is 24 Mbit/s, and the maximum supported bit rate for USART slave synchronous mode is 12.5 Mbit/s.

- 7, 8, or 9 data bits and 1 or 2 stop bits.

- Synchronous mode with master or slave operation. Includes data phase selection and continuous clock option.

- Multiprocessor/multidrop (9-bit) mode with software address compare.

- RS-485 transceiver output enable.

- Autobaud mode for automatic baud rate detection

- Parity generation and checking: odd, even, or none.

- Software selectable oversampling from 5 to 16 clocks in asynchronous mode.

- One transmit and one receive data buffer.

- RTS/CTS for hardware signaling for automatic flow control. Software flow control can be performed using Delta CTS detect, Transmit Disable control, and any GPIO as an RTS output.

- · Received data and status can optionally be read from a single register

- Break generation and detection.

- Receive data is 2 of 3 sample "voting". Status flag set when one sample differs.

- Built-in Baud Rate Generator with auto-baud function.

- A fractional rate divider is shared among all USARTs.

- Interrupts available for Receiver Ready, Transmitter Ready, Receiver Idle, change in receiver break detect, Framing error, Parity error, Overrun, Underrun, Delta CTS detect, and receiver sample noise detected.

- Loopback mode for testing of data and flow control.

- In synchronous slave mode, wakes up the part from deep-sleep mode.

- Special operating mode allows operation at up to 9600 baud using the 32.768 kHz RTC oscillator as the UART clock. This mode can be used while the device is in deep-sleep mode and can wake-up the device when a character is received.

- USART transmit and receive functions work with the system DMA controller.

# 7.17.8.5 I<sup>2</sup>S-bus interface

The I<sup>2</sup>S bus provides a standard communication interface for streaming data transfer applications such as digital audio or data collection. The I<sup>2</sup>S bus specification defines a 3-wire serial bus, having one data, one clock, and one word select/frame trigger signal, providing single or dual (mono or stereo) audio data transfer as well as other configurations. In the LPC546xx, the I<sup>2</sup>S function is included in Flexcomm Interface 6 and Flexcomm Interface 7. Each of the Flexcomm Interface implements four I<sup>2</sup>S channel pairs.

The I<sup>2</sup>S interface within one Flexcomm Interface provides at least one channel pair that can be configured as a master or a slave. Other channel pairs, if present, always operate as slaves. All of the channel pairs within one Flexcomm Interface share one set of I<sup>2</sup>S

# 7.18.3.1 Features

- Read and write buffers to reduce latency and to improve performance.

- Low transaction latency.

- Asynchronous static memory device support including RAM, ROM, and flash, with or without asynchronous page mode.

- 8/16/32 data and 16/20/26 address lines wide static memory support.

- Static memory features include:

- Asynchronous page mode read.

- Programmable Wait States.

- Bus turnaround delay.

- Output enable and write enable delays.

- Extended wait.

- Dynamic memory interface support including single data rate SDRAM.

- 16 bit and 32 bit wide chip select SDRAM memory support.

- EMC bus width (bit) on LQFP100 and TFBGA100 packages supports up to 8/16 data line wide static memory, in addition to dynamic memories, such as, SDRAM (2 banks only) with an SDRAM clock of up to 100 MHz.

- Four chip selects for synchronous memory and four chip selects for static memory devices.

- Power-saving modes dynamically control EMC\_CKE and EMC\_CLK outputs to SDRAMs.

- Dynamic memory self-refresh mode controlled by software.

- Controller supports 2048 (A0 to A10), 4096 (A0 to A11), and 8192 (A0 to A12) row address synchronous memory parts. That is typical 512 MB, 256 MB, and 128 MB parts, with 4, 8, 16, or 32 data bits per device.

- Separate reset domains allow the for auto-refresh through a chip reset if desired.

Note: Synchronous static memory devices (synchronous burst mode) are not supported.

# 7.21 CRC engine

The Cyclic Redundancy Check (CRC) generator with programmable polynomial settings supports several CRC standards commonly used. To save system power and bus bandwidth, the CRC engine supports DMA transfers.

# 7.21.1 Features

- Supports three common polynomials CRC-CCITT, CRC-16, and CRC-32.

- CRC-CCITT:  $x^{16} + x^{12} + x^5 + 1$

- CRC-16:  $x^{16} + x^{15} + x^2 + 1$

- CRC-32:  $x^{32} + x^{26} + x^{23} + x^{22} + x^{16} + x^{12} + x^{11} + x^{10} + x^8 + x^7 + x^5 + x^4 + x^2 + x + 1$

- Bit order reverse and 1's complement programmable setting for input data and CRC sum.

- Programmable seed number setting.

- Supports CPU PIO or DMA back-to-back transfer.

- Accept any size of data width per write: 8, 16 or 32-bit.

- 8-bit write: 1-cycle operation.

- 16-bit write: 2-cycle operation (8-bit x 2-cycle).

- 32-bit write: 4-cycle operation (8-bit x 4-cycle).

# 7.22 Temperature sensor

The temperature sensor transducer uses an intrinsic pn-junction diode reference and outputs a CTAT voltage (Complement To Absolute Temperature). The output voltage varies inversely with device temperature with an absolute accuracy of better than  $\pm 5$  °C over the full temperature range (-40 °C to +105 °C). The temperature sensor is only approximately linear with a slight curvature. The output voltage is measured over different ranges of temperatures and fit with linear-least-square lines.

After power-up, the temperature sensor output must be allowed to settle to its stable value before it can be used as an accurate ADC input.

For an accurate measurement of the temperature sensor by the ADC, the ADC must be configured in single-channel burst mode. The last value of a nine-conversion (or more) burst provides an accurate result.

# 7.23 Security features

The OTP memory contains a memory bank of 128 bits each. OTP bank contains 4 words: word 0 for ECRP, word 1 is reserved, words 2 and 3 can be used by user application for storing application specific options.

# 7.23.1 Features

- OTP memory.

- Random number generator (RNG).

registers. All other blocks are disabled and no code accessing the peripheral is executed. The supply currents are shown for system clock frequencies of 12 MHz, 48 MHz, 96 MHz and 180MHz.

#### Table 19. Typical peripheral power consumption<sup>[1][2]</sup>

$V_{DD} = 3.3 V; T_{amb} = 25 °C$

| Peripheral | I <sub>DD</sub> in uA |

|------------|-----------------------|

| FRO        | 100                   |

| WDT OSC    | 2.0                   |

| Flash      | 200                   |

| BOD        | 2.0                   |

| SYSOSC     | 247                   |

[1] The supply current per peripheral is measured as the difference in supply current between the peripheral block enabled and the peripheral block disabled using PDRUNCFG0/1 registers. All other blocks are disabled and no code accessing the peripheral is executed.

[2] Typical ratings are not guaranteed. Characterized through bench measurements using typical samples.

| Table 20. Typical AHB/APB peripheral power consu | mption [3][4][3] |

|--------------------------------------------------|------------------|

|--------------------------------------------------|------------------|

$T_{amb} = 25 \text{ °C}, V_{DD} = 3.3 \text{ V};$

| Peripheral                                             |     | I <sub>DD</sub> in uA/MHz                 | I <sub>DD</sub> in uA/MHz                 |

|--------------------------------------------------------|-----|-----------------------------------------|-----------------------------------------|-----------------------------------------|-------------------------------------------|-------------------------------------------|

| AHB peripheral                                         |     | CPU: 12 MHz,<br>sync APB bus:<br>12 MHz | CPU: 48 MHz,<br>sync APB bus:<br>48 MHz | CPU: 96 MHz,<br>sync APB bus:<br>96 MHz | CPU: 180 MHz,<br>sync APB bus:<br>180 MHz | CPU: 220 MHz,<br>sync APB bus:<br>220 MHz |

| USB0 device                                            |     | 0.3                                     | 0.3                                     | 0.3                                     | 0.4                                       | 0.5                                       |

| USB1 device                                            |     | 4.4                                     | 4.4                                     | 4.4                                     | 5.0                                       | 6.5                                       |

| DMIC                                                   |     | 0.2                                     | 0.2                                     | 0.2                                     | 0.2                                       | 0.3                                       |

| GPIO0                                                  | [1] | 0.9                                     | 0.9                                     | 0.9                                     | 1.0                                       | 1.4                                       |

| GPIO1                                                  | [1] | 0.8                                     | 0.8                                     | 0.8                                     | 1.0                                       | 1.4                                       |

| GPIO2                                                  | [1] | 1.0                                     | 1.0                                     | 1.0                                     | 1.1                                       | 1.4                                       |

| GPIO3                                                  | [1] | 1.1                                     | 1.1                                     | 1.1                                     | 1.3                                       | 1.7                                       |

| GPIO4                                                  | [1] | 1.0                                     | 1.0                                     | 1.0                                     | 1.2                                       | 1.6                                       |

| GPIO5                                                  | [1] | 0.7                                     | 0.7                                     | 0.7                                     | 0.8                                       | 1.1                                       |

| DMA                                                    |     | 0.7                                     | 0.7                                     | 0.7                                     | 0.8                                       | 1.1                                       |

| CRC                                                    |     | 1.0                                     | 1.0                                     | 1.0                                     | 1.0                                       | 1.4                                       |

| ADC0                                                   |     | 1.6                                     | 1.6                                     | 1.6                                     | 1.9                                       | 2.6                                       |

| SCTimer/PWM                                            |     | 4.5                                     | 4.5                                     | 4.5                                     | 5.3                                       | 7.0                                       |

| Ethernet AVB                                           |     | 24.0                                    | 24.0                                    | 24.0                                    | 28.0                                      | 38.0                                      |

| LCD                                                    |     | 13.0                                    | 13.0                                    | 13.0                                    | 15.0                                      | 19.0                                      |

| EEPROM                                                 |     | 1.1                                     | 1.1                                     | 1.1                                     | 1.2                                       | 1.6                                       |

| EMC                                                    |     | 39.0                                    | 39.0                                    | 39.0                                    | 45.4                                      | 60.1                                      |

| CAN0                                                   |     | 10.8                                    | 10.8                                    | 10.8                                    | 12.6                                      | 16.5                                      |

| CAN1                                                   |     | 10.7                                    | 10.7                                    | 10.7                                    | 12.4                                      | 16.4                                      |

| SD/MMC                                                 |     | 7.9                                     | 7.9                                     | 7.9                                     | 9.3                                       | 12.3                                      |

| Flexcomm Interface 0<br>(USART, SPI, I <sup>2</sup> C) |     | 1.6                                     | 1.6                                     | 1.6                                     | 1.9                                       | 2.5                                       |

LPC546xx

All information provided in this document is subject to legal disclaimers.

# Table 20. Typical AHB/APB peripheral power consumption [3][4][5]

$T_{amb} = 25 \ ^{\circ}C, \ V_{DD} = 3.3 \ V;$

| Peripheral                                                               |     | I <sub>DD</sub> in uA/MHz                 | I <sub>DD</sub> in uA/MHz                 |

|--------------------------------------------------------------------------|-----|-----------------------------------------|-----------------------------------------|-----------------------------------------|-------------------------------------------|-------------------------------------------|

| Flexcomm Interface1<br>(USART, SPI, I <sup>2</sup> C)                    |     | 1.6                                     | 1.6                                     | 1.6                                     | 1.8                                       | 2.4                                       |

| Flexcomm Interface 2<br>(USART, SPI, I <sup>2</sup> C)                   |     | 1.7                                     | 1.7                                     | 1.7                                     | 1.9                                       | 2.6                                       |

| Flexcomm Interface 3<br>(USART, SPI, I <sup>2</sup> C)                   |     | 1.4                                     | 1.4                                     | 1.4                                     | 1.6                                       | 2.2                                       |

| Flexcomm Interface 4<br>(USART, SPI, I <sup>2</sup> C)                   |     | 1.4                                     | 1.5                                     | 1.5                                     | 1.7                                       | 2.3                                       |

| Flexcomm Interface 5<br>(USART, SPI, I <sup>2</sup> C)                   |     | 1.7                                     | 1.7                                     | 1.7                                     | 1.9                                       | 2.5                                       |

| Flexcomm Interface 6<br>(USART, SPI, I <sup>2</sup> C, I <sup>2</sup> S) |     | 2.0                                     | 2.0                                     | 2.0                                     | 2.3                                       | 3.0                                       |

| Flexcomm Interface 7<br>(USART, SPI, I <sup>2</sup> C, I <sup>2</sup> S) |     | 1.6                                     | 1.6                                     | 1.6                                     | 1.9                                       | 2.5                                       |

| Flexcomm Interface 8<br>(USART, SPI, I <sup>2</sup> C)                   |     | 1.5                                     | 1.5                                     | 1.5                                     | 1.8                                       | 2.3                                       |

| Flexcomm Interface 9<br>(USART, SPI, I <sup>2</sup> C)                   |     | 1.5                                     | 1.5                                     | 1.5                                     | 1.8                                       | 2.3                                       |

| Sync APB peripheral                                                      |     | CPU: 12 MHz,<br>sync APB bus:<br>12 MHz | CPU: 48 MHz,<br>sync APB bus:<br>48 MHz | CPU: 96 MHz,<br>sync APB bus:<br>96 MHz | CPU: 180 MHz,<br>sync APB bus:<br>180 MHz | CPU: 220 MHz,<br>sync APB bus:<br>220 MHz |

| INPUTMUX                                                                 | [1] | 0.83                                    | 0.85                                    | 0.86                                    | 1.0                                       | 1.3                                       |

| IOCON                                                                    | [1] | 2.67                                    | 2.65                                    | 2.65                                    | 3.13                                      | 4.2                                       |

| PINT                                                                     |     | 1.1                                     | 1.1                                     | 1.1                                     | 1.3                                       | 1.8                                       |

| GINT0 and GINT1                                                          |     | 1.33                                    | 1.35                                    | 1.34                                    | 1.52                                      | 2.0                                       |

| WWDT                                                                     |     | 0.42                                    | 0.42                                    | 0.42                                    | 0.46                                      | 0.6                                       |

| RTC                                                                      |     | 0.3                                     | 0.3                                     | 0.3                                     | 0.3                                       | 0.4                                       |

| MRT                                                                      |     | 0.3                                     | 0.3                                     | 0.3                                     | 0.3                                       | 0.4                                       |

| RIT                                                                      |     | 0.1                                     | 0.1                                     | 0.1                                     | 0.1                                       | 0.1                                       |

| UTICK                                                                    |     | 0.2                                     | 0.2                                     | 0.2                                     | 0.2                                       | 0.3                                       |

| CTimer0                                                                  |     | 0.8                                     | 0.8                                     | 0.8                                     | 0.9                                       | 1.3                                       |

| CTimer1                                                                  |     | 0.8                                     | 0.9                                     | 0.9                                     | 1.0                                       | 1.4                                       |

| CTimer2                                                                  |     | 0.83                                    | 0.85                                    | 0.88                                    | 0.99                                      | 1.3                                       |

| Smart card0                                                              |     | 2.5                                     | 2.5                                     | 2.5                                     | 2.8                                       | 3.7                                       |

| Smart card1                                                              |     | 2.5                                     | 2.5                                     | 2.5                                     | 2.8                                       | 3.7                                       |

| RNG                                                                      |     | 1.4                                     | 1.4                                     | 1.4                                     | 1.5                                       | 2.0                                       |

| OTP controller                                                           |     | 4.0                                     | 4.0                                     | 4.0                                     | 4.5                                       | 6.0                                       |

| SHA                                                                      |     | 1.2                                     | 1.2                                     | 1.2                                     | 1.3                                       | 1.7                                       |

# 11.4 Wake-up process

# **Table 25.** Dynamic characteristic: Typical wake-up times from low power modes $V_{DD} = 3.3 \ V;T_{amb} = 25 \ ^{\circ}C;$ using FRO as the system clock.

| Symbol            | Parameter | Conditions                                                   |        | Min | Typ <u><sup>[1]</sup></u> | Max | Unit |

|-------------------|-----------|--------------------------------------------------------------|--------|-----|---------------------------|-----|------|

| t <sub>wake</sub> | wake-up   | from sleep mode                                              | [2][3] | -   | 2.0                       | -   | μs   |

|                   | time      | from deep-sleep mode; SRAMx powered.                         | [2][5] | -   | 150                       | -   | μS   |

|                   |           | SRAM0, SRAM1, SRAM2,<br>SRAM3, and USB SRAM powered<br>down. |        |     |                           |     |      |

|                   |           | from deep power-down mode;<br>RTC disabled; using RESET pin. | [4][5] | -   | 1.2                       | -   | ms   |

[1] Typical ratings are not guaranteed. The values listed are at room temperature (25 °C), nominal supply voltages.

[2] The wake-up time measured is the time between when a GPIO input pin is triggered to wake the device up from the low power modes and from when a GPIO output pin is set in the interrupt service routine (ISR) wake-up handler.

- [3] FRO enabled, all peripherals off. PLL disabled.

- [4] RTC disabled. Wake up from deep power-down causes the part to go through entire reset process. The wake-up time measured is the time between when the RESET pin is triggered to wake the device up and when a GPIO output pin is set in the reset handler.

[5] FRO disabled.

# **11.5** External memory interface

#### Table 26. Dynamic characteristics: Static external memory interface

$C_L = 10 \text{ pF}$  balanced loading on all pins,  $T_{amb} = -40 \text{ °C}$  to 105 °C,  $V_{DD} = 2.7 \text{ V}$  to 3.6 V. Max EMC clock = 100 MHz. Input slew = 1 ns; SLEW set to fast-mode. Parameters sampled at the 90 % and 10 % level of the rising or falling edge. Excluding delays introduced by external device and PCB; Values based on simulation.

| Symbol                | Parameter[1]                       | Conditions <sup>[1]</sup> |               | Min                                                                                     | Тур | Max                                                          | Unit |

|-----------------------|------------------------------------|---------------------------|---------------|-----------------------------------------------------------------------------------------|-----|--------------------------------------------------------------|------|

| Read cyc              | le parameters                      | 1                         |               | 1                                                                                       |     |                                                              |      |

| t <sub>CSLAV</sub>    | CS LOW to address valid time       | RD <sub>1</sub>           |               | -1.2                                                                                    | -   | 1.6                                                          | ns   |

| t <sub>CSLOEL</sub>   | CS LOW to OE LOW time              | RD <sub>2</sub>           | [2]           | 0.4+ T <sub>cy(clk)</sub> ×<br>WAITOEN                                                  | -   | 0.8+ T <sub>cy(clk)</sub> ×<br>WAITOEN                       | ns   |

| t <sub>CSLBLSL</sub>  | CS LOW to BLS LOW time             | RD <sub>3</sub> ; PB = 1  | <u>[2][6]</u> | -1.6                                                                                    | -   | 0                                                            | ns   |

| t <sub>oeloeh</sub>   | OE LOW to OE HIGH<br>time          | RD <sub>4</sub>           | [2]           | (WAITRD –<br>WAITOEN + 1) ×<br>T <sub>cy(clk)</sub>                                     | -   | 0.3<br>+ (WAITRD –<br>WAITOEN + 1) ×<br>T <sub>cy(clk)</sub> | ns   |

| t <sub>am</sub>       | memory access time                 | RD₅                       | [2][3]        | $\begin{array}{l} -6.7 \\ + (WAITRD - \\ WAITOEN +1) \times \\ T_{cy(clk)} \end{array}$ | -   | -                                                            | ns   |

| t <sub>h(D)</sub>     | data input hold time               | RD <sub>6</sub>           | [2][4]        | -4.8                                                                                    | -   | -                                                            | ns   |

| t <sub>CSHBLSH</sub>  | CS HIGH to BLS HIGH time           | PB = 1                    | <u>[6]</u>    | 0.8                                                                                     | -   | 1.5                                                          | ns   |

| t <sub>CSHOEH</sub>   | CS HIGH to OE HIGH time            |                           | [2]           | 0.5                                                                                     | -   | 0.9                                                          | ns   |

| t <sub>oehanv</sub>   | OE HIGH to address<br>invalid time |                           | [2]           | -0.4                                                                                    | -   | 0                                                            | ns   |

| t <sub>deact</sub>    | deactivation time                  | RD <sub>7</sub>           | [2]           | 0.5                                                                                     | -   | 0.9                                                          | ns   |

| Write cyc             | le parameters                      |                           |               |                                                                                         |     |                                                              |      |

| t <sub>CSLAV</sub>    | CS LOW to address valid time       | WR <sub>1</sub>           |               | 0.1                                                                                     | -   | 0.5                                                          | ns   |

| t <sub>CSLDV</sub>    | CS LOW to data valid time          | WR <sub>2</sub>           |               | 1.0                                                                                     | -   | 2.2                                                          | ns   |

| t <sub>CSLWEL</sub>   | CS LOW to WE LOW time              | WR <sub>3</sub> ; PB =1   | <u>[2][6]</u> | -0.6                                                                                    | -   | 0                                                            | ns   |

| t <sub>CSLBLSL</sub>  | CS LOW to BLS LOW time             | WR <sub>4</sub> ; PB = 1  | <u>[2][6]</u> | -1.2                                                                                    | -   | 0                                                            | ns   |

| twelweh               | WE LOW to WE HIGH time             | WR <sub>5</sub> ; PB =1   | [2][6]        | (WAITWR –<br>WAITWEN + 1) ×<br>T <sub>cy(clk)</sub>                                     | -   | 0.1<br>+ (WAITWR –<br>WAITWEN + 1) ×<br>T <sub>cy(clk)</sub> | ns   |

| t <sub>BLSLBLSH</sub> | BLS LOW to BLS<br>HIGH time        | PB = 1                    | <u>[2][6]</u> | 2.5                                                                                     | -   | 5.5                                                          | ns   |

| t <sub>WEHDNV</sub>   | WE HIGH to data invalid time       | WR <sub>6</sub> ; PB =1   | <u>[2][6]</u> | 1.6                                                                                     | -   | 2.9                                                          | ns   |

| t <sub>WEHEOW</sub>   | WE HIGH to end of write time       | WR <sub>7</sub> ; PB = 1  | [2][5][6]     | 0.6                                                                                     | -   | 0.9                                                          | ns   |

|                       | 1                                  | 1                         |               | 1                                                                                       | 1   | I                                                            | 1    |

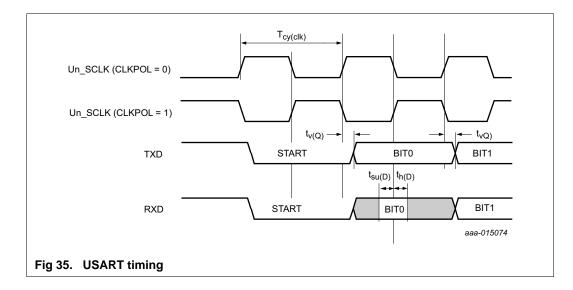

# 11.19 USART interface

The actual USART bit rate depends on the delays introduced by the external trace, the external device, system clock (CCLK), and capacitive loading. Excluding delays introduced by external device and PCB, the maximum supported bit rate for USART master synchronous mode is 24 Mbit/s, and the maximum supported bit rate for USART slave synchronous mode is 12.5 Mbit/s.

#### Table 47. USART dynamic characteristics<sup>[1]</sup>

$T_{amb} = -40$  °C to 105 °C;  $V_{DD} = 1.71$  V to 3.6 V;  $C_L = 30$  pF balanced loading on all pins; Input slew = 1 ns, SLEW setting = standard mode for all pins; Parameters sampled at the 50 % level of the rising or falling edge.

| Symbol             | Parameter                | Conditions                          | Min  | Тур      | Max      | Unit |

|--------------------|--------------------------|-------------------------------------|------|----------|----------|------|

| USART r            | naster (in synchronous r | node) 1.71 V ≤ VDD ≤ 2.7 V          |      | <b>I</b> | I        | I    |

| t <sub>su(D)</sub> | data input set-up time   | CCLK ≤ 100 MHz                      | 21.2 | -        | -        | ns   |

|                    |                          | 100 MHz < CCLK ≤ 180 MHz            | 19.7 | -        | -        | ns   |

| t <sub>h(D)</sub>  | data input hold time     | CCLK ≤ 100 MHz                      | 0    | -        | -        | ns   |

|                    |                          | 100 MHz < CCLK $\leq$ 180 MHz       | 0    | -        | -        | ns   |

| t <sub>v(Q)</sub>  | data output valid time   | CCLK ≤ 100 MHz                      | 0    | -        | 4.9      | ns   |

|                    |                          | 100 MHz < CCLK $\leq$ 180 MHz       | 0    | -        | 4.5      | ns   |

| USART s            | slave (in synchronous mo | ode)1.71 V ≤ VDD ≤ 2.7 V            |      | ·        | <u> </u> | L    |

| t <sub>su(D)</sub> | data input set-up time   | $CCLK \le 100 \text{ MHz}$          | 1.7  | -        | -        | ns   |

|                    |                          | 100 MHz < CCLK $\leq$ 180 MHz       | 1.5  | -        | -        | ns   |

| t <sub>h(D)</sub>  | data input hold time     | $CCLK \le 100 \text{ MHz}$          | 1.2  | -        | -        | ns   |

|                    |                          | 100 MHz < CCLK $\leq$ 180 MHz       | 1.4  | -        | -        | ns   |

| t <sub>v(Q)</sub>  | data output valid time   | $CCLK \le 100 \text{ MHz}$          | 20.2 | -        | 39.5     | ns   |

|                    |                          | 100 MHz < CCLK $\leq$ 180 MHz       | 19.3 | -        | 37.7     | ns   |

| USART r            | naster (in synchronous r | node) 2.7 V $\leq$ VDD $\leq$ 3.6 V |      |          |          |      |

| t <sub>su(D)</sub> | data input set-up time   | $CCLK \le 100 \text{ MHz}$          | 20.5 | -        | -        | ns   |

|                    |                          | 100 MHz < CCLK $\leq$ 180 MHz       | 18.9 | -        | -        | ns   |

| t <sub>h(D)</sub>  | data input hold time     | $CCLK \le 100 \text{ MHz}$          | 0    | -        | -        | ns   |

|                    |                          | 100 MHz < CCLK $\leq$ 180 MHz       | 0    | -        | -        | ns   |

| t <sub>v(Q)</sub>  | data output valid time   | $CCLK \le 100 \text{ MHz}$          | 1.5  | -        | 3.6      | ns   |

|                    |                          | 100 MHz < CCLK $\leq$ 180 MHz       | 1.3  | -        | 3.2      | ns   |

| USART s            | slave (in synchronous m  | ode) 2.7 V $\leq$ VDD $\leq$ 3.6 V  |      |          |          |      |

| t <sub>su(D)</sub> | data input set-up time   | $CCLK \le 100 \text{ MHz}$          | 1.2  | -        | -        | ns   |

|                    |                          | 100 MHz < CCLK $\leq$ 180 MHz       | 1    | -        | -        | ns   |

| t <sub>h(D)</sub>  | data input hold time     | $CCLK \le 100 \text{ MHz}$          | 0    | -        | -        | ns   |

|                    |                          | 100 MHz < CCLK $\leq$ 180 MHz       | 0    | -        | -        | ns   |

| t <sub>v(Q)</sub>  | data output valid time   | $CCLK \le 100 \text{ MHz}$          | 15.2 | -        | 26.1     | ns   |

|                    |                          | 100 MHz < CCLK $\leq$ 180 MHz       | 14.3 | -        | 24.2     | ns   |

[1] Based on characterization; not tested in production.

# LPC546xx

#### 32-bit ARM Cortex-M4 microcontroller

# 11.20 SCTimer/PWM output timing

#### Table 48. SCTimer/PWM output dynamic characteristics

$T_{amb} = -40 \text{ }^{\circ}\text{C}$  to 105  $^{\circ}\text{C}$ ; 1.71 V  $\leq$  V<sub>DD</sub>  $\leq$  3.6 V C<sub>L</sub> = 30 pF. Simulated skew (over process, voltage, and temperature) of any two SCT fixed-pin output signals; sampled at the 90 % and 10 % level of the rising or falling edge; values guaranteed by design.

| Symbol             | Parameter        | Conditions | Min | Тур | Мах | Unit |

|--------------------|------------------|------------|-----|-----|-----|------|

| t <sub>sk(o)</sub> | output skew time | -          | 3.4 | -   | 4.5 | ns   |

# 11.21 USB interface characteristics

#### Table 49. Dynamic characteristics: USB0 pins (full-speed)

$C_L = 50 \text{ pF}$ ;  $R_{pu} = 1.5 \text{ k}\Omega \text{ on } D$ + to  $V_{DD}$ , unless otherwise specified;  $3.0 \text{ V} \le V_{DD} \le 3.6 \text{ V}$ .

| Symbol             | Parameter                                                   | Conditions                              |            | Min   | Тур | Max    | Unit |

|--------------------|-------------------------------------------------------------|-----------------------------------------|------------|-------|-----|--------|------|

| t <sub>r</sub>     | rise time                                                   | 10 % to 90 %                            |            | 4.0   |     | 20     | ns   |

| t <sub>f</sub>     | fall time                                                   | 10 % to 90 %                            |            | 4.0   |     | 20     | ns   |

| t <sub>FRFM</sub>  | differential rise and fall time matching                    | t <sub>r</sub> / t <sub>f</sub>         |            | 90    |     | 111.11 | %    |

| V <sub>CRS</sub>   | output signal crossover voltage                             |                                         |            | 1.3   |     | 2.0    | V    |

| t <sub>FEOPT</sub> | source SE0 interval of EOP                                  | see Figure 36                           |            | 160   |     | 175    | ns   |

| t <sub>FDEOP</sub> | source jitter for differential transition to SE0 transition | see <u>Figure 36</u>                    |            | -2    |     | +5     | ns   |

| t <sub>JR1</sub>   | receiver jitter to next transition                          |                                         |            | -18.5 |     | +18.5  | ns   |

| t <sub>JR2</sub>   | receiver jitter for paired transitions                      | 10 % to 90 %                            |            | -9    | -   | +9     | ns   |

| t <sub>EOPR1</sub> | EOP width at receiver                                       | must reject as<br>EOP; see<br>Figure 36 | [1]        | 40    | -   |        | ns   |

| t <sub>EOPR2</sub> | EOP width at receiver                                       | must accept as<br>EOP; see<br>Figure 36 | <u>[1]</u> | 82    | -   | -      | ns   |

[1] Characterized but not implemented as production test. Guaranteed by design.

# Table 55. ADC sampling times<sup>[1]</sup>

-40 °C  $\leq$   $T_{amb}$  <= 85 °C; 1.71 V  $\leq$  V<sub>DDA</sub>  $\leq$  3.6 V; 1.71 V  $\leq$  V<sub>DD</sub>  $\leq$  3.6 V

| Symbol            | Parameter         | Conditions                                            |        | Min | Тур | Max | Unit |

|-------------------|-------------------|-------------------------------------------------------|--------|-----|-----|-----|------|

| ADC inpu          | ts ADC_5 to ADC_0 | (fast channels); ADC resolution = 1                   | 2 bit  |     |     |     |      |

| t <sub>s</sub>    | sampling time     | Z <sub>o</sub> < 0.05 kΩ                              | [3]    | 20  | -   | -   | ns   |

|                   |                   | 0.05 kΩ <= Z <sub>o</sub> < 0.1 kΩ                    |        | 23  | -   | -   | ns   |

|                   |                   | 0.1 kΩ <= Z <sub>o</sub> < 0.2 kΩ                     |        | 26  | -   | -   | ns   |

|                   |                   | $0.2 \text{ k}\Omega \le Z_0 \le 0.5 \text{ k}\Omega$ |        | 31  | -   | -   | ns   |

|                   |                   | 0.5 kΩ <= $Z_0$ < 1 kΩ                                |        | 47  | -   | -   | ns   |

|                   |                   | 1 kΩ <= Z <sub>o</sub> < 5 kΩ                         |        | 75  | -   | -   | ns   |

| ADC inpu          | ts ADC_5 to ADC_0 | (fast channels); ADC resolution = 1                   | 0 bit  |     |     |     | 1    |

| t <sub>s</sub> sa | sampling time     | Z <sub>o</sub> < 0.05 kΩ                              | [3]    | 15  | -   | -   | ns   |

|                   |                   | 0.05 kΩ <= Z <sub>o</sub> < 0.1 kΩ                    |        | 18  | -   | -   | ns   |

|                   |                   | 0.1 kΩ <= $Z_0$ < 0.2 kΩ                              |        | 20  | -   | -   | ns   |

|                   |                   | $0.2 \text{ k}\Omega \le Z_0 \le 0.5 \text{ k}\Omega$ |        | 24  | -   | -   | ns   |

|                   |                   | 0.5 kΩ <= $Z_0$ < 1 kΩ                                |        | 38  | -   | -   | ns   |

|                   |                   | 1 kΩ <= Z <sub>o</sub> < 5 kΩ                         |        | 62  | -   | -   | ns   |

| ADC inpu          | ts ADC_5 to ADC_0 | (fast channels); ADC resolution = 8                   | bit    |     |     |     | 1    |