Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                            |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 220MHz                                                                     |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, UART/USART, USB                   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT          |

| Number of I/O              | 145                                                                        |

| Program Memory Size        | 512KB (512K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 16K x 8                                                                    |

| RAM Size                   | 200K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                               |

| Data Converters            | A/D 12x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 180-TFBGA                                                                  |

| Supplier Device Package    | 180-TFBGA (12x12)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc54628j512et180e |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

LPC546xx

| Symbol             | 100-pin, TFBGA | 180-pin, TFBGA | 208-pin, LQFP | 100-pin, LQFP |     | Reset state [1] | Type       | Description                                                                                                                                                     |

|--------------------|----------------|----------------|---------------|---------------|-----|-----------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIO0_30            | A2             | A2             | 200           | 95            | [2] | PU              | I/O        | PIO0_30 — General-purpose digital input/output pin.                                                                                                             |

|                    |                |                |               |               |     |                 |            | <b>Remark:</b> In ISP mode, this pin is set to the Flexcomm 0 USART TXD function.                                                                               |

|                    |                |                |               |               |     |                 | I/O        | FC0_TXD_SCL_MISO — Flexcomm 0: USART transmitter,<br>I2C clock, SPI master-in/slave-out data.                                                                   |

|                    |                |                |               |               |     |                 |            | R — Reserved.                                                                                                                                                   |

|                    |                |                |               |               |     |                 | 0          | CT0_MAT0 — Match output 0 from Timer 0.                                                                                                                         |

|                    |                |                |               |               |     |                 | 0          | SCT0_OUT9 — SCTimer/PWM output 9.                                                                                                                               |

|                    |                |                |               |               |     |                 | 0          | TRACEDATA[1] — Trace data bit 1.                                                                                                                                |

| PIO0_31/<br>ADC0_5 | К3             | M5             | 55            | 28            | [4] | PU              | I/O;<br>AI | <b>PIO0_31/ADC0_5</b> — General-purpose digital input/output pin.<br>ADC input channel 5 if the DIGIMODE bit is set to 0 in the<br>IOCON register for this pin. |

|                    |                |                |               |               |     |                 | I/O        | FC0_CTS_SDA_SSEL0 — Flexcomm 0: USART clear-to-send, I2C data I/O, SPI Slave Select 0.                                                                          |

|                    |                |                |               |               |     |                 | I/O        | <b>SD_D[2] —</b> SD/MMC data 2.                                                                                                                                 |

|                    |                |                |               |               |     |                 | 0          | CT0_MAT1 — Match output 1 from Timer 0.                                                                                                                         |

|                    |                |                |               |               |     |                 | 0          | SCT0_OUT3 — SCTimer/PWM output 3.                                                                                                                               |

|                    |                |                |               |               |     |                 | 0          | TRACEDATA[0] — Trace data bit 0.                                                                                                                                |

| PIO1_0/<br>ADC0_6  | J3             | N3             | 56            | 29            | [4] | PU              | I/O;<br>Al | <b>PIO1_0/ADC0_6</b> — General-purpose digital input/output pin.<br>ADC input channel 6 if the DIGIMODE bit is set to 0 in the<br>IOCON register for this pin.  |

|                    |                |                |               |               |     |                 | I/O        | FC0_RTS_SCL_SSEL1 — Flexcomm 0: USART request-to-send, I2C clock, SPI slave select 1.                                                                           |

|                    |                |                |               |               |     |                 | I/O        | <b>SD_D[3]</b> — SD/MMC data 3.                                                                                                                                 |

|                    |                |                |               |               |     |                 | I          | CT0_CAP2 — Capture 2 input to Timer 0.                                                                                                                          |

|                    |                |                |               |               |     |                 | I          | SCT0_GPI4 — Pin input 4 to SCTimer/PWM.                                                                                                                         |

|                    |                |                |               |               |     |                 | 0          | TRACECLK — Trace clock.                                                                                                                                         |

| PIO1_1             | J10            | K12            | 109           | 55            | [2] | PU              | I/O        | <b>PIO1_1/</b> — General-purpose digital input/output pin.                                                                                                      |

|                    |                |                |               |               |     |                 | I/O        | <b>FC3_RXD_SDA_MOSI</b> — Flexcomm 3: USART receiver, I2C data I/O, SPI master-out/slave-in data.                                                               |

|                    |                |                |               |               |     |                 |            | R — Reserved.                                                                                                                                                   |

|                    |                |                |               |               |     |                 | I          | CT0_CAP3 — Capture 3 input to Timer 0.                                                                                                                          |

|                    |                |                |               |               |     |                 | I          | SCT0_GPI5 — Pin input 5 to SCTimer/PWM.                                                                                                                         |

|                    |                |                |               |               |     |                 |            | R — Reserved.                                                                                                                                                   |

|                    |                |                |               |               |     |                 |            | R — Reserved.                                                                                                                                                   |

|                    |                |                |               |               |     |                 | I          | <b>USB1_OVERCURRENTN</b> — USB1 bus overcurrent indicator (active low).                                                                                         |

# Table 4. Pin description ...continued

| Symbol | 100-pin, TFBGA | 180-pin, TFBGA | 208-pin, LQFP | 100-pin, LQFP |          | Reset state [1] | Type     | Description                                                                                                 |

|--------|----------------|----------------|---------------|---------------|----------|-----------------|----------|-------------------------------------------------------------------------------------------------------------|

| PIO2_2 | -              | C3             | 4             | -             | [2]      | PU              | I/O      | PIO2_2 — General-purpose digital input/output pin.                                                          |

|        |                |                |               |               |          |                 | I        | <b>ENET_CRS</b> — Ethernet Carrier Sense (MII interface) or                                                 |

|        |                |                |               |               |          |                 |          | Ethernet                                                                                                    |

|        |                |                |               |               |          |                 | 1/0      | Carrier Sense/Data Valid (RMII interface).<br>FC3_SSEL3 — Flexcomm 3: SPI slave select 3.                   |

|        |                |                |               |               |          |                 | 1/O<br>O | SCT0_OUT6 — SCTimer/PWM output 6.                                                                           |

|        |                |                |               |               |          |                 | 0        | CT1_MAT1 — Match output 1 from Timer 1.                                                                     |

|        |                | B1             | 7             |               | [2]      | PU              | 0<br>I/O |                                                                                                             |

| PIO2_3 | -              | ы              | 1             | -             | <u> </u> | FU              | 0        | PIO2_3 — General-purpose digital input/output pin.<br>ENET_TXD2 — Ethernet transmit data 2 (MII interface). |

|        |                |                |               |               |          |                 | 0        | SD_CLK — SD/MMC clock.                                                                                      |

|        |                |                |               |               |          |                 | 0<br>1/0 | FC1_RXD_SDA_MOSI — Flexcomm 1: USART receiver, I2C                                                          |

|        |                |                |               |               |          |                 | 1/0      | data I/O, SPI master-out/slave-in data.                                                                     |

|        |                |                |               |               |          |                 | 0        | CT2_MAT0 — Match output 0 from Timer 2.                                                                     |

| PIO2_4 | -              | D3             | 9             | -             | [2]      | PU              | I/O      | <b>PIO2_4</b> — General-purpose digital input/output pin.                                                   |

|        |                |                |               |               |          |                 | 0        | <b>ENET_TXD3</b> — Ethernet transmit data 3 (MII interface).                                                |

|        |                |                |               |               |          |                 | I/O      | <b>SD_CMD</b> — SD/MMC card command I/O.                                                                    |

|        |                |                |               |               |          |                 | I/O      | FC1_TXD_SCL_MISO — Flexcomm 1: USART transmitter,<br>I2C clock, SPI master-in/slave-out data.               |

|        |                |                |               |               |          |                 | 0        | CT2_MAT1 — Match output 1 from Timer 2.                                                                     |

| PIO2_5 | -              | C1             | 12            | -             | [2]      | PU              | I/O      | PIO2_5 — General-purpose digital input/output pin.                                                          |

|        |                |                |               |               |          |                 | 0        | <b>ENET_TX_ER</b> — Ethernet Transmit Error (MII interface).                                                |

|        |                |                |               |               |          |                 | 0        | SD_POW_EN — SD/MMC card power enable                                                                        |

|        |                |                |               |               |          |                 | I/O      | FC1_CTS_SDA_SSEL0 — Flexcomm 1: USART clear-to-send, I2C data I/O, SPI Slave Select 0.                      |

|        |                |                |               |               |          |                 | 0        | CT1_MAT2 — Match output 2 from Timer 1.                                                                     |

| PIO2_6 | -              | F3             | 17            | -             | [2]      | PU              | I/O      | PIO2_6 — General-purpose digital input/output pin.                                                          |

|        |                |                |               |               |          |                 | I        | <b>ENET_TX_CLK</b> — Ethernet Transmit Clock (MII interface).                                               |

|        |                |                |               |               |          |                 | I/O      | <b>SD_D[0]</b> — SD/MMC data 0.                                                                             |

|        |                |                |               |               |          |                 | I/O      | FC1_RTS_SCL_SSEL1 — Flexcomm 1: USART request-to-send, I2C clock, SPI slave select 1.                       |

|        |                |                |               |               |          |                 | I        | CT0_CAP0 — Capture input 0 to Timer 0.                                                                      |

| PIO2_7 | -              | J2             | 29            | -             | [2]      | PU              | I/O      | PIO2_7 — General-purpose digital input/output pin.                                                          |

|        |                |                |               |               |          |                 | I        | <b>ENET_COL</b> — Ethernet Collision detect (MII interface).                                                |

|        |                |                |               |               |          |                 | I/O      | <b>SD_D(1)</b> — SD/MMC data 1.                                                                             |

|        |                |                |               |               |          |                 | I        | <b>FREQME_GPIO_CLK_B</b> — Frequency Measure pin clock input B.                                             |

|        |                |                |               |               |          |                 | I        | CT0_CAP1 — Capture input 1 to Timer 0.                                                                      |

LPC546xx

| Table 4. | Pin description | continued |

|----------|-----------------|-----------|

|----------|-----------------|-----------|

| Symbol     | 100-pin, TFBGA | 180-pin, TFBGA | 208-pin, LQFP | 100-pin, LQFP |        | Reset state [1] | Type | Description                                                                                             |

|------------|----------------|----------------|---------------|---------------|--------|-----------------|------|---------------------------------------------------------------------------------------------------------|

| PIO5_7     | -              | -              | 171           | -             | [2]    | PU              | I/O  | <b>PIO5_7</b> — General-purpose digital input/output pin.                                               |

|            |                |                |               |               |        |                 | I    | <b>SCT0_GPI2</b> — Pin input 2 to SCTimer/PWM.                                                          |

|            |                |                |               |               |        |                 | I/O  | <b>MCLK</b> — MCLK input or output for I2S and/or digital microphone.                                   |

|            |                |                |               |               |        |                 | I/O  | <b>FC5_RXD_SDA_MOSI</b> — Flexcomm 5: USART receiver, I2C data I/O, SPI master-out/slave-in data.       |

|            |                |                |               |               |        |                 | 0    | SCT0_OUT6 — SCTimer/PWM output 6.                                                                       |

|            |                |                |               |               |        |                 | 0    | TRACEDATA[1] — Trace data bit 1.                                                                        |

|            |                |                |               |               |        |                 | 0    | <b>EMC_A[23]</b> — External memory interface address 23.                                                |

| PIO5_8     | -              | -              | 175           | -             | [2]    | PU              | I/O  | PIO5_8 — General-purpose digital input/output pin.                                                      |

|            |                |                |               |               |        |                 | I    | SCT0_GPI3 — Pin input 3 to SCTimer/PWM.                                                                 |

|            |                |                |               |               |        |                 | 0    | <b>PDM0_CLK</b> — Clock for PDM interface 0, for digital microphone.                                    |

|            |                |                |               |               |        |                 | I/O  | FC5_TXD_SCL_MISO — Flexcomm 5: USART transmitter, I2C clock, SPI master-in/slave-out data.              |

|            |                |                |               |               |        |                 | 0    | SCT0_OUT7 — SCTimer/PWM output 7.                                                                       |

|            |                |                |               |               |        |                 | 0    | TRACEDATA[2] — Trace data bit 2.                                                                        |

|            |                |                |               |               |        |                 | 0    | EMC_A[24] — External memory interface address 24.                                                       |

| PIO5_9     | -              | -              | 179           | -             | [2]    | PU              | I/O  | PIO5_9 — General-purpose digital input/output pin.                                                      |

|            |                |                |               |               |        |                 | I    | SCT0_GPI4 — Pin input 4 to SCTimer/PWM.                                                                 |

|            |                |                |               |               |        |                 | I    | <b>PDM0_DATA</b> — Data for PDM interface 0 (digital microphone).                                       |

|            |                |                |               |               |        |                 | I/O  | FC5_CTS_SDA_SSEL0 — Flexcomm 5: USART clear-to-send, I2C data I/O, SPI Slave Select 0.                  |

|            |                |                |               |               |        |                 | 0    | SCT0_OUT8 — SCTimer/PWM output 8.                                                                       |

|            |                |                |               |               |        |                 | 0    | TRACEDATA[3] — Trace data bit 3.                                                                        |

|            |                |                |               |               |        |                 | 0    | EMC_A[25] — External memory interface address 25.                                                       |

| PIO5_10    | -              | -              | 168           | -             | [2]    | PU              | I/O  | PIO5_10 — General-purpose digital input/output pin.                                                     |

|            |                |                |               |               |        |                 | I    | SCT0_GPI5 — Pin input 5 to SCTimer/PWM.                                                                 |

|            |                |                |               |               |        |                 |      | R — Reserved.                                                                                           |

|            |                |                |               |               |        |                 | I/O  | FC5_RTS_SCL_SSEL1 — Flexcomm 5: USART request-to-send, I2C clock, SPI slave select 1.                   |

|            |                |                |               |               |        |                 | 0    | SCT0_OUT9 — SCTimer/PWM output 9.                                                                       |

|            |                |                |               |               |        |                 | I    | UTICK_CAP3 — Micro-tick timer capture input 3.                                                          |

| USB1_AVSSC | D1             | F2             | 20            | 6             |        |                 |      | USB1 analog 3.3 V ground.                                                                               |

| USB1_REXT  | B1             | F1             | 21            | 7             |        |                 |      | USB1 analog signal for reference resistor, 12.4 k $\Omega$ +/-1%                                        |

| USB1_ID    | C1             | G1             | 22            | 8             |        |                 |      | Indicates to the transceiver whether connected as an A-device (USB1_ID LOW) or B-device (USB1_ID HIGH). |

| USB1_VBUS  | D3             | G2             | 23            | 9             | [6][8] |                 | I/O  | VBUS pin (power on USB cable).                                                                          |

- [1] PU = input mode, pull-up enabled (pull-up resistor pulls up pin to V<sub>DD</sub>). Z = high impedance; pull-up or pull-down disabled, AI = analog input, I = input, O = output, F = floating. Reset state reflects the pin state at reset without boot code operation. For pin states in the different power modes, see Section 6.2.2 "Pin states in different power modes". For termination on unused pins, see Section 6.2.1 "Termination of unused pins".

- [2] 5 V tolerant pad with programmable glitch filter (5 V tolerant if V<sub>DD</sub> present; if V<sub>DD</sub> not present, do not exceed 3.6 V); provides digital I/O functions with TTL levels and hysteresis; normal drive strength. See <u>Figure 44</u>. Pulse width of spikes or glitches suppressed by input filter is from 3 ns to 16 ns (simulated value).

- [3] True open-drain pin. I2C-bus pins compliant with the I2C-bus specification for I2C standard mode, I2C Fast-mode, and I2C Fast-mode Plus. The pin requires an external pull-up to provide output functionality. When power is switched off, this pin is floating and does not disturb the I2C lines. Open-drain configuration applies to all functions on this pin.

- [4] 5 V tolerant pin providing standard digital I/O functions with configurable modes, configurable hysteresis, and analog input. When configured as an analog input, the digital section of the pin is disabled, and the pin is not 5 V tolerant.

- [5] Reset pad.5 V tolerant pad with glitch filter with hysteresis. Pulse width of spikes or glitches suppressed by input filter is from 3 ns to 20 ns (simulated value)

- [6] 5 V tolerant transparent analog pad.

- [7] The oscillator input pin (XTALIN) cannot be driven by an external clock. Must connect a crystal between XTALIN and XTALOUT.

- [8] VBUS must be connected to supply voltage when using the USB peripheral.

# 6.2.1 Termination of unused pins

<u>Table 5</u> shows how to terminate pins that are **not** used in the application. In many cases, unused pins should be connected externally or configured correctly by software to minimize the overall power consumption of the part.

Unused pins with GPIO function should be configured as outputs set to LOW with their internal pull-up disabled. To configure a GPIO pin as output and drive it LOW, select the GPIO function in the IOCON register, select output in the GPIO DIR register, and write a 0 to the GPIO PORT register for that pin. Disable the pull-up in the pin's IOCON register.

In addition, it is recommended to configure all GPIO pins that are not bonded out on smaller packages as outputs driven LOW with their internal pull-up disabled.

| Pin                         | Default<br>state <sup>[1]</sup> | Recommended termination of unused pins                                                                                                                                                                         |

|-----------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET                       | I; PU                           | The RESET pin can be left unconnected if the application does not use it.                                                                                                                                      |

| all PIOn_m (not open-drain) | I; PU                           | Can be left unconnected if driven LOW and configured as GPIO output with pull-up disabled by software.                                                                                                         |

| PIOn_m (I2C open-drain)     | IA                              | Can be left unconnected if driven LOW and configured as GPIO output by software.                                                                                                                               |

| RTCXIN                      | -                               | Connect to ground. When grounded, the RTC oscillator is disabled.                                                                                                                                              |

| RTCXOUT                     | -                               | Can be left unconnected.                                                                                                                                                                                       |

| XTALIN                      | -                               | Connect to ground. When grounded, the RTC oscillator is disabled.                                                                                                                                              |

| XTALOUT                     | -                               | Can be left unconnected.                                                                                                                                                                                       |

| VREFP                       | -                               | Tie to VDD.                                                                                                                                                                                                    |

| VREFN                       | -                               | Tie to VSS.                                                                                                                                                                                                    |

| VDDA                        | -                               | Tie to VDD.                                                                                                                                                                                                    |

| VSSA                        | -                               | Tie to VSS.                                                                                                                                                                                                    |

| VBAT                        | -                               | Tie to VDD.                                                                                                                                                                                                    |

| USBn_DP                     | F                               | Can be left unconnected. If USB interface is not used, pin can be left unconnected except in deep power-down mode where it must be externally pulled low. When the USB PHY is disabled, the pins are floating. |

Table 5. Termination of unused pins

# 7.17.1.2 USB0 host controller

The host controller enables full- and low-speed data exchange with USB devices attached to the bus. It consists of register interface, serial interface engine and DMA controller. The register interface complies with the Open Host Controller Interface (OHCI) specification.

## Features

- OHCI compliant.

- Two downstream ports.

# 7.17.2 High-speed USB Host/Device interface (USB1)

The Universal Serial Bus (USB) is a 4-wire bus that supports communication between a host and one or more (up to 127) peripherals. The host controller allocates the USB bandwidth to attached devices through a token-based protocol. The bus supports hot plugging and dynamic configuration of the devices. All transactions are initiated by the host controller.

# 7.17.2.1 USB1 device controller

The device controller enables 480 Mbit/s data exchange with a USB host controller. It consists of a register interface, serial interface engine, endpoint buffer memory. The serial interface engine decodes the USB data stream and writes data to the appropriate endpoint buffer. The status of a completed USB transfer or error condition is indicated via status registers. An interrupt is also generated if enabled.

### Features

- Fully compliant with USB 2.0 Specification (high speed).

- Supports 8 physical (16 logical) endpoints with up to 8 kB endpoint buffer RAM.

- Supports Control, Bulk, Interrupt and Isochronous endpoints.

- Scalable realization of endpoints at run time.

- Endpoint Maximum packet size selection (up to USB maximum specification) by software at run time.

- While USB is in the Suspend mode, the LPC546xx can enter one of the reduced power modes and wake up on USB activity.

- Double buffer implementation for Bulk and Isochronous endpoints.

# 7.17.2.2 USB1 host controller

The host controller enables high speed data exchange with USB devices attached to the bus. It consists of register interface and serial interface engine. The register interface complies with the Enhanced Host Controller Interface (EHCI) specification.

# Features

- EHCI compliant.

- Two downstream ports.

- Supports per-port power switching.

# 7.18.1.1 Features

- AHB master interface to access frame buffer.

- Setup and control via a separate AHB slave interface.

- Dual 16-deep programmable 64-bit wide FIFOs for buffering incoming display data.

- Supports single and dual-panel monochrome Super Twisted Nematic (STN) displays with 4-bit or 8-bit interfaces.

- Supports single and dual-panel color STN displays.

- Supports Thin Film Transistor (TFT) color displays.

- Programmable display resolution including, but not limited to:  $320 \times 200$ ,  $320 \times 240$ ,  $640 \times 200$ ,  $640 \times 240$ ,  $640 \times 480$ ,  $800 \times 600$ , and  $1024 \times 768$ .

- Hardware cursor support for single-panel displays.

- 15 gray-level monochrome, 3375 color STN, and 32 K color palettized TFT support.

- 1, 2, or 4 bits-per-pixel (bpp) palettized displays for monochrome STN.

- 1, 2, 4, or 8 bpp palettized color displays for color STN and TFT.

- 16 bpp true-color non-palettized for color STN and TFT.

- 24 bpp true-color non-palettized for color TFT.

- Programmable timing for different display panels.

- 256 entry, 16-bit palette RAM, arranged as a  $128 \times 32$ -bit RAM.

- Frame, line, and pixel clock signals.

- AC bias signal for STN, data enable signal for TFT panels.

- Supports little and big-endian, and Windows CE data formats.

- LCD panel clock may be generated from the peripheral clock, or from a clock input pin.

# 7.18.2 SD/MMC card interface

The SD/MMC card interface supports the following modes to control:

# 7.18.2.1 Features

- Secure Digital memory (SD version 1.1).

- Secure Digital I/O (SDIO version 2.0).

- Consumer Electronics Advanced Transport Architecture (CE-ATA version 1.1).

- MultiMedia Cards (MMC version 4.1).

- Supports up to a maximum of 50 MHz of interface frequency.

# 7.18.3 External memory controller

The LPC546xx EMC is an ARM PrimeCell MultiPort Memory Controller peripheral offering support for asynchronous static memory devices such as RAM, ROM, and flash. In addition, it can be used as an interface with off-chip memory-mapped devices and peripherals. The EMC is an Advanced Microcontroller Bus Architecture (AMBA) compliant peripheral.

# 7.23.2 SHA-1 and SHA-2

The Hash peripheral is used to perform SHA-1 and SHA-2 (256) based hashing. A hash takes an arbitrarily large message or image and forms a relatively small fixed size "unique" number called a digest. The data is fed by words from the processor, DMA, or hosted access; the words are converted from little-endian (ARM standard) to big-endian (SHA standard) by the block.

### 7.23.2.1 Features

- Used with an HMAC to support a challenge/response or to validate a message.

- Can be used to verify external memory that has not been compromised.

# 7.24 Code security (enhanced Code Read Protection - eCRP)

eCRP is a mechanism that allows the user to enable different features in the security system. The features are specified using a combination of OTP and flash values. Some levels are only controlled by either flash or OTP, but the majority have dual control. The overlap allows higher security by specifying access using OTP bits, which cannot be changed (except to increase security) while allowing customers who are less concerned about security the ability to change levels in the flash image.

eCRP is calculated by reading the ECRP from the flash boot sector (offset 0x0000 0020) and then masking it with the value read from OTP. The OTP bits are more restrictive (that is, disable access) than equivalent values in flash. Certain aspects of eCRP are only specified in the OTP (that is, Mass Erase disable), while others are only specified in flash (that is, Sector Protection count).

For Dual Enhanced images, eCRP is calculated by reading the eCRP from the bootable image sector. The bootable image is defined as the highest revision image that passes the required validation methods.

# 7.25 Emulation and debugging

Debug and trace functions are integrated into the ARM Cortex-M4. Serial wire debug and trace functions are supported. The ARM Cortex-M4 is configured to support up to eight breakpoints and four watch points.

The ARM SYSREQ reset is supported and causes the processor to reset the peripherals, execute the boot code, restart from address 0x0000 0000, and break at the user entry point.

The SWD pins are multiplexed with other digital I/O pins. On reset, the pins assume the SWD functions by default.

<u>Table 19</u> shows the typical peripheral power consumption measured on a typical sample at Tamb = 25 °C and VDD = 3.3 V. The supply current per peripheral is measured as the difference in supply current between the peripheral block enabled and the peripheral block disabled using ASYNCAPBCLKCTRL, AHBCLKCTRL0/1/2, and PDRUNCFG0/1

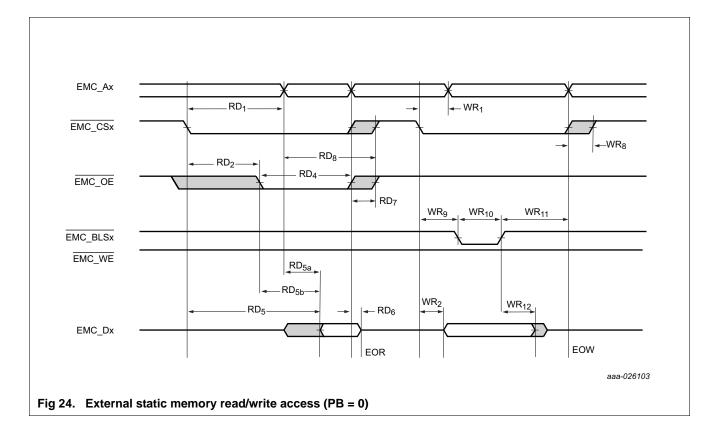

- [2] T<sub>cy(clk)</sub> = 1/EMC\_CLK (see UM10912 LPC546xx manual).

- [3] Latest of address valid, EMC\_CSx LOW, EMC\_OE LOW, EMC\_BLSx LOW (PB = 1).

- [4] After End Of Read (EOR): Earliest of EMC\_CSx HIGH, EMC\_OE HIGH, EMC\_BLSx HIGH (PB = 1), address invalid.

- [5] End Of Write (EOW): Earliest of address invalid, EMC\_CSx HIGH, EMC\_BLSx HIGH (PB = 1).

- [6] The byte lane state bit, PB, enables different types of memory to be connected (see *the* STATICCONFIG[0:3] register in the UM10912 LPC546xx manual).

# Table 30. Dynamic characteristics: Dynamic external memory interface programmable clock delays (CMDDLY, FBCLKDLY)

$T_{amb} = -40$  °C to 105 °C,  $V_{DD} = 2.7$  V to 3.6 V.Values guaranteed by design.  $t_{cmddly}$  is programmable delay value for EMC command outputs in command delayed mode;  $t_{fbdly}$  is programmable delay value for the feedback clock that controls input data sampling.

| Symbols                                  | Parameter  | Five bit value for each delay in EMCDLYCTL <sup>[1]</sup> | Min  | Тур  | Max  | Unit |

|------------------------------------------|------------|-----------------------------------------------------------|------|------|------|------|

| t <sub>cmddly</sub> , t <sub>fbdly</sub> | delay time | b00000                                                    | 0.41 | 0.66 | 0.77 | ns   |

|                                          |            | b00001                                                    | 0.52 | 0.85 | 1.03 | ns   |

|                                          |            | b00010                                                    | 0.69 | 1.11 | 1.3  | ns   |

|                                          |            | b00011                                                    | 0.8  | 1.3  | 1.56 | ns   |

|                                          |            | b00100                                                    | 0.95 | 1.53 | 1.77 | ns   |

|                                          |            | b00101                                                    | 1.06 | 1.72 | 2.03 | ns   |

|                                          |            | b00110                                                    | 1.23 | 1.98 | 2.3  | ns   |

|                                          |            | b00111                                                    | 1.34 | 2.17 | 2.56 | ns   |

|                                          |            | b01000                                                    | 1.45 | 2.3  | 2.67 | ns   |

|                                          |            | b01001                                                    | 1.56 | 2.49 | 2.93 | ns   |

|                                          |            | b01010                                                    | 1.73 | 2.75 | 3.2  | ns   |

|                                          |            | b01011                                                    | 1.84 | 2.94 | 3.46 | ns   |

|                                          |            | b01100                                                    | 1.99 | 3.17 | 3.67 | ns   |

|                                          |            | b01101                                                    | 2.1  | 3.36 | 3.93 | ns   |

|                                          |            | b01110                                                    | 2.27 | 3.62 | 4.2  | ns   |

|                                          |            | b01111                                                    | 2.38 | 3.81 | 4.46 | ns   |

|                                          |            | b10000                                                    | 2.45 | 3.86 | 4.46 | ns   |

|                                          |            | b10001                                                    | 2.56 | 4.05 | 4.72 | ns   |

|                                          |            | b10010                                                    | 2.73 | 4.31 | 4.99 | ns   |

|                                          |            | b10011                                                    | 2.84 | 4.5  | 5.25 | ns   |

|                                          |            | b10100                                                    | 2.99 | 4.73 | 5.46 | ns   |

|                                          |            | b10101                                                    | 3.1  | 4.92 | 5.72 | ns   |

|                                          |            | b10110                                                    | 3.27 | 5.18 | 5.99 | ns   |

|                                          |            | b10111                                                    | 3.38 | 5.37 | 6.25 | ns   |

|                                          |            | b11000                                                    | 3.49 | 5.5  | 6.36 | ns   |

|                                          |            | b11001                                                    | 3.6  | 5.69 | 6.62 | ns   |

|                                          |            | b11010                                                    | 3.77 | 5.95 | 6.89 | ns   |

|                                          |            | b11011                                                    | 3.88 | 6.14 | 7.15 | ns   |

|                                          |            | b11100                                                    | 4.03 | 6.37 | 7.36 | ns   |

|                                          |            | b11101                                                    | 4.14 | 6.56 | 7.62 | ns   |

|                                          |            | b11110                                                    | 4.31 | 6.82 | 7.89 | ns   |

|                                          |            | b11111                                                    | 4.42 | 7.01 | 8.15 | ns   |

[1] The programmable delay blocks are controlled by the EMCDLYCTL register in the EMC register block. All delay times are incremental delays for each element starting from delay block 0. See the *LPC546xx. user manual* for details.

# 11.7 USB PLL (PLL1)

### Table 33. PLL1 lock times and current

$T_{amb} = -40 \text{ }^{\circ}\text{C}$  to +105  $^{\circ}\text{C}$ , unless otherwise specified.  $V_{DD} = 1.71 \text{ V}$  to 3.6 V

| Symbol                  | Parameter            | Conditions                         |            | Min | Тур | Max | Unit |

|-------------------------|----------------------|------------------------------------|------------|-----|-----|-----|------|

| PLL1 configur           | ation: input frequen | cy 12 MHz; output frequency 48 MHz |            |     |     |     |      |

| t <sub>lock(PLL1)</sub> | PLL1 lock time       |                                    | <u>[1]</u> | -   | 7.4 | -   | μS   |

| I <sub>DD(PLL1)</sub>   | PLL1 current         | When locked                        | [1][2]     | -   | 260 | -   | μA   |

[1] Data based on characterization results, not tested in production.

[2] PLL current measured using lowest CCO frequency to obtain the desired output frequency.

| Symbol                 | Parameter                                        | Conditions                   |               | Min    | Тур      | Max  | Unit     |

|------------------------|--------------------------------------------------|------------------------------|---------------|--------|----------|------|----------|

| Reference              | e clock input                                    |                              | -             |        |          |      |          |

| F <sub>in</sub>        | input frequency                                  |                              |               | 1      | -        | 25   | MHz      |

| Clock out              | put                                              | ÷                            |               |        |          |      | <b>i</b> |

| f <sub>o</sub>         | output frequency                                 | for PLL1 clkout output       | [2]           | 9.75   | -        | 160  | MHz      |

| d <sub>o</sub>         | output duty cycle                                | for PLL1 clkout output       |               | 45     | -        | 55   | %        |

| f <sub>CCO</sub>       | CCO frequency                                    |                              |               | 156    | -        | 320  | MHz      |

| Dynamic                | parameters at f <sub>out</sub> = f <sub>CC</sub> | <sub>o</sub> = 320 MHz; stan | dard ba       | andwid | th setti | ings |          |

| J <sub>pp-period</sub> | peak-to-peak, period<br>jitter                   | f <sub>ref</sub> = 4 MHz     | <u>[3][4]</u> | -      | -        | 300  | ps       |

### Table 34. Dynamic characteristics of the PLL1<sup>[1]</sup>

[1] Data based on simulation, not tested in production.

[2] Excluding under- and overshoot which may occur when the PLL is not in lock.

- [3] Actual jitter dependent on amplitude and spectrum of substrate noise.

- [4] Input clock coming from a crystal oscillator with less than 250 ps peak-to-peak period jitter.

# 11.8 Audio PLL (PLL2)

#### Table 35. PLL2 lock times and current

$T_{amb} = -40$  °C to +105 °C, unless otherwise specified.  $V_{DD} = 1.71$  V to 3.6 V

| Symbol                  | Parameter          | Conditions                    |        | Min   | Тур | Max | Unit |

|-------------------------|--------------------|-------------------------------|--------|-------|-----|-----|------|

| PLL2 conf               | iguration: input f | requency 12 MHz; output frequ | iency  | 100 M | Hz  |     | -    |

| t <sub>lock(PLL2)</sub> | PLL2 lock time     |                               | [1]    | -     | -   | 96  | μS   |

| I <sub>DD(PLL2)</sub>   | PLL2 current       | when locked                   | [1][2] | -     | -   | 2.0 | mA   |

| PLL2 conf               | iguration: input f | requency 12 MHz; output frequ | iency  | 100 M | Hz  |     |      |

| t <sub>lock(PLL2)</sub> | PLL2 lock time     |                               | [1]    | -     | -   | 108 | μS   |

| I <sub>DD(PLL2)</sub>   | PLL2 current       | when locked                   | [1][2] | -     | -   | 1.6 | mA   |

[1] Data based on characterization results, not tested in production.

[2] PLL current measured using lowest CCO frequency to obtain the desired output frequency.

# 11.15 SPI interfaces

The actual SPI bit rate depends on the delays introduced by the external trace, the external device, system clock (CCLK), and capacitive loading. Excluding delays introduced by external device and PCB, the maximum supported bit rate for SPI master mode is 48 Mbit/s, and the maximum supported bit rate for SPI slave mode is 14 Mbit/s.

## Table 43. SPI dynamic characteristics<sup>[1]</sup>

$T_{amb} = -40 \text{ }^{\circ}\text{C}$  to 105  $\text{}^{\circ}\text{C}$ ; 1.71 V  $\leq$  V<sub>DD</sub>  $\leq$  3.6 V;  $C_L = 30 \text{ pF}$  balanced loading on all pins; Input slew = 1 ns, SLEW setting = standard mode for all pins;. Parameters sampled at the 50 % level of the rising or falling edge.

| Symbol            | Parameter                                      | Conditions                    | Min  | Тур      | Max  | Unit |

|-------------------|------------------------------------------------|-------------------------------|------|----------|------|------|

| SPI mas           | ter 1.71 V $\leq$ V <sub>DD</sub> $\leq$ 2.7 V | 1                             |      |          |      | I    |

| t <sub>DS</sub>   | data set-up time                               | CCLK ≤ 100 MHz                | 2.2  | -        | -    | ns   |

|                   |                                                | 100 MHz < CCLK $\leq$ 180 MHz | 1.9  | -        | -    | ns   |

| t <sub>DH</sub>   | DH data hold time                              | CCLK ≤ 100 MHz                | 6.3  | -        | -    | ns   |

|                   |                                                | 100 MHz < CCLK $\leq$ 180 MHz | 6.7  | -        | -    | ns   |

| t <sub>v(Q)</sub> | a) data output valid time                      | CCLK ≤ 100 MHz                | 2.6  | -        | 5.0  | ns   |

|                   |                                                | 100 MHz < CCLK $\leq$ 180 MHz | 0.3  | -        | 4.7  | ns   |

| SPI slav          | e 1.71 V $\leq$ V <sub>DD</sub> $\leq$ 2.7 V   |                               |      |          |      |      |

| t <sub>DS</sub>   | data set-up time                               | CCLK ≤ 100 MHz                | 1.1  | -        | -    | ns   |

|                   |                                                | 100 MHz < CCLK $\leq$ 180 MHz | 0.9  | -        | -    | ns   |

| t <sub>DH</sub>   | data hold time                                 | CCLK ≤ 100 MHz                | 2.1  | -        | -    | ns   |

|                   |                                                | 100 MHz < CCLK $\leq$ 180 MHz | 2.2  | -        | -    | ns   |

| t <sub>v(Q)</sub> | ata output valid time                          | CCLK ≤ 100 MHz                | 18.8 | -        | 37.0 | ns   |

|                   |                                                | 100 MHz < CCLK $\leq$ 180 MHz | 18.0 | -        | 36.0 | ns   |

| SPI mas           | ter 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V  |                               |      | <b>I</b> |      | I    |

| t <sub>DS</sub>   | data set-up time                               | CCLK ≤ 100 MHz                | 2.4  | -        | -    | ns   |

|                   |                                                | 100 MHz < CCLK $\leq$ 180 MHz | 2.2  | -        | -    | ns   |

| t <sub>DH</sub>   | data hold time                                 | CCLK ≤ 100 MHz                | 4.2  | -        | -    | ns   |

|                   |                                                | 100 MHz < CCLK $\leq$ 180 MHz | 4.5  | -        | -    | ns   |

| t <sub>v(Q)</sub> | data output valid time                         | CCLK ≤ 100 MHz                | 1.8  | -        | 4.6  | ns   |

|                   |                                                | 100 MHz < CCLK $\leq$ 180 MHz | 1.7  | -        | 4.0  | ns   |

| SPI slave         | e 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V    |                               |      | <b>I</b> |      | I    |

| t <sub>DS</sub>   | data set-up time                               | $CCLK \le 100 \text{ MHz}$    | 1.2  | -        | -    | ns   |

|                   |                                                | 100 MHz < CCLK $\leq$ 180 MHz | 1.0  | -        | -    | ns   |

| t <sub>DH</sub>   | data hold time                                 | $CCLK \le 100 \text{ MHz}$    | 0    | -        | -    | ns   |

|                   |                                                | 100 MHz < CCLK $\leq$ 180 MHz | 0    | -        | -    | ns   |

| t <sub>v(Q)</sub> | data output valid time                         | CCLK ≤ 100 MHz                | 14   | -        | 23.9 | ns   |

|                   |                                                | 100 MHz < CCLK ≤ 180 MHz      | 13.3 | -        | 22.2 | ns   |

[1] Based on characterization; not tested in production.

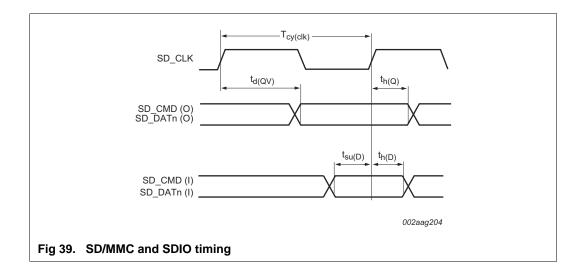

# 11.24 SD/MMC and SDIO

### Table 51. Dynamic characteristics: SD/MMC and SDIO

$T_{amb} = -40$  °C to +105 °C,  $V_{DD} = 2.7$  V to 3.6 V;  $C_L = 20$  pF. SAMPLE\_DELAY = 0, DRV\_DELAY = 0 in the SDDELAY register, SDIOCLKCTRL = 0x84, sampled at 90 % and 10 % of the signal level, SLEW = 1 ns for SD\_CLK pin, SLEW = 1 ns for SD\_DATn and SD\_CMD pins. Simulated values in high-speed mode.

| Symbol             | Parameter              | Conditions                        | Min  | Тур | Max | Unit |

|--------------------|------------------------|-----------------------------------|------|-----|-----|------|

| f <sub>clk</sub>   | clock frequency        | on pin SD_CLK; data transfer mode | -    | -   | 50  | MHz  |

| t <sub>su(D)</sub> | data input set-up time | on pins SD_DATn as inputs         |      |     |     |      |

|                    |                        | CCLK ≤ 100 MHz                    | 14.4 | -   | -   | ns   |

|                    |                        | 100 MHz < CCLK $\leq$ 180 MHz     | 14.4 | -   | -   | ns   |

|                    |                        | on pins SD_CMD as inputs          |      |     |     |      |

|                    |                        | CCLK ≤ 100 MHz                    | 14.4 | -   | -   | ns   |

|                    |                        | 100 MHz < CCLK $\leq$ 180 MHz     | 14.4 | -   | -   | ns   |

| t <sub>h(D)</sub>  | data input hold time   | on pins SD_DATn as inputs         |      |     |     |      |

|                    |                        | $CCLK \le 100 \text{ MHz}$        | 1.5  | -   | -   | ns   |

|                    |                        | 100 MHz < CCLK $\leq$ 180 MHz     | 1.5  | -   | -   | ns   |

|                    |                        | on pins SD_CMD as inputs          |      |     |     |      |

|                    |                        | CCLK ≤ 100 MHz                    | 1.5  | -   | -   | ns   |

|                    |                        | 100 MHz < CCLK $\leq$ 180 MHz     | 1.5  | -   | -   | ns   |

| t <sub>v(Q)</sub>  | data output valid time | on pins SD_DATn as outputs        |      |     |     |      |

|                    |                        | CCLK ≤ 100 MHz                    | 1.9  | -   | 3.5 | ns   |

|                    |                        | 100 MHz < CCLK $\leq$ 180 MHz     | 1.9  | -   | 3.5 | ns   |

|                    |                        | on pins SD_CMD as outputs         |      |     |     |      |

|                    |                        | CCLK ≤ 100 MHz                    | 1.9  | -   | 3.5 | ns   |

|                    |                        | 100 MHz < CCLK $\leq$ 180 MHz     | 1.9  | -   | 3.5 | ns   |

# 12.3 Temperature sensor

# Table 56. Temperature sensor static and dynamic characteristics

| Symbol             | Parameter                         | Conditions                                |     | Min | Тур  | Max  | Unit |

|--------------------|-----------------------------------|-------------------------------------------|-----|-----|------|------|------|

| DT <sub>sen</sub>  | sensor<br>temperature<br>accuracy | $T_{amb}$ = -40 °C to +105 °C             | [1] | -   |      | 3.7  | °C   |

| EL                 | linearity error                   | $T_{amb}$ = -40 °C to +105 °C             |     | -   | -    | 3.7  | °C   |

| t <sub>s(pu)</sub> | power-up<br>settling time         | to 99% of temperature sensor output value | [2] | -   | 10.0 | 15.0 | μS   |

[1] Absolute temperature accuracy.

[2] Based on simulation.

# 13.5.1 RTC Printed Circuit Board (PCB) design guidelines

- Connect the crystal and external load capacitors on the PCB as close as possible to the oscillator input and output pins of the chip.

- The length of traces in the oscillation circuit should be as short as possible and must not cross other signal lines.

- Ensure that the load capacitors CX1, CX2, and CX3, in case of third overtone crystal usage, have a common ground plane.

- Loops must be made as small as possible to minimize the noise coupled in through the PCB and to keep the parasitics as small as possible.

- Lay out the ground (GND) pattern under crystal unit.

- Do not lay out other signal lines under crystal unit for multi-layered PCB.

Product data sheet

# 13.6 XTAL oscillator

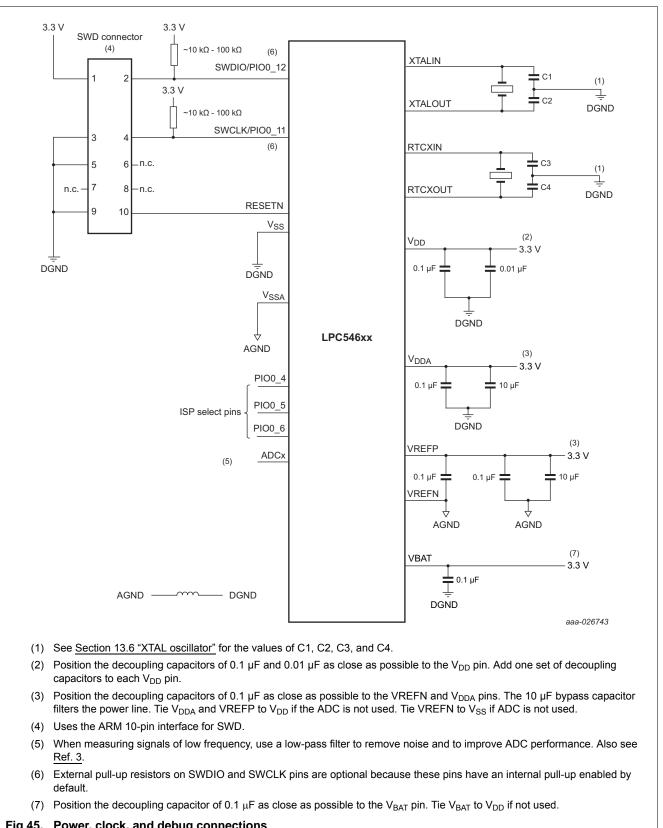

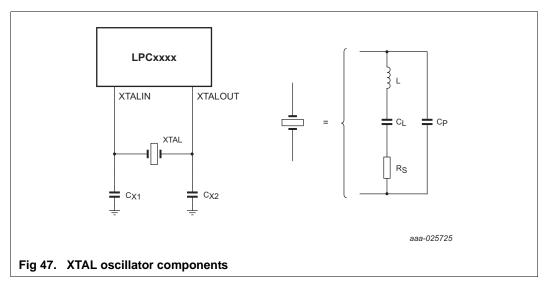

In the XTAL oscillator circuit, only the crystal (XTAL) and the capacitances  $C_{X1}$  and  $C_{X2}$  need to be connected externally on XTALIN and XTALOUT. See Figure 47.

For best results, it is very critical to select a matching crystal for the on-chip oscillator. Load capacitance (CL), series resistance (RS), and drive level (DL) are important parameters to consider while choosing the crystal. After selecting the proper crystal, the external load capacitor  $C_{X1}$  and  $C_{X2}$  values can also be generally determined by the following expression:

$C_{X1} = C_{X2} = 2C_L - (C_{Pad} + C_{Parasitic})$

Where:

CL - Crystal load capacitance

C<sub>Pad</sub> - Pad capacitance of the XTALIN and XTALOUT pins (~3 pF).

C<sub>Parasitic</sub> – Parasitic or stray capacitance of external circuit.

Although C<sub>Parasitic</sub> can be ignored in general, the actual board layout and placement of external components influences the optimal values of external load capacitors. Therefore, it is recommended to fine tune the values of external load capacitors on actual hardware board to get the accurate clock frequency. For fine tuning, measure the clock on the XTALOUT pin and optimize the values of external load capacitors for minimum frequency deviation.

# 19. Legal information

# 19.1 Data sheet status

| Document status <sup>[1][2]</sup> | Product status <sup>[3]</sup> | Definition                                                                            |

|-----------------------------------|-------------------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet      | Development                   | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet    | Qualification                 | This document contains data from the preliminary specification.                       |

| Product [short] data sheet        | Production                    | This document contains the product specification.                                     |

[1] Please consult the most recently issued document before initiating or completing a design.

[2] The term 'short data sheet' is explained in section "Definitions".

[3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL http://www.nxp.com.

# 19.2 Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

**Product specification** — The information and data provided in a Product data sheet shall define the specification of the product as agreed between NXP Semiconductors and its customer, unless NXP Semiconductors and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the NXP Semiconductors product is deemed to offer functions and qualities beyond those described in the Product data sheet.

# 19.3 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the *Terms and conditions of commercial sale* of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product sole and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at <a href="http://www.nxp.com/profile/terms">http://www.nxp.com/profile/terms</a>, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**No offer to sell or license** — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Non-automotive qualified products** — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond

# 20. Contact information

NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

# 19.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

I<sup>2</sup>C-bus — logo is a trademark of NXP B.V.

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com