#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                              |

|----------------------------|---------------------------------------------------------------------|

| Core Processor             | -                                                                   |

| Core Size                  | 16-Bit                                                              |

| Speed                      | 25MHz                                                               |

| Connectivity               | EBI/EMI, UART/USART                                                 |

| Peripherals                | DMA                                                                 |

| Number of I/O              | -                                                                   |

| Program Memory Size        | •                                                                   |

| Program Memory Type        | ROMIess                                                             |

| EEPROM Size                | -                                                                   |

| RAM Size                   | •                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                         |

| Data Converters            | •                                                                   |

| Oscillator Type            | Internal                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                       |

| Package / Case             | 68-LCC (J-Lead)                                                     |

| Supplier Device Package    | 68-PLCC (24.21x24.21)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/ia188xlplc68ir2 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# LIST OF FIGURES

| Figure 1. IA186XL 68-Lead PLCC Package Diagram      | 10 |

|-----------------------------------------------------|----|

| Figure 2. IA188XL 68-Lead PLCC Package Diagram      |    |

| Figure 3. PLCC Physical Package Dimensions          |    |

| Figure 4. IA186XL 80-Lead PQFP Package Diagram      | 15 |

| Figure 5. IA188XL 80-Lead PQFP Package Diagram      | 17 |

| Figure 6. PQFP Physical Package Dimensions          | 19 |

| Figure 7. IA186XL 80-Lead LQFP Package Diagram      | 20 |

| Figure 8. IA188XL 80-Lead LQFP Package Diagram      | 22 |

| Figure 9. LQFP Physical Package Dimensions          | 24 |

| Figure 10. IA186XL/IA188XL Functional Block Diagram | 41 |

| Figure 11. Clock Circuit Connection Options         | 43 |

| Figure 12. Read Cycle Waveforms                     | 48 |

| Figure 13. Write Cycle Waveforms                    | 50 |

| Figure 14. Interrupt Acknowledge Cycle Waveforms    | 52 |

| Figure 15. Software Halt Cycle Waveforms            | 54 |

| Figure 16. Clock Waveforms                          | 58 |

| Figure 17. Reset Waveforms                          | 58 |

| Figure 18. Synchronous Ready (SRDY) Waveforms       | 58 |

| Figure 19. Asynchronous Ready (ARDY) Waveforms      | 59 |

| Figure 20. Peripheral and Queue Status Waveforms    | 59 |

| Figure 21. HOLDA/HLDA Waveforms (Entering Hold)     | 60 |

| Figure 22. HOLD/HLDA Waveforms (Leaving Hold)       |    |

|                                                     |    |

IA211080711-09 UNCONTROLLED WHEN PRINTED OR COPIED Page 5 of 75

#### 2.1.5 IA188XL 80 PQFP Package

The pinout for the IA186XL 80 PQFP package is as shown in Figure 5. The corresponding pinout is provided in Table 4.

Figure 5. IA188XL 80-Lead PQFP Package Diagram

IA211080711-09 UNCONTROLLED WHEN PRINTED OR COPIED Page 17 of 75

#### 2.1.6 PQFP Physical Dimensions

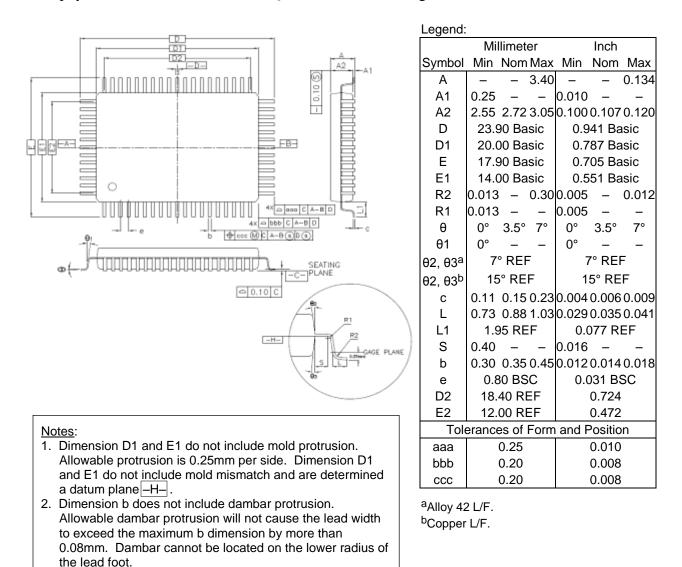

The physical dimensions for the 80 PQFP are as shown in Figure 6.

# Figure 6. PQFP Physical Package Dimensions

|        |                | Pin  |                                               |                         |                                                                                                                                                                                                                                                                                                                                     |

|--------|----------------|------|-----------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal | Name           | PLCC | PQFP                                          | LQFP                    | Description                                                                                                                                                                                                                                                                                                                         |

| lcs_n  | lcs_n          | 33   | 46                                            | 63                      | lower <b>c</b> hip <b>s</b> elect. Output. Active Low. This<br>pin provides a chip select signal that will be<br>asserted (low) whenever the address of a<br>memory bus cycle is within the address space<br>programmed for that output.                                                                                            |

| lock_n | lock_n         | 48   | 28                                            | 45                      | <b>lock</b> . Output. Active Low. When asserted<br>(low), this signal indicates that the bus cycle in<br>progress cannot be interrupted. While <b>lock_n</b><br>is active, the IA186XL will not service bus<br>requests such as HOLD.<br>When <b>resin_n</b> is active, this pin is weakly held<br>high and must not be driven low. |

| mcs0_n | mcs0_n/pereq   | 38   | 39                                            | 57                      | mid-range memory chip select. Output.                                                                                                                                                                                                                                                                                               |

| mcs1_n | mcs1_n/error_n | 37   | 40                                            | 58                      |                                                                                                                                                                                                                                                                                                                                     |

| mcs2_n | mcs2_n         | 36   | 41                                            | 59                      |                                                                                                                                                                                                                                                                                                                                     |

| mcs3_n | mcs3_n/nps_n   | 35   | 42                                            | 60                      |                                                                                                                                                                                                                                                                                                                                     |

| n.c.   | n.c.           | NA   | 2, 11,<br>14, 15,<br>24, 43,<br>44, 62,<br>63 | 4, 25,<br>35, 55,<br>72 | not <b>c</b> onnected.                                                                                                                                                                                                                                                                                                              |

| nmi    | nmi            | 46   | 30                                            | 47                      | <b>n</b> on- <b>m</b> askable interrupt. Input. Active High.<br>When the <b>nmi</b> signal is asserted (high) it<br>causes a Type 2 interrupt.                                                                                                                                                                                      |

| nps_n  | mcs3_n/nps_n   | 35   | 42                                            | 60                      | numeric processor select                                                                                                                                                                                                                                                                                                            |

| pcs0_n | pcs0_n         | 25   | 54                                            | 71                      | <b>p</b> eripheral <b>c</b> hip <b>s</b> elect signals <b>0–6</b> . Output.                                                                                                                                                                                                                                                         |

| pcs1_n | pcs1_n         | 27   | 52                                            | 69                      |                                                                                                                                                                                                                                                                                                                                     |

| pcs2_n | pcs2_n         | 28   | 51                                            | 68                      |                                                                                                                                                                                                                                                                                                                                     |

| pcs3_n | pcs3_n         | 29   | 50                                            | 67                      |                                                                                                                                                                                                                                                                                                                                     |

| pcs4_n | pcs4_n         | 30   | 49                                            | 66                      |                                                                                                                                                                                                                                                                                                                                     |

| pcs5_n | pcs5_n/a1      | 31   | 48                                            | 65                      |                                                                                                                                                                                                                                                                                                                                     |

| pcs6_n | pcs6_n/a2      | 32   | 47                                            | 64                      |                                                                                                                                                                                                                                                                                                                                     |

| pereq  | mcs0_n/pereq   | 38   | 39                                            | 57                      | numerics co <b>p</b> rocessor <b>e</b> xternal <b>req</b> uest.<br>Input. Active High. When asserted (high), this<br>signal indicates that a data transfer between<br>an Intel 80C187 Numerics Coprocessor and<br>the CPU is pending.                                                                                               |

# Table 7. IA186XL Pin/Signal Descriptions (Continued)

|                 | Pin             |           |                   |                              |                                                                                                                                                                                                                                               |

|-----------------|-----------------|-----------|-------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal          | Name            | PLCC      | PQFP              | LQFP                         | Description                                                                                                                                                                                                                                   |

| test_n          | test_n/busy     | 47        | 29                | 46                           | <b>test.</b> Input. Active Low. When the <b>test_n</b> input is high (i.e., not asserted), it causes the IA186XL to suspend operation during the execution of the WAIT instruction. Operation resumes when the pin is sampled low (asserted). |

| tmr in 0        | tmr in 0        | 20        | 59                | 77                           | timer 0 input. Input. Depending on the Timer<br>Mode programmed for Timer 0, this input is<br>used either as clock input or a control signal.                                                                                                 |

| tmr in 1        | tmr in 1        | 21        | 58                | 76                           | timer <b>1</b> input. Input. Depending on the Timer<br>Mode programmed for Timer 1, this input is<br>used either as clock input or a control signal.                                                                                          |

| tmr out 0       | tmr out 0       | 22        | 57                | 75                           | <b>timer 0 out</b> put. Output. Depending on the Timer Mode programmed for Timer 0, this output can provide a single pulse or a repetitive waveform.                                                                                          |

| tmr out 1       | tmr out 1       | 23        | 56                | 74                           | timer <b>1 out</b> put. Output. Depending on the<br>Timer Mode programmed for Timer 1, this<br>output can provide a single clock or a<br>repetitive waveform.                                                                                 |

| ucs_n           | ucs_n           | 34        | 45                | 62                           | upper chip select. Output. Active Low. This<br>pin provides a chip select signal that will be<br>asserted (low) whenever the address of a<br>memory bus cycle is within the address space<br>programmed for that output.                      |

| V <sub>cc</sub> | V <sub>cc</sub> | 9, 43     | 33, 34,<br>72, 73 | 10, 11,<br>20, 50,<br>51, 61 | Power ( $V_{cc}$ ). This pin provides power for the IA186XL device. It must be connected to a +5V DC power source.                                                                                                                            |

| V <sub>ss</sub> | V <sub>SS</sub> | 26,<br>60 | 12, 13,<br>53     | 30, 31,<br>41, 70,<br>80     | Ground ( $V_{ss}$ ). This pin provides the digital ground (0V) for the IA186XL. It must be connected to a $V_{ss}$ board plane.                                                                                                               |

| wr_n            | wr_n/qs1        | 63        | 8                 | 27                           | <pre>write. Output. Active Low. When asserted (low), wr_n indicates that data available on the data bus are to be latched into the accessed memory or I/O device.</pre>                                                                       |

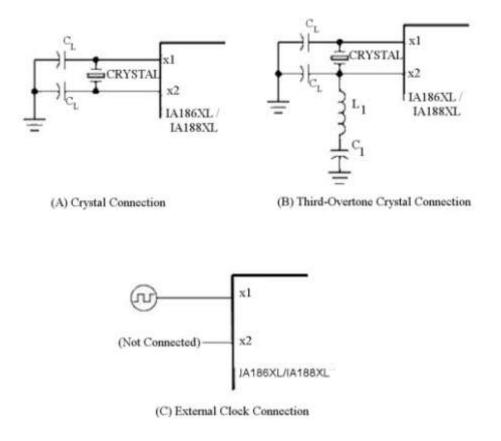

| x1              | x1              | 59        | 16                | 32                           | x1 and x2 are inputs for the crystal                                                                                                                                                                                                          |

| x2              | x2              | 58        | 17                | 33                           |                                                                                                                                                                                                                                               |

# Table 7. IA186XL Pin/Signal Descriptions (Continued)

# 3. Maximum Ratings, Thermal Characteristics, and DC Parameters

For the Innovasic Semiconductor IA186XL and IA188XL microcontrollers, the absolute maximum ratings, thermal characteristics, and DC parameters are provided in Tables 9 through 11, respectively.

# Table 9. IA186XL and IA188XL Absolute Maximum Ratings

| Parameter                                                         | Rating                 |

|-------------------------------------------------------------------|------------------------|

| Storage Temperature                                               | −40°C to +125°C        |

| Supply Voltage with Respect to v <sub>ss</sub>                    | -0.3V to +6.0V         |

| Voltage on Pins other than Supply with Respect to v <sub>ss</sub> | -0.3V to +(Vcc + 0.3)V |

## Table 10. IA186XL and IA188XL Thermal Characteristics

| Symbol         | Characteristic               | Value                            | Units |

|----------------|------------------------------|----------------------------------|-------|

| T <sub>A</sub> | Ambient Temperature          | -40°C to 85°C                    | С°    |

| PD             | Power Dissipation            | $MHz \times ICC \times V/1000$   | W     |

| $\Theta_{Ja}$  | 68-Lead PLCC Package         | 32                               | °C/W  |

|                | 80-Lead PQFP Package         | 46                               |       |

|                | 80-Lead LQFP Package         | 52                               |       |

| TJ             | Average Junction Temperature | $T_A + (P_D \times \Theta_{Ja})$ | °C    |

Figure 11. Clock Circuit Connection Options

# 4.1.5 Chip-Select/Ready Generation Logic

The IA186XL provides programmable chip-select generation for memories and peripherals. The chip can be programmed to provide READY or WAIT state generation. It can also provide latched address bits A1 and A2. Chip select behavior is the same whether the access is generated by the CPU or the DMA.

A total of 6 chip selects are dedicated for different memory ranges. A single select for upper memory (ucs\_n), with a fixed end address of 0FFFFH, is good for use as system memory since the reset vector points to FFFF0H. A single select for lower memory (lcs\_n), with a fixed start address of 0H, is good for interrupt vectors which reside beginning at address 00000H. There are also four selects for anywhere else (exclusive of ucs\_n and lcs\_n areas) in the 1 Mbyte memory in the user-locatable memory block. For the middle chip selects, the base address and block size are programmable, while only the block size for the upper and lower chip selects are programmable.

Seven additional chip selects can be programmed to access either peripherals or memory in seven contiguous fixed blocks of 128 bytes each. A single base address is programmable for these chip selects.

IA211080711-09 UNCONTROLLED WHEN PRINTED OR COPIED Page 43 of 75

# 4.2 Operating Modes

During reset the IA186XL can be configured to enable special operating modes described as follows.

# 4.2.1 Enhanced Mode

If Enhanced Mode is enabled, the IA186XL has DRAM refresh, Power-Save and coprocessor support available in addition to the normal features available in Compatible Mode. Enhanced Mode will be invoked automatically if a coprocessor is attached. It can also be entered by tying the reset output to the test\_n/busy input. An internal pull-up keeps the part from entering Enhanced mode during normal operation.

When not in Enhanced Mode, none of the Enhanced Mode registers can be accessed. Queue-Status functions, except for the coprocessor support, will be available when not in Enhanced Mode.

# 4.2.2 Queue Status Mode

When Queue Status Mode is enabled, information about the instruction queue is output on the ale/qs0 and wr\_n/qs1 pins. To enter Queue Status Mode, the rd\_n input should be tied low. It is sampled at reset, and if low, Queue Status Mode is entered. An internal pull-up keeps the part from entering Queue Status mode during normal operation.

## 4.2.3 ONCE Mode

ONCE mode is a special test mode where all pins are set to a high impedance state. ONCE mode is entered by forcing lcs\_n and ucs\_n low during reset. These pins are sampled on the rising edge of res but should be held low for at least a full clock cycle after res goes high. ONCE mode is exited by reseting the part with lcs\_n and ucs\_n high. Internal pull-ups keep the part from entering ONCE mode during normal operation.

# 4.2.4 Math Coprocessor (IA186XL Only)

When Enhanced mode is enabled, the IA186XL is configured to interface with a math coprocessor via three of the middle chip select pins. Pin mcs0/pereq is used for Processor Extension Request. Pin mcs1/error is used for coprocessor error indication. Pin mcs3/nps is used for Numeric Processor Select.

IA211080711-09 UNCONTROLLED WHEN PRINTED OR COPIED Page 45 of 75

# 5. AC Specifications

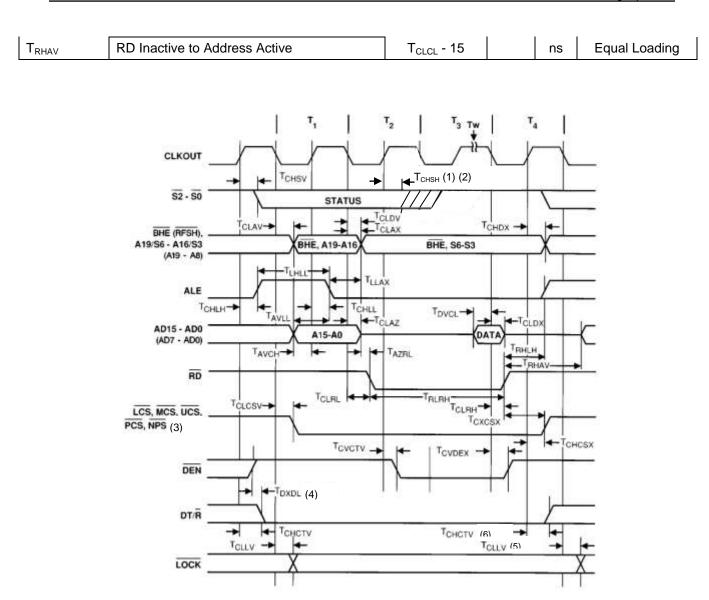

# 5.1 Major Cycle Timings – Read Cycle

- $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ ,  $V_{CC} = 5V \pm 10\%$

- All timings are measured at 1.5V and 50 pF loading on CLKOUT unless otherwise noted.

- All output test conditions are with  $C_L = 50 \text{ pF}$ .

- For AC tests, input  $V_{IL} = 0.45V$  and  $V_{IH} = 2.4V$  except at X1 where  $V_{IH} = V_{CC} 0.5V$ .

## Table 13. Major Cycle Timings – Read Cycle

| Cumb al            | Parameter                              | Values                  |     | 11   | Tast Osmilitians |

|--------------------|----------------------------------------|-------------------------|-----|------|------------------|

| Symbol             | Parameter                              | Min                     | Max | Unit | Test Conditions  |

| T <sub>DVCL</sub>  | Data in Setup (A/D)                    | 8                       |     | ns   |                  |

| T <sub>CLDX</sub>  | Data in Hold (A/D)                     | 3                       |     | ns   |                  |

| T <sub>CHSV</sub>  | Status Active Delay                    | 3                       | 20  | ns   |                  |

| T <sub>CHSH</sub>  | Status Inactive Delay                  | 3                       | 20  | ns   |                  |

| T <sub>CLAV</sub>  | Address Valid Delay                    | 3                       | 20  | ns   |                  |

| T <sub>CLAX</sub>  | Address Hold                           | 0                       |     | ns   |                  |

| T <sub>CLDV</sub>  | Data Valid Delay                       | 3                       | 20  | ns   |                  |

| T <sub>CHDX</sub>  | Status Hold Time                       | 10                      |     | ns   |                  |

| T <sub>CHLH</sub>  | ALE Active Delay                       |                         | 20  | ns   |                  |

| T <sub>LHLL</sub>  | ALE Width                              | T <sub>CLCL</sub> - 15  |     | ns   |                  |

| T <sub>CHLL</sub>  | ALE Inactive Delay                     |                         | 20  | ns   |                  |

| T <sub>AVLL</sub>  | Address Valid to ALE Low               | Т <sub>сьсн</sub> - 10  |     | ns   | Equal Loading    |

| T <sub>LLAX</sub>  | Address Hold from ALE Inactive         | T <sub>CHCL</sub> - 8   |     | ns   | Equal Loading    |

| T <sub>AVCH</sub>  | Address Valid to Clock High            | 0                       |     | ns   |                  |

| T <sub>CLAZ</sub>  | Address Float Delay                    | T <sub>CLAX</sub>       | 20  | ns   |                  |

| T <sub>CLCSV</sub> | Chip-Select Active Delay               | 3                       | 20  | ns   |                  |

| T <sub>CXCSX</sub> | Chip-Select Hold from Command Inactive | Т <sub>сьсн</sub> - 10  |     | ns   | Equal Loading    |

| T <sub>CHCSX</sub> | Chip-Select Inactive Delay             | 3                       | 17  | ns   |                  |

| T <sub>DXDL</sub>  | DEN Inactive to DT/R Low               | 0                       |     | ns   | Equal Loading    |

| T <sub>CVCTV</sub> | Control Active Delay 1                 | 3                       | 17  | ns   |                  |

| T <sub>CVDEX</sub> | DEN Inactive Delay                     | 3                       | 17  | ns   |                  |

| T <sub>CHCTV</sub> | Control Active Delay 2                 | 3                       | 20  | ns   |                  |

| T <sub>CLLV</sub>  | LOCK Valid/Invalid Delay               | 3                       | 17  | ns   |                  |

| T <sub>AZRL</sub>  | Address Float to RD Active             | 0                       |     | ns   |                  |

| T <sub>CLRL</sub>  | RD Active Delay                        | 3                       | 20  | ns   |                  |

| T <sub>RLRH</sub>  | RD Pulse Width                         | 2 <sub>TCLCL</sub> - 15 |     | ns   |                  |

| T <sub>CLRH</sub>  | RD Inactive Delay                      | 3                       | 20  | ns   |                  |

| T <sub>RHLH</sub>  | RD Inactive to ALE High                | Т <sub>СLСН</sub> - 14  |     | ns   | Equal Loading    |

IA211080711-09 UNCONTROLLED WHEN PRINTED OR COPIED Page 47 of 75

Data Sheet July 6, 2011

Figure 12. Read Cycle Waveforms

Please note that pins indicated in the parentheses are for the IA188XL version.

Notes:

(1) The OEM part (80C186XL) operates differently in that it deasserts on the falling edge of CLKOUT.

(2) Status is inactive in the state preceding T4.

(3) Only TCLCSV is applicable if latched A1 and A2 are selected instead of PCS5 and PCS6.

(4) This applies when a write cycle is followed by read cycle.

(5) This is T1 of next bus cycle.

(6) This changes in the T-state preceding the next bus cycle if followed by a write.

Innovasic<sup>®</sup> Semiconductor

IA211080711-09 UNCONTROLLED WHEN PRINTED OR COPIED Page 48 of 75

#### 5.2 Major Cycle Timings – Write Cycle

- $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ ,  $V_{CC} = 5V \pm 10\%$

- All timings are measured at 1.5V and 50 pF loading on CLKOUT unless otherwise noted.

- All output test conditions are with  $C_L = 50 \text{ pF}$ .

- For AC tests, input  $V_{IL} = 0.45V$  and  $V_{IH} = 2.4V$  except at X1 where  $V_{IH} = V_{CC} 0.5V$ .

#### Table 14. Major Cycle Timings – Write Cycle

| Cumb al            | Parameter                              | Values                  |     |      | Test          |

|--------------------|----------------------------------------|-------------------------|-----|------|---------------|

| Symbol             |                                        | Min                     | Max | Unit | Conditions    |

| T <sub>CHSV</sub>  | Status Active Delay                    | 3                       | 20  | ns   |               |

| T <sub>CHSH</sub>  | Status Inactive Delay                  | 3                       | 20  | ns   |               |

| T <sub>CLAV</sub>  | Address Valid Delay                    | 3                       | 20  | ns   |               |

| T <sub>CLAX</sub>  | Address Hold                           | 0                       |     | ns   |               |

| T <sub>CLDV</sub>  | Data Valid Delay                       | 3                       | 20  | ns   |               |

| T <sub>CHDX</sub>  | Status Hold Time                       | 10                      |     | ns   |               |

| T <sub>CHLH</sub>  | ALE Active Delay                       |                         | 20  | ns   |               |

| T <sub>LHLL</sub>  | ALE Width                              | T <sub>CLCL</sub> - 15  |     | ns   |               |

| T <sub>CHLL</sub>  | ALE Inactive Delay                     |                         | 20  | ns   |               |

| T <sub>AVLL</sub>  | Address Valid to ALE Low               | Т <sub>СLСН</sub> - 10  |     | ns   | Equal Loading |

| T <sub>LLAX</sub>  | Address Hold from ALE Inactive         | Т <sub>СНСL</sub> - 10  |     | ns   | Equal Loading |

| T <sub>AVCH</sub>  | Address Valid to Clock High            | 0                       |     | ns   |               |

| T <sub>CLDOX</sub> | Data Hold Time                         | 3                       |     | ns   |               |

| T <sub>CVCTV</sub> | Control Active Delay 1                 | 3                       | 20  | ns   |               |

| T <sub>CVCTX</sub> | Control Inactive Delay                 | 3                       | 17  | ns   |               |

| T <sub>CLCSV</sub> | Chip-Select Active Delay               | 3                       | 20  | ns   |               |

| T <sub>CXCSX</sub> | Chip-Select Hold from Command Inactive | Т <sub>СLСН</sub> - 10  |     | ns   | Equal Loading |

| T <sub>CHCSX</sub> | Chip-Select Inactive Delay             | 3                       | 17  | ns   |               |

| $T_{DXDL}$         | DEN Inactive to DT/R Low               | 0                       |     | ns   | Equal Loading |

| T <sub>CLLV</sub>  | LOCK Valid/Invalid Delay               | 3                       | 17  | ns   |               |

| $T_{WLWH}$         | WR Pulse Width                         | 2 <sub>TCLCL</sub> - 15 |     | ns   |               |

| T <sub>WHLH</sub>  | WR Inactive to ALE High                | Т <sub>СLСН</sub> - 14  |     | ns   | Equal Loading |

| T <sub>WHDX</sub>  | Data Hold after WR                     | T <sub>CLCL</sub> - 10  |     | ns   | Equal Loading |

| T <sub>WHDEX</sub> | WR Inactive to DEN Inactive            | Т <sub>СLСН</sub> - 10  |     | ns   | Equal Loading |

IA211080711-09 UNCONTROLLED WHEN PRINTED OR COPIED Page 49 of 75

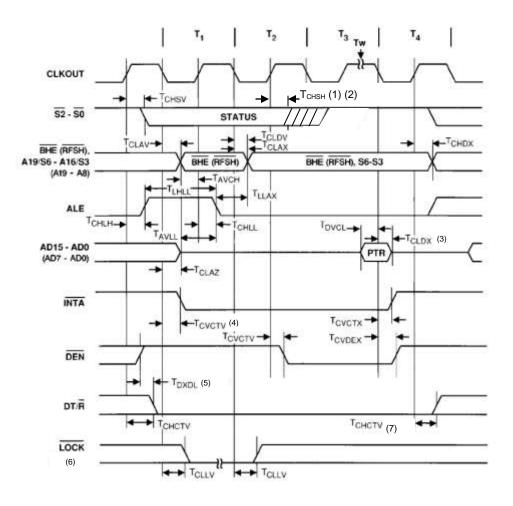

Figure 14. Interrupt Acknowledge Cycle Waveforms

Please note that pins indicated in the parentheses are for the IA188XL version.

Notes:

- (1) The OEM part (80C186XL) operates differently in that it deasserts on the falling edge of CLKOUT.

- (2) Status is inactive in the state preceding T4.

- (3) The data hold time lasts only until INTA goes inactive, even if the INTA transition occurs prior to TCLDX (min).

- (4) INTA occurs one clock later in Slave Mode.

- (5) This applies when a write cycle is followed by an interrupt acknowledge cycle.

- (6) LOCK is active upon T1 of the first interrupt acknowledge cycle, and inactive upon T2 of the second interrupt acknowledge cycle.

- (7) Changes in T-state preceding next bus cycle if followed by write.

IA211080711-09 UNCONTROLLED WHEN PRINTED OR COPIED Page 52 of 75

#### 5.4 Software Halt Cycle Timings

- $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ ,  $V_{CC} = 5V \pm 10\%$

- All timings are measured at 1.5V and 50 pF loading on CLKOUT unless otherwise noted.

- All output test conditions are with  $C_L = 50 \text{ pF}$ .

- For AC tests, input  $V_{IL} = 0.45V$  and  $V_{IH} = 2.4V$  except at X1 where  $V_{IH} = V_{CC} 0.5V$ .

#### Table 16. Software Halt Cycle Timings

| Symbol             | Parameter                | Values                 |     | l Init | Test<br>Conditions |

|--------------------|--------------------------|------------------------|-----|--------|--------------------|

|                    |                          | Min                    | Max | Unit   |                    |

| T <sub>CHSV</sub>  | Status Active Delay      | 3                      | 20  | ns     |                    |

| T <sub>CHSH</sub>  | Status Inactive Delay    | 3                      | 20  | ns     |                    |

| T <sub>CLAV</sub>  | Address Valid Delay      | 3                      | 20  | ns     |                    |

| T <sub>CHLH</sub>  | ALE Active Delay         |                        | 20  | ns     |                    |

| T <sub>LHLL</sub>  | ALE Width                | T <sub>CLCL</sub> - 15 |     | ns     |                    |

| T <sub>CHLL</sub>  | ALE Inactive Delay       |                        | 20  | ns     |                    |

| T <sub>DXDL</sub>  | DEN Inactive to DT/R Low |                        | 0   | ns     | Equal<br>Loading   |

| T <sub>CHCTV</sub> | Control Active Delay 2   | 3                      | 20  | ns     |                    |

IA211080711-09 UNCONTROLLED WHEN PRINTED OR COPIED Page 53 of 75

## 5.5 Clock Timings

- $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ ,  $V_{CC} = 5V \pm 10\%$

- All timings are measured at 1.5V and 50 pF loading on CLKOUT unless otherwise noted.

- All output test conditions are with  $C_L = 50 \text{ pF}$ .

- For AC tests, input  $V_{IL} = 0.45V$  and  $V_{IH} = 2.4V$  except at X1 where  $V_{IH} = V_{CC} 0.5V$ .

| Symbol              | Parameter            | Value                     | s   | Unit | Test                        |

|---------------------|----------------------|---------------------------|-----|------|-----------------------------|

| Symbol              |                      | Min                       | Max | Unit | Conditions                  |

| T <sub>CKIN</sub>   | CLKIN Period         | 20                        | 8   | ns   |                             |

| T <sub>CLCK</sub>   | CLKIN Low Time       | 8                         | 8   | ns   | 1.5V(2)                     |

| Т <sub>СНСК</sub>   | CLKIN High Time      | 8                         | 8   | ns   | 1.5V(2)                     |

| T <sub>CKHL</sub>   | CLKIN Fall Time      |                           | 5   | ns   | 3.5 to 1.0V                 |

| T <sub>CKLH</sub>   | CLKIN Rise Time      |                           | 5   | ns   | 1.0 to 3.5V                 |

| T <sub>CICO</sub>   | CLKIN to CLKOUT Skew |                           | 17  | ns   |                             |

| T <sub>CLCL</sub>   | CLKOUT Period        | 40                        | 8   | ns   |                             |

| T <sub>CLCH</sub>   | CLKOUT Low Time      | 0.5 T <sub>CLCL</sub> - 5 |     | ns   | $C_{L} = 100 \text{ pF}(3)$ |

| T <sub>CHCL</sub>   | CLKOUT High Time     | 0.5 T <sub>CLCL</sub> - 5 |     | ns   | $C_{L} = 100 \text{ pF}(4)$ |

| T <sub>CH1CH2</sub> | CLKOUT Rise Time     |                           | 6   | ns   | 1.0 to 3.5V                 |

| T <sub>CL2CL1</sub> | CLKOUT Fall Time     |                           | 6   | ns   | 3.5 to 1.0V                 |

#### Table 17. Clock Timings

#### NOTES:

- 1. External clock applied to X1 and X2 not connected.

- 2. T<sub>CLCK</sub> and T<sub>CHCK</sub> (CLKIN Low and High times) should not have a duration less than 40% of T<sub>CKIN</sub>.

- 3. Tested under worst case conditions:  $V_{CC}$  = 5.5V.  $T_A$  = 70°C.

- 4. Tested under worst case conditions:  $V_{CC} = 4.5V$ .  $T_A = 0^{\circ}C$ .

IA211080711-09 UNCONTROLLED WHEN PRINTED OR COPIED Page 55 of 75

| Clock Cycles                       |                |                |                           |

|------------------------------------|----------------|----------------|---------------------------|

| Instruction                        | IA186XL        | IA188XL        | Comments                  |

| JNS                                | 3/5            | 3/5            | Jump not taken/Jump taken |

| JNZ                                | 3/5            | 3/5            |                           |

| JO                                 | 3/5            | 3/5            | -                         |

| JP                                 | 3/5            | 3/5            |                           |

| JPE                                | 3/5            | 3/5            |                           |

| JPO                                | 3/5            | 3/5            |                           |

| JS                                 | 3/5            | 3/5            |                           |

| JZ                                 | 3/5            | 3/5            |                           |

| LAHF                               | 2              | 2              | _                         |

| LDS                                | 1/24           | 1/33           | register/memory           |

| LEA                                | 3              | 3              |                           |

| LEAVE                              | 12             | 12             | _                         |

| LES                                | 12             | 32             | _                         |

| LOCK                               | 1              | 1              | _                         |

| LODS                               | 8              | 12             | _                         |

| LODS (repeated <i>n</i> times)     | 8+8 <i>n</i>   | 12+12 <i>n</i> | _                         |

| LOOP                               | 3/4            | 3/4            | Loop not taken/Loop taken |

| LOOPE                              | 3/4            | 3/4            | Loop not taken/Loop taken |

| LOOPNE                             | 3/4            | 3/4            |                           |

| LOOPNZ                             | 3/4            | 3/4            | _                         |

| LOOPZ                              | 3/4            | 3/4            |                           |

| MOV Accumulator to memory          | 5              | 8/12           | 8-bit/16-bit              |

| MOV Immediate to register          | 1              | 1              | -                         |

| MOV Immediate to                   | 1/5            | 1/12           | register/memory           |

| register/memory                    |                |                |                           |

| MOV Memory to accumulator          | 5              | 8/12           | 8-bit/16-bit              |

| MOV Register to                    | 2/5            | 2/20           | register/memory           |

| Register/Memory                    | 0/5            | 0/00           | _                         |

| MOV Register/memory to             | 2/5            | 2/20           |                           |

| register<br>MOV Register/memory to | 2/5            | 2/20           | _                         |

| segment register                   | 2/3            | 2/20           |                           |

| MOV Segment register to            | 2/5            | 2/20           | -                         |

| register/memory                    | 2/5            | 2/20           |                           |

| MOVS                               | 24             | 32             | _                         |

| MOVS (repeated <i>n</i> times)     | 24+24 <i>n</i> | 32+32 <i>n</i> | _                         |

| MUL Memory-Byte                    | 16             | 20             | _                         |

| MUL Memory-Word                    | 15             | 25             | _                         |

| MUL Register-Byte                  | 5              | 5              | -                         |

| MUL Register-Word                  | 5              | 5              | -                         |

| NEG                                | 1/32           | 1/15           | register/memory           |

| NOP                                | 1              | 1              |                           |

| NOT                                | 1/24           | 1/24           | register/memory           |

| OR Immediate to accumulator        | 1              | 1              |                           |

# Table 20. Instruction Set Timing (Continued)

# Table 22. Innovasic Part Number Cross-Reference for the PQFP (Special Order only)

| Innovasic Part Number               | Intel Part Number                                                                                                                                         | Package Type | Temperature Range |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------|

| IA186XLPQF80IR1<br>(lead free–RoHS) | S80C186XL25<br>S80C186XL20<br>S80C186XL12<br>TS80C186XL25<br>TS80C186XL20<br>TS80C186XL20<br>TS80C186XL12<br>EG80C186XL25<br>EG80C186XL20<br>ES80C186XL20 | 80-Lead PQFP | Industrial        |

| IA188XLPQF80IR1<br>(lead free–RoHS) | S80C188XL25<br>S80C188XL20<br>S80C188XL12<br>TS80C188XL25<br>TS80C188XL20<br>TS80C188XL20<br>TS80C188XL25<br>EG80C188XL25<br>EG80C188XL20<br>ES80C188XL20 | 80-Lead PQFP | Industrial        |

IA211080711-09 UNCONTROLLED WHEN PRINTED OR COPIED Page 67 of 75

# 8. Errata

The following errata are associated with the IA186XL/IA188XL. A workaround to the identified problem has been provided where possible.

## 8.1 Summary

Table 24 presents a summary of errata.

Table 24.

Summary of Errata

| Errata<br>No. | Problem                                                                                                                                  | Ver. 0 | Ver. 1 | Ver. 2 |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|--------|

| 1             | Pin LOCK_n does not have an internal pullup and will float during reset and bus hold.                                                    | Exists | Exists | Exists |

| 2             | When the timer compare register for any of the timers is set to $x0000$ , the max count is xFFFF instead of $x10000$ as in the OEM part. | Exists | Fixed  | Fixed  |

| 3             | When using external interrupts IRQ0 or IRQ1 in<br>Cascade Mode, the acknowledge signal on INTA0<br>or INTA1 may be lost or truncated.    | Exists | Fixed  | Fixed  |

| 4             | Memory->Memory moves interrupted by two DMA cycles can corrupt data.                                                                     | Exists | Fixed  | Fixed  |

| 5             | Bit 15 of RELREG (offset 0xFE) behaves differently than Intel device.                                                                    | Exists | Fixed  | Fixed  |

| 6             | Enhanced mode makes bit 15 of RELREG (offset 0xFE) read-only.                                                                            | Exists | Fixed  | Fixed  |

| 7             | Sbus deasserts on the wrong edge of CLKOUT.                                                                                              | Exists | Fixed  | Fixed  |

| 8             | Timer2 count register must be written to enable counting.                                                                                | Exists | Exists | Fixed  |

| 9             | Non-maskable interrupt (NMI) can be pre-empted by maskable interrupt.                                                                    | Exists | Exists | Fixed  |

| 10            | DMA can hang.                                                                                                                            | Exists | Exists | Fixed  |

| Errata<br>No. | Problem                                                         | Ver. 0 | Ver. 1 | Ver. 2 |

|---------------|-----------------------------------------------------------------|--------|--------|--------|

| 11            | MOVS/POP/PUSH instructions interrupted by DMA can corrupt data. | Exists | Exists | Fixed  |

| 12            | MOVS/POP/PUSH instructions interrupted by DMA can corrupt data. | Exists | Exists | Fixed  |

#### 8.2 Detail

#### Errata No. 1

**Problem:** Pin LOCK\_n does not have an internal pullup.

**Description:** Because Pin LOCK\_n does not have an internal pullup, it will float during reset and bus hold.

Workaround: An external pullup may be necessary if there is high external load on the signal.

#### Errata No. 2

#### Problem:

When the timer compare register for any of the timers is set to x0000, the max count is xFFFF instead of x10000 as in the OEM part.

**Description:** The timer output will change one count earlier than it should when the max count is set to x0000.

**Workaround:** The workaround is application dependent. Please contact Innovasic Technical Support if this erratum is an issue.

## Errata No. 3

## Problem:

When using external interrupts IRQ0 or IRQ1 in Cascade Mode, the acknowledge signal on INTA0 or INTA1 may be lost or truncated.

**Description:** The acknowledge for IRQ0 or IRQ1 will be lost or truncated in Cascade Mode if another interrupt, with a higher priority setting (as configured in the interrupt control registers), occurs just before or during the acknowledge. This does not apply to interrupts generated by the DMA. This also does not apply when using the inherent priority settings (all interrupts configured with the same priority).

IA211080711-09 UNCONTROLLED WHEN PRINTED OR COPIED Page 70 of 75

#### Errata No. 5

#### Problem:

Bit 15 of RELREG (offset 0xFE) behaves differently than Intel device.

**Description:** For both 188 and 186 devices, an ESC opcode will generate a type 7 interrupt only when RELREG[15] is a 0.

Workaround: Initialize RELREG[15] to 0 if a type 7 interrupt is desired.

# Errata No. 6

Problem:

Enhanced mode makes bit 15 of RELREG (offset 0xFE) read-only.

**Description:** If the device comes out of reset in enhanced mode, RELREG[15] will be set to a 1.

Workaround: Avoid enhanced mode if a type 7 interrupt is desired.

## Errata No. 7

**Problem:** Sbus deasserts on the wrong edge of CLKOUT.

**Description:** The sbus goes inactive (high) at the end of a bus cycle on the falling edge of CLKOUT. It should be on the rising edge of CLKOUT.

Workaround: None.

## Errata No. 8

**Problem:** Timer2 count register must be written to enable counting.

**Description:** If timer 2 count register is not explicitly written timer 2 will not count; this can also prevent timers 0 & 1 from counting if timer 2 is used as a prescaler.

**Workaround:** Write timer 2 count register before enabling timer 2.

Innovasic<sup>®</sup> Semiconductor Extended Life Semiconductor Solutions

IA211080711-09 UNCONTROLLED WHEN PRINTED OR COPIED Page 72 of 75

#### Errata No. 9

#### Problem:

Non-maskable interrupt (NMI) can be pre-empted by maskable interrupt.

**Description:** When instruction execution unit is in Decode state for 2 or more consecutive cycles and an NMI is recognized, it could be pre-empted by a maskable interrupt.

Workaround: None.

Errata No. 10

**Problem:** DMA can hang.

**Description:** DMA to a region of memory using destination synchronization and a chip select with extra wait states can hang.

Workaround: Do not use wait states and destination synchronization together.

Errata No. 11

**Problem:** MOVS/POP/PUSH instructions interrupted by DMA can corrupt data.

**Description:** MOVS/POP/PUSH instructions interrupted by both a DMA transaction and an instruction fetch bus cycle can corrupt data. *This affects the IA186XL only*.

Workaround: None.

#### Errata No. 12

**Problem:** MOVS/POP/PUSH instructions interrupted by DMA can corrupt data.

**Description:** MOVS/PUSH/POP instructions with 16-bit, non-aligned destination address interrupted by DMA can corrupt data. *This affects the IA186XL only.*

Workaround: None.

IA211080711-09 UNCONTROLLED WHEN PRINTED OR COPIED Page 73 of 75