Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | -                                                                            |

| Core Size                  | -                                                                            |

| Speed                      | -                                                                            |

| Connectivity               | -                                                                            |

| Peripherals                | -                                                                            |

| Number of I/O              | -                                                                            |

| Program Memory Size        | -                                                                            |

| Program Memory Type        | -                                                                            |

| EEPROM Size                | -                                                                            |

| RAM Size                   | -                                                                            |

| Voltage - Supply (Vcc/Vdd) | -                                                                            |

| Data Converters            | -                                                                            |

| Oscillator Type            | -                                                                            |

| Operating Temperature      | -                                                                            |

| Mounting Type              | -                                                                            |

| Package / Case             | -                                                                            |

| Supplier Device Package    | -                                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/d12392f20iv |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Туре                     | Instruction    | Size*1 | Function                                                                                                                                                                                                                                                                                         |

|--------------------------|----------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Arithmetic<br>operations | DIVXU          | B/W    | $Rd \div Rs \rightarrow Rd$<br>Performs unsigned division on data in two general<br>registers: either 16 bits ÷ 8 bits $\rightarrow$ 8-bit quotient and 8-bit<br>remainder or 32 bits ÷ 16 bits $\rightarrow$ 16-bit quotient and 16-<br>bit remainder.                                          |

|                          | DIVXS          | B/W    | $\begin{array}{l} Rd \div Rs \to Rd \\ Performs \text{ signed division on data in two general} \\ registers: either 16 bits \div 8 \text{ bits} \to 8 \text{-bit quotient and 8-bit} \\ remainder or 32 bits \div 16 \text{ bits} \to 16 \text{-bit quotient and 16-bit remainder.} \end{array}$ |

|                          | CMP            | B/W/L  | Rd – Rs, Rd – #IMM<br>Compares data in a general register with data in another<br>general register or with immediate data, and sets CCR<br>bits according to the result.                                                                                                                         |

|                          | NEG            | B/W/L  | $0 - Rd \rightarrow Rd$<br>Takes the two's complement (arithmetic complement) of data in a general register.                                                                                                                                                                                     |

|                          | EXTU           | W/L    | Rd (zero extension) $\rightarrow$ Rd<br>Extends the lower 8 bits of a 16-bit register to word size,<br>or the lower 16 bits of a 32-bit register to longword size,<br>by padding with zeros on the left.                                                                                         |

|                          | EXTS           | W/L    | Rd (sign extension) $\rightarrow$ Rd<br>Extends the lower 8 bits of a 16-bit register to word size,<br>or the lower 16 bits of a 32-bit register to longword size,<br>by extending the sign bit.                                                                                                 |

|                          | TAS            | В      | @ERd – 0, 1 $\rightarrow$ ( <bit 7=""> of @ERd)*<sup>2</sup><br/>Tests memory contents, and sets the most significant bit<br/>(bit 7) to 1.</bit>                                                                                                                                                |

| Logic<br>operations      | AND            | B/W/L  | $Rd \wedge Rs \rightarrow Rd$ , $Rd \wedge \#IMM \rightarrow Rd$<br>Performs a logical AND operation on a general register<br>and another general register or immediate data.                                                                                                                    |

|                          | OR             | B/W/L  | $Rd \lor Rs \rightarrow Rd$ , $Rd \lor \#IMM \rightarrow Rd$<br>Performs a logical OR operation on a general register<br>and another general register or immediate data.                                                                                                                         |

|                          | XOR            | B/W/L  | $Rd \oplus Rs \rightarrow Rd$ , $Rd \oplus \#IMM \rightarrow Rd$<br>Performs a logical exclusive OR operation on a general<br>register and another general register or immediate data.                                                                                                           |

|                          | NOT            | B/W/L  | ¬ (Rd) → (Rd)<br>Takes the one's complement of general register<br>contents.                                                                                                                                                                                                                     |

| Shift<br>operations      | SHAL<br>SHAR   | B/W/L  | Rd (shift) $\rightarrow$ Rd<br>Performs an arithmetic shift on general register contents.<br>1-bit or 2-bit shift is possible.                                                                                                                                                                   |

|                          | SHLL<br>SHLR   | B/W/L  | Rd (shift) $\rightarrow$ Rd<br>Performs a logical shift on general register contents.<br>1-bit or 2-bit shift is possible.                                                                                                                                                                       |

|                          | ROTL<br>ROTR   | B/W/L  | Rd (rotate) $\rightarrow$ Rd<br>Rotates general register contents.<br>1-bit or 2-bit rotation is possible.                                                                                                                                                                                       |

|                          | ROTXL<br>ROTXR | B/W/L  | $\begin{array}{l} \mbox{Rd (rotate)} \rightarrow \mbox{Rd} \\ \mbox{Rotates general register contents through the carry flag.} \\ \mbox{1-bit or 2-bit rotation is possible.} \end{array}$                                                                                                       |

## 6.5.7 Precharge State Control

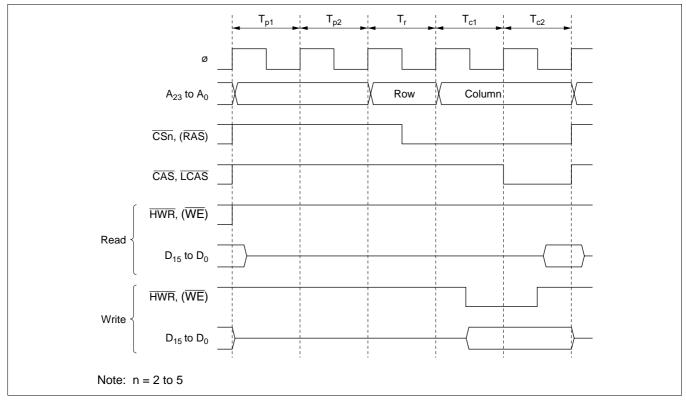

When DRAM is accessed, RAS precharging time must be secured. With the H8S/2357 Series, one  $T_p$  state is always inserted when DRAM space is accessed. This can be changed to two  $T_p$  states by setting the TPC bit in MCR to 1. Set the appropriate number of  $T_p$  cycles according to the DRAM connected and the operating frequency of the H8S/2357 Group. Figure 6-16 shows the timing when two  $T_p$  states are inserted.

When the TPC bit is set to 1, two  $T_p$  states are also used for refresh cycles.

Figure 6-16 Timing with Two Precharge States

## 6.5.8 Wait Control

There are two ways of inserting wait states in a DRAM access cycle: program wait insertion and pin wait insertion using the  $\overline{\text{WAIT}}$  pin.

**Program Wait Insertion:** When the bit in ASTCR corresponding to an area designated as DRAM space is set to 1, from 0 to 3 wait states can be inserted automatically between the  $T_{c1}$  state and  $T_{c2}$  state, according to the settings of WCRH and WCRL.

**Pin Wait Insertion:** When the WAITE bit in BCRH is set to 1, wait input by means of the  $\overline{WAIT}$  pin is enabled regardless of the setting of the AST bit in ASTCR. When DRAM space is accessed in this state, a program wait is first inserted. If the  $\overline{WAIT}$  pin is low at the falling edge of  $\emptyset$  in the last  $T_{c1}$  or  $T_w$  state, another  $T_w$  state is inserted. If the  $\overline{WAIT}$  pin is held low,  $T_w$  states are inserted until it goes high.

## RENESAS

Bit 7—Data Transfer Master Enable 1 (DTME1): Enables or disables data transfer on channel 1.

| Bit 7<br>DTME1 | Description                                                             |                 |

|----------------|-------------------------------------------------------------------------|-----------------|

| 0              | Data transfer disabled. In burst mode, cleared to 0 by an NMI interrupt | (Initial value) |

| 1              | Data transfer enabled                                                   |                 |

Bit 5—Data Transfer Master Enable 0 (DTME0): Enables or disables data transfer on channel 0.

| Bit 5<br>DTME0 | Description                                                                             |                |

|----------------|-----------------------------------------------------------------------------------------|----------------|

| 0              | Data transfer disabled. In normal mode, cleared to 0 by an NMI interrupt (Initial value | <del>)</del> ) |

| 1              | Data transfer enabled                                                                   | _              |

**Bits 6 and 4—Data Transfer Enable (DTE):** When DTE = 0, data transfer is disabled and the activation source selected by the data transfer factor setting is ignored. If the activation source is an internal interrupt, an interrupt request is issued to the CPU or DTC. If the DTIE bit is set to 1 when DTE = 0, the DMAC regards this as indicating the end of a transfer, and issues a transfer end interrupt request to the CPU.

The conditions for the DTE bit being cleared to 0 are as follows:

- When initialization is performed

- When the specified number of transfers have been completed

- When 0 is written to the DTE bit to forcibly abort the transfer, or for a similar reason

When DTE = 1 and DTME = 1, data transfer is enabled and the DMAC waits for a request by the activation source selected by the data transfer factor setting. When a request is issued by the activation source, DMA transfer is executed.

The condition for the DTE bit being set to 1 is as follows:

• When 1 is written to the DTE bit after the DTE bit is read as 0

Bit 6—Data Transfer Enable 1 (DTE1): Enables or disables data transfer on channel 1.

| Bit 6 |                        |                 |

|-------|------------------------|-----------------|

| DTE1  | Description            |                 |

| 0     | Data transfer disabled | (Initial value) |

| 1     | Data transfer enabled  |                 |

Bit 4—Data Transfer Enable 0 (DTE0): Enables or disables data transfer on channel 0.

| Bit 4<br>DTE0 | Description            |                 |

|---------------|------------------------|-----------------|

| 0             | Data transfer disabled | (Initial value) |

| 1             | Data transfer enabled  |                 |

When the DMAC is activated, take any necessary steps to prevent an internal interrupt or  $\overline{\text{DREQ}}$  pin low level remaining from the end of the previous transfer, etc.

**Internal Interrupt after End of Transfer:** When the DTE bit is cleared to 0 by the end of transfer or an abort, the selected internal interrupt request will be sent to the CPU or DTC even if DTA is set to 1.

Also, if internal DMAC activation has already been initiated when operation is aborted, the transfer is executed but flag clearing is not performed for the selected internal interrupt even if DTA is set to 1.

An internal interrupt request following the end of transfer or an abort should be handled by the CPU as necessary.

**Channel Re-Setting:** To reactivate a number of channels when multiple channels are enabled, use exclusive handling of transfer end interrupts, and perform DMABCR control bit operations exclusively.

Note, in particular, that in cases where multiple interrupts are generated between reading and writing of DMABCR, and a DMABCR operation is performed during new interrupt handling, the DMABCR write data in the original interrupt handling routine will be incorrect, and the write may invalidate the results of the operations by the multiple interrupts. Ensure that overlapping DMABCR operations are not performed by multiple interrupts, and that there is no separation between read and write operations by the use of a bit-manipulation instruction.

Also, when the DTE and DTME bits are cleared by the DMAC or are written with 0, they must first be read while cleared to 0 before the CPU can write 1 to them.

#### Selection Method and Pin Functions

Pin

P1₄/PO12/TIOCA1 The pin function is switched as shown below according to the combination of the TPU channel 1 setting by bits MD3 to MD0 in TMDR1, bits IOA3 to IOA0 in TIOR1, bits CCLR1 and CCLR0 in TCR1, bit NDER12 in NDERH, and bit P14DDR.

| TPU Channel<br>1 Setting | Table Below (1) | Та           | able Below    | (2)            |

|--------------------------|-----------------|--------------|---------------|----------------|

| P14DDR                   | —               | 0            | 1             | 1              |

| NDER12                   | —               | —            | 0             | 1              |

| Pin function             | TIOCA1 output   | P1₄<br>input | P1₄<br>output | PO12<br>output |

|                          |                 | TI           | OCA1 inpu     | t *1           |

Note: 1. TIOCA1 input when MD3 to MD0 = B'0000, B'01××, IOA3 to IOA0 = B'10××.

| TPU Channel<br>1 Setting | (2)                        | (1)                                        | (2)    | (1)                                   | (1)                     | (2)       |

|--------------------------|----------------------------|--------------------------------------------|--------|---------------------------------------|-------------------------|-----------|

| MD3 to MD0               | B'0000                     | , B'01××                                   | B'001× | B'0010                                | B'00                    | 011       |

| IOA3 to IOA0             | B'0000<br>B'0100<br>B'1××× | B'0001 to<br>B'0011<br>B'0101 to<br>B'0111 | B'××00 | Other<br>than<br>B'××00               | Other tha               | ın B'××00 |

| CCLR1,<br>CCLR0          | _                          |                                            |        |                                       | Other<br>than B'01      | B'01      |

| Output<br>function       |                            | Output<br>compare<br>output                |        | PWM<br>mode 1<br>output* <sup>2</sup> | PWM<br>mode 2<br>output | —         |

$\times$ : Don't care

Note: 2. TIOCB1 output is disabled.

## 9.7.3 Pin Functions

Port 6 pins also function as interrupt input pins ( $\overline{IRQ0}$  to  $\overline{IRQ3}$ ), DMAC I/O pins ( $\overline{DREQ0}$ ,  $\overline{TEND0}$ ,  $\overline{DREQ1}$ , and  $\overline{TEND1}$ ), and bus control output pins ( $\overline{CS4}$  to  $\overline{CS7}$ ). Port 6 pin functions are shown in table 9-12.

| Pin                       | Selection Meth                                                       | od and Pin Fur                                                       | nctions            |                           |                 |  |

|---------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|--------------------|---------------------------|-----------------|--|

| P6 <sub>7</sub> /IRQ3/CS7 | The pin function is switched as shown below according to bit P67DDR. |                                                                      |                    |                           |                 |  |

|                           | Mode                                                                 | Мос                                                                  | le 7*              | Modes 4 to 6*             |                 |  |

|                           | P67DDR                                                               | 0                                                                    | 1                  | 0                         | 1               |  |

|                           | Pin function                                                         | P67 input pin                                                        | P67 output pin     | P67 input pin             | CS7 output pir  |  |

|                           |                                                                      |                                                                      | IRQ3 interru       | upt input pin             |                 |  |

|                           | Note: * Modes 6                                                      | and 7 are prov                                                       | rided in the on-cl | hip ROM versio            | n only.         |  |

| P6 <sub>6</sub> /IRQ2/CS6 | The pin function                                                     | is switched as                                                       | shown below ac     | cording to bit P          | 66DDR.          |  |

|                           | Mode                                                                 | Mode 7*                                                              |                    | Modes                     | 4 to 6*         |  |

|                           | P66DDR                                                               | 0                                                                    | 1                  | 0                         | 1               |  |

|                           | Pin function                                                         | P6 <sub>6</sub> input pin                                            | P66 output pin     | P6 <sub>6</sub> input pin | CS6 output pi   |  |

|                           |                                                                      | IRQ2 interrupt input pin                                             |                    |                           |                 |  |

|                           | Note: * Modes 6                                                      | 6 and 7 are prov                                                     | rided in the on-cl | hip ROM versio            | M version only. |  |

| P6₅/IRQ1                  | The pin function                                                     | The pin function is switched as shown below according to bit P65DDR. |                    |                           |                 |  |

|                           | P65DDR                                                               |                                                                      | 0                  | 1                         |                 |  |

|                           | Pin function                                                         | P6₅ in                                                               | put pin            | P6₅ output pin            |                 |  |

|                           |                                                                      | IRQ1 interrupt input pin                                             |                    |                           |                 |  |

|                           |                                                                      |                                                                      |                    |                           |                 |  |

| P6 <sub>4</sub> /IRQ0     | The pin function                                                     | is switched as                                                       | shown below ac     | cording to bit P          | 64DDR.          |  |

|                           | P64DDR                                                               |                                                                      | 0                  | 1                         |                 |  |

|                           | Pin function                                                         | P6 <sub>4</sub> in                                                   | put pin            | P6₄ output pin            |                 |  |

|                           |                                                                      |                                                                      | IRQ0 interru       | upt input pin             | pt input pin    |  |

## Table 9-12Port 6 Pin Functions

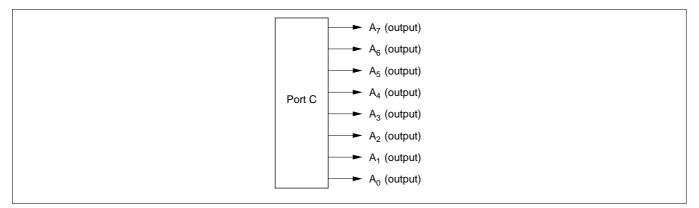

Modes 4 and 5: In modes 4 and 5, port C pins are automatically designated as address outputs.

Port C pin functions in modes 4 and 5 are shown in figure 9-18.

Figure 9-18 Port C Pin Functions (Modes 4 and 5)

## 9.10.4 MOS Input Pull-Up Function (On-Chip ROM Version Only)

Port C has a on-chip MOS input pull-up function that can be controlled by software. This MOS input pull-up function can be used in modes 6 and 7, and can be specified as on or off on an individual bit basis.

When a PCDDR bit is cleared to 0 in mode 6 or 7, setting the corresponding PCPCR bit to 1 turns on the MOS input pullup for that pin.

The MOS input pull-up function is in the off state after a power-on reset, and in hardware standby mode. The prior state is retained after a manual reset\*, and in software standby mode.

Table 9-18 summarizes the MOS input pull-up states.

Note: \* Manual reset is only supported in the H8S/2357 ZTAT.

## Table 9-18 MOS Input Pull-Up States (Port C)

| Modes | Power-On<br>Reset | <br>   | Software<br>Standby Mode | In Other<br>Operations |

|-------|-------------------|--------|--------------------------|------------------------|

| 6, 7  | OFF               | ON/OFF |                          |                        |

| 4, 5  |                   | OFF    |                          |                        |

Legend:

OFF: MOS input pull-up is always off.

ON/OFF: On when PCDDR = 0 and PCPCR = 1; otherwise off.

Note: \* Manual reset is only supported in the H8S/2357 ZTAT.

| ltem                        | Channel 0                                                                                                                                                                                                                                                              | Channel 1                                                                                           | Channel 2                                                                                                                           | Channel 3                                                                               | Channel 4                                                                                                        | Channel 5                                                                                |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| DMAC<br>activation          | TGR0A<br>compare<br>match or<br>input capture                                                                                                                                                                                                                          | TGR1A<br>compare<br>match or<br>input capture                                                       | TGR2A<br>compare<br>match or<br>input capture                                                                                       | TGR3A<br>compare<br>match or<br>input capture                                           | TGR4A<br>compare<br>match or<br>input capture                                                                    | TGR5A<br>compare<br>match or<br>input capture                                            |

| DTC<br>activation           | TGR<br>compare<br>match or<br>input capture                                                                                                                                                                                                                            | TGR<br>compare<br>match or<br>input capture                                                         | TGR<br>compare<br>match or<br>input capture                                                                                         | TGR<br>compare<br>match or<br>input capture                                             | TGR<br>compare<br>match or<br>input capture                                                                      | TGR<br>compare<br>match or<br>input capture                                              |

| A/D<br>converter<br>trigger | TGR0A<br>compare<br>match or<br>input capture                                                                                                                                                                                                                          | TGR1A<br>compare<br>match or<br>input capture                                                       | TGR2A<br>compare<br>match or<br>input capture                                                                                       | TGR3A<br>compare<br>match or<br>input capture                                           | TGR4A<br>compare<br>match or<br>input capture                                                                    | TGR5A<br>compare<br>match or<br>input capture                                            |

| PPG<br>trigger              | TGR0A/<br>TGR0B<br>compare<br>match or<br>input capture                                                                                                                                                                                                                | TGR1A/<br>TGR1B<br>compare<br>match or<br>input capture                                             | TGR2A/<br>TGR2B<br>compare<br>match or<br>input capture                                                                             | TGR3A/<br>TGR3B<br>compare<br>match or<br>input capture                                 | _                                                                                                                | _                                                                                        |

| Interrupt<br>sources        | <ul> <li>5 sources</li> <li>Compare match or input capture 04</li> <li>Compare match or input capture 0E</li> <li>Compare match or input capture 0C</li> <li>Compare match or input capture 0C</li> <li>Compare match or input capture 0E</li> <li>Overflow</li> </ul> | <ul> <li>Compare match or input</li> <li>capture 18</li> <li>Overflow</li> <li>Underflow</li> </ul> | <ul> <li>match or input</li> <li>capture 2<i>A</i></li> <li>Compare match or input</li> <li>capture 2E</li> <li>Overflow</li> </ul> | <ul> <li>Compare<br/>match or<br/>input</li> <li>capture 31</li> <li>Compare</li> </ul> | match or<br>input<br>A capture 44<br>• Compare<br>match or<br>input<br>B capture 4E<br>• Overflow<br>• Underflow | <ul> <li>Compare<br/>match or<br/>input</li> <li>capture 5B</li> <li>Overflow</li> </ul> |

Legend:

$\bigcirc$ : Possible

— : Not possible

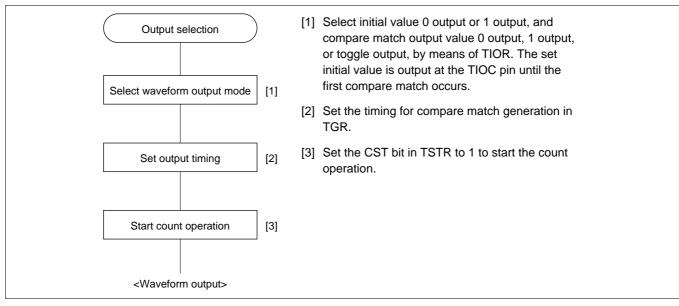

**Waveform Output by Compare Match:** The TPU can perform 0, 1, or toggle output from the corresponding output pin using compare match.

• Example of setting procedure for waveform output by compare match Figure 10-9 shows an example of the setting procedure for waveform output by compare match

Figure 10-9 Example of Setting Procedure for Waveform Output by Compare Match

• Examples of waveform output operation Figure 10-10 shows an example of 0 output/1 output.

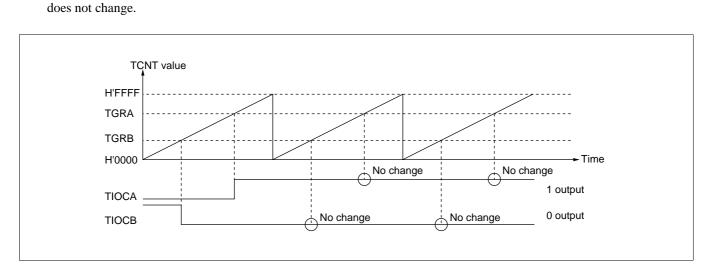

In this example TCNT has been designated as a free-running counter, and settings have been made so that 1 is output by compare match A, and 0 is output by compare match B. When the set level and the pin level coincide, the pin level

Figure 10-10 Example of 0 Output/1 Output Operation

PWM output is generated from the TIOCA and TIOCC pins by pairing TGRA with TGRB and TGRC with TGRD. The output specified by bits IOA3 to IOA0 and IOC3 to IOC0 in TIOR is output from the TIOCA and TIOCC pins at compare matches A and C, and the output specified by bits IOB3 to IOB0 and IOD3 to IOD0 in TIOR is output at compare matches B and D. The initial output value is the value set in TGRA or TGRC. If the set values of paired TGRs are identical, the output value does not change when a compare match occurs.

In PWM mode 1, a maximum 8-phase PWM output is possible.

• PWM mode 2

PWM output is generated using one TGR as the cycle register and the others as duty registers. The output specified in TIOR is performed by means of compare matches. Upon counter clearing by a synchronization register compare match, the output value of each pin is the initial value set in TIOR. If the set values of the cycle and duty registers are identical, the output value does not change when a compare match occurs.

In PWM mode 2, a maximum 15-phase PWM output is possible by combined use with synchronous operation.

The correspondence between PWM output pins and registers is shown in table 10-7.

|         |           | (          | Dutput Pins |

|---------|-----------|------------|-------------|

| Channel | Registers | PWM Mode 1 | PWM Mode 2  |

| 0       | TGR0A     | TIOCA0     | TIOCA0      |

|         | TGR0B     |            | TIOCB0      |

|         | TGR0C     | TIOCC0     | TIOCC0      |

|         | TGR0D     |            | TIOCD0      |

| 1       | TGR1A     | TIOCA1     | TIOCA1      |

|         | TGR1B     |            | TIOCB1      |

| 2       | TGR2A     | TIOCA2     | TIOCA2      |

|         | TGR2B     |            | TIOCB2      |

| 3       | TGR3A     | TIOCA3     | TIOCA3      |

|         | TGR3B     |            | TIOCB3      |

|         | TGR3C     | TIOCC3     | TIOCC3      |

|         | TGR3D     |            | TIOCD3      |

| 4       | TGR4A     | TIOCA4     | TIOCA4      |

|         | TGR4B     |            | TIOCB4      |

| 5       | TGR5A     | TIOCA5     | TIOCA5      |

|         | TGR5B     |            | TIOCB5      |

## Table 10-7 PWM Output Registers and Output Pins

Note: In PWM mode 2, PWM output is not possible for the TGR register in which the period is set.

| Bit 5<br>OVF | Description                                                |                 |

|--------------|------------------------------------------------------------|-----------------|

| 0            | [Clearing condition]                                       | (Initial value) |

|              | Cleared by reading OVF when OVF = 1, then writing 0 to OVF |                 |

| 1            | [Setting condition]                                        |                 |

|              | Set when TCNT overflows from H'FF to H'00                  |                 |

Bit 5—Timer Overflow Flag (OVF): Status flag indicating that TCNT has overflowed (changed from H'FF to H'00).

**Bit 4—A/D Trigger Enable (ADTE) (TCSR0 Only):** Selects enabling or disabling of A/D converter start requests by compare-match A.

In TCSR1, this bit is reserved: it is always read as 1 and cannot be modified.

| Bit 4<br>ADTE | Description                                                  |                 |

|---------------|--------------------------------------------------------------|-----------------|

| 0             | A/D converter start requests by compare match A are disabled | (Initial value) |

| 1             | A/D converter start requests by compare match A are enabled  |                 |

Bits 3 to 0—Output Select 3 to 0 (OS3 to OS0): These bits specify how the timer output level is to be changed by a compare match of TCOR and TCNT.

Bits OS3 and OS2 select the effect of compare match B on the output level, bits OS1 and OS0 select the effect of compare match A on the output level, and both of them can be controlled independently.

Note, however, that priorities are set such that: toggle output > 1 output > 0 output. If compare matches occur simultaneously, the output changes according to the compare match with the higher priority.

Timer output is disabled when bits OS3 to OS0 are all 0.

After a reset, the timer output is 0 until the first compare match event occurs.

| Bit 3<br>OS3 | Bit 2<br>OS2 | Description                                                    |                 |

|--------------|--------------|----------------------------------------------------------------|-----------------|

| 0            | 0            | No change when compare match B occurs                          | (Initial value) |

|              | 1            | 0 is output when compare match B occurs                        |                 |

| 1            | 0            | 1 is output when compare match B occurs                        |                 |

|              | 1            | Output is inverted when compare match B occurs (toggle output) |                 |

| Bit 1<br>OS1 | Bit 0<br>OS0 | Description                                                    |                 |

| 0            | 0            | No change when compare match A acquire                         | (Initial value) |

| 0 | 0 | No change when compare match A occurs                          | (Initial value) |

|---|---|----------------------------------------------------------------|-----------------|

|   | 1 | 0 is output when compare match A occurs                        |                 |

| 1 | 0 | 1 is output when compare match A occurs                        |                 |

| _ | 1 | Output is inverted when compare match A occurs (toggle output) |                 |

## 12.3.5 Operation with Cascaded Connection

If bits CKS2 to CKS0 in either TCR0 or TCR1 are set to B'100, the 8-bit timers of the two channels are cascaded. With this configuration, a single 16-bit timer could be used (16-bit timer mode) or compare matches of the 8-bit channel 0 could be counted by the timer of channel 1 (compare match counter mode). In this case, the timer operates as below.

**16-Bit Counter Mode:** When bits CKS2 to CKS0 in TCR0 are set to B'100, the timer functions as a single 16-bit timer with channel 0 occupying the upper 8 bits and channel 1 occupying the lower 8 bits.

- Setting of compare match flags

- The CMF flag in TCSR0 is set to 1 when a 16-bit compare match event occurs.

- The CMF flag in TCSR1 is set to 1 when a lower 8-bit compare match event occurs.

- Counter clear specification

- If the CCLR1 and CCLR0 bits in TCR0 have been set for counter clear at compare match, the 16-bit counter (TCNT0 and TCNT1 together) is cleared when a 16-bit compare match event occurs. The 16-bit counter (TCNT0 and TCNT1 together) is cleared even if counter clear by the TMRI0 pin has also been set.

- The settings of the CCLR1 and CCLR0 bits in TCR1 are ignored. The lower 8 bits cannot be cleared independently.

- Pin output

- Control of output from the TMO0 pin by bits OS3 to OS0 in TCSR0 is in accordance with the 16-bit compare match conditions.

- Control of output from the TMO1 pin by bits OS3 to OS0 in TCSR1 is in accordance with the lower 8-bit compare match conditions.

# **Compare Match Counter Mode:** When bits CKS2 to CKS0 in TCR1 are B'100, TCNT1 counts compare match A's for channel 0.

Channels 0 and 1 are controlled independently. Conditions such as setting of the CMF flag, generation of interrupts, output from the TMO pin, and counter clear are in accordance with the settings for each channel.

**Note on Usage:** If the 16-bit counter mode and compare match counter mode are set simultaneously, the input clock pulses for TCNT0 and TCNT1 are not generated and thus the counters will stop operating. Software should therefore avoid using both these modes.

## 13.3 Operation

## 13.3.1 Watchdog Timer Operation

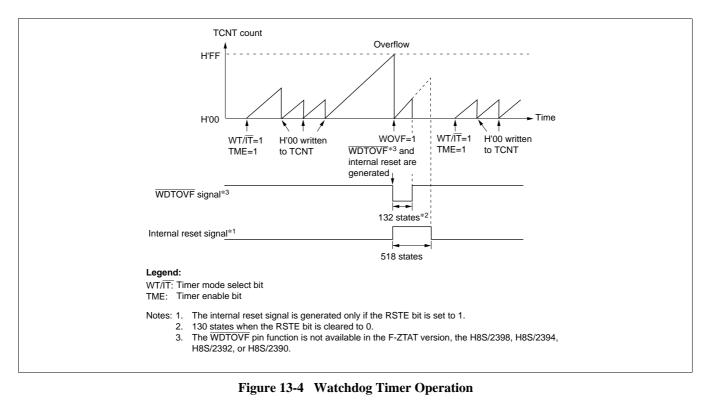

To use the WDT as a watchdog timer, set the WT/ $\overline{\text{IT}}$  and TME bits to 1. Software must prevent TCNT overflows by rewriting the TCNT value (normally be writing H'00) before overflows occurs. This ensures that TCNT does not overflow while the system is operating normally. If TCNT overflows without being rewritten because of a system crash or other error, the WDTOVF signal\*<sup>1</sup> is output. This is shown in figure 13-4. This WDTOVF signal\*<sup>1</sup> can be used to reset the system. The WDTOVF signal\*<sup>1</sup> is output for 132 states when RSTE = 1, and for 130 states when RSTE = 0.

If TCNT overflows when 1 is set in the RSTE bit in RSTCSR, a signal that resets the H8S/2357 Group internally is generated at the same time as the  $\overline{\text{WDTOVF}}$  signal<sup>\*1</sup>. This reset can be selected as a power-on reset or a manual reset<sup>\*2</sup>, depending on the setting of the RSTS bit in RSTCSR. The internal reset signal is output for 518 states.

If a reset caused by a signal input to the  $\overline{\text{RES}}$  pin occurs at the same time as a reset caused by a WDT overflow, the  $\overline{\text{RES}}$  pin reset has priority and the WOVF bit in RSTCSR is cleared to 0.

Notes: 1. In the F-ZTAT version, the H8S/2398, H8S/2394, H8S/2392, or H8S/2390, the WDTOVF pin function is not available.

2. Manual reset is only supported in the H8S/2357 ZTAT.

## **16.2** Register Descriptions

| Bit :           | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|---|---|---|---|---|---|

|                 | AD9 | AD8 | AD7 | AD6 | AD5 | AD4 | AD3 | AD2 | AD1 | AD0 | — | Ι | — | — | Ι | — |

| Initial value : | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0 | 0 | 0 | 0 | 0 | 0 |

| R/W :           | R   | R   | R   | R   | R   | R   | R   | R   | R   | R   | R | R | R | R | R | R |

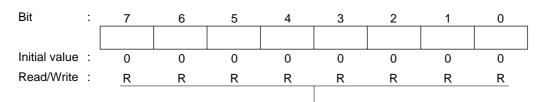

## 16.2.1 A/D Data Registers A to D (ADDRA to ADDRD)

There are four 16-bit read-only ADDR registers, ADDRA to ADDRD, used to store the results of A/D conversion.

The 10-bit data resulting from A/D conversion is transferred to the ADDR register for the selected channel and stored there. The upper 8 bits of the converted data are transferred to the upper byte (bits 15 to 8) of ADDR, and the lower 2 bits are transferred to the lower byte (bits 7 and 6) and stored. Bits 5 to 0 are always read as 0.

The correspondence between the analog input channels and ADDR registers is shown in table 16-3.

ADDR can always be read by the CPU. The upper byte can be read directly, but for the lower byte, data transfer is performed via a temporary register (TEMP). For details, see section 16.3, Interface to Bus Master.

The ADDR registers are initialized to H'0000 by a reset, and in standby mode or module stop mode.

#### Table 16-3 Analog Input Channels and Corresponding ADDR Registers

| Ana     | log Input Channel |                   |  |

|---------|-------------------|-------------------|--|

| Group 0 | Group 1           | A/D Data Register |  |

| AN0     | AN4               | ADDRA             |  |

| AN1     | AN5               | ADDRB             |  |

| AN2     | AN6               | ADDRC             |  |

| AN3     | AN7               | ADDRD             |  |

## 16.2.2 A/D Control/Status Register (ADCSR)

| Bit          | :    | 7      | 6    | 5    | 4    | 3   | 2   | 1   | 0   |

|--------------|------|--------|------|------|------|-----|-----|-----|-----|

|              |      | ADF    | ADIE | ADST | SCAN | CKS | CH2 | CH1 | CH0 |

| Initial valu | le : | 0      | 0    | 0    | 0    | 0   | 0   | 0   | 0   |

| R/W          | :    | R/(W)* | R/W  | R/W  | R/W  | R/W | R/W | R/W | R/W |

Note: \* Only 0 can be written to bit 7, to clear this flag.

ADCSR is an 8-bit readable/writable register that controls A/D conversion operations and shows the status of the operation.

ADCSR is initialized to H'00 by a reset, and in hardware standby mode or module stop mode.

## **17.1.3 Pin Configuration**

Table 17-1 summarizes the input and output pins of the D/A converter.

## Table 17-1Pin Configuration

| Pin Name              | Symbol        | I/O    | Function                            |

|-----------------------|---------------|--------|-------------------------------------|

| Analog power pin      | $AV_{cc}$     | Input  | Analog power source                 |

| Analog ground pin     | $AV_{ss}$     | Input  | Analog ground and reference voltage |

| Analog output pin 0   | DA0           | Output | Channel 0 analog output             |

| Analog output pin 1   | DA1           | Output | Channel 1 analog output             |

| Reference voltage pin | $V_{\rm ref}$ | Input  | Analog reference voltage            |

## 17.1.4 Register Configuration

Table 17-2 summarizes the registers of the D/A converter.

## Table 17-2 D/A Converter Registers

| Name                         | Abbreviation | R/W | Initial Value | Address* |

|------------------------------|--------------|-----|---------------|----------|

| D/A data register 0          | DADR0        | R/W | H'00          | H'FFA4   |

| D/A data register 1          | DADR1        | R/W | H'00          | H'FFA5   |

| D/A control register         | DACR         | R/W | H'1F          | H'FFA6   |

| Module stop control register | MSTPCR       | R/W | H'3FFF        | H'FF3C   |

Note:\* Lower 16 bits of the address.

# 19.10 Flash Memory Protection

There are three kinds of flash memory program/erase protection: hardware protection, software protection, and error protection.

## **19.10.1 Hardware Protection**

Hardware protection refers to a state in which programming/erasing of flash memory is forcibly disabled or aborted. Hardware protection is reset by settings in flash memory control registers 1 and 2 (FLMCR1, FLMCR2) and erase block registers 1 and 2 (EBR1, EBR2). (See table 19-16.)

| Table 19-16 | <b>Hardware Protection</b> |

|-------------|----------------------------|

| Table 19-16 | Hardware Protection        |

|                             |                                                                                                                                                                                                                                                                                         | Fu      | nctions |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|

| Item                        | Description                                                                                                                                                                                                                                                                             | Program | Erase   |

| FWE pin protection          | <ul> <li>When a low level is input to the FWE pin,<br/>FLMCR1, FLMCR2 (excluding the FLER<br/>bit), EBR1, and EBR2 are initialized, and<br/>the program/erase-protected state is<br/>entered.</li> </ul>                                                                                | Yes     | Yes     |

| Reset/standby<br>protection | <ul> <li>In a reset (including a WDT overflow reset) and in standby mode, FLMCR1, FLMCR2, EBR1, and EBR2 are initialized, and the program/erase-protected state is entered.</li> <li>In a reset via the RES pin, the reset state</li> </ul>                                             | Yes     | Yes     |

|                             | is not entered unless the RES pin is held<br>low until oscillation stabilizes after<br>powering on. In the case of a reset during<br>operation, hold the $\overline{\text{RES}}$ pin low for the<br>$\overline{\text{RES}}$ pulse width specified in the AC<br>Characteristics section. |         |         |

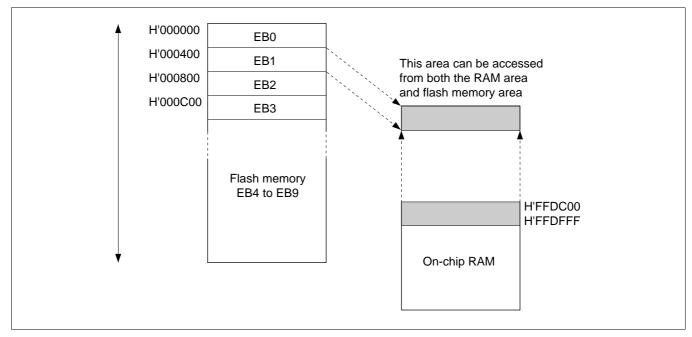

## 19.11.2 RAM Overlap

An example in which flash memory block area EB1 is overlapped is shown below.

Figure 19.23 Example of RAM Overlap Operation

## Example in Which Flash Memory Block Area (EB1) is Overlapped

- 1. Set bits RAMS, RAM1, and RAM0 in RAMER to 1, 0, 1, to overlap part of RAM onto the area (EB1) for which realtime programming is required.

- 2. Real-time programming is performed using the overlapping RAM.

- 3. After the program data has been confirmed, the RAMS bit is cleared, releasing RAM overlap.

- 4. The data written in the overlapping RAM is written into the flash memory space (EB1).

- Notes: 1. When the RAMS bit is set to 1, program/erase protection is enabled for all blocks regardless of the value of RAM1 and RAM0 (emulation protection). In this state, setting the P or E bit in flash memory control register 1 (FLMCR1) will not cause a transition to program mode or erase mode. When actually programming a flash memory area, the RAMS bit should be cleared to 0.

- 2. A RAM area cannot be erased by execution of software in accordance with the erase algorithm while flash memory emulation in RAM is being used.

- 3. Block area EB0 includes the vector table. When performing RAM emulation, the vector table is needed by the overlap RAM.

|     |                  | 1          | lus | Addressing Mode/<br>Instruction Length (Bytes) | dre           | ising<br>Ler | Addressing Mode/<br>ruction Length (By | (By   | tes  |                    |   |    |      |                   |        |                |                             |

|-----|------------------|------------|-----|------------------------------------------------|---------------|--------------|----------------------------------------|-------|------|--------------------|---|----|------|-------------------|--------|----------------|-----------------------------|

|     |                  | erand Size |     | ~d:                                            | d,ERn)<br>מאז | +uЯ3@\nЯ3    | e                                      | 4,PC) | 88 ( |                    |   | ပိ | indi | tion              | ပိ     | Condition Code | No. of States* <sup>1</sup> |

|     | Mnemonic         | odO        | xx# | u A                                            |               |              | <b>e</b> @                             |       | ത    | Operation          |   | -  | I    | z                 | ><br>2 | с<br>2         | Advanced                    |

| AND | AND.B #xx:8,Rd   | В          | 5   |                                                |               |              |                                        |       |      | Rd8∧#xx:8→Rd8      |   |    |      | $\leftrightarrow$ | 0<br>↔ | 0              | -                           |

|     | AND.B Rs,Rd      | В          |     | 2                                              |               |              |                                        |       |      | Rd8∧Rs8→Rd8        |   |    |      | $\leftrightarrow$ | C<br>↔ | 0              | -                           |

|     | AND.W #xx:16,Rd  | ≥          | 4   |                                                |               |              |                                        |       |      | Rd16∧#xx:16→Rd16   |   |    |      | $\leftrightarrow$ | C<br>↔ | 0              | 5                           |

|     | AND.W Rs,Rd      | ≥          |     | 2                                              |               |              |                                        |       |      | Rd16∧Rs16→Rd16     |   |    |      | $\leftrightarrow$ |        | 0              | -                           |

|     | AND.L #xx:32,ERd | ٦          | 6   |                                                |               |              |                                        |       |      | ERd32∧#xx:32→ERd32 | 2 |    |      | $\Rightarrow$     | ¢      | 0              | - 3                         |

|     | AND.L ERs, ERd   | Г          |     | 4                                              |               |              |                                        |       |      | ERd32∧ERs32→ERd32  | 2 |    |      | $\leftrightarrow$ | ¢ C    | 0              | 2                           |

| OR  | OR.B #xx:8,Rd    | В          | 2   |                                                |               |              |                                        |       |      | Rd8∨#xx:8→Rd8      |   |    |      | $\leftrightarrow$ | 0<br>≎ |                | -                           |

|     | OR.B Rs,Rd       | В          |     | 2                                              |               |              |                                        |       |      | Rd8∨Rs8→Rd8        |   |    |      | $\leftrightarrow$ | C<br>↔ | 0              | -                           |

|     | OR.W #xx:16,Rd   | ≥          | 4   |                                                |               |              |                                        |       |      | Rd16∨#xx:16→Rd16   |   |    |      | $\leftrightarrow$ | C<br>↔ | 0              | 2                           |

|     | OR.W Rs,Rd       | ≥          |     | 2                                              |               |              |                                        |       |      | Rd16∨Rs16→Rd16     |   |    |      | $\leftrightarrow$ | 0<br>↓ |                | -                           |

|     | OR.L #xx:32,ERd  | _          | 9   |                                                |               |              |                                        |       |      | ERd32∨#xx:32→ERd32 | 2 |    |      | $\leftrightarrow$ | ¢<br>¢ | 0              | 3                           |

|     | OR.L ERS, ERd    | Г          |     | 4                                              |               |              |                                        |       |      | ERd32∨ERs32→ERd32  | 2 |    |      | $\leftrightarrow$ | ¢<br>¢ | 0              | 2                           |

| XOR | XOR.B #xx:8,Rd   | В          | 5   |                                                |               |              |                                        | -     |      | Rd8⊕#xx:8→Rd8      |   |    |      | $\leftrightarrow$ | 0<br>↔ | 0              | -<br>-                      |

|     | XOR.B Rs,Rd      | В          |     | 2                                              |               |              |                                        |       |      | Rd8⊕Rs8→Rd8        |   |    |      | $\leftrightarrow$ | O<br>↔ | 0              | -                           |

|     | XOR.W #xx:16,Rd  | ≥          | 4   |                                                |               |              |                                        |       |      | Rd16⊕#xx:16→Rd16   |   |    |      | $\leftrightarrow$ | C<br>↔ | 0              | 2                           |

|     | XOR.W Rs,Rd      | ≥          |     | 2                                              |               |              |                                        |       |      | Rd16⊕Rs16→Rd16     |   |    |      | $\leftrightarrow$ | C<br>↔ | 0              | +                           |

|     | XOR.L #xx:32,ERd | _          | 9   |                                                |               |              |                                        |       |      | ERd32⊕#xx:32→ERd32 | 2 |    |      | $\leftrightarrow$ | ¢<br>¢ | 0              | 3                           |

|     | XOR.L ERs, ERd   | _          |     | 4                                              |               |              |                                        |       |      | ERd32⊕ERs32→ERd32  | 2 |    |      | $\leftrightarrow$ | 0<br>↔ |                | 2                           |

| NOT | NOT.B Rd         | В          |     | 2                                              |               |              |                                        |       |      | – Rd8→Rd8          |   |    |      | $\leftrightarrow$ | 0<br>↔ | 0              | -                           |

|     | NOT.W Rd         | 8          |     | 2                                              |               |              |                                        |       |      | – Rd16→Rd16        |   |    |      | $\leftrightarrow$ | ¢<br>¢ | 0              | -                           |

|     | NOT.L ERd        | _          |     | 2                                              |               |              |                                        |       |      | - ERd32-→ERd32     |   |    |      | $\leftrightarrow$ | ¢ C    | 0              | ۰                           |

|     |                  |            |     |                                                |               |              |                                        |       |      |                    |   |    |      |                   |        |                |                             |

(3) Logical Instructions

## **RDR1**—Receive Data Register 1

Stores received serial data

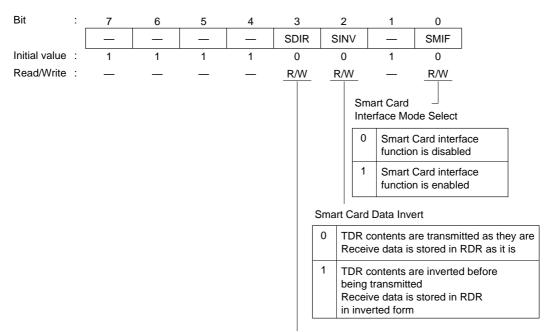

## SCMR1—Smart Card Mode Register 1

H'FF86 SCI1, Smart Card Interface 1

Smart Card Data Direction

| 0 | TDR contents are transmitted LSB-first<br>Receive data is stored in RDR LSB-first |

|---|-----------------------------------------------------------------------------------|

| 1 | TDR contents are transmitted MSB-first<br>Receive data is stored in RDR MSB-first |

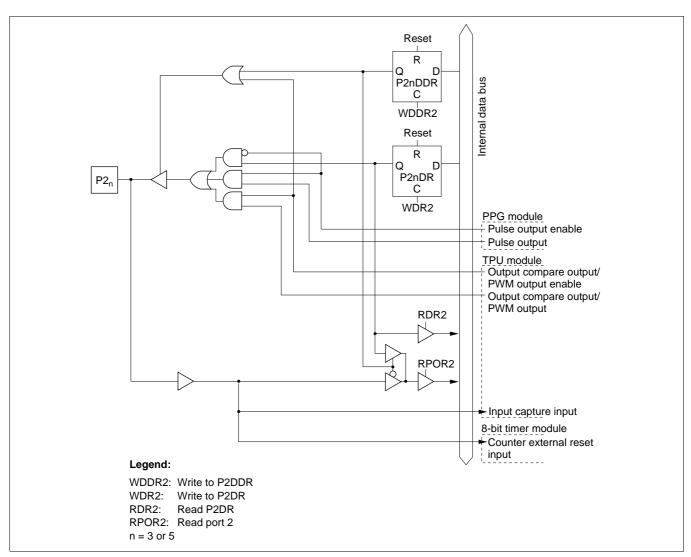

Figure C-2 (c) Port 2 Block Diagram (Pins P2<sub>3</sub> and P2<sub>5</sub>)