Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | H8S/2000                                                                     |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 20MHz                                                                        |

| Connectivity               | SCI, SmartCard                                                               |

| Peripherals                | DMA, POR, PWM, WDT                                                           |

| Number of I/O              | 87                                                                           |

| Program Memory Size        | -                                                                            |

| Program Memory Type        | ROMIess                                                                      |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 8K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b; D/A 2x8b                                                          |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 120-TQFP                                                                     |

| Supplier Device Package    | 120-TQFP (14x14)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/d12392te20v |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| ltem                               | Page | Revision (See Manual for Details)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

|------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 9.8.2 Register Configuration       | 303  | Note added<br>Port A MOS Pull-Up Control Register (PAPCR) (ON-Chip ROM<br>Version Only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|                                    |      | Bit : 7 6 5 4 3 2 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|                                    |      | PA7PCR PA6PCR PA5PCR PA4PCR PA3PCR PA2PCR PA1PCR PA0PCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|                                    |      | Initial value : 0 0 0 0 0 0 0 0 0<br>R/W : R/W R/W R/W R/W R/W R/W R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|                                    |      | Note: Setting is prohibited in the H8S/2352, H8S/2394, H8S/2392, and H8S/2390.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

|                                    | 304  | Port A Open Drain Control Register (PAODR) (ON-Chip ROM Version Only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|                                    |      | Bit : 7 6 5 4 3 2 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|                                    |      | PA7ODR PA6ODR PA5ODR PA4ODR PA3ODR PA2ODR PA1ODR PA0ODR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|                                    |      | Initial value : 0 0 0 0 0 0 0 0 0<br>R/W : R/W R/W R/W R/W R/W R/W R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|                                    |      | PA7ODR         PA6ODR         PA5ODR         PA4ODR         PA3ODR         PA2ODR         PA1ODR         PA0ODF           Initial value :         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 |  |  |  |  |  |  |  |

| 9.9.2 Register Configuration (On-  | 309  | Note added                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| Chip ROM Version Only)             |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

|                                    |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

|                                    |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

|                                    |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

|                                    |      | Note: Setting is prohibited in the H8S/2352, H8S/2394, H8S/2392, and H8S/2390.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| 9.10.2 Register Configuration (On- | 314  | Note added                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| Chip ROM Version Only)             |      | Port C MOS Pull-Up Control Register (PCPCR) (ON-Chip ROM<br>Version Only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

|                                    |      | Bit : 7 6 5 4 3 2 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|                                    |      | PC7PCR PC6PCR PC5PCR PC4PCR PC3PCR PC2PCR PC1PCR PC0PCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|                                    |      | Initial value : 0 0 0 0 0 0 0 0 0<br>R/W : R/W R/W R/W R/W R/W R/W R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|                                    |      | Note: Setting is prohibited in the H8S/2352, H8S/2394, H8S/2392, and H8S/2390.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| 9.11.2 Register Configuration (On- | 319  | Note added                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| Chip ROM Version Only)             |      | Port D MOS Pull-Up Control Register (PDPCR) (ON-Chip ROM<br>Version Only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

|                                    |      | Bit : 7 6 5 4 3 2 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|                                    |      | PD7PCR PD6PCR PD5PCR PD4PCR PD3PCR PD2PCR PD1PCR PD0PCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|                                    |      | Initial value : 0 0 0 0 0 0 0 0 0<br>R/W : R/W R/W R/W R/W R/W R/W R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|                                    |      | Note: Setting is prohibited in the H8S/2352, H8S/2394, H8S/2392, and H8S/2390.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

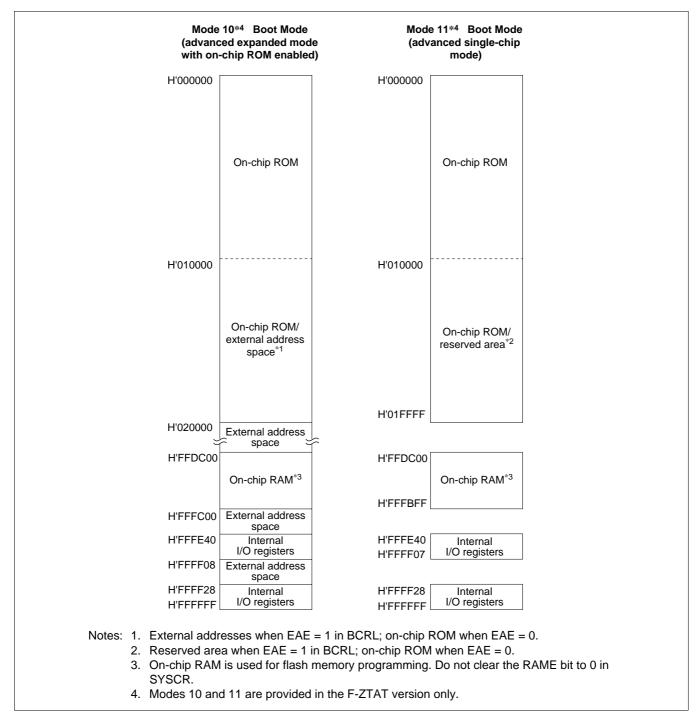

Figure 3-1 Memory Map in Each Operating Mode (H8S/2357, H8S/2352) (2)

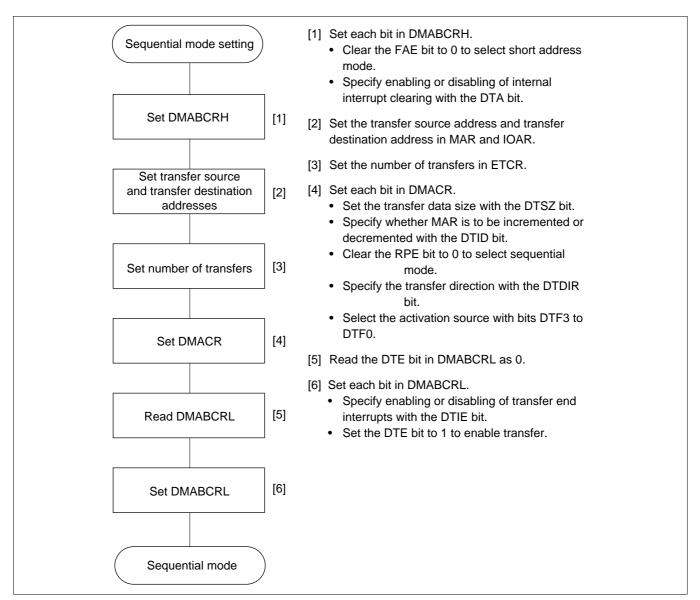

Figure 7-4 shows an example of the setting procedure for sequential mode.

Figure 7-4 Example of Sequential Mode Setting Procedure

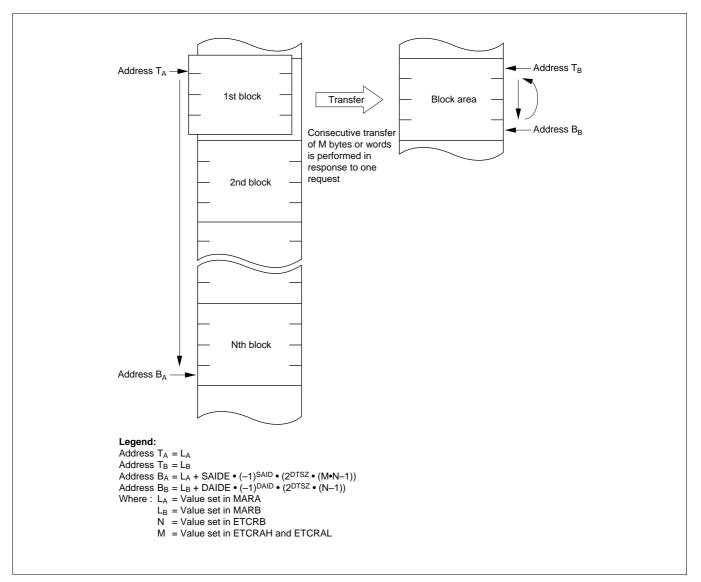

Figure 7-13 Operation in Block Transfer Mode (BLKDIR = 0)

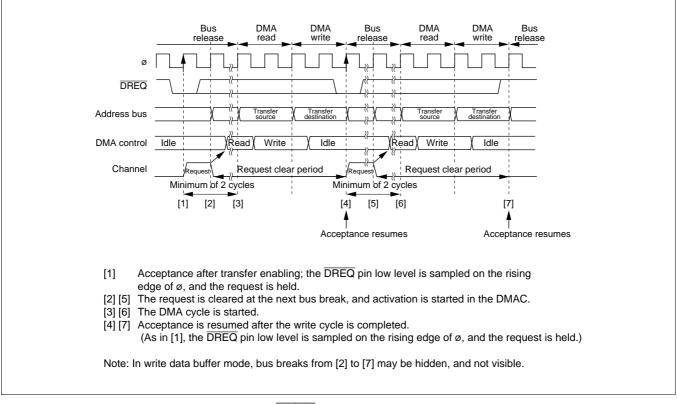

**DREQ** Level Activation Timing (Normal Mode): Set the DTA bit for the channel for which the  $\overline{\text{DREQ}}$  pin is selected to 1.

Figure 7-25 shows an example of  $\overline{\text{DREQ}}$  level activated normal mode transfer.

# Figure 7-25 Example of DREQ Level Activated Normal Mode Transfer

$\overline{\text{DREQ}}$  pin sampling is performed every cycle, with the rising edge of the next  $\phi$  cycle after the end of the DMABCR write cycle for setting the transfer enabled state as the starting point.

When the  $\overline{\text{DREQ}}$  pin low level is sampled while acceptance by means of the  $\overline{\text{DREQ}}$  pin is possible, the request is held in the DMAC. Then, when activation is initiated in the DMAC, the request is cleared. After the end of the write cycle, acceptance resumes,  $\overline{\text{DREQ}}$  pin low level sampling is performed again, and this operation is repeated until the transfer ends.

| Interrupt Source                             | Origin of<br>Interrupt<br>Source | Vector<br>Number | Vector<br>Address | DTCE*  | Priority |

|----------------------------------------------|----------------------------------|------------------|-------------------|--------|----------|

| TGI5B (GR5B compare match/<br>input capture) | TPU<br>channel 5                 | 61               | H'047A            | DTCED4 | High     |

| CMIA0                                        | 8-bit timer                      | 64               | H'0480            | DTCED3 |          |

| CMIB0                                        | channel 0                        | 65               | H'0482            | DTCED2 | _        |

| CMIA1                                        | 8-bit timer                      | 68               | H'0488            | DTCED1 | _        |

| CMIB1                                        | channel 1                        | 69               | H'048A            | DTCED0 | _        |

| DMTEND0A (DMAC transfer end 0)               |                                  | 72               | H'0490            | DTCEE7 | _        |

| DMTEND0B (DMAC transfer end 1)               |                                  | 73               | H'0492            | DTCEE6 |          |

| DMTEND1A (DMAC transfer end 2)               | _                                | 74               | H'0494            | DTCEE5 | _        |

| DMTEND1B (DMAC transfer end 3)               | _                                | 75               | H'0496            | DTCEE4 |          |

| RXI0 (reception data full 0)                 | SCI                              | 81               | H'04A2            | DTCEE3 | _        |

| TXI0 (transmit data empty 0)                 | channel 0                        | 82               | H'04A4            | DTCEE2 | _        |

| RXI1 (reception data full 1)                 | SCI                              | 85               | H'04AA            | DTCEE1 | _        |

| TXI1 (transmit data empty 1)                 | channel 1                        | 86               | H'04AC            | DTCEE0 | _        |

| RXI2 (reception data full 2)                 | SCI                              | 89               | H'04B2            | DTCEF7 | _        |

| TXI2 (transmit data empty 2)                 | channel 2                        | 90               | H'04B4            | DTCEF6 | Low      |

Note: \* DTCE bits with no corresponding interrupt are reserved, and should be written with 0.

#### 9.3.3 Pin Functions

Port 2 pins also function as PPG output pins (PO7 to PO0) and TPU I/O pins (TIOCA3, TIOCB3, TIOCC3, TIOCD3, TIOCA4, TIOCB4, TIOCA5, and TIOCB5), and 8-bit timer I/O pins (TMRI0, TMCI0, TMO0, TMRI1, TMCI1, and TMO1). Port 2 pin functions are shown in table 9-5.

# Table 9-5Port 2 Pin Functions

| Pin                                  | Selection Method and Pin Functions            |                                                                                                                                                                                                                                                            |                          |                           |               |                |  |  |  |  |

|--------------------------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------------------------|---------------|----------------|--|--|--|--|

| P2 <sub>7</sub> /PO7/TIOCB5/<br>TMO1 | the TPU channe<br>TIOR5, bits CCL             | The pin function is switched as shown below according to the combination of the TPU channel 5 setting by bits MD3 to MD0 in TMDR5, bits IOB3 to IOB0 ir TIOR5, bits CCLR1 and CCLR0 in TCR5, bit NDER7 in NDERL, bits OS3 to OS0 in TCSR1, and bit P27DDR. |                          |                           |               |                |  |  |  |  |

|                                      | OS3 to OS0                                    | All 0 Any 1                                                                                                                                                                                                                                                |                          |                           |               |                |  |  |  |  |

|                                      | TPU ChannelTable5 SettingBelow (1)Table Below |                                                                                                                                                                                                                                                            |                          | able Below (              | (2) —         |                |  |  |  |  |

|                                      | P27DDR                                        | —                                                                                                                                                                                                                                                          | 0                        | 1                         | 1             | —              |  |  |  |  |

|                                      | NDER7                                         | —                                                                                                                                                                                                                                                          | _                        | 0                         | 1             | —              |  |  |  |  |

|                                      | Pin function                                  | TIOCB5<br>output                                                                                                                                                                                                                                           | P2 <sub>7</sub><br>input | P2 <sub>7</sub><br>output | PO7<br>output | TMO1<br>output |  |  |  |  |

TIOCB5 input \*

Note: \* TIOCB5 input when MD3 to MD0 = B'0000, B'01 $\times$ x, and IOB3 = 1.

| TPU Channel<br>5 Setting | (2)                        | (1)                                        | (2)    | (2)    | (1)                     | (2)  |  |  |

|--------------------------|----------------------------|--------------------------------------------|--------|--------|-------------------------|------|--|--|

| MD3 to MD0               | B'0000                     | , B'01××                                   | B'0010 |        | B'0011                  |      |  |  |

| IOB3 to IOB0             | B'0000<br>B'0100<br>B'1××× | B'0001 to<br>B'0011<br>B'0101 to<br>B'0111 | _      | B'××00 | Other than B'xx00       |      |  |  |

| CCLR1,<br>CCLR0          |                            | _                                          | _      |        | Other<br>than B'10      | B'10 |  |  |

| Output<br>function       | —                          | Output<br>compare<br>output                | —      | —      | PWM<br>mode 2<br>output | —    |  |  |

×: Don't care

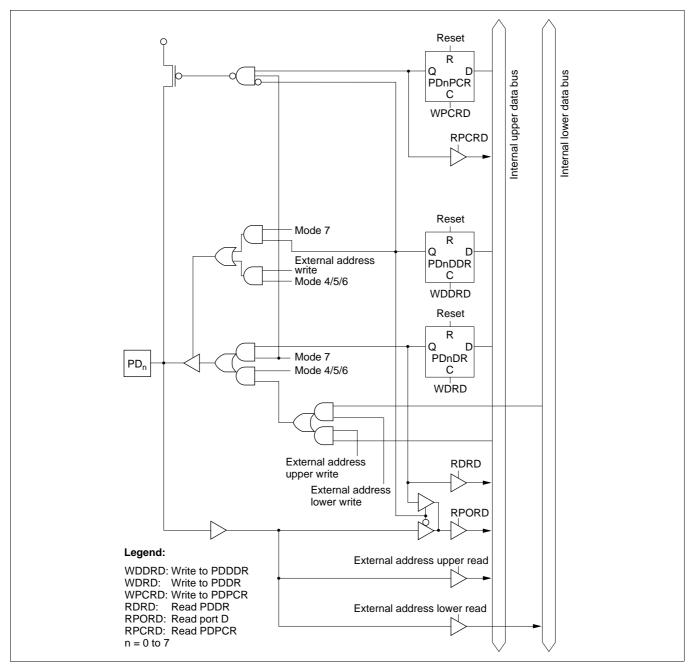

## 9.11.2 Register Configuration (On-Chip ROM Version Only)

Table 9-19 shows the port D register configuration.

#### Table 9-19Port D Registers

| Name                                | Abbreviation | R/W | Initial Value | Address * |

|-------------------------------------|--------------|-----|---------------|-----------|

| Port D data direction register      | PDDDR        | W   | H'00          | H'FEBC    |

| Port D data register                | PDDR         | R/W | H'00          | H'FF6C    |

| Port D register                     | PORTD        | R   | Undefined     | H'FF5C    |

| Port D MOS pull-up control register | PDPCR        | R/W | H'00          | H'FF73    |

Note: \* Lower 16 bits of the address.

### Port D Data Direction Register (PDDDR) (On-Chip ROM Version Only)

| Bit        | :      | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

|            |        | PD7DDR | PD6DDR | PD5DDR | PD4DDR | PD3DDR | PD2DDR | PD1DDR | PD0DDR |

| Initial va | alue : | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| R/W        | :      | W      | W      | W      | W      | W      | W      | W      | W      |

PDDDR is an 8-bit write-only register, the individual bits of which specify input or output for the pins of port D. PDDDR cannot be read; if it is, an undefined value will be read.

PDDDR is initialized to H'00 by a power-on reset, and in hardware standby mode. It retains its prior state after a manual reset\*, and in software standby mode.

Note: \* Manual reset is only supported in the H8S/2357 ZTAT.

• Mode 7

Setting a PDDDR bit to 1 makes the corresponding port D pin an output port, while clearing the bit to 0 makes the pin an input port.

• Modes 4 to 6

The input/output direction specification by PDDDR is ignored, and port D is automatically designated for data I/O.

### Port D Data Register (PDDR) (On-Chip ROM Version Only)

| Bit        | :      | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|------------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

|            |        | PD7DR | PD6DR | PD5DR | PD4DR | PD3DR | PD2DR | PD1DR | PD0DR |

| Initial va | alue : | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| R/W        | :      | R/W   |

PDDR is an 8-bit readable/writable register that stores output data for the port D pins (PD<sub>7</sub> to PD<sub>0</sub>).

PDDR is initialized to H'00 by a power-on reset, and in hardware standby mode. It retains its prior state after a manual reset\*, and in software standby mode.

Note: \* Manual reset is only supported in the H8S/2357 ZTAT.

### Port G Data Direction Register (PGDDR)

| Bit          | :   | 7         | 6         | 5         | 4      | 3      | 2      | 1      | 0      |

|--------------|-----|-----------|-----------|-----------|--------|--------|--------|--------|--------|

|              |     | —         | —         |           | PG4DDR | PG3DDR | PG2DDR | PG1DDR | PG0DDR |

| Modes 6, 7   |     |           |           |           |        |        |        |        |        |

| Initial valu | e : | Undefined | Undefined | Undefined | 0      | 0      | 0      | 0      | 0      |

| R/W          | :   | —         | —         | —         | W      | W      | W      | W      | W      |

| Modes 4, 5   |     |           |           |           |        |        |        |        |        |

| Initial valu | e:  | Undefined | Undefined | Undefined | 1      | 0      | 0      | 0      | 0      |

| R/W          | :   | —         | —         | —         | W      | W      | W      | W      | W      |

PGDDR is an 8-bit write-only register, the individual bits of which specify input or output for the pins of port G. PGDDR cannot be read, and bits 7 to 5 are reserved. If PGDDR is read, an undefined value will be read.

The PG4DDR bit is initialized by a power-on reset and in hardware standby mode, to 1 in modes 4 and 5, and to 0 in modes 6 and 7. It retains its prior state after a manual reset\* and in software standby mode. The OPE bit in SBYCR is used to select whether the bus control output pins retain their output state or become high-impedance when a transition is made to software standby mode.

Note: \* Manual reset is only supported in the H8S/2357 ZTAT.

#### • Mode 7\*

Setting a PGDDR bit to 1 makes the corresponding port G pin an output port, while clearing the bit to 0 makes the pin an input port.

• Modes 4 to 6\*

Pins PG<sub>4</sub> to PG<sub>1</sub> function as bus control output pins ( $\overline{CS0}$  to  $\overline{CS3}$ ) when the corresponding PGDDR bits are set to 1, and as input ports when the bits are cleared to 0.

Pin PG<sub>0</sub> functions as the  $\overline{CAS}$  output pin when DRAM interface is designated. Otherwise, setting the corresponding PGDDR bit to 1 makes the pin an output port, while clearing the bit to 0 makes the pin an input port. For details of the DRAM interfaces, see section 6, Bus Controller.

Note: \* Modes 6 and 7 are provided in the on-chip ROM version only.

#### Port G Data Register (PGDR)

| Bit        | :     | 7         | 6         | 5         | 4     | 3     | 2     | 1     | 0     |

|------------|-------|-----------|-----------|-----------|-------|-------|-------|-------|-------|

|            |       | —         | —         | —         | PG4DR | PG3DR | PG2DR | PG1DR | PG0DR |

| Initial va | lue : | Undefined | Undefined | Undefined | 0     | 0     | 0     | 0     | 0     |

| R/W        | :     | —         | —         | —         | R/W   | R/W   | R/W   | R/W   | R/W   |

PGDR is an 8-bit readable/writable register that stores output data for the port G pins (PG<sub>4</sub> to PG<sub>0</sub>).

Bits 7 to 5 are reserved; they return an undetermined value if read, and cannot be modified.

PGDR is initialized to H'00 (bits 4 to 0) by a power-on reset, and in hardware standby mode. It retains its prior state after a manual reset\*, and in software standby mode.

Note: \* Manual reset is only supported in the H8S/2357 ZTAT.

#### RENESAS

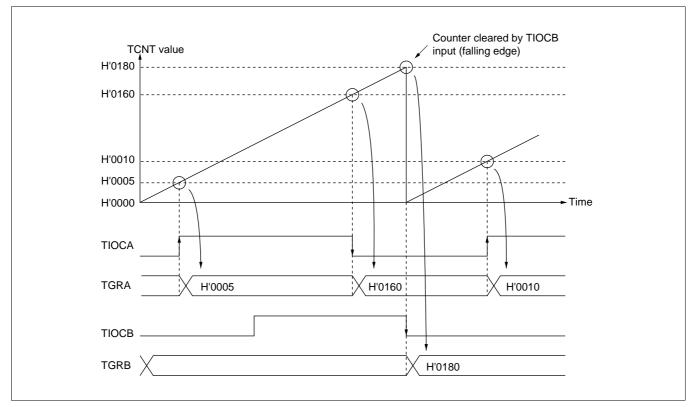

# • Example of input capture operation

Figure 10-13 shows an example of input capture operation.

In this example both rising and falling edges have been selected as the TIOCA pin input capture input edge, falling edge has been selected as the TIOCB pin input capture input edge, and counter clearing by TGRB input capture has been designated for TCNT.

Figure 10-13 Example of Input Capture Operation

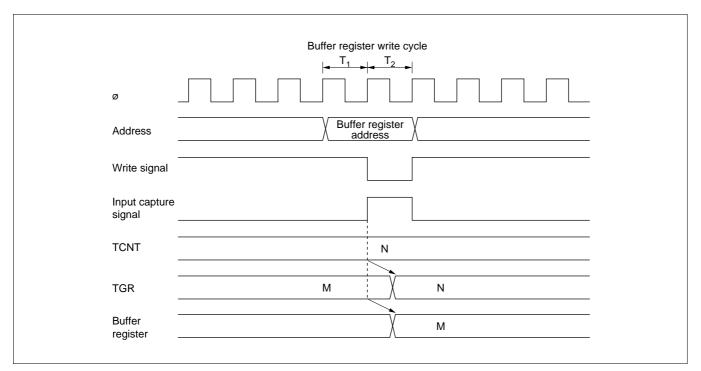

**Contention between Buffer Register Write and Input Capture:** If the input capture signal is generated in the  $T_2$  state of a buffer write cycle, the buffer operation takes precedence and the write to the buffer register is not performed.

Figure 10-55 shows the timing in this case.

Figure 10-55 Contention between Buffer Register Write and Input Capture

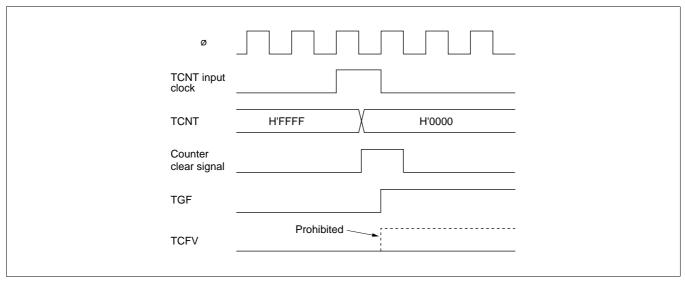

**Contention between Overflow/Underflow and Counter Clearing:** If overflow/underflow and counter clearing occur simultaneously, the TCFV/TCFU flag in TSR is not set and TCNT clearing takes precedence.

Figure 10-56 shows the operation timing when a TGR compare match is specified as the clearing source, and H'FFFF is set in TGR.

Figure 10-56 Contention between Overflow and Counter Clearing

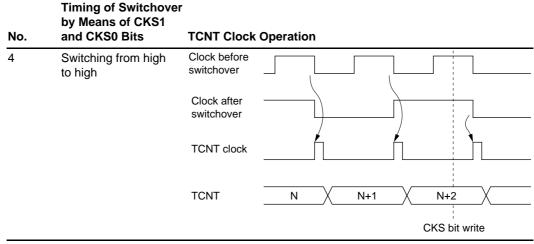

- Notes: 1. Includes switching from low to stop, and from stop to low.

- 2. Includes switching from stop to high.

- 3. Includes switching from high to stop.

- 4. Generated on the assumption that the switchover is a falling edge; TCNT is incremented.

### 12.6.6 Interrupts and Module Stop Mode

If module stop mode is entered when an interrupt has been requested, it will not be possible to clear the CPU interrupt source or the DMAC or DTC activation source. Interrupts should therefore be disabled before entering module stop mode.

Bits 2 to 0—Channel Select 2 to 0 (CH2 to CH0): Together with the SCAN bit, these bits select the analog input channels.

| Group<br>Selection | Chan | nel Selection | Description          |                    |  |  |  |  |

|--------------------|------|---------------|----------------------|--------------------|--|--|--|--|

| CH2                | CH1  | CH0           | Single Mode (SCAN=0) | Scan Mode (SCAN=1) |  |  |  |  |

| 0                  | 0    | 0             | AN0 (Initial value)  | ANO                |  |  |  |  |

|                    |      | 1             | AN1                  | ANO, AN1           |  |  |  |  |

|                    | 1    | 0             | AN2                  | AN0 to AN2         |  |  |  |  |

|                    |      | 1             | AN3                  | AN0 to AN3         |  |  |  |  |

| 1                  | 0    | 0             | AN4                  | AN4                |  |  |  |  |

|                    |      | 1             | AN5                  | AN4, AN5           |  |  |  |  |

|                    | 1    | 0             | AN6                  | AN4 to AN6         |  |  |  |  |

|                    |      | 1             | AN7                  | AN4 to AN7         |  |  |  |  |

Only set the input channel while conversion is stopped (ADST = 0).

### 16.2.3 A/D Control Register (ADCR)

| Bit        | :      | 7     | 6          | 5 | 4        | 3        | 2        | 1 | 0 |

|------------|--------|-------|------------|---|----------|----------|----------|---|---|

|            |        | TRGS1 | TRGS0      |   |          | —        |          | _ | — |

| Initial va | alue : | 0     | 0          | 1 | 1        | 1        | 1        | 1 | 1 |

| R/W        | :      | R/W   | R/W        |   | —        | —/(R/W)* | —/(R/W)* | — | — |

|            |        |       | 0/0000 110 |   | 100/0000 |          | 000      |   |   |

Note: \* Applies to the H8S/2398, H8S/2394, H8S/2392, and H8S/2390.

ADCR is an 8-bit readable/writable register that enables or disables external triggering of A/D conversion operations.

ADCR is initialized to H'3F by a reset, and in standby mode or module stop mode.

**Bits 7 and 6—Timer Trigger Select 1 and 0 (TRGS1, TRGS0):** Select enabling or disabling of the start of A/D conversion by a trigger signal. Only set bits TRGS1 and TRGS0 while conversion is stopped (ADST = 0).

| Bit 7<br>TRGS1 | Bit 6<br>TRGS0 | Description                                                                           |        |

|----------------|----------------|---------------------------------------------------------------------------------------|--------|

| 0              | 0              | A/D conversion start by external trigger is disabled (Initial                         | value) |

|                | 1              | A/D conversion start by external trigger (TPU) is enabled                             |        |

| 1              | 0              | A/D conversion start by external trigger (8-bit timer) is enabled                     |        |

|                | 1              | A/D conversion start by external trigger pin ( $\overline{\text{ADTRG}}$ ) is enabled |        |

#### (1) For H8S/2357 and H8S/2352

Bits 5 to 0—Reserved: They are always read as 1 and cannot be modified.

(2) For H8S/2398, H8S/2394, H8S/2392, and H8S/2390

Bits 5, 4, 1, and 0—Reserved: They are always read as 1 and cannot be modified.

Bits 3 and 2—Reserved: Should always be written with 1.

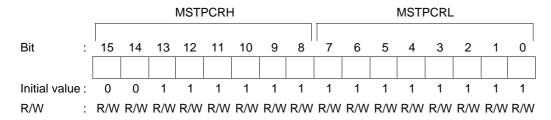

### 16.2.4 Module Stop Control Register (MSTPCR)

MSTPCR is a 16-bit readable/writable register that performs module stop mode control.

When the MSTP9 bit in MSTPCR is set to 1, A/D converter operation stops at the end of the bus cycle and a transition is made to module stop mode. Registers cannot be read or written to in module stop mode. For details, see section 21.5, Module Stop Mode.

MSTPCR is initialized to H'3FFF by a reset and in hardware standby mode. It is not initialized in software standby mode.

Bit 9—Module Stop (MSTP9): Specifies the A/D converter module stop mode.

| Bit 9<br>MSTP9 | Description                            |                 |

|----------------|----------------------------------------|-----------------|

| 0              | A/D converter module stop mode cleared |                 |

| 1              | A/D converter module stop mode set     | (Initial value) |

# Section 20 Clock Pulse Generator

# 20.1 Overview

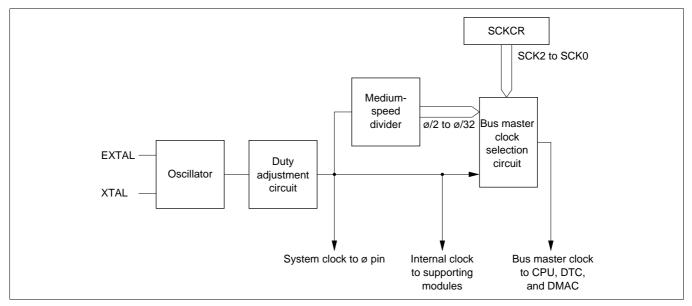

The H8S/2357 Group has a on-chip clock pulse generator (CPG) that generates the system clock ( $\phi$ ), the bus master clock, and internal clocks.

The clock pulse generator consists of an oscillator circuit, a duty adjustment circuit, a medium-speed clock divider, and a bus master clock selection circuit.

### 20.1.1 Block Diagram

Figure 20-1 shows a block diagram of the clock pulse generator.

Figure 20-1 Block Diagram of Clock Pulse Generator

### 20.1.2 Register Configuration

The clock pulse generator is controlled by SCKCR. Table 20-1 shows the register configuration.

### Table 20-1 Clock Pulse Generator Register

|      | Name                          | Abbreviation | R/W | Initial Value | Address* |

|------|-------------------------------|--------------|-----|---------------|----------|

|      | System clock control register | SCKCR        | R/W | H'00          | H'FF3A   |

| NI ( |                               |              |     |               |          |

Note:\* Lower 16 bits of the address.

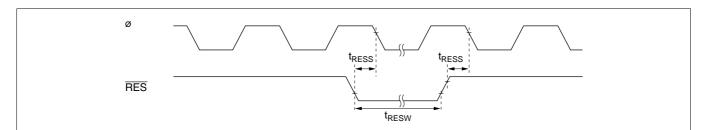

Figure 22-38 Reset Input Timing

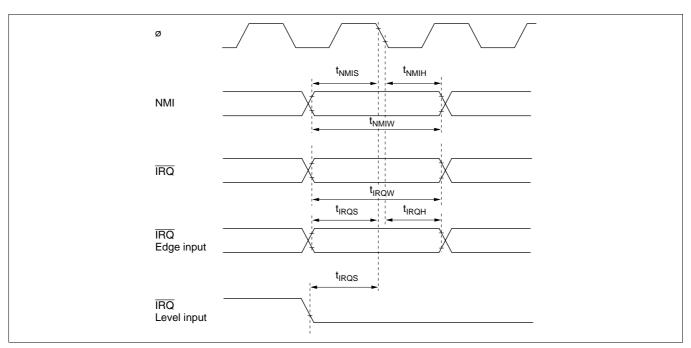

Figure 22-39 Interrupt Input Timing

| Item                              |                                     | Symbol                         | Min | Тур            | Max | Unit | <b>Test Conditions</b>                             |

|-----------------------------------|-------------------------------------|--------------------------------|-----|----------------|-----|------|----------------------------------------------------|

| Current dissipation* <sup>2</sup> | Normal operation                    | I <sub>CC</sub> * <sup>4</sup> | _   | 32<br>(3.3 V)  | 80  | mA   | f = 13 MHz                                         |

|                                   | Sleep mode                          |                                | _   | 22<br>(3.3 V)  | 55  | mA   | f = 13 MHz                                         |

|                                   | Standby                             | _                              | _   | 0.01           | 5.0 | μΑ   | $T_a \le 50^{\circ}C$                              |

|                                   | mode* <sup>3</sup>                  |                                | _   | _              | 20  | _    | 50°C < T <sub>a</sub>                              |

|                                   | Flash memory programming/ erasing   |                                | _   | 42<br>(3.3 V)  | 80  | mA   | $0^{\circ}C \le T_a \le 75^{\circ}C$<br>f = 13 MHz |

| Analog power supply current       | During A/D<br>and D/A<br>conversion | Al <sub>cc</sub>               | _   | 0.3<br>(3.3 V) | 2.0 | mA   |                                                    |

|                                   | Idle                                |                                |     | 0.01           | 5.0 | μA   | _                                                  |

| Reference<br>current              | During A/D<br>and D/A<br>conversion | Al <sub>cc</sub>               | _   | 1.6<br>(3.3 V) | 3.0 | mA   |                                                    |

|                                   | Idle                                |                                | _   | 0.01           | 5.0 | μA   |                                                    |

| RAM standby voltage               |                                     | $V_{RAM}$                      | 2.0 | _              | _   | V    |                                                    |

Notes: 1. If the A/D and D/A converters are not used, do not leave the  $AV_{cc}$ ,  $AV_{ss}$ , and  $V_{ref}$  pins open.

Connect  $AV_{cc}$  and  $V_{ref}$  to  $V_{cc}$ , and connect  $AV_{ss}$  to  $V_{ss}$ . 2. Current dissipation values are for  $V_{IH}$  min =  $V_{cc}$  –0.5 V and  $V_{IL}$  max = 0.5 V with all output pins unloaded and the on-chip pull-up transistors in the off state.

3. The values are for V\_{\_{RAM}} \leq V\_{\_{CC}} < 3.0 V, V  $_{_{I\!H}}$  min = V  $_{_{CC}} \times 0.9$ , and V  $_{_{I\!L}}$  max = 0.3 V.

4.

$$I_{cc}$$

depends on  $V_{cc}$  and f as follows:

$I_{cc}$  max = 1.0 (mA) + 1.1 (mA/(MHz × V)) ×  $V_{cc}$  × f [normal mode]

$I_{cc}$  max = 1.0 (mA) + 0.75 (mA/(MHz × V)) ×  $V_{cc}$  × f [sleep mode]

#### **Table 22-35 Permissible Output Currents**

Conditions:  $V_{CC} = 3.0$  to 5.5 V,  $AV_{CC} = 3.0$  to 5.5 V,  $V_{ref} = 3.0$  V to  $AV_{CC}$ ,  $V_{SS} = AV_{SS} = 0$  V,

$T_a = -20$  to +75°C (regular specifications),  $T_a = -40$  to +85°C (wide-range specifications)

| Item                                         |                                                     | Symbol            | Min | Тур | Max | Unit |

|----------------------------------------------|-----------------------------------------------------|-------------------|-----|-----|-----|------|

| Permissible output                           | Ports 1, A to C                                     | I <sub>ol</sub>   | _   | _   | 10  | mA   |

| low current (per pin)                        | Other output pins                                   |                   |     | _   | 2.0 | mA   |

| Permissible output<br>low current (total)    | Total of 32 pins<br>including ports 1<br>and A to C | $\sum I_{OL}$     | _   | _   | 80  | mA   |

|                                              | Total of all output<br>pins, including the<br>above |                   | _   | _   | 120 | mA   |

| Permissible output<br>high current (per pin) | All output pins                                     | —I <sub>он</sub>  | _   | —   | 2.0 | mA   |

| Permissible output<br>high current (total)   | Total of all output pins                            | $\Sigma - I_{OH}$ | _   | —   | 40  | mA   |

Notes: 1. To protect chip reliability, do not exceed the output current values in table 22-35.

2. When driving a darlington pair or LED directly, always insert a current-limiting resistor in the output line, as show in figures 22-65 and 22-66.

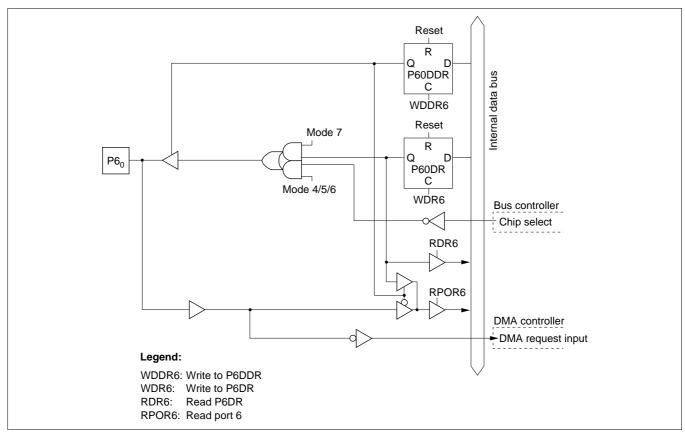

# C.6 Port 6 Block Diagram

Figure C-6 (a) Port 6 Block Diagram (Pin P6<sub>0</sub>)

# C.10 Port D Block Diagram

Figure C-10 Port D Block Diagram (Pin PD<sub>0</sub> to PD<sub>7</sub>)

# Renesas Technology Corp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

#### **RENESAS SALES OFFICES**

http://www.renesas.com

Refer to "http://www.renesas.com/en/network" for the latest and detailed information.

Renesas Technology America, Inc. 450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

Renesas Technology Europe Limited Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K. Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

Renesas Technology Hong Kong Ltd. 7th Floor, North Tower, World Finance Centre, Harbour City, 1 Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2730-6071

Renesas Technology Taiwan Co., Ltd. 10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 2713-2999

Renesas Technology (Shanghai) Co., Ltd. Unit2607 Ruijing Building, No.205 Maoming Road (S), Shanghai 200020, China Tel: <86> (21) 6472-1001, Fax: <86> (21) 6415-2952

Renesas Technology Singapore Pte. Ltd. 1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001