Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-UQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-UQFN (6x6)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f25k83-i-mx |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.3.2 LOOK-UP TABLES IN PROGRAM MEMORY

There may be programming situations that require the creation of data structures, or look-up tables, in program memory. For PIC18 devices, look-up tables can be implemented in two ways:

- Computed GOTO

- Table Reads

#### 4.3.2.1 **Computed** GOTO

A computed GOTO is accomplished by adding an offset to the Program Counter. An example is shown in Example 4-2.

A look-up table can be formed with an ADDWF PCL instruction and a group of RETLW nn instructions. The W register is loaded with an offset into the table before executing a call to that table. The first instruction of the called routine is the ADDWF PCL instruction. The next instruction executed will be one of the RETLW nn instructions that returns the value 'nn' to the calling function.

The offset value (in WREG) specifies the number of bytes that the Program Counter should advance and should be multiples of two (LSb = 0).

In this method, only one data byte may be stored in each instruction location and room on the return address stack is required.

#### EXAMPLE 4-2: COMPUTED GOTO USING AN OFFSET VALUE

|       | MOVF  | OFFSET, | W |

|-------|-------|---------|---|

|       | CALL  | TABLE   |   |

| ORG   | nn00h |         |   |

| TABLE | ADDWF | PCL     |   |

|       | RETLW | nnh     |   |

|       | RETLW | nnh     |   |

|       | RETLW | nnh     |   |

|       |       |         |   |

|       |       |         |   |

|       |       |         |   |

|       |       |         |   |

#### 4.3.2.2 Table Reads and Table Writes

A better method of storing data in program memory allows two bytes of data to be stored in each instruction location.

Look-up table data may be stored two bytes per program word by using table reads and writes. The Table Pointer (TBLPTR) register specifies the byte address and the Table Latch (TABLAT) register contains the data that is read from or written to program memory.

Table read and table write operations are discussed further in Section 13.1.1 "Table Reads and Table Writes".

#### 4.7 Data Addressing Modes

Note: The execution of some instructions in the core PIC18 instruction set are changed when the PIC18 extended instruction set is enabled. See Section 4.8 "Data Memory and the Extended Instruction Set" for more information.

While the program memory can be addressed in only one way – through the Program Counter – information in the data memory space can be addressed in several ways. For most instructions, the addressing mode is fixed. Other instructions may use up to three modes, depending on which operands are used and whether or not the extended instruction set is enabled.

The addressing modes are:

- Inherent

- Literal

- Direct

- Indirect

An additional addressing mode, Indexed Literal Offset, is available when the extended instruction set is enabled (XINST Configuration bit = 1). Its operation is discussed in detail in **Section 4.8.1 "Indexed Addressing with Literal Offset**".

### 4.7.1 INHERENT AND LITERAL ADDRESSING

Many PIC18 control instructions do not need any argument at all; they either perform an operation that globally affects the device or they operate implicitly on one register. This addressing mode is known as Inherent Addressing. Examples include SLEEP, RESET and DAW.

Other instructions work in a similar way but require an additional explicit argument in the opcode. This is known as Literal Addressing mode because they require some literal value as an argument. Examples include ADDLW and MOVLW, which respectively, add or move a literal value to the W register. Other examples include CALL and GOTO, which include a 20-bit program memory address.

. . . . . . . .

| U-0            | U-0                         | U-0              | U-0         | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|----------------|-----------------------------|------------------|-------------|----------------|------------------|------------------|--------------|

|                |                             | _                | _           |                |                  | <3:0>            |              |

| bit 7          |                             |                  |             |                |                  |                  | bit          |

| Legend:        |                             |                  |             |                |                  |                  |              |

| R = Readal     | ole bit                     | W = Writable     | bit         | U = Unimplen   | nented bit, read | d as '0'         |              |

| u = Bit is ur  | nchanged                    | x = Bit is unk   | nown        | -n/n = Value a | t POR and BC     | R/Value at all o | other Resets |

| '1' = Bit is s | •                           | '0' = Bit is cle | ared        |                |                  |                  |              |

| hit 7 4        | Unimplomon                  | ted. Dood oo '   | 0'          |                |                  |                  |              |

| bit 7-4        |                             |                  |             |                |                  |                  |              |

| bit 3-0        | CLK<3:0>: C<br>1111 = Reser |                  | ection bits |                |                  |                  |              |

|                |                             | ved              |             |                |                  |                  |              |

|                | •                           |                  |             |                |                  |                  |              |

|                | •                           |                  |             |                |                  |                  |              |

|                | •<br>1011 = Reser           | hed              |             |                |                  |                  |              |

|                | 1011 = Reset                |                  |             |                |                  |                  |              |

|                | 1001 = CLC3                 | •                |             |                |                  |                  |              |

|                | 1000 = CLC2                 | •                |             |                |                  |                  |              |

|                | 0111 = CLC1                 | •                |             |                |                  |                  |              |

|                | 0110 = NCO1                 | •                |             |                |                  |                  |              |

|                | 0101 <b>= SOSC</b>          | •                |             |                |                  |                  |              |

|                | 0100 = MFIN                 | TOSC (31.25      | (Hz)        |                |                  |                  |              |

|                | 0011 = MFIN                 | TOSC (500 k⊦     | lz)         |                |                  |                  |              |

|                | 0010 = LFINT                | OSC (31 kHz      | )           |                |                  |                  |              |

|                | 0001 = HFIN <sup>-</sup>    | TOSC             |             |                |                  |                  |              |

|                | 0000 = Fosc                 |                  |             |                |                  |                  |              |

#### TABLE 8-1: SUMMARY OF REGISTERS ASSOCIATED WITH CLOCK REFERENCE OUTPUT

| Name    | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2    | Bit 1 | Bit 0 | Register<br>on Page |

|---------|-------|-------|-------|---------|-------|----------|-------|-------|---------------------|

| CLKRCON | EN    | _     | _     | DC<1:0> |       | DIV<2:0> |       |       | 103                 |

| CLKRCLK | _     | _     |       | -       | _     | CLK<2:0> |       | 104   |                     |

Legend: — = unimplemented, read as '0'. Shaded cells are not used by the CLKR module.

| Name      | Bit 7       | Bit 6       | Bit 5 | Bit 4  | Bit 3  | Bit 2    | Bit 1   | Bit 0 | Register<br>on Page |  |

|-----------|-------------|-------------|-------|--------|--------|----------|---------|-------|---------------------|--|

| CRCACCH   |             | ACC<15:8>   |       |        |        |          |         |       |                     |  |

| CRCACCL   |             | ACC<7:0>    |       |        |        |          |         |       |                     |  |

| CRCCON0   | EN          | GO          | BUSY  | ACCM   | —      | —        | SHIFTM  | FULL  | 208                 |  |

| CRCCON1   |             | DLEN<       | 3:0>  |        |        | PLE      | N<3:0>  |       | 208                 |  |

| CRCDATH   |             |             |       | DATA   | <15:8> |          |         |       | 209                 |  |

| CRCDATL   |             | DATA<7:0>   |       |        |        |          |         |       | 209                 |  |

| CRCSHIFTH |             | SHIFT<15:8> |       |        |        |          |         |       | 210                 |  |

| CRCSHIFTL | SHIFT<7:0>  |             |       |        |        |          |         | 210   |                     |  |

| CRCXORH   |             | X<15:8>     |       |        |        |          |         |       | 211                 |  |

| CRCXORL   |             |             |       | X<7:1> |        |          |         | -     | 211                 |  |

| SCANCON0  | EN          | TRIGEN      | SGO   | —      | —      | MREG     | BURSTMD | BUSY  | 212                 |  |

| SCANHADRU |             | -           |       |        | HADF   | R<21:16> |         |       | 214                 |  |

| SCANHADRH |             |             |       | HADR   | <15:8> |          |         |       | 215                 |  |

| SCANHADRL |             |             |       | HADF   | R<7:0> |          |         |       | 215                 |  |

| SCANLADRU | LADR<21:16> |             |       |        |        |          |         | 213   |                     |  |

| SCANLADRH | LADR<15:8>  |             |       |        |        |          |         | 213   |                     |  |

| SCANLADRL |             |             |       | LADF   | R<7:0> |          |         |       | 214                 |  |

| SCANTRIG  |             | _           | _     | _      |        | TSE      | _<3:0>  |       | 216                 |  |

TABLE 14-2: SUMMARY OF REGISTERS ASSOCIATED WITH CRC

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used for the CRC module.

#### REGISTER 22-3: TxTMR: TIMERx COUNTER REGISTER

| R/W-0/0          | R/W-0/0 | R/W-0/0                                                               | R/W-0/0 | R/W-0/0      | R/W-0/0          | R/W-0/0      | R/W-0/0 |

|------------------|---------|-----------------------------------------------------------------------|---------|--------------|------------------|--------------|---------|

|                  |         |                                                                       | TMR>    | (<7:0>       |                  |              |         |

| bit 7            |         |                                                                       |         |              |                  |              | bit 0   |

|                  |         |                                                                       |         |              |                  |              |         |

| Legend:          |         |                                                                       |         |              |                  |              |         |

| R = Readable     | bit     | W = Writable I                                                        | bit     | U = Unimpler | nented bit, read | d as '0'     |         |

| u = Bit is unch  | anged   | x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Res |         |              |                  | other Resets |         |

| '1' = Bit is set |         | '0' = Bit is clea                                                     | ared    |              |                  |              |         |

bit 7-0 **TMRx<7:0>:** Timerx Counter bits

#### **REGISTER 22-4: TxPR: TIMERx PERIOD REGISTER**

| R/W-1/1        | R/W-1/1 | R/W-1/1         | R/W-1/1 | R/W-1/1      | R/W-1/1          | R/W-1/1  | R/W-1/1 |

|----------------|---------|-----------------|---------|--------------|------------------|----------|---------|

|                |         |                 | PRx<    | <7:0>        |                  |          |         |

| bit 7          |         |                 |         |              |                  |          | bit 0   |

|                |         |                 |         |              |                  |          |         |

| Legend:        |         |                 |         |              |                  |          |         |

| R = Readable b | it      | W = Writable bi | it      | U = Unimpler | mented bit, read | d as '0' |         |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| R = Readable bit     | vv = vvritable bit   | U = Unimplemented bit, read as 'U'                    |

bit 7-0 **PRx<7:0>:** Timerx Period Register bits

#### 23.4.2 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for standard PWM operation:

- Use the desired output pin RxyPPS control to select CCPx as the source and disable the CCPx pin output driver by setting the associated TRIS bit.

- 2. Load the T2PR register with the PWM period value.

- Configure the CCP module for the PWM mode by loading the CCPxCON register with the appropriate values.

- 4. Load the CCPRxL register, and the CCPRxH register with the PWM duty cycle value and configure the FMT bit of the CCPxCON register to set the proper register alignment.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the respective PIR register. See Note below.

- Select the timer clock source to be as Fosc/4 using the T2CLK register. This is required for correct operation of the PWM module.

- Configure the CKPS bits of the T2CON register with the Timer prescale value.

- Enable the Timer by setting the ON bit of the T2CON register.

- 6. Enable PWM output pin:

- Wait until the Timer overflows and the TMR2IF bit of the PIR4 register is set. See Note below.

- Enable the CCPx pin output driver by clearing the associated TRIS bit.

**Note:** In order to send a complete duty cycle and period on the first PWM output, the above steps must be included in the setup sequence. If it is not critical to start with a complete PWM signal on the first output, then step 6 may be ignored.

#### 23.4.3 TIMER2 TIMER RESOURCE

The PWM standard mode makes use of the 8-bit Timer2 timer resources to specify the PWM period.

#### 23.4.4 PWM PERIOD

The PWM period is specified by the T2PR register of Timer2. The PWM period can be calculated using the formula of Equation 23-1.

#### EQUATION 23-1: PWM PERIOD

$PWM Period = [(T2PR) + 1] \bullet 4 \bullet Tosc \bullet$ (TMR2 Prescale Value)

Note 1: Tosc = 1/Fosc

When T2TMR is equal to T2PR, the following three events occur on the next increment cycle:

- T2TMR is cleared

- The CCPx pin is set. (Exception: If the PWM duty cycle = 0%, the pin will not be set.)

- The PWM duty cycle is transferred from the CCPRxL/H register pair into a 10-bit buffer.

Note: The Timer postscaler (see Section 22.3 "External Reset Sources") is not used in the determination of the PWM frequency.

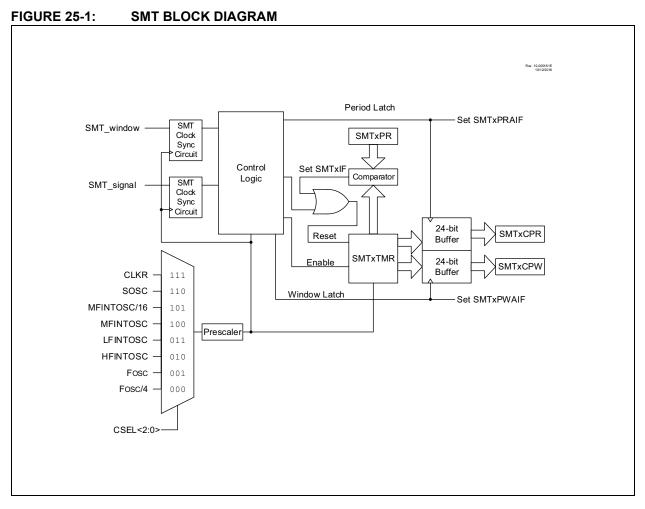

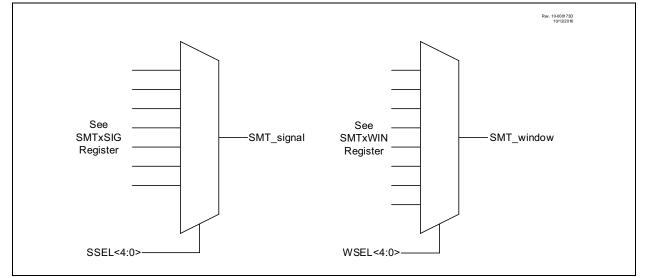

# PIC18(L)F25/26K83

FIGURE 25-2: SMT SIGNAL AND WINDOW BLOCK DIAGRAM

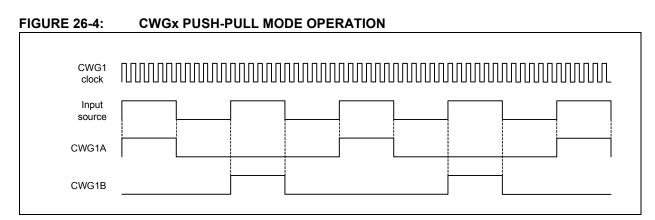

#### 26.2.3 FULL-BRIDGE MODES

In Forward and Reverse Full-Bridge modes, three outputs drive static values while the fourth is modulated by the input data signal. The mode selection may be toggled between forward and reverse by toggling the MODE<0> bit of the CWGxCON0 while keeping MODE<2:1> static, without disabling the CWG module. When connected as shown in Figure 26-5, the outputs are appropriate for a full-bridge motor driver. Each CWG output signal has independent polarity control, so the circuit can be adapted to high-active and low-active drivers. A simplified block diagram for the Full-Bridge modes is shown in Figure 26-6.

#### 26.9 Dead-Band Jitter

When the rising and falling edges of the input source are asynchronous to the CWG clock, it creates jitter in the dead-band time delay. The maximum jitter is equal to one CWG clock period. Refer to Equation 26-1 for more details.

### EQUATION 26-1: DEAD-BAND DELAY TIME CALCULATION

$T_{DEAD - BAND\_MIN} = \frac{1}{F_{CWG} CLOCK} \bullet DBx < 4:0>$   $T_{DEAD - BANDMAX} = \frac{1}{F_{CWG} CLOCK} \bullet DBx < 4:0>+1$   $T_{JITTER} = T_{DEAD - BAND\_MAX} - T_{DEAD - BAND\_MIN}$   $T_{JITTER} = \frac{1}{F_{CWG\_CLOCK}}$   $T_{DEAD - BAND\_MAX} = T_{DEAD - BAND\_MIN} + T_{JITTER}$  EXAMPLE DBR < 4:0>= 0x0A = 10  $F_{CWG\_CLOCK} = 8 MHz$   $T_{JITTER} = \frac{1}{8MHz} = 125 \text{ ns}$   $T_{DEAD - BAND\_MIN} = 125 \text{ ns} *10 = 125 \text{ µs}$   $T_{DEAD - BAND\_MIN} = 1.25 \text{ µs} + 0.125 \text{ µs} = 1.37 \text{µs}$

### 27.0 CONFIGURABLE LOGIC CELL (CLC)

The Configurable Logic Cell (CLCx) module provides programmable logic that operates outside the speed limitations of software execution. The logic cell takes up to 32 input signals and, through the use of configurable gates, reduces the 32 inputs to four logic lines that drive one of eight selectable single-output logic functions.

Input sources are a combination of the following:

- · I/O pins

- Internal clocks

- · Peripherals

- Register bits

The output can be directed internally to peripherals and to an output pin.

There are four CLC modules available on this device - CLC1, CLC2, CLC3 and CLC4.

Note: The CLC1, CLC2, CLC3 and CLC4 are four separate module instances of the same CLC module design. Throughout this section, the lower case 'x' in register names is a generic reference to the CLC number (which should be substituted with 1, 2, 3, or 4 during code development). For example, the control register is generically described in this chapter as CLCxCON, but the actual device registers are CLC1CON, CLC2CON, CLC3CON and CLC4CON.

Refer to Figure 27-1 for a simplified diagram showing signal flow through the CLCx.

Possible configurations include:

- Combinatorial Logic

- AND

- NAND

- AND-OR

- AND-OR-INVERT

- OR-XOR

- OR-XNOR

- Latches

- S-R

- Clocked D with Set and Reset

- Transparent D with Set and Reset

| TABLE 27-1: | CLCx DATA INPUT |

|-------------|-----------------|

|             | SELECTION       |

|             |                 |

|                    | LECTION           |

|--------------------|-------------------|

| DyS<5:0><br>Value  | CLCx Input Source |

| 111111 [63]        | Reserved          |

| •                  |                   |

| •                  | -                 |

| •                  | -                 |

| 110110 [55]        | -                 |

| 110110 <b>[54]</b> | CAN_tx1           |

| 110101 <b>[53]</b> | CAN_tx0           |

| 110100 <b>[52]</b> | CWG3B_out         |

| 110011 <b>[51]</b> | CWG3A_out         |

| 110010 <b>[50]</b> | CWG2B_out         |

| 110001 <b>[49]</b> | CWG2A_out         |

| 110000 <b>[48]</b> | CWG1B_out         |

| 101111 [47]        | CWG1A_out         |

| 101110 <b>[46]</b> | SS1               |

| 101101 [45]        | SCK1              |

| 101100 <b>[44]</b> | SDO1              |

| 101011 <b>[43]</b> | Reserved          |

| 101010 <b>[42]</b> | UART2_tx_out      |

| 101001 <b>[41]</b> | UART1_tx_out      |

| 101000 <b>[40]</b> | CLC4_out          |

| 100111 <b>[39]</b> | CLC3_out          |

| 100110 <b>[38]</b> | CLC2_out          |

| 100101 <b>[37]</b> | CLC1_out          |

| 100100 <b>[36]</b> | DSM1_out          |

| 100011 <b>[35]</b> | IOC_flag          |

| 100010 [34]        | ZCD_out           |

| 100001 <b>[33]</b> | CMP2_out          |

| 100000 <b>[32]</b> | CMP1_out          |

| 011111 [31]        | NCO1_out          |

| 011110 [30]        | Reserved          |

| 011101 [29]        | Reserved          |

| 011100 [28]        | PWM8_out          |

| 011011 [27]        | PWM7_out          |

| 011010 [26]        | PWM6_out          |

| 011001 [25]        | PWM5_out          |

| 011000 [24]        | CCP4_out          |

| 010111 [23]        | CCP3_out          |

| 010110 [22]        | CCP2_out          |

| 010101 [21]        | CCP1_out          |

| 010100 [20]        | SMT2_out          |

| 010011 [19]        | SMT1_out          |

| 010010 [18]        | TMR6_out          |

### TABLE 27-1:CLCx DATA INPUT SELECTION<br/>(CONTINUED)

| DyS<5:0><br>Value | CLCx Input Source  |

|-------------------|--------------------|

| 010001 [17]       | TMR5 _overflow     |

| 010000 [16]       | TMR4 _out          |

| 001111 [15]       | TMR3 _overflow     |

| 001110 [14]       | TMR2 _out          |

| 001101 [13]       | TMR1 _overflow     |

| 001100 [12]       | TMR0 _overflow     |

| 001011 [11]       | CLKR _out          |

| 001010 [10]       | ADCRC              |

| 001001 [9]        | SOSC               |

| 001000 [8]        | MFINTOSC (32 kHz)  |

| 000111 [7]        | MFINTOSC (500 kHz) |

| 000110 [6]        | LFINTOSC           |

| 000101 [5]        | HFINTOSC           |

| 000100 [4]        | Fosc               |

| 000011 [3]        | CLCIN3PPS          |

| 000010 [2]        | CLCIN2PPS          |

| 000001 [1]        | CLCIN1PPS          |

| 000000 <b>[0]</b> | CLCIN0PPS          |

#### 28.1 NCO Operation

The NCO operates by repeatedly adding a fixed value to an accumulator. Additions occur at the input clock rate. The accumulator will overflow with a carry periodically, which is the raw NCO output (NCO\_overflow). This effectively reduces the input clock by the ratio of the addition value to the maximum accumulator value. See Equation 28-1.

The NCO output can be further modified by stretching the pulse or toggling a flip-flop. The modified NCO output is then distributed internally to other peripherals and can be optionally output to a pin. The accumulator overflow also generates an interrupt (NCO\_overflow).

The NCO period changes in discrete steps to create an average frequency. This output depends on the ability of the receiving circuit (i.e., CWG or external resonant converter circuitry) to average the NCO output to reduce uncertainty.

#### EQUATION 28-1: NCO OVERFLOW FREQUENCY

$FoverFLow = \frac{NCO \ Clock \ Frequency \times Increment \ Value}{2^{20}}$

#### 28.1.1 NCO CLOCK SOURCES

Clock sources available to the NCO include:

- Fosc

- HFINTOSC

- LFINTOSC

- MFINTOSC/4 (32 kHz)

- MFINTOSC (500 kHz)

- CLC1/2/3/4\_out

- CLKREF

- SOSC

The NCO clock source is selected by configuring the N1CKS<2:0> bits in the NCO1CLK register.

#### 28.1.2 ACCUMULATOR

The accumulator is a 20-bit register. Read and write access to the accumulator is available through three registers:

- NCO1ACCL

- NCO1ACCH

- NCO1ACCU

#### 28.1.3 ADDER

The NCO Adder is a full adder, which operates independently from the source clock. The addition of the previous result and the increment value replaces the accumulator value on the rising edge of each input clock.

#### 28.1.4 INCREMENT REGISTERS

The increment value is stored in three registers making up a 20-bit incrementer. In order of LSB to MSB they are:

- NCO1INCL

- NCO1INCH

- NCO1INCU

When the NCO module is enabled, the NCO1INCU and NCO1INCH registers should be written first, then the NCO1INCL register. Writing to the NCO1INCL register initiates the increment buffer registers to be loaded simultaneously on the second rising edge of the NCO\_clk signal.

The registers are readable and writable. The increment registers are double-buffered to allow value changes to be made without first disabling the NCO module.

When the NCO module is disabled, the increment buffers are loaded immediately after a write to the increment registers.

**Note:** The increment buffer registers are not useraccessible.

#### 31.17.2 AUTO-BAUD OVERFLOW

During the course of automatic baud detection, the ABDOVF bit in the UxERRIR register will be set if the baud rate counter overflows before the fifth falling edge is detected on the RX pin. The ABDOVF bit indicates that the counter has exceeded the maximum count that can fit in the 16 bits of the UxBRGH:UxBRGL register pair. After the ABDOVF bit has been set, the state machine continues to search until the fifth falling edge is detected on the RX pin. Upon detecting the fifth falling RX edge, the hardware will set the ABDIF interrupt flag and clear the ABDEN bit in the UxCON0 register. The UxBRGH and UxBRGL register values retain their previous value. The ABDIF flag in the UxUIR register and ABDOVF flag in the UxERRIR register can be cleared by software directly. To generate an interrupt on an auto-baud overflow condition, all the following bits must be set:

- ABDOVE bit in the UxERRIE register

- UxEIE bit in the PIEx register

- PIE and GIE bits in the INTCON register

To terminate the auto-baud process before the ABDIF flag is set, clear the ABDEN bit, then clear the ABDOVF bit in the UxERRIR register.

#### 31.17.3 AUTO-WAKE-UP ON BREAK

During Sleep mode, all clocks to the UART are suspended. Because of this, the Baud Rate Generator is inactive and a proper character reception cannot be performed. The Auto-Wake-up feature allows the controller to wake-up due to activity on the RX line.

The Auto-Wake-up feature is enabled by setting both the WUE bit in the UxCON1 register and the UxIE bit in the PIEx register. Once set, the normal receive sequence on RX is disabled, and the UART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a transition out of the Idle state on the RX line. (This coincides with the start of a Break or a wake-up signal character for the LIN protocol.)

The UART module generates a WUIF interrupt coincident with the wake-up event. The interrupt is generated synchronously to the Q clocks in normal CPU operating modes (Figure 31-13), and asynchronously, if the device is in Sleep mode (Figure 31-14). The interrupt condition is cleared by clearing the WUIF bit in the UxUIR register. To generate an interrupt on a wake-up event, all the following bits must be set:

- UxIE bit in the PIEx register

- PIE and GIE bits in the INTCON register

The WUE bit is automatically cleared by the transition to the Idle state on the RX line at the end of the Break. This signals to the user that the Break event is over. At this point, the UART module is in Idle mode, waiting to receive the next character.

#### 31.17.3.1 Special Considerations

#### **Break Character**

To avoid character errors or character fragments during a wake-up event, the wake-up character must be all zeros.

When the wake-up is enabled, the function works independent of the low time on the data stream. If the WUE bit is set and a valid non-zero character is received, the low time from the Start bit to the first rising edge will be interpreted as the wake-up event. The remaining bits of the character will be received as a fragmented character and subsequent characters can result in framing or overrun errors.

Therefore, the initial character of the transmission must be all zeros. This must be eleven or more bit times, 13bit times recommended for LIN bus, or any number of bit times for standard RS-232 devices.

#### **Oscillator Start-up Time**

Oscillator start-up time must be considered, especially in applications using oscillators with longer start-up intervals (i.e., LP, XT or HS/PLL modes). The Sync Break (or wake-up signal) character must be of sufficient length, and be followed by a sufficient interval, to allow enough time for the selected oscillator to start and provide proper initialization of the UART.

#### WUE Bit

To ensure that no actual data is lost, check the RXIDL bit to verify that a receive operation is not in process before setting the WUE bit. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

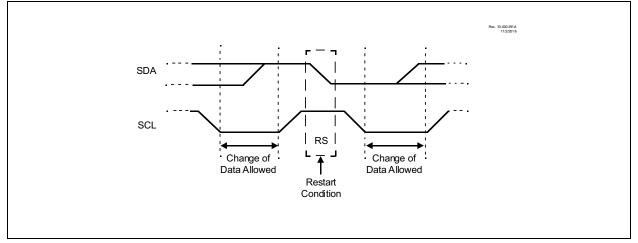

#### 33.3.7 RESTART CONDITION

A Restart is valid any time that a Stop would be valid. A master can issue a Restart if it wishes to hold the bus after terminating the current transfer. A Restart has the same effect on the slave that a Start would, resetting all slave logic and preparing it to clock in an address. The master may want to address the same or another slave. Figure 33-4 shows the waveform for a Restart condition.

FIGURE 33-4: RESTART CONDITION

In 10-bit Addressing Slave mode a Restart is required for the master to clock data out of the addressed slave. Once a slave has been fully addressed, matching both high and low address bytes (SMA = 1), the master can issue a Restart and the high address byte with the R/W bit set. The slave logic will then hold the clock and prepare to clock out data.

#### 33.3.8 ACKNOWLEDGE SEQUENCE

The ninth SCL pulse for any transferred byte in  $I^2C$  is dedicated as an Acknowledge. It allows receiving devices to respond back to the transmitter by pulling the SDA line low. The transmitter must release control of the line during this time to shift in the response. The Acknowledge (ACK) is an active-low signal, pulling the SDA line low indicates to the transmitter that the device has received the transmitted data and is ready to receive more.

The result of an ACK is placed in the ACKSTAT bit of the I2CxCON1 register. The ACKSTAT bit is cleared when the receiving device sends an Acknowledge and is set when the receiving device does not Acknowledge. A slave sends an Acknowledge when it has recognized its address. When in a mode that is receiving data, the ACK data being sent to the transmitter depends on the value of I2CxCNT register. ACKDT is the value sent when I2CxCNT! = 0. When I2CxCNT = 0, the ACKCNT value is used instead.

In Slave mode, if the ADRIE or WRIE bits are set, clock stretching is initiated when there is an address match or when there is an attempt to write to slave. This allows the user to set the ACK value sent back to the transmitter. The ACKDT bit of the I2CxCON1 register is set/cleared to determine the response. Slave hardware will generate an ACK response if the ADRIE or WRIE bits are clear. Certain conditions will cause a not-ACK (NACK) to be sent automatically. If any of the RXRE, TXRE, RXO, or TXU bits is set, the hardware response is forced to NACK. All subsequent responses from the device for address matches or data will be a NACK response.

#### 33.3.9 BUS TIME-OUT

The I2CxBTO register can be used to select the timeout source for the module. The I<sup>2</sup>C module is reset when the selected bus time out signal goes high. This feature is useful for SMBus and PMBus<sup>TM</sup> compatibility.

For example, Timer2 can be selected as the bus timeout source and configured to count when the SCL pin is low. If the timer runs over before the SCL pin transitioned high, the timer-out pulse will reset the module.

Note: The bus time-out source should produce a rising edge.

If the module is configured as a slave and a BTO event occurs when the slave is active (i.e., the SMA bit is set), the module is immediately reset. The SMA and CSTR bits are also cleared, and the BTOIF bit is set.

### 34.15.3.1 Programmable TX/RX and Auto-RTR Buffers

The ECAN module contains six message buffers that can be programmed as transmit or receive buffers. Any of these buffers can also be programmed to automatically handle RTR messages.

**Note:** These registers are not used in Mode 0.

### REGISTER 34-22: BnCON: TX/RX BUFFER 'n' CONTROL REGISTERS IN RECEIVE MODE $[0 \le n \le 5, TXnEN (BSEL0 < n >) = 0]^{(1)}$

| R/W-0                | R/W-0 | R-0     | R-0     | R-0     | R-0     | R-0     | R-0     |

|----------------------|-------|---------|---------|---------|---------|---------|---------|

| RXFUL <sup>(2)</sup> | RXM1  | RXRTRRO | FILHIT4 | FILHIT3 | FILHIT2 | FILHIT1 | FILHIT0 |

| bit 7                |       |         |         |         |         |         | bit 0   |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 7   | RXFUL: Receive Full Status bit <sup>(2)</sup>                                                                                                                                 |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = Receive buffer contains a received message                                                                                                                                |

|         | 0 = Receive buffer is open to receive a new message                                                                                                                           |

| bit 6   | RXM1: Receive Buffer Mode bit                                                                                                                                                 |

|         | <ul> <li>1 = Receive all messages including partial and invalid (acceptance filters are ignored)</li> <li>0 = Receive all valid messages as per acceptance filters</li> </ul> |

| bit 5   | RXRTRRO: Read-Only Remote Transmission Request for Received Message bit                                                                                                       |

|         | 1 = Received message is a remote transmission request                                                                                                                         |

|         | 0 = Received message is not a remote transmission request                                                                                                                     |

| bit 4-0 | FILHIT<4:0>: Filter Hit bits                                                                                                                                                  |

|         | These bits indicate which acceptance filter enabled the last message reception into this buffer.                                                                              |

|         | 01111 = Acceptance Filter 15 (RXF15)                                                                                                                                          |

|         | 01110 = Acceptance Filter 14 (RXF14)                                                                                                                                          |

|         |                                                                                                                                                                               |

|         | 00001 = Acceptance Filter 1 (RXF1)                                                                                                                                            |

|         | 00000 = Acceptance Filter 0 (RXF0)                                                                                                                                            |

|         |                                                                                                                                                                               |

- **Note 1:** These registers are available in Mode 1 and 2 only.

- 2: This bit is set by the CAN module upon receiving a message and must be cleared by software after the buffer is read. As long as RXFUL is set, no new message will be loaded and the buffer will be considered full.

#### 40.0 HIGH/LOW-VOLTAGE DETECT (HLVD)

The PIC18(L)F25/26K83 family of devices has a High/ Low-Voltage Detect module (HLVD). This is a programmable circuit that sets both a device voltage trip point and the direction of change from that point (positive going, negative going or both). If the device experiences an excursion past the trip point in that direction, an interrupt flag is set. If the interrupt is enabled, the program execution branches to the interrupt vector address and the software responds to the interrupt.

Complete control of the HLVD module is provided through the HLVDCON0 and HLVDCON1 register. This allows the circuitry to be "turned off" by the user under software control, which minimizes the current consumption for the device.

The module's block diagram is shown in Figure 40-1.

Since the HLVD can be software enabled through the EN bit, setting and clearing the enable bit does not produce a false HLVD event glitch. Each time the HLVD module is enabled, the circuitry requires some time to stabilize. The RDY bit (HLVDCON0<4>) is a read-only bit used to indicate when the band gap reference voltages are stable.

The module can only generate an interrupt after the module is turned ON and the band gap reference voltages are ready.

The INTH and INTL bits determine the overall operation of the module. When INTH is set, the module monitors for rises in VDD above the trip point set by the HLVDCON1 register. When INTL is set, the module monitors for drops in VDD below the trip point set by the HLVDCON1 register. When both the INTH and INTL bits are set, any changes above or below the trip point set by the HLVDCON1 register can be monitored.

The OUT bit can be read to determine if the voltage is greater than or less than the voltage level selected by the HLVDCON1 register.

# PIC18(L)F25/26K83

| мо\   | /SS                          | Move Indexed to Indexed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                             |     |    |                   |  |  |  |  |

|-------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-----|----|-------------------|--|--|--|--|

| Synta | ax:                          | MOVSS [z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | MOVSS [z <sub>s</sub> ], [z <sub>d</sub> ]  |     |    |                   |  |  |  |  |

| Oper  | ands:                        | $0 \le z_s \le 127$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                             |     |    |                   |  |  |  |  |

|       |                              | $0 \le z_d \le 127$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                             |     |    |                   |  |  |  |  |

| Oper  | ation:                       | ((FSR2) + z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $((FSR2) + z_s) \rightarrow ((FSR2) + z_d)$ |     |    |                   |  |  |  |  |

| Statu | s Affected:                  | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | None                                        |     |    |                   |  |  |  |  |

| Enco  | 0                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                             |     |    |                   |  |  |  |  |

|       | ord (source)<br>vord (dest.) | 1110<br>1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1011                                        | 1zz | -  | ZZZZS             |  |  |  |  |

|       | ription                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | XXXX                                        | XZZ |    | zzzzd             |  |  |  |  |

|       |                              | The contents of the source register are<br>moved to the destination register. The<br>addresses of the source and destination<br>registers are determined by adding the<br>7-bit literal offsets ' $z_s$ ' or ' $z_d$ ',<br>respectively, to the value of FSR2. Both<br>registers can be located anywhere in<br>the 4096-byte data memory space<br>(000h to FFFh).<br>The MOVSS instruction cannot use the<br>PCL, TOSU, TOSH or TOSL as the<br>destination register.<br>If the resultant source address points to<br>an indirect addressing register, the<br>value returned will be 00h. If the<br>resultant destination address points to<br>an indirect addressing register, the<br>instruction will execute as a NOP. |                                             |     |    |                   |  |  |  |  |

| Word  | ls:                          | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                             |     |    |                   |  |  |  |  |

| Cycle | es:                          | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2                                           |     |    |                   |  |  |  |  |

| QC    | ycle Activity:               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                             |     |    |                   |  |  |  |  |

|       | Q1                           | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Q3                                          |     |    | Q4                |  |  |  |  |

|       | Decode                       | Determine source addr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Determ<br>source a                          | -   |    | Read              |  |  |  |  |

|       | Decode                       | Determine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Determ                                      | ine |    | urce reg<br>Write |  |  |  |  |

|       |                              | dest addr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | dest ad                                     | ddr | to | dest reg          |  |  |  |  |

| Example:                               | MOVSS   | [05h], | [06h] |

|----------------------------------------|---------|--------|-------|

| Before Instruction<br>FSR2<br>Contents | on<br>= | 80h    |       |

| of 85h<br>Contents                     | =       | 33h    |       |

| of 86h                                 | =       | 11h    |       |

| After Instruction<br>FSR2<br>Contents  | =       | 80h    |       |

| of 85h<br>Contents                     | =       | 33h    |       |

| of 86h                                 | =       | 33h    |       |

| PUSHL            | Store Liter                          | al at FSR                                | 2, Decr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ement FSR2              |

|------------------|--------------------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| Syntax:          | PUSHL k                              |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                         |

| Operands:        | $0 \leq k \leq 255$                  |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                         |

| Operation:       | $k \rightarrow (FSR2)$<br>FSR2 – 1 – |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                         |

| Status Affected: | None                                 |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                         |

| Encoding:        | 1111                                 | 1010                                     | kkkk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | kkkk                    |

| Description:     | is decreme                           | dress spec<br>nted by 1 a<br>tion allows | after the output of the output | FSR2. FSR2              |

| Words:           | 1                                    |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                         |

| Cycles:          | 1                                    |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                         |