Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| - · ·                      |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Details                    |                                                                            |

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f25k83-i-sp |

# 4.3 Register Definitions: Stack Pointer

#### REGISTER 4-1: TOSU: TOP-OF-STACK UPPER BYTE

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|------------|-------|-------|

| _     | _   | _   |       |       | TOS<20:16> |       |       |

| bit 7 |     |     |       |       |            |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented C = Clearable only bit <math>-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-5 **Unimplemented:** Read as '0'

bit 4-0 TOS<20:16>: Top-of-Stack Location bits

# REGISTER 4-2: TOSH: TOP-OF-STACK HIGH BYTE

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

|       |       |       | TOS<  | 15:8> |       |       |       |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented C = Clearable only bit-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-0 TOS<15:8>: Top-of-Stack Location bits

#### REGISTER 4-3: TOSL: TOP-OF-STACK LOW BYTE

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

|       |       |       | TOS<  | <7:0> |       |       |       |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented C = Clearable only bit -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-0 **TOS<7:0>:** Top-of-Stack Location bits

# REGISTER 5-3: CONFIGURATION WORD 2L (30 0002h)

| R/W-1 | R/W-1  | R/W-1   | R/W-1   | R/W-1  | R/W-1 | R/W-1  | R/W-1 |

|-------|--------|---------|---------|--------|-------|--------|-------|

| BOREI | N<1:0> | LPBOREN | IVT1WAY | MVECEN | PWRT  | S<1:0> | MCLRE |

| bit 7 |        |         |         |        |       |        | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '1'

-n = Value for blank device '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-6 BOREN<1:0>: Brown-out Reset Enable bits

When enabled, Brown-out Reset Voltage (VBOR) is set by the BORV bit.

11 = Brown-out Reset is enabled, SBOREN bit is ignored

10 = Brown-out Reset is enabled while running, disabled in Sleep; SBOREN is ignored

01 = Brown-out Reset is enabled according to SBOREN

00 = Brown-out Reset is disabled

bit 5 LPBOREN: Low-Power BOR Enable bit

1 = Low-Power BOR is disabled0 = Low-Power BOR is enabled

bit 4 IVT1WAY: IVTLOCK bit One-Way Set Enable bit

1 = IVTLOCKED bit can be cleared and set only once; IVT registers remain locked after one clear/set

cycle

0 = IVTLOCK ED bit can be set and cleared repeatedly (subject to the unlock sequence)

bit 3 MVECEN: Multi-vector Enable bit

1 = Multi-vector enabled; Vector table used for interrupts

0 = Legacy interrupt behavior

bit 2-1 **PWRTS<1:0>:** Power-up Timer Selection bits

11 = PWRT is disabled

10 = PWRT set at 64 ms

01 = PWRT set at 16 ms

00 = PWRT set at 1 ms

bit 0 MCLRE: Master Clear (MCLR) Enable bit

If LVP = 1:

RE3 pin function is MCLR

If LVP = 0:

$1 = \overline{MCLR}$  pin is  $\overline{MCLR}$

0 = MCLR pin function is a port defined function

# 6.1 Power-on Reset (POR)

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

# 6.2 Brown-out Reset (BOR)

The BOR circuit holds the device in Reset when VDD reaches a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Words. The four operating modes are:

- · BOR is always on

- · BOR is off when in Sleep

- · BOR is controlled by software

- · BOR is always off

Refer to Table 6-1 for more information.

The Brown-out Reset voltage level is selectable by configuring the BORV<1:0> bits in Configuration Words.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below VBOR for a duration greater than parameter TBORDC, the device will reset. See Table 45-11 for more information.

#### 6.2.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Words are programmed to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

#### 6.2.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Words are programmed to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is not active during Sleep. The device wake-up will be delayed until the BOR is ready.

#### 6.2.3 BOR CONTROLLED BY SOFTWARE

When the BOREN bits of Configuration Words are programmed to '01', the BOR is controlled by the SBOREN bit of the BORCON register. The device start-up is not delayed by the BOR ready condition or the VDD level.

BOR protection begins as soon as the BOR circuit is ready. The status of the BOR circuit is reflected in the BORRDY bit of the BORCON register.

BOR protection is unchanged by Sleep.

#### 6.2.4 BOR AND BULK ERASE

BOR is forced ON during PFM Bulk Erase operations to make sure that a safe erase voltage is maintained for a successful erase cycle.

During Bulk Erase, the BOR is enabled at 2.45V for F and LF devices, even if it is configured to some other value. If VDD falls, the erase cycle will be aborted, but the device will not be reset.

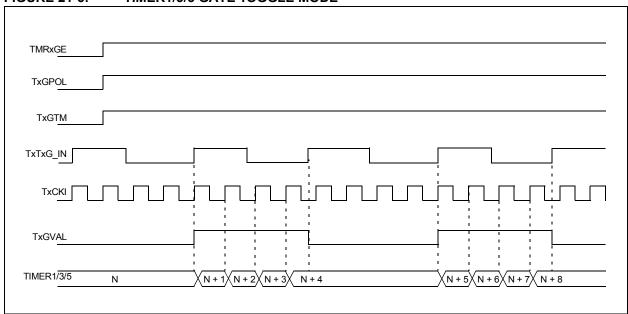

FIGURE 21-5: TIMER1/3/5 GATE TOGGLE MODE

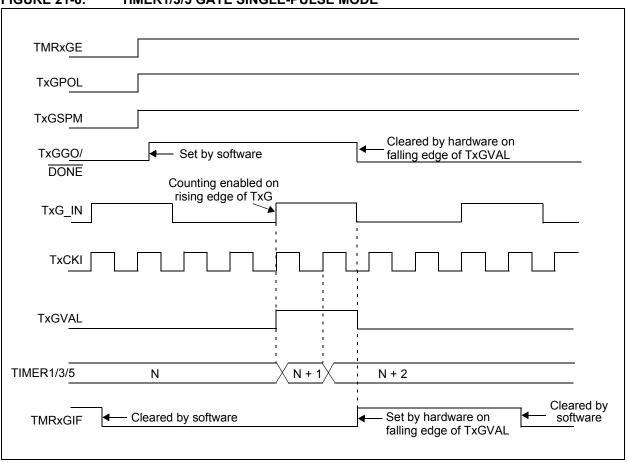

FIGURE 21-6: TIMER1/3/5 GATE SINGLE-PULSE MODE

# REGISTER 21-5: TMRxL: TIMERx LOW BYTE REGISTER

| R/W-x/x |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | TMRxI   | L<7:0>  |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7-0 TMRxL<7:0>:Timerx Low Byte bits

# REGISTER 21-6: TMRxH: TIMERx HIGH BYTE REGISTER

| R/W-x/x    | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x |

|------------|---------|---------|---------|---------|---------|---------|---------|

| TMRxH<7:0> |         |         |         |         |         |         |         |

| bit 7      |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 TMRxH<7:0>:Timerx High Byte bits

#### TABLE 23-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1         | 1         |

| T2PR Value                | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

# TABLE 23-3: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1          | 1         |

| T2PR Value                | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

# 23.4.7 OPERATION IN SLEEP MODE

In Sleep mode, the T2TMR register will not increment and the state of the module will not change. If the CCPx pin is driving a value, it will continue to drive that value. When the device wakes up, T2TMR will continue from its previous state.

# 23.4.8 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See **Section 7.0 "Oscillator Module (with Fail-Safe Clock Monitor)"** for additional details.

# 23.4.9 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

# 26.0 COMPLEMENTARY WAVEFORM GENERATOR (CWG) MODULE

The Complementary Waveform Generator (CWG) produces half-bridge, full-bridge, and steering of PWM waveforms. It is backwards compatible with previous CCP functions. The PIC18(L)F25/26K83 family has three instances of the CWG module.

Each of the CWG modules has the following features:

- · Six operating modes:

- Synchronous Steering mode

- Asynchronous Steering mode

- Full-Bridge mode, Forward

- Full-Bridge mode, Reverse

- Half-Bridge mode

- Push-Pull mode

- · Output polarity control

- · Output steering

- Independent 6-bit rising and falling event deadband timers

- Clocked dead band

- Independent rising and falling dead-band enables

- · Auto-shutdown control with:

- Selectable shutdown sources

- Auto-restart option

- Auto-shutdown pin override control

# 26.1 Fundamental Operation

The CWG generates two output waveforms from the selected input source.

The off-to-on transition of each output can be delayed from the on-to-off transition of the other output, thereby, creating a time delay immediately where neither output is driven. This is referred to as dead time and is covered in **Section 26.6 "Dead-Band Control"**.

It may be necessary to guard against the possibility of circuit faults or a feedback event arriving too late or not at all. In this case, the active drive must be terminated before the Fault condition causes damage. This is referred to as auto-shutdown and is covered in **Section 26.10** "Auto-Shutdown".

#### 26.2 Operating Modes

The CWG module can operate in six different modes, as specified by the MODE<2:0> bits of the CWGxCON0 register:

- · Half-Bridge mode

- · Push-Pull mode

- · Asynchronous Steering mode

- · Synchronous Steering mode

- · Full-Bridge mode, Forward

- · Full-Bridge mode, Reverse

All modes accept a single pulse data input, and provide up to four outputs as described in the following sections.

All modes include auto-shutdown control as described in Section 26.10 "Auto-Shutdown".

Note: Except as noted for Full-bridge mode (Section 26.2.3 "Full-Bridge Modes"), mode changes should only be performed while EN = 0 (Register 26-1).

#### 26.2.1 HALF-BRIDGE MODE

In Half-Bridge mode, two output signals are generated as true and inverted versions of the input as illustrated in Figure 26-2. A non-overlap (dead-band) time is inserted between the two outputs as described in **Section 26.6 "Dead-Band Control"**. The output steering feature cannot be used in this mode. A basic block diagram of this mode is shown in Figure 26-1.

The unused outputs CWGxC and CWGxD drive similar signals as CWGxA and CWGxB, with polarity independently controlled by the POLC and POLD bits of the CWGxCON1 register, respectively.

# 26.14 Register Definitions: CWG Control

Long bit name prefixes for the CWG peripheral is shown below. Refer to **Section 1.3.2.2 "Long Bit Names"** for more information.

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| CWG1       | CWG1            |

| CWG2       | CWG2            |

| CWG3       | CWG3            |

# REGISTER 26-1: CWGxCON0: CWG CONTROL REGISTER 0

| R/W-0/0 | R/W/HC-0/0        | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0   | R/W-0/0 |

|---------|-------------------|-----|-----|-----|---------|-----------|---------|

| EN      | LD <sup>(1)</sup> | _   | _   | _   |         | MODE<2:0> |         |

| bit 7   |                   |     |     |     |         |           | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HC = Bit is cleared by hardware                       |

bit 7 EN: CWGx Enable bit

1 = Module is enabled0 = Module is disabled

bit 6 LD: CWGx Load Buffers bit<sup>(1)</sup>

1 = Dead-band count buffers to be loaded on CWG data rising edge, following first falling edge after

this bit is set

0 = Buffers remain unchanged

bit 5-3 **Unimplemented**: Read as '0' bit 2-0 **MODE<2:0>**: CWGx Mode bits

111 = Reserved 110 = Reserved

101 = CWG outputs operate in Push-Pull mode

100 = CWG outputs operate in Half-Bridge mode

011 = CWG outputs operate in Reverse Full-Bridge mode

010 = CWG outputs operate in Forward Full-Bridge mode

001 = CWG outputs operate in Synchronous Steering mode

000 = CWG outputs operate in Asynchronous Steering mode

Note 1: This bit can only be set after EN = 1; it cannot be set in the same cycle when EN is set.

# REGISTER 30-2: MD1CON1: MODULATION CONTROL REGISTER 1

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|-----|-----|---------|---------|

| _     | _   | CHPOL   | CHSYNC  | _   | _   | CLPOL   | CLSYNC  |

| bit 7 |     |         |         | •   |     |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 **Unimplemented:** Read as '0'

bit 5 CHPOL: Modulator High Carrier Polarity Select bit

1 = Selected high carrier signal is inverted0 = Selected high carrier signal is not inverted

bit 4 CHSYNC: Modulator High Carrier Synchronization Enable bit

1 = Modulator waits for a falling edge on the high time carrier signal before allowing a switch to the low time carrier

0 = Modulator output is not synchronized to the high time carrier signal<sup>(1)</sup>

bit 3-2 **Unimplemented:** Read as '0'

bit 1 CLPOL: Modulator Low Carrier Polarity Select bit

1 = Selected low carrier signal is inverted0 = Selected low carrier signal is not inverted

bit 0 CLSYNC: Modulator Low Carrier Synchronization Enable bit

1 = Modulator waits for a falling edge on the low time carrier signal before allowing a switch to the high time carrier

0 = Modulator output is not synchronized to the low time carrier signal (1)

Note 1: Narrowed carrier pulse widths or spurs may occur in the signal stream if the carrier is not synchronized.

#### REGISTER 31-3: UxCON2: UART CONTROL REGISTER 2

| R/W-0/0 | R/W-0/0 | R/W-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0  | R/W-0/0 |

|---------|---------|----------|---------|---------|---------|----------|---------|

| RUNOVF  | RXPOL   | STP<1:0> |         | C0EN    | TXPOL   | FLO<1:0> |         |

| bit 7   |         |          |         |         |         |          | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7 RUNOVF: Run During Overflow Control bit

1 = RX input shifter continues to synchronize with Start bits after overflow condition

0 = RX input shifter stops all activity on receiver overflow condition

bit 6 RXPOL: Receive Polarity Control bit

1 = Invert RX polarity, Idle state is low

0 = RX polarity is not inverted, Idle state is high

bit 5-4 STP<1:0>: Stop Bit Mode Control bits<sup>(1)</sup>

11 = Transmit 2 Stop bits, receiver verifies first Stop bit

10 = Transmit 2 Stop bits, receiver verifies first and second Stop bits

01 = Transmit 1.5 Stop bits, receiver verifies first Stop bit

00 = Transmit 1 Stop bit, receiver verifies first Stop bit

bit 3 COEN: Checksum Mode Select bit

LIN mode:

1 = Checksum Mode 1, enhanced LIN checksum includes PID in sum

0 = Checksum Mode 0, legacy LIN checksum does not include PID in sum

Other modes:

1 = Add all TX and RX characters

0 = Checksums disabled

bit 2 **TXPOL:** Transmit Polarity Control bit

1 = Output data is inverted, TX output is low in Idle state

0 = Output data is not inverted, TX output is high in Idle state

bit 1-0 FLO<1:0>: Handshake Flow Control bits

11 = Reserved

$10 = \overline{RTS}/\overline{CTS}$  and TXDE Hardware flow control

01 = XON/XOFF Software flow control

00 = Flow control is off

**Note 1:** All modes transmit selected number of Stop bits. Only DMX and DALI receivers verify selected number of Stop bits and all others verify only the first Stop bit.

#### 32.6 Slave Mode

# 32.6.1 SLAVE MODE TRANSMIT OPTIONS

The SDO output of the SPI module in Slave mode is controlled by the TXR bit of SPIxCON2, the TRIS bit associated with the SDO pin, the Slave Select input, and the current state of the TXFIFO. This control is summarized in Table 32-2. In this table, TRISxn refers to the bit in the TRIS register corresponding to the pin that SDO has been assigned with PPS, TXR is the Transmit Data Required Control bit of SPIxCON2, SS is the state of the Slave Select input, and TXBE is the TXFIFO Buffer Empty bit of SPIxSTATUS.

#### 32.6.1.1 SDO Drive/Tri-state

The TRIS bit associated with the SDO pin controls whether the SDO pin will tri-state. When this TRIS bit is cleared, the pin will always be driving to a level, even when the SPI module is inactive. When the SPI module is inactive (either due to the master not clocking the SCK line or the SS being false), the SDO pin will be driven to the value of the LAT bit associated with the SDO pin. When the SPI module is active, its output is determined by both TXR and whether there is data in the TXFIFO.

When the TRIS bit associated with the SDO pin is set, the pin will only have an output level driven to it when TXR = 1 and the Slave Select input is true. In all other cases, the pin will be tri-stated.

#### 32.6.1.2 SDO Output Data

The TXR bit controls the nature of the data that is transmitted in Slave mode. When TXR is set, transmitted data is taken from the TXFIFO. If the FIFO is empty, the most recently received data will be transmitted and the TXUIF flag will be set to indicate that a transmit FIFO underflow has occurred.

When TXR is cleared, the data will be taken from the TXFIFO, and the TXFIFO occupancy will not decrease. If the TXFIFO is empty, the most recently received data will be transmitted, and the TXUIF bit will not be set. However, if the TRIS bit associated with the SDO pin is set, clearing the TXR bit will cause the SPI module to not output any data to the SDO pin.

TABLE 32-2: SLAVE MODE TRANSMIT

| TRISxn <sup>(1)</sup> TXR |   | KR SS TX |                                                                                                            | SDO State                                                                                                           |

|---------------------------|---|----------|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| 0 0                       |   | FALSE    | 0                                                                                                          | Drives state determined by LATxn(2)                                                                                 |

| 0                         | 0 | FALSE    | 1                                                                                                          | Drives state determined by LATxn(2)                                                                                 |

| 0                         | 0 | TRUE     | 0                                                                                                          | Outputs the oldest byte in the TXFIFO Does not remove data from the TXFIFO                                          |

| 0                         | 0 | TRUE     | 1                                                                                                          | Outputs the most recently received byte                                                                             |

| 0                         | 1 | FALSE    | 0                                                                                                          | Drives state determined by LATxn(2)                                                                                 |

| 0                         | 1 | FALSE    | 1                                                                                                          | Drives state determined by LATxn(2)                                                                                 |

| 0                         | 1 | TRUE     | Outputs the oldest byte in the TXFIFO Removes transmitted byte from the TXF Decrements occupancy of TXFIFO |                                                                                                                     |

| 0                         | 1 | TRUE     | 1                                                                                                          | Outputs the most recently received byte<br>Sets the TXUIF bit of SPIxINTF                                           |

| 1                         | 0 | FALSE    | 0                                                                                                          | Tri-stated                                                                                                          |

| 1                         | 0 | FALSE    | 1                                                                                                          | Tri-stated                                                                                                          |

| 1                         | 0 | TRUE     | 0                                                                                                          | Tri-stated                                                                                                          |

| 1                         | 0 | TRUE     | 1                                                                                                          | Tri-stated                                                                                                          |

| 1                         | 1 | FALSE    | 0                                                                                                          | Tri-stated                                                                                                          |

| 1                         | 1 | FALSE    | 1                                                                                                          | Tri-stated                                                                                                          |

| 1                         | 1 | TRUE     | 0                                                                                                          | Outputs the oldest byte in the TXFIFO<br>Removes transmitted byte from the TXFIFO<br>Decrements occupancy of TXFIFO |

| 1                         | 1 | TRUE     | 1                                                                                                          | Outputs the most recently received byte<br>Sets the TXUIF bit of SPIxINTF                                           |

Note 1: TRISxn is the bit in the TRISx register corresponding to the pin that SDO has been assigned with PPS.

2: LATxn is the bit in the LATx register corresponding to the pin that SDO has been assigned with PPS.

#### REGISTER 32-6: SPIXBAUD: SPI BAUD RATE REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| BAUD7   | BAUD6   | BAUD5   | BAUD4   | BAUD3   | BAUD2   | BAUD1   | BAUD0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

R = Readable bit W = Writable bit U = U

U = Unimplemented bit, read as '0'

bit 7-0 BAUD<7:0>: Baud Clock Prescaler Select bits

SCK high or low time: TSC=SPI Clock Period\*(BAUD+1)

SCK toggle frequency: FSCK=FBAUD= SPI Clock Frequency/(2\*(BAUD+1))

Note: This register should not be written while the SPI is enabled (EN bit of SPIxCON0 = 1)

#### REGISTER 32-7: SPIxCON0: SPI CONFIGURATION REGISTER 0

| R/W-0/0     | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |

|-------------|-----|-----|-----|-----|---------|---------|---------|--|--|

| EN          | _   | _   | _   | _   | LSBF    | MST     | BMODE   |  |  |

| bit 7 bit 0 |     |     |     |     |         |         |         |  |  |

Legend:

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

bit 7 EN: SPI Module Enable Control bit

1 = SPI is enabled

0 = SPI is disabled.

bit 6-3 **Unimplemented**: Read as '0'

bit 2 LSBF: LSb-First Data Exchange bit

1 = Data is exchanged LSb first

0 = Data is exchanged MSb first (traditional SPI operation)

bit 1 MST: SPI Operating Mode Master Select bit

1 = SPI module operates as the bus master

0 = SPI module operates as a bus slave

bit 0 BMODE: Bit-Length Mode Select bit

1 = SPIxTWIDTH setting applies to every byte: total bits sent is SPIxTWIDTH\*SPIxTCNT, end-of-packet occurs when SPIxTCNT = 0

0 = SPIxTWIDTH setting applies only to the last byte exchanged; total bits sent is SPIxTWIDTH + (SPIxTCNT\*8)

Note: This register should only be written when the EN bit is cleared, or to clear the EN bit.

# REGISTER 33-10: I2CxPIR: I2CxIF INTERRUPT FLAG REGISTER

| R/W/HS-0    | R/W/HS-0 | U-0 | R/W/HS-0 | R/W/HS-0 | R/W/HS-0 | R/W/HS-0 | R/W/HS-0 |  |  |

|-------------|----------|-----|----------|----------|----------|----------|----------|--|--|

| CNTIF       | ACKTIF   | _   | WRIF     | ADRIF    | PCIF     | RSCIF    | SCIF     |  |  |

| bit 7 bit 0 |          |     |          |          |          |          |          |  |  |

| Legend:              |                      |                                                       |  |  |  |  |

|----------------------|----------------------|-------------------------------------------------------|--|--|--|--|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |  |  |  |  |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |  |  |  |  |

| '1' = Bit is set     | '0' = Bit is cleared | HS = Hardware set HC = Hardware clear                 |  |  |  |  |

| bit 7 | CNTIF: Byte Count Interrupt Flag bit  1 = When I2CCNT = 0, set by the 9th falling edge of SCL.  0 = I2CCNT condition has not occurred.                                                                                           |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | <b>ACKTIF:</b> Acknowledge Status Time Interrupt Flag bit <sup>(2)</sup> (MODE<2:0> = $0xx$ OR $11x$ ) $1$ = Set by the 9th falling edge of SCL for any byte when addressed as a slave $0$ = Acknowledge condition not detected. |

| bit 5 | Unimplemented: Read as '0'                                                                                                                                                                                                       |

| bit 4 | <ul> <li>WRIF: Data Write Interrupt Flag bit (MODE&lt;2:0&gt; = 0xx OR 11x)</li> <li>1 = Set the 8th falling edge of SCL for a received data byte.</li> <li>0 = Data Write condition not detected</li> </ul>                     |

| bit 3 | <b>ADRIF:</b> Address Interrupt Flag bit (MODE<2:0> = 0xx OR 11x)<br>1 = Set the 8th falling edge of SCL for a matching received (high/low) address byte 0 = Address condition not detected                                      |

| bit 2 | PCIF: Stop Condition Interrupt Flag  1 = Set on detection of Stop condition  0 = No Stop condition detected                                                                                                                      |

| bit 1 | RSCIF: Restart Condition Interrupt Flag  1 = Set on detection of Restart condition  0 = No Restart condition detected                                                                                                            |

| bit 0 | SCIF: Start Condition Interrupt Flag  1 = Set on detection of Start condition  0 = No Start condition detected                                                                                                                   |

- **Note 1:** Enabled interrupt flags are OR'd to produce the PIRx<I2CxIF> bit.

- **2:** ACKTIF is not set by a matching, 10-bit, high address byte with the R/W bit clear. It is only set after the matching low address byte is shifted in.

#### REGISTER 34-4: COMSTAT: COMMUNICATION STATUS REGISTER

| Mode 0 | R/C-0     | R/C-0    | R-0  | R-0  | R-0  | R-0    | R-0    | R-0   |

|--------|-----------|----------|------|------|------|--------|--------|-------|

| wode 0 | RXB00VFL  | RXB10VFL | TXBO | TXBP | RXBP | TXWARN | RXWARN | EWARN |

|        |           |          |      |      |      |        |        |       |

| Mode 1 | R/C-0     | R/C-0    | R-0  | R-0  | R-0  | R-0    | R-0    | R-0   |

| wode i | _         | RXBnOVFL | TXB0 | TXBP | RXBP | TXWARN | RXWARN | EWARN |

|        |           |          |      |      |      |        |        |       |

| Mada 2 | R/C-0     | R/C-0    | R-0  | R-0  | R-0  | R-0    | R-0    | R-0   |

| Mode 2 | FIFOEMPTY | RXBnOVFL | TXBO | TXBP | RXBP | TXWARN | RXWARN | EWARN |

|        | bit 7     |          |      | •    |      |        |        | bit 0 |

|        |           |          |      |      |      |        |        |       |

| Legend:           | C = Clearable bit |                          |                    |

|-------------------|-------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, r | read as '0'        |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared     | x = Bit is unknown |

bit 7 Mode 0:

RXB0OVFL: Receive Buffer 0 Overflow bit

1 = Receive Buffer 0 has overflowed

0 = Receive Buffer 0 has not overflowed

Mode 1:

Unimplemented: Read as '0'

Mode 2:

FIFOEMPTY: FIFO Not Empty bit

1 = Receive FIFO is not empty

0 = Receive FIFO is empty

bit 6 Mode 0:

RXB10VFL: Receive Buffer 1 Overflow bit

1 = Receive Buffer 1 has overflowed

0 = Receive Buffer 1 has not overflowed

Mode 1, 2:

RXBnOVFL: Receive Buffer n Overflow bit

1 = Receive Buffer n has overflowed

0 = Receive Buffer n has not overflowed

bit 5 TXBO: Transmitter Bus-Off bit

1 = Transmit error counter > 255

$0 = Transmit error counter \le 255$

bit 4 **TXBP:** Transmitter Bus Passive bit

1 = Transmit error counter > 127

0 = Transmit error counter ≤ 127

bit 3 RXBP: Receiver Bus Passive bit

1 = Receive error counter > 127

0 = Receive error counter ≤ 127

bit 2 **TXWARN:** Transmitter Warning bit

1 = Transmit error counter > 95

0 = Transmit error counter ≤ 95

bit 1 **RXWARN:** Receiver Warning bit

1 = 127  $\geq$  Receive error counter > 95

0 = Receive error counter ≤ 95

bit 0 **EWARN:** Error Warning bit

This bit is a flag of the RXWARN and TXWARN bits.

1 = The RXWARN or the TXWARN bits are set

0 = Neither the RXWARN or the TXWARN bits are set

# REGISTER 34-49: MSEL1: MASK SELECT REGISTER 1(1)

| R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-1  | R/W-0  | R/W-1  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| FIL7_1 | FIL7_0 | FIL6_1 | FIL6_0 | FIL5_1 | FIL5_0 | FIL4_1 | FIL4_0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-6 FIL7\_<1:0>: Filter 7 Select bits 1 and 0

11 = No mask

10 = Filter 15

01 = Acceptance Mask 1 00 = Acceptance Mask 0

bit 5-4 FIL6\_<1:0>: Filter 6 Select bits 1 and 0

11 = No mask

10 = Filter 15

01 = Acceptance Mask 1

00 = Acceptance Mask 0

bit 3-2 FIL5\_<1:0>: Filter 5 Select bits 1 and 0

11 = No mask

10 = Filter 15

01 = Acceptance Mask 1

00 = Acceptance Mask 0

bit 1-0 FIL4\_<1:0>: Filter 4 Select bits 1 and 0

11 = No mask

10 = Filter 15

01 = Acceptance Mask 1

00 = Acceptance Mask 0

Note 1: This register is available in Mode 1 and 2 only.

#### 37.6.1 DIGITAL FILTER/AVERAGE

The digital filter/average module consists of an accumulator with data feedback options, and control logic to determine when threshold tests need to be applied. The accumulator is a 16-bit wide register which can be accessed through the ADACCH:ADACCL register pair.

Upon each trigger event (the GO bit set or external event trigger), the ADC conversion result is added to the accumulator. If the accumulated result exceeds  $2^{(accumulator\_width)}-1 = 18 = 262143$ , the overflow bit ADAOV in the ADSTAT register is set.

The number of samples to be accumulated is determined by the RPT (A/D Repeat Setting) register. Each time a sample is added to the accumulator, the ADCNT register is incremented. Once RPT samples are accumulated (CNT = RPT), an Accumulator Clear command can be issued by the software by setting the ADACLR bit in the ADCON2 register. Setting the ADACLR bit will also clear the ADAOV (Accumulator overflow) bit in the ADSTAT register, as well as the

ADCNT register. The ADACLR bit is cleared by the hardware when accumulator clearing action is complete.

**Note:** When ADC is operating from FRC, five FRC clock cycles are required to execute the ACC clearing operation.

The ADCRS <2:0> bits in the ADCON2 register control the data shift on the accumulator result, which effectively divides the value in accumulator (ADACCU:ADACCH:ADACCL) register pair. For the Accumulate mode of the digital filter, the shift provides a simple scaling operation. For the Average/Burst Average mode, the shift bits are used to determine the number of logical right shifts to be performed on the accumulated result. For the Low-pass Filter mode, the shift is an integral part of the filter, and determines the cut-off frequency of the filter. Table 37-3 shows the -3 dB cut-off frequency in  $\omega T$  (radians) and the highest signal attenuation obtained by this filter at nyquist frequency ( $\omega T = \pi$ ).

TABLE 37-3: LOW-PASS FILTER -3 dB CUT-OFF FREQUENCY

| ADCRS | ωT (radians) @ -3 dB Frequency | dB @ F <sub>nyquist</sub> =1/(2T) |

|-------|--------------------------------|-----------------------------------|

| 1     | 0.72                           | -9.5                              |

| 2     | 0.284                          | -16.9                             |

| 3     | 0.134                          | -23.5                             |

| 4     | 0.065                          | -29.8                             |

| 5     | 0.032                          | -36.0                             |

| 6     | 0.016                          | -42.0                             |

| 7     | 0.0078                         | -48.1                             |

# 37.6.2 BASIC MODE

Basic mode (ADMD = 000) disables all additional computation features. In this mode, no accumulation occurs but threshold error comparison is performed. Double sampling, Continuous mode, and all CVD features are still available, but no features involving the digital filter/average features are used.

#### 37.6.3 ACCUMULATE MODE

In Accumulate mode (ADMD = 001), after every conversion, the ADC result is added to the ADACC register. The ADACC register is right-shifted by the value of the ADCRS bits in the ADCON2 register. This right-shifted value is copied in to the ADFLT register. The Formatting mode does not affect the right-justification of the ACC value. Upon each sample, CNT is also incremented, incrementing the number of samples accumulated. After each sample and accumulation, the ACC value has a threshold comparison performed on it (see Section 37.6.7 "Threshold Comparison") and the ADTIF interrupt may trigger.

# 37.6.4 AVERAGE MODE

In Average mode (ADMD = 010), the ADACC registers accumulate with each ADC sample, much as in Accumulate mode, and the ADCNT register increments with each sample. The ADFLT register is also updated with the right-shifted value of the ADACC register. The value of the ADCRS bits governs the number of right shifts. However, in Average mode, the threshold comparison is performed upon CNT being greater than or equal to a user-defined RPT value. In this mode when RPT = 2^CNT, then the final accumulated value will be divided by number of samples, allowing for a threshold comparison operation on the average of all gathered samples.

#### REGISTER 37-6: ADCLK: ADC CLOCK SELECTION REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| _     | _   |         |         | CS<     | 5:0>    |         |         |

| bit 7 |     |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-6 **Unimplemented**: Read as '0'

bit 5-0 CS<5:0>: ADC Conversion Clock Select bits

111111 = Fosc/128 111110 = Fosc/126 111101 = Fosc/124

•

•

000000 = Fosc/2

#### REGISTER 37-7: ADREF: ADC REFERENCE SELECTION REGISTER

| U-0   | U-0 | U-0 | R/W-0/0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|---------|-----|-----|---------|---------|

| _     | _   | _   | NREF    | _   | _   | PREF    | <1:0>   |

| bit 7 |     |     |         |     |     |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-5 **Unimplemented**: Read as '0'

bit 4 NREF: ADC Negative Voltage Reference Selection bit

1 = VREF- is connected to external VREF-

0 = VREF- is connected to VSS

bit 3-2 **Unimplemented**: Read as '0'

bit 1-0 PREF: ADC Positive Voltage Reference Selection bits

11 = VREF+ is connected to internal Fixed Voltage Reference (FVR) module

10 = VREF+ is connected to external VREF+

01 = Reserved

00 = VREF+ is connected to VDD

# REGISTER 37-9: ADPREL: ADC PRECHARGE TIME CONTROL REGISTER (LOW BYTE)

| R/W-0/0   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-----------|---------|---------|---------|---------|---------|---------|---------|

|           |         |         | PRE<    | <7:0>   |         |         |         |

| bit 7 bit |         |         |         |         |         | bit 0   |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **PRE<7:0>:** Precharge Time Select bits See Table 37-4.

# REGISTER 37-10: ADPREH: ADC PRECHARGE TIME CONTROL REGISTER (HIGH BYTE)

| U-0   | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0   | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|---------|---------|-----------|---------|---------|

| _     | _   | _   |         |         | PRE<12:8> |         |         |

| bit 7 |     |     |         |         |           |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-5 **Unimplemented**: Read as '0'

bit 4-0 PRE<12:8>: Precharge Time Select bits

See Table 37-4.

Note: If PRE is not equal to '0', then ADACQ = b'00000000 means Acquisition time is 256 clocks of the selected

ADC clock.

# TABLE 37-4: PRECHARGE TIME

| ADPRE            | Precharge time                            |

|------------------|-------------------------------------------|

| 1 1111 1111 1111 | 8191 clocks of the selected ADC clock     |

| 1 1111 1111 1110 | 8190 clocks of the selected ADC clock     |

| 1 1111 1111 1101 | 8189 clocks of the selected ADC clock     |

|                  |                                           |

| 0 0000 0000 0010 | 2 clocks of the selected ADC clock        |

| 0 0000 0000 0001 | 1 clock of the selected ADC clock         |

| 0 0000 0000 0000 | Not included in the data conversion cycle |

#### 39.9 CWG1 Auto-Shutdown Source

The output of the comparator module can be used as an auto-shutdown source for the CWG1 module. When the output of the comparator is active and the corresponding WGASxE is enabled, the CWG operation will be suspended immediately (see Section 26.10.1.2 "External Input Source").

# 39.10 ADC Auto-Trigger Source

The output of the comparator module can be used to trigger an ADC conversion. When the ADACT register is set to trigger on a comparator output, an ADC conversion will trigger when the Comparator output goes high.

#### 39.11 TMR2/4/6 Reset

The output of the comparator module can be used to reset Timer2. When the TxERS register is appropriately set, the timer will reset when the Comparator output goes high.

# 39.12 Operation in Sleep Mode

The comparator module can operate during Sleep. The comparator clock source is based on the Timer1 clock source. If the Timer1 clock source is either the system clock (Fosc) or the instruction clock (Fosc/4), Timer1 will not operate during Sleep, and synchronized comparator outputs will not operate.

A comparator interrupt will wake the device from Sleep. The CxIE bits of the respective PIE register must be set to enable comparator interrupts.