Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                  |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f25k83t-i-ml |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 9.6 Returning from Interrupt Service Routine (ISR)

The "Return from Interrupt" instruction (RETFIE) is used to mark the end of an ISR.

When RETFIE 1 instruction is executed, the PC is loaded with the saved PC value from the top of the PC stack. Saved context is also restored with the execution of this instruction. Thus, execution returns to the previous state of operation that existed before the interrupt occurred.

When RETFIE 0 instruction is executed, the saved context is not restored back to the registers.

# 9.7 Interrupt Latency

By assigning each interrupt with a vector address/number (MVECEN = 1), scanning of all interrupts is not necessary to determine the source of the interrupt.

When MVECEN = 1, Vectored interrupt controller requires three clock cycles to vector to the ISR from main routine, thereby removing dependency of interrupt timing on compiled code.

There is a fixed latency of three instruction cycles between the completion of the instruction active when the interrupt occurred and the first instruction of the Interrupt Service Routine. Figure 9-7, Figure 9-8 and Figure 9-9 illustrates the sequence of events when a peripheral interrupt is asserted when the last executed instruction is one-cycle, two-cycle and three-cycle respectively, when MVECEN = 1.

After the Interrupt Flag Status bit is set, the current instruction completes executing. In the first latency cycle, the contents of the PC, STATUS, WREG, BSR, FSR0/1/2, PRODL/H and PCLATH/U registers are context saved and the IVTBASE+ Vector number is calculated. In the second latency cycle, the PC is loaded with the calculated vector table address for the interrupt source and the starting address of the ISR is fetched. In the third latency cycle, the PC is loaded with the ISR address. All the latency cycles are executed as a FNOP instruction.

When MVECEN = 0, Vectored interrupt controller requires two clock cycles to vector to the ISR from main routine. There is a latency of two instruction cycles plus the software latency between the completion of the instruction active when the interrupt occurred and the first instruction of the Interrupt Service Routine.

| EXAMPLE 9-3:                            | SETTING UP VECTORED I                         | NTERRUPTS USING MPASM                                  |

|-----------------------------------------|-----------------------------------------------|--------------------------------------------------------|

| ISR_TMR0: CODE                          | 0x8C0                                         | ; ISR code at 0x08C0 in PFM                            |

| BANKSEL                                 | PIR0                                          | ; Select bank for PIR0                                 |

| BCF                                     | PIR3, TMR0IF                                  | ; Clear TMR0IF                                         |

| BTG                                     | LATC, 0, ACCESS                               | ; Code to execute in ISR                               |

| RETFIE                                  | 1                                             | ; Return from ISR                                      |

| InterruptInit:                          |                                               |                                                        |

| BANKSEL                                 | INTCON0                                       | ; Select bank for INTCON0                              |

| BSF                                     |                                               | ; Enable high priority interrupts                      |

| BSF                                     |                                               | ; Enable low priority interrupts                       |

| BSF                                     |                                               | ; Enable interrupt priority                            |

| BANKSEL                                 | PIEO                                          | ; Select bank for PIE0                                 |

| BSF                                     | PIE3, TMROIE                                  | ; Enable TMR0 interrupt                                |

| BSF                                     | PIE4, TMR1IE                                  | ; Enable TMR1 interrupt                                |

| BCF                                     | IPR3, TMR0IP                                  | ; Make TMR0 interrupt low priority                     |

| RETURN                                  | 1                                             |                                                        |

| VectorTableInit:                        |                                               |                                                        |

|                                         | SE (optional - default is                     | 0x000008)                                              |

| MOVLW                                   | 0x00                                          | ; This is optional                                     |

| MOVWF                                   | IVTBASEU, ACCESS                              | ; If not included, then the                            |

| MOVLW                                   | 0x40                                          | ; hardware default value of                            |

| MOVWF                                   | IVTBASEH, ACCESS                              | ; 0x0008 will be taken.                                |

|                                         | ,                                             | , uxuuus wiii be taken.                                |

| MOVLW                                   | 0x08                                          |                                                        |

| MOVWF                                   | IVTBASEL, ACCESS                              |                                                        |

|                                         |                                               | ector number i.e. 31) = 0x4046                         |

| MOVLW                                   | 0x00                                          | ; Load TBLPTR with the                                 |

| MOVWF                                   | TBLPTRU, ACCESS                               | ; PFM memory location to be                            |

| MOVLW                                   | 0x40                                          | ; written to.                                          |

| MOVWF                                   | TBLPTRH, ACCESS                               |                                                        |

| MOVLW                                   | 0x46                                          |                                                        |

| MOVWF                                   | TBLPTRL, ACCESS                               |                                                        |

| ; Write the                             | contents of TMR0 vector 1                     | ocation                                                |

| ; ISR_TMR0_A                            | ADDRESS >> 2 = 0x08C0 >> 2                    | $2 = 0 \times 0230$                                    |

| MOVLW                                   | 0x30                                          | ; Low byte first                                       |

| MOVWF                                   | TABLAT, ACCESS                                | -                                                      |

| TBLWT*+                                 | ,                                             | ; Write to temp table latch                            |

| 10201                                   |                                               |                                                        |

| MOVLW                                   | 0x02<br>TABLAT, ACCESS                        | ; High byte next                                       |

| MOVWF<br>TBLWT*+                        | IABLAI, ACCESS                                | ; Write to temp table latch                            |

| · Write to I                            | EM now uning NUMCON                           |                                                        |

|                                         | PFM now using NVMCON<br>NVMCON1               | ; Select bank for NVMCON1                              |

| BANKSEL                                 |                                               |                                                        |

| MOVLW                                   | 0x84                                          | ; Setting to write to PFM                              |

| MOVWF                                   | NVMCON1                                       |                                                        |

|                                         | 0x55                                          | ; Required unlock sequence                             |

| MOVLW                                   | NVMCON2                                       |                                                        |

| MOVWF                                   |                                               |                                                        |

|                                         | 0xAA                                          |                                                        |

| MOVWF                                   |                                               |                                                        |

| MOVWF<br>MOVLW                          | 0xAA                                          | ; Start writing to PFM                                 |

| MOVWF<br>MOVLW<br>MOVWF                 | 0xaa<br>nvmcon2                               | ; Start writing to PFM<br>; Wait for write to complete |

| MOVWF<br>MOVLW<br>MOVWF<br>BSF          | 0xAA<br>NVMCON2<br>NVMCON1, WR                |                                                        |

| MOVWF<br>MOVLW<br>MOVWF<br>BSF<br>BTFSC | 0xAA<br>NVMCON2<br>NVMCON1, WR<br>NVMCON1, WR |                                                        |

| C1TXIE |

|--------|

|        |

| bit    |

|        |

|        |

| Resets |

| 100000 |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

|        |

# REGISTER 9-16: PIE3: PERIPHERAL INTERRUPT ENABLE REGISTER 3

Example 12-3 shows the sequence to do a 16 x 16 unsigned multiplication. Equation 12-1 shows the algorithm that is used. The 32-bit result is stored in four registers (RES<3:0>).

#### EQUATION 12-1: 16 x 16 UNSIGNED MULTIPLICATION ALGORITHM

| RES3:RES0 | = |                                          |

|-----------|---|------------------------------------------|

|           | = | $(ARG1H \bullet ARG2H \bullet 2^{16}) +$ |

|           |   | $(ARG1H \bullet ARG2L \bullet 2^8) +$    |

|           |   | $(ARG1L \bullet ARG2H \bullet 2^8) +$    |

|           |   | $(ARG1L \bullet ARG2L)$                  |

|           |   |                                          |

## EXAMPLE 12-3: 16 x 16 UNSIGNED MULTIPLY ROUTINE

|   | MOVF   | ARG1L, W    |                   |

|---|--------|-------------|-------------------|

|   | MULWF  | ARG2L       | ; ARG1L * ARG2L-> |

|   |        |             | ; PRODH:PRODL     |

|   | MOVFF  | PRODH, RES1 | i                 |

|   | MOVFF  | PRODL, RESO | ;                 |

| ; |        |             |                   |

|   |        | ARG1H, W    |                   |

|   | MULWF  | ARG2H       | ; ARG1H * ARG2H-> |

|   |        |             | ; PRODH:PRODL     |

|   |        | PRODH, RES3 | ;                 |

|   | MOVFF  | PRODL, RES2 | ;                 |

| ; |        |             |                   |

|   |        | ARG1L, W    |                   |

|   | MULWF  | ARG2H       | ; ARG1L * ARG2H-> |

|   |        |             | ; PRODH:PRODL     |

|   |        | PRODL, W    | ;                 |

|   |        | RES1, F     | ; Add cross       |

|   |        | PRODH, W    | ; products        |

|   |        | RES2, F     | i                 |

|   | CLRF   |             | i                 |

|   | ADDWFC | RES3, F     | ;                 |

| ; |        |             |                   |

|   |        | ARG1H, W    | ;                 |

|   | MOLWF. | ARG2L       | ; ARG1H * ARG2L-> |

|   | MOUTE  | DDODI W     | ; PRODH:PRODL     |

|   |        | PRODL, W    | <i>i</i>          |

|   |        | RES1, F     | ; Add cross       |

|   |        | PRODH, W    | ; products        |

|   |        | RES2, F     | ,                 |

|   | CLRF   |             | ,                 |

|   | ADDWFC | RES3, F     | ,                 |

Example 12-4 shows the sequence to do a 16 x 16 signed multiply. Equation 12-2 shows the algorithm used. The 32-bit result is stored in four registers (RES<3:0>). To account for the sign bits of the arguments, the MSb for each argument pair is tested and the appropriate subtractions are done.

## EQUATION 12-2: 16 x 16 SIGNED MULTIPLICATION ALGORITHM

| RES3:RES0 = ARG1H:ARG1L • ARG2H:ARG2L                           |

|-----------------------------------------------------------------|

| $= (ARG1H \bullet ARG2H \bullet 2^{16}) +$                      |

| $(ARG1H \bullet ARG2L \bullet 2^8) +$                           |

| $(ARG1L \bullet ARG2H \bullet 2^8) +$                           |

| $(ARG1L \bullet ARG2L) +$                                       |

| $(-1 \bullet ARG2H < 7 > \bullet ARG1H:ARG1L \bullet 2^{16}) +$ |

| $(-1 \bullet ARG1H < 7 > \bullet ARG2H:ARG2L \bullet 2^{16})$   |

|                                                                 |

#### EXAMPLE 12-4: 16 x 16 SIGNED MULTIPLY ROUTINE

| MOVF      | ARG1L, W              |                                        |

|-----------|-----------------------|----------------------------------------|

| MULWF     | ARG2L                 | ; ARG1L * ARG2L ->                     |

|           |                       | ; PRODH:PRODL                          |

| MOVFF     | PRODH, RES1           | ;                                      |

| MOVFF     |                       |                                        |

| ;         |                       |                                        |

| MOVF      | ARG1H, W              |                                        |

|           | ARG2H                 | ; ARG1H * ARG2H ->                     |

|           |                       | ; PRODH:PRODL                          |

| MOVEE     | PRODH, RES3           |                                        |

| MOVFF     |                       |                                        |

| ;         |                       |                                        |

| MOVF      | ARG1L, W              |                                        |

|           | ARG2H                 | ; ARG1L * ARG2H ->                     |

|           |                       | ; PRODH:PRODL                          |

| MOVF      | PRODL, W              | i inodii inodd                         |

| ADDWF     |                       | ; Add cross                            |

| MOVE      | PRODH, W              | ; products                             |

| ADDWF     | C RES2, F             | ;                                      |

| CLRF      | WREG                  | ;                                      |

| ADDWF     | C RES3, F             | i                                      |

| ;         |                       |                                        |

| MOVE      | ARG1H, W              | i                                      |

| MULWF     |                       | ; ARG1H * ARG2L ->                     |

|           |                       | ; PRODH:PRODL                          |

| MOVF      | PRODL, W              | i                                      |

|           | RES1, F               | ; Add cross                            |

| MOVF      |                       | ; products                             |

| ADDWF     | C RES2, F             | ;                                      |

| CLRF      | WREG                  | i                                      |

| ADDWF     | C RES3, F             | ;                                      |

| ;         |                       |                                        |

| BTFSS     | ARG2H, 7<br>SIGN_ARG1 | ; ARG2H:ARG2L neg?                     |

| BRA       | SIGN_ARG1             | ; ARG2H:ARG2L neg?<br>; no, check ARG1 |

| MOVF      | ARG1L, W              | ;                                      |

| SUBWF     | RES2                  | ;                                      |

| MOVF      |                       | ;                                      |

| SUBWF     | 'B RES3               |                                        |

| ;         |                       |                                        |

| SIGN_ARG1 |                       |                                        |

| BTFSS     | ARG1H, 7              | ; ARG1H:ARG1L neg?                     |

| BRA       | CONT_CODE             | ; ARG1H:ARG1L neg?<br>; no, done       |

| MOVF      | ARG2L, W              | ;                                      |

| SUBWF     |                       | ;                                      |

| MOVF      | ARG2H, W              | ;                                      |

| SUBWF     | 'B RES3               |                                        |

| ;         |                       |                                        |

| CONT_CODE |                       |                                        |

| :         |                       |                                        |

| L         |                       |                                        |

| IABLE IO U.        |                                             |  |  |  |  |  |  |

|--------------------|---------------------------------------------|--|--|--|--|--|--|

| Example            | Operation on Table Pointer                  |  |  |  |  |  |  |

| TBLRD*<br>TBLWT*   | TBLPTR is not modified                      |  |  |  |  |  |  |

| TBLRD*+<br>TBLWT*+ | TBLPTR is incremented after the read/write  |  |  |  |  |  |  |

| TBLRD*-<br>TBLWT*- | TBLPTR is decremented after the read/write  |  |  |  |  |  |  |

| TBLRD+*<br>TBLWT+* | TBLPTR is incremented before the read/write |  |  |  |  |  |  |

## TABLE 13-3: TABLE POINTER OPERATIONS WITH TBLRD AND TBLWT INSTRUCTIONS

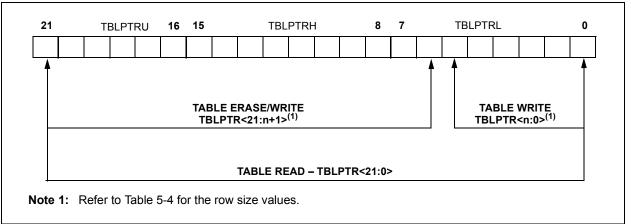

#### **FIGURE 13-3:**

TABLE POINTER BOUNDARIES BASED ON OPERATION

#### 13.3.8 ERASING THE DATA EEPROM MEMORY

\_\_\_\_

Data EEPROM Memory can be erased by writing 0xFF to all locations in the Data EEPROM Memory that needs to be erased.

. . . . . . . . . . . . . . .

| PLE 13-7: | DATA E                                                                                                     | EPROM RE                                                                                                                                                                                | FR                                                                                                                                                                                                                               | ESH ROUTINE                                                                                                                                                                                                        |

|-----------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLRF      | NVMADRL                                                                                                    |                                                                                                                                                                                         | ;                                                                                                                                                                                                                                | Start at address 0                                                                                                                                                                                                 |

| BCF       | NVMCON1,                                                                                                   | CFGS                                                                                                                                                                                    | ;                                                                                                                                                                                                                                | Set for memory                                                                                                                                                                                                     |

| BCF       | NVMCON1,                                                                                                   | EEPGD                                                                                                                                                                                   | ;                                                                                                                                                                                                                                | Set for Data EEPROM                                                                                                                                                                                                |

| BCF       | INTCON0,                                                                                                   | GIE                                                                                                                                                                                     | ;                                                                                                                                                                                                                                | Disable interrupts                                                                                                                                                                                                 |

| BSF       | NVMCON1,                                                                                                   | WREN                                                                                                                                                                                    | ;                                                                                                                                                                                                                                | Enable writes                                                                                                                                                                                                      |

|           |                                                                                                            |                                                                                                                                                                                         | ;                                                                                                                                                                                                                                | Loop to refresh array                                                                                                                                                                                              |

| BSF       | NVMCON1,                                                                                                   | RD                                                                                                                                                                                      | ;                                                                                                                                                                                                                                | Read current address                                                                                                                                                                                               |

| MOVLW     | 55h                                                                                                        |                                                                                                                                                                                         | ;                                                                                                                                                                                                                                |                                                                                                                                                                                                                    |

| MOVWF     | NVMCON2                                                                                                    |                                                                                                                                                                                         | ;                                                                                                                                                                                                                                | Write 55h                                                                                                                                                                                                          |

| MOVLW     | 0AAh                                                                                                       |                                                                                                                                                                                         | ;                                                                                                                                                                                                                                |                                                                                                                                                                                                                    |

| MOVWF     | NVMCOM2                                                                                                    |                                                                                                                                                                                         | ;                                                                                                                                                                                                                                | Write OAAh                                                                                                                                                                                                         |

| BSF       | NVMCON1,                                                                                                   | WR                                                                                                                                                                                      | ;                                                                                                                                                                                                                                | Set WR bit to begin write                                                                                                                                                                                          |

| BTFSC     | NVMCON1,                                                                                                   | WR                                                                                                                                                                                      | ;                                                                                                                                                                                                                                | Wait for write to complete                                                                                                                                                                                         |

| BRA       | \$-2                                                                                                       |                                                                                                                                                                                         |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                    |

| INCFSZ    | NVMADRL,                                                                                                   | F                                                                                                                                                                                       | ;                                                                                                                                                                                                                                | Increment address                                                                                                                                                                                                  |

| BRA       | LOOP                                                                                                       |                                                                                                                                                                                         | ;                                                                                                                                                                                                                                | Not zero, do it again                                                                                                                                                                                              |

|           |                                                                                                            |                                                                                                                                                                                         |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                    |

|           |                                                                                                            |                                                                                                                                                                                         |                                                                                                                                                                                                                                  | Disable writes                                                                                                                                                                                                     |

| BSF       | INTCON0,                                                                                                   | GIE                                                                                                                                                                                     | ;                                                                                                                                                                                                                                | Enable interrupts                                                                                                                                                                                                  |

|           | CLRF<br>BCF<br>BCF<br>BSF<br>BSF<br>MOVLW<br>MOVWF<br>MOVWF<br>BSF<br>BTFSC<br>BRA<br>INCFSZ<br>BRA<br>BCF | CLRFNVMADRLBCFNVMCON1,BCFNVMCON1,BCFINTCON0,BSFNVMCON1,BSFNVMCON1,MOVLW55hMOVWFNVMCON2MOVLW0AAhMOVWFNVMCON2BSFNVMCON1,BTFSCNVMCON1,BTFSCNVMCON1,BRA\$-2INCFSZNVMADRL,BRALOOPBCFNVMCON1, | CLRFNVMADRLBCFNVMCON1, CFGSBCFNVMCON1, EEPGDBCFINTCON0, GIEBSFNVMCON1, WRENBSFNVMCON1, RDMOVLW55hMOVWFNVMCON2MOVLW0AAhMOVWFNVMCON1, WRBSFNVMCON1, WRBSFNVMCON1, WRBTFSCNVMCON1, WRBRA\$-2INCFSZNVMADRL, FBRALOOPBCFNVMCON1, WREN | BCFNVMCON1, CFGS;BCFNVMCON1, EEPGD;BCFINTCON0, GIE;BSFNVMCON1, WREN;BSFNVMCON1, RD;MOVLW55h;MOVWFNVMCON2;MOVLW0AAh;BSFNVMCON1, WR;BSFNVMCON1, WR;BSFNVMCON1, WR;BTFSCNVMCON1, WR;BRA\$-2;INCFSZNVMADRL, F;BRALOOP; |

# 15.0 DIRECT MEMORY ACCESS (DMA)

# 15.1 Introduction

The Direct Memory Access (DMA) module is designed to service data transfers between different memory regions directly without intervention from the CPU. By eliminating the need for CPU-intensive management of handling interrupts intended for data transfers, the CPU now can spend more time on other tasks.

PIC18(L)F25/26K83 family has two DMA modules which can be independently programmed to transfer data between different memory locations, move different data sizes, and use a wide range of hardware triggers to initiate transfers. The two DMA registers can even be programmed to work together, in order to carry out more complex data transfers without CPU overhead.

Key features of the DMA module include:

- Support access to the following memory regions:

- GPR and SFR space (R/W)

- Program Flash Memory (R only)

- Data EEPROM Memory (R only)

- Programmable priority between the DMA and CPU Operations. Refer to **Section 3.1 "System Arbitration"** for details.

- Programmable Source and Destination address modes

- Fixed address

- Post-increment address

- Post-decrement address

- Programmable Source and Destination sizes

- Source and destination pointer register, dynamically updated and reloadable

- Source and destination count register, dynamically updated and reloadable

- Programmable auto-stop based on Source or Destination counter

- · Software triggered transfers

- Multiple user selectable sources for hardware triggered transfers

- Multiple user selectable sources for aborting DMA transfers

# 15.2 DMA Registers

The operation of the DMA module has the following registers:

- Control registers (DMAxCON0, DMAxCON1)

- Data buffer register (DMAxBUF)

- Source Start Address Register (DMAxSSAU:H:L)

- Source Pointer Register (DMAxSPTRU:H:L)

- Source Message Size Register (DMAxSSZH:L)

- Source Count Register (DMAxSCNTH:L)

- Destination Start Address Register (DMAxDSAH:L)

- Destination Pointer Register (DMAxDPTRH:L)

- Destination Message Size Register (DMAxDSZH:L)

- Destination Count Register (DMAxDCNTH:L)

- Start Interrupt Request Source Register (DMAxSIRQ)

- Abort Interrupt Request Source Register (DMAxAIRQ)

These registers are detailed in Section 15.13 "Register definitions: DMA".

#### 15.9.5 OVERRUN INTERRUPT

The Overrun Interrupt flag is set if the DMA receives a trigger to start a new message before the current message is completed.

| Instruction                | Э<br>ПППП  | @<br>ПППП | ()<br>   | @<br>ПППП         | ©<br>∩∩∩∩         | 6<br>ПППП         | 0<br>             | ®<br>חחחח | 9<br>ПППП | ₪<br>₪ | ⊕<br>∩∩∩∩         | 9<br>10000        | <br>1000          | ⊌<br>∩∩∩∩         | ₽<br>1000  | Ю<br>ПППП | ₽<br>000000000000000000000000000000000000 | 9<br>1000 | Ray: 10-000275E<br>(19) |

|----------------------------|------------|-----------|----------|-------------------|-------------------|-------------------|-------------------|-----------|-----------|--------|-------------------|-------------------|-------------------|-------------------|------------|-----------|-------------------------------------------|-----------|-------------------------|

| Clock                      |            |           |          |                   |                   |                   |                   |           |           |        |                   |                   |                   |                   |            |           |                                           |           |                         |

| EN                         |            |           |          |                   |                   |                   |                   |           |           |        |                   |                   |                   |                   |            |           |                                           |           |                         |

| SIRQEN                     |            |           |          |                   |                   |                   |                   |           |           |        |                   |                   |                   |                   |            |           |                                           |           |                         |

| Source Hardware<br>Trigger |            |           |          |                   |                   |                   |                   |           |           |        |                   |                   |                   |                   |            |           |                                           |           |                         |

| DGO-                       |            |           |          |                   |                   |                   |                   |           |           |        |                   |                   |                   |                   | 1          |           |                                           |           |                         |

| DMAxSPTR                   |            |           | 0x100    | 0                 |                   | 0x1               | 101               |           |           | 0x100  |                   | y                 | 0x1               | 01                |            |           | 0x100                                     | )         | $\rightarrow$           |

|                            |            |           |          |                   | (                 |                   |                   |           |           |        |                   |                   |                   |                   | \          |           |                                           |           |                         |

| DMAxDPTR                   | <          |           | 0x200    | 0                 | /                 | χ(0x2             | 201               | K         |           | 0x202  |                   | X                 | 0x2               | 03                | (          |           | 0x200                                     | )         | >                       |

| DMAxSCNT                   | $\langle $ |           | 2        |                   |                   | Χ                 | 1                 |           |           | 2      |                   | X                 | 1                 | L                 |            |           | 2                                         |           |                         |

| DMAxDCNT                   | $\langle $ |           | 4        |                   | /                 | Χ                 | 3                 |           |           | 2      |                   | X                 | 1                 | L )               | $\langle $ |           | 4                                         |           |                         |

| DMA STATE                  |            | IDLE      | 1        | SR <sup>(1)</sup> | DW <sup>(2)</sup> | SR <sup>(1)</sup> | DW <sup>(2)</sup> |           | IDLE      | 1      | SR <sup>(1)</sup> | DW <sup>(2)</sup> | SR <sup>(1)</sup> | DW <sup>(2)</sup> |            |           | IDLE                                      |           |                         |

| DMAxSCNTIF                 |            |           |          |                   |                   |                   |                   |           |           |        |                   |                   |                   |                   |            |           |                                           |           |                         |

| DMAxDCNTIF                 |            |           |          |                   |                   |                   |                   |           |           |        |                   |                   |                   |                   |            |           |                                           |           |                         |

| DMAxORIF _                 |            |           |          |                   |                   |                   |                   |           |           |        |                   |                   |                   |                   |            |           |                                           |           |                         |

|                            | DM         | AxCON     | 1bits.SM | A = 01            |                   |                   |                   |           |           |        |                   |                   |                   |                   |            |           |                                           |           |                         |

|                            | DM         | AxSSA     | 0x10     | 00                |                   | DMAxD             | SA                | 0x200     |           |        |                   |                   |                   |                   |            |           |                                           |           |                         |

|                            | DM         | AxSSZ     | 0x2      | 2                 |                   | DMAxD             | sz                | 0x20      |           |        |                   |                   |                   |                   |            |           |                                           |           |                         |

| Note 1:                    | SR -       | Sou       | rce R    | ead               |                   |                   |                   |           |           |        |                   |                   |                   |                   |            |           |                                           |           |                         |

| 2:                         |            |           | stinati  |                   | rite              |                   |                   |           |           |        |                   |                   |                   |                   |            |           |                                           |           |                         |

| 2.                         | 511-       | Det       | sinati   |                   |                   |                   |                   |           |           |        |                   |                   |                   |                   |            |           |                                           |           |                         |

## FIGURE 15-9: OVERRUN INTERRUPT

## REGISTER 15-15: DMAxDSAH: DMAx DESTINATION START ADDRESS HIGH REGISTER

| R/W-0/0      | R/W-0/0 | R/W-0/0         | R/W-0/0 | R/W-0/0      | R/W-0/0           | R/W-0/0 | R/W-0/0 |

|--------------|---------|-----------------|---------|--------------|-------------------|---------|---------|

|              |         |                 | DSA     | <15:8>       |                   |         |         |

| bit 7        |         |                 |         |              |                   |         | bit 0   |

|              |         |                 |         |              |                   |         |         |

| Legend:      |         |                 |         |              |                   |         |         |

| R = Readable | bit     | W = Writable bi | t       | U = Unimplem | ented bit, read a | as 'O'  |         |

|                         |                |                    | 43 0                 |

|-------------------------|----------------|--------------------|----------------------|

| -n/n = Value at POR and | 1 = bit is set | 0 = bit is cleared | x = bit is unknown   |

| BOR/Value at all other  |                |                    | u = bit is unchanged |

| Resets                  |                |                    |                      |

bit 7-0 DSA<15:8>: Destination Start Address bits

#### REGISTER 15-16: DMAxDPTRL: DMAx DESTINATION POINTER LOW REGISTER

| R-0       | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0   |  |  |

|-----------|-----|-----|-----|-----|-----|-----|-------|--|--|

| DPTR<7:0> |     |     |     |     |     |     |       |  |  |

| bit 7     |     |     |     |     |     |     | bit 0 |  |  |

|           |     |     |     |     |     |     |       |  |  |

| Legend:   |     |     |     |     |     |     |       |  |  |

| Logonan                                                     |                  |                                    |                                            |  |  |  |

|-------------------------------------------------------------|------------------|------------------------------------|--------------------------------------------|--|--|--|

| R = Readable bit                                            | W = Writable bit | U = Unimplemented bit, read as '0' |                                            |  |  |  |

| -n/n = Value at POR and<br>BOR/Value at all other<br>Resets | 1 = bit is set   | 0 = bit is cleared                 | x = bit is unknown<br>u = bit is unchanged |  |  |  |

bit 7-0 DPTR<7:0>: Current Destination Address Pointer

#### REGISTER 15-17: DMAxDPTRH: DMAx DESTINATION POINTER HIGH REGISTER

| R-0        | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 |  |  |  |

|------------|-----|-----|-----|-----|-----|-----|-----|--|--|--|

| DPTR<15:8> |     |     |     |     |     |     |     |  |  |  |

| bit 7      |     |     |     |     |     |     |     |  |  |  |

| Legend:                                                     |                  |                          |                                            |

|-------------------------------------------------------------|------------------|--------------------------|--------------------------------------------|

| R = Readable bit                                            | W = Writable bit | U = Unimplemented bit, r | ead as '0'                                 |

| -n/n = Value at POR and<br>BOR/Value at all other<br>Resets | 1 = bit is set   | 0 = bit is cleared       | x = bit is unknown<br>u = bit is unchanged |

bit 7-0 DPTR<15:8>: Current Destination Address Pointer

© 2017 Microchip Technology Inc.

| U-0                                                                                                                       | R/W-0/0                                                         | R/W-0/0                              | R/W-0/0         | U-0             | U-0              | R/W-0/0        | R/W-0/0       |

|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--------------------------------------|-----------------|-----------------|------------------|----------------|---------------|

| 0-0                                                                                                                       | SLEW                                                            | PU<1:0>                              |                 | 0-0             | 0-0              |                | :1:0>         |

|                                                                                                                           |                                                                 |                                      |                 | _               | —                | 184            |               |

| bit 7                                                                                                                     |                                                                 |                                      |                 |                 |                  |                | bit 0         |

|                                                                                                                           |                                                                 |                                      |                 |                 |                  |                |               |

| Legend:                                                                                                                   |                                                                 |                                      |                 |                 |                  |                |               |

| R = Readable                                                                                                              | e bit                                                           | W = Writable                         | bit             | U = Unimpler    | nented bit, read | d as '0'       |               |

| u = Bit is uncl                                                                                                           | hanged                                                          | x = Bit is unki                      | nown            | -n/n = Value a  | at POR and BO    | R/Value at all | other Resets  |

| '1' = Bit is set                                                                                                          |                                                                 | '0' = Bit is cle                     | ared            | HS = Hardwa     | ire set          |                |               |

|                                                                                                                           |                                                                 |                                      |                 |                 |                  |                |               |

| bit 7                                                                                                                     | Unimplemer                                                      | nted: Read as '                      | 0'              |                 |                  |                |               |

| bit 6                                                                                                                     | SLEW: I <sup>2</sup> C S                                        | pecific Slew Ra                      | ate Limiting is | Enabled         |                  |                |               |

|                                                                                                                           |                                                                 |                                      | imiting is enat | oled. Standard  | pad slew limitin | g is disabled. | The SLRxy bit |

|                                                                                                                           | is ignor                                                        |                                      |                 |                 |                  |                |               |

|                                                                                                                           | _                                                               |                                      |                 | disabled via SL | Rxy bit.         |                |               |

| bit 5-4                                                                                                                   |                                                                 | Pull-up Select                       | tion bits       |                 |                  |                |               |

|                                                                                                                           | 11 = Reserv                                                     |                                      |                 |                 |                  |                |               |

|                                                                                                                           |                                                                 | irrent of standa<br>rent of standard | •               | •               |                  |                |               |

|                                                                                                                           |                                                                 |                                      |                 | led via WPUxy   | bit              |                |               |

| bit 3-2                                                                                                                   |                                                                 | nted: Read as '                      |                 |                 |                  |                |               |

|                                                                                                                           | -                                                               |                                      |                 |                 |                  |                |               |

| bit 1-0 <b>TH&lt;1:0&gt;</b> : I <sup>2</sup> C Input Threshold Selection bits<br>11 = SMBus 3.0 (1.35 V) input threshold |                                                                 |                                      |                 |                 |                  |                |               |

|                                                                                                                           |                                                                 | s 2.0 (2.1 V) inj                    |                 |                 |                  |                |               |

|                                                                                                                           |                                                                 | ecific input thre                    |                 |                 |                  |                |               |

|                                                                                                                           |                                                                 | registers                            |                 |                 |                  |                |               |

|                                                                                                                           | 00 = Standard GPIO Input pull-up, enabled via INLVLxy registers |                                      |                 |                 |                  |                |               |

# REGISTER 16-9: RxyI2C: I<sup>2</sup>C PAD Rxy CONTROL REGISTER

# TABLE 16-10: I2C PAD CONTROL REGISTERS

| Name   | Bit 7 | Bit 6 | Bit 5   | Bit 4 | Bit 3 | Bit 2 | Bit 1   | Bit 0 |

|--------|-------|-------|---------|-------|-------|-------|---------|-------|

| RB1I2C |       | SLEW  | PU<1:0> |       | —     | _     | TH<1:0> |       |

| RB2I2C | —     | SLEW  | PU<1:0> |       | —     | _     | TH<1:0> |       |

| RC3I2C | —     | SLEW  | PU<     | 1:0>  | —     | _     | TH<     | 1:0>  |

| RC4I2C | _     | SLEW  | PU<1:0> |       | —     | _     | TH<     | 1:0>  |

# 22.7 Register Definitions: Timer2/4/6 Control

Long bit name prefixes for the Timer2/4/6 peripherals are shown in Table 22-2. Refer to **Section 1.3.2.2 "Long Bit Names"** for more information.

# TABLE 22-2: OPERATING MODES

| Peripheral | Bit Name Prefix |  |  |  |

|------------|-----------------|--|--|--|

| Timer2     | T2              |  |  |  |

| Timer4     | T4              |  |  |  |

| Timer6     | Т6              |  |  |  |

## REGISTER 22-1: TxCLK: TIMERx CLOCK SELECTION REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|---------|---------|---------|---------|

| —     | —   |     | —   |         | CS<     | 3:0>    |         |

| bit 7 |     |     |     |         |         |         | bit 0   |

# Legend:

| Logonal              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-4 Unimplemented: Read as '0'

#### bit 3-0 CS<3:0>: Timerx Clock Selection bits

| CS<3:0> | T2TMR                   | TMR4                    | TMR6                    |

|---------|-------------------------|-------------------------|-------------------------|

| 03<3:0> | Clock Source            | Clock Source            | Clock Source            |

| 1111    | Reserved                | Reserved                | Reserved                |

| 1110    | CLC4_out                | CLC4_out                | CLC4_out                |

| 1101    | CLC3_out                | CLC3_out                | CLC3_out                |

| 1100    | CLC2_out                | CLC2_out                | CLC2_out                |

| 1011    | CLC1_out                | CLC1_out                | CLC1_out                |

| 1010    | ZCD_OUT                 | ZCD_OUT                 | ZCD_OUT                 |

| 1001    | NCO10UT                 | NCO10UT                 | NCO1OUT                 |

| 1000    | CLKREF_OUT              | CLKREF_OUT              | CLKREF_OUT              |

| 0111    | SOSC                    | SOSC                    | SOSC                    |

| 0110    | MFINTOSC (32 kHz)       | MFINTOSC (32 kHz)       | MFINTOSC (32 kHz)       |

| 0101    | MFINTOSC (500 kHz)      | MFINTOSC (500 kHz)      | MFINTOSC (500 kHz)      |

| 0100    | LFINTOSC                | LFINTOSC                | LFINTOSC                |

| 0011    | HFINTOSC                | HFINTOSC                | HFINTOSC                |

| 0010    | Fosc                    | Fosc                    | Fosc                    |

| 0001    | Fosc/4                  | Fosc/4                  | Fosc/4                  |

| 0000    | Pin selected by T2INPPS | Pin selected by T4INPPS | Pin selected by T6INPPS |

## 23.3.1 CCPx PIN CONFIGURATION

The software must configure the CCPx pin as an output by clearing the associated TRIS bit and defining the appropriate output pin through the RxyPPS registers. See **Section 17.0 "Peripheral Pin Select (PPS) Module"** for more details.

Note: Clearing the CCPxCON register will force the CCPx compare output latch to the default low level. This is not the PORT I/O data latch.

#### 23.3.2 TIMER1 MODE RESOURCE

In Compare mode, Timer1 must be running in either Timer mode or Synchronized Counter mode. The compare operation may not work in Asynchronous Counter mode.

See Section 21.0 "Timer1/3/5 Module with Gate Control" for more information on configuring Timer1.

Note: Clocking Timer1 from the system clock (Fosc) should not be used in Compare mode. In order for Compare mode to recognize the trigger event on the CCPx pin, TImer1 must be clocked from the instruction clock (Fosc/4) or from an external clock source.

## 23.3.3 AUTO-CONVERSION TRIGGER

All CCPx modes set the CCP interrupt flag (CCPxIF). When this flag is set and a match occurs, an autoconversion trigger can take place if the CCP module is selected as the conversion trigger source.

Refer to **Section 37.2.5 "Auto-Conversion Trigger"** for more information.

| Note: | Removing the match condition by       |

|-------|---------------------------------------|

|       | changing the contents of the CCPRxH   |

|       | and CCPRxL register pair, between the |

|       | clock edge that generates the Auto-   |

|       | conversion Trigger and the clock edge |

|       | that generates the Timer1 Reset, will |

|       | preclude the Reset from occurring     |

#### 23.3.4 COMPARE DURING SLEEP

Since FOSC is shut down during Sleep mode, the Compare mode will not function properly during Sleep, unless the timer is running. The device will wake on interrupt (if enabled).

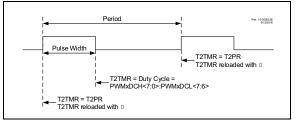

# 23.4 PWM Overview

Pulse-Width Modulation (PWM) is a scheme that provides power to a load by switching quickly between fully ON and fully OFF states. The PWM signal resembles a square wave where the high portion of the signal is considered the ON state and the low portion of the signal is considered the OFF state. The high portion, also known as the pulse width, can vary in time and is defined in steps. A larger number of steps applied, which lengthens the pulse width, also supplies more power to the load. Lowering the number of steps applied, which shortens the pulse width, supplies less power. The PWM period is defined as the duration of one complete cycle or the total amount of on and off time combined.

PWM resolution defines the maximum number of steps that can be present in a single PWM period. A higher resolution allows for more precise control of the pulsewidth time and in turn the power that is applied to the load.

The term duty cycle describes the proportion of the on time to the off time and is expressed in percentages, where 0% is fully off and 100% is fully on. A lower duty cycle corresponds to less power applied and a higher duty cycle corresponds to more power applied.

Figure 23-3 shows a typical waveform of the PWM signal.

#### 23.4.1 STANDARD PWM OPERATION

The standard PWM mode generates a Pulse-Width Modulation (PWM) signal on the CCPx pin with up to ten bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- T2PR registers

- · T2CON registers

- · CCPRxL and CCPRxH registers

- CCPxCON registers

It is required to have Fosc/4 as the clock input to TMR2/4/6 for correct PWM operation. Figure 23-4 shows a simplified block diagram of PWM operation.

Note: The corresponding TRIS bit must be cleared to enable the PWM output on the CCPx pin.

#### FIGURE 23-3: CCP PWM OUTPUT SIGNAL

## REGISTER 25-13: SMTxCPWL: SMT CAPTURED PULSE WIDTH REGISTER – LOW BYTE

| R-x/x            | R-x/x                         | R-x/x             | R-x/x | R-x/x                                               | R-x/x                              | R-x/x | R-x/x |  |  |

|------------------|-------------------------------|-------------------|-------|-----------------------------------------------------|------------------------------------|-------|-------|--|--|

|                  |                               |                   | SMTx0 | CPW<7:0>                                            |                                    |       |       |  |  |

| bit 7            |                               |                   |       |                                                     |                                    |       | bit 0 |  |  |

|                  |                               |                   |       |                                                     |                                    |       |       |  |  |

| Legend:          |                               |                   |       |                                                     |                                    |       |       |  |  |

| R = Readable     | able bit W = Writable bit U = |                   |       |                                                     | U = Unimplemented bit, read as '0' |       |       |  |  |

| u = Bit is uncha | anged                         | x = Bit is unkne  | own   | -n/n = Value at POR and BOR/Value at all other Rese |                                    |       |       |  |  |

| '1' = Bit is set |                               | '0' = Bit is clea | red   |                                                     |                                    |       |       |  |  |

bit 7-0 SMTxCPW<7:0>: Significant bits of the SMT PW Latch – Low Byte

#### REGISTER 25-14: SMTxCPWH: SMT CAPTURED PULSE WIDTH REGISTER - HIGH BYTE

| R-x/x            | R-x/x | R-x/x            | R-x/x  | R-x/x           | R-x/x           | R-x/x    | R-x/x |

|------------------|-------|------------------|--------|-----------------|-----------------|----------|-------|

|                  |       |                  | SMTxCP | W<15:8>         |                 |          |       |

| bit 7            |       |                  |        |                 |                 |          | bit 0 |

|                  |       |                  |        |                 |                 |          |       |

| Legend:          |       |                  |        |                 |                 |          |       |

| R = Readable bit |       | W = Writable bit |        | II = I Inimpler | mented hit read | 1 as '0' |       |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SMTxCPW<15:8>: Significant bits of the SMT PW Latch – High Byte

## REGISTER 25-15: SMTxCPWU: SMT CAPTURED PULSE WIDTH REGISTER - UPPER BYTE

| R-x/x | R-x/x | R-x/x | R-x/x   | R-x/x    | R-x/x | R-x/x | R-x/x |

|-------|-------|-------|---------|----------|-------|-------|-------|

|       |       |       | SMTxCPV | V<23:16> |       |       |       |

| bit 7 |       |       |         |          |       |       | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SMTxCPW<23:16>: Significant bits of the SMT PW Latch – Upper Byte

# PIC18(L)F25/26K83

© 2017 Microchip Technology Inc.

DS40001943A-page 660

# 37.7 Register Definitions: ADC Control

| REGISTER        |                    | ONO: ADC C                     |                    |                                  |                    |               |                   |

|-----------------|--------------------|--------------------------------|--------------------|----------------------------------|--------------------|---------------|-------------------|

| R/W-0/0         | R/W-0/0            | U-0                            | R/W-0/0            | U-0                              | R/W-0/0            | U-0           | R/W/HC-0          |

| ON              | CONT               | —                              | CS                 | —                                | FM                 | -             | GO                |

| bit 7           |                    |                                |                    |                                  |                    |               | bit C             |

|                 |                    |                                |                    |                                  |                    |               |                   |

| Legend:         |                    |                                |                    |                                  |                    |               |                   |

| R = Readabl     | le bit             | W = Writable                   | e bit              |                                  | mented bit, read   |               |                   |

| u = Bit is und  | changed            | x = Bit is unł                 | known              | -n/n = Value                     | at POR and BO      | R/Value at a  | Il other Resets   |

| '1' = Bit is se | et                 | '0' = Bit is cl                | eared              | HC = Bit is cl                   | leared by hardwa   | are           |                   |

|                 |                    |                                |                    |                                  |                    |               |                   |

| bit 7           | ON: ADC Er         | nable bit                      |                    |                                  |                    |               |                   |

|                 | 1 = ADC is e       |                                |                    |                                  |                    |               |                   |

|                 | 0 = ADC is c       |                                |                    |                                  |                    |               |                   |

| bit 6           |                    | Continuous O                   |                    |                                  |                    |               |                   |

|                 |                    |                                |                    | each conversions of the value of | on trigger until A | DTIF is set ( | if ADSOI is set   |

|                 |                    |                                |                    | ach conversion                   |                    |               |                   |

| bit 5           |                    | nted: Read as                  | •                  |                                  |                    |               |                   |

| bit 4           | -                  | ock Selection b                |                    |                                  |                    |               |                   |

|                 | 1 = Clock s        | upplied from Fl                | RC dedicated of    | oscillator                       |                    |               |                   |