Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                  |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-UQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-UQFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f25k83t-i-mx |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.1 System Arbitration

The System Arbiter resolves memory access between the System Level Selections (i.e., Main, Interrupt Service Routine) and Peripheral Selection (i.e., DMA and Scanner) based on user-assigned priorities. Each of the system level and peripheral selections has its own priority selection registers. Memory access priority is resolved using the number written to the corresponding Priority registers, 0 being the highest priority and 4 the lowest. The default priorities are listed in Table 3-1.

In case the user wants to change priorities, ensure each Priority register is written with a unique value from 0 to 4.

**TABLE 3-1: DEFAULT PRIORITIES**

| Sele         | Priority register<br>Reset value |   |

|--------------|----------------------------------|---|

| System Level | ISR                              | 0 |

|              | MAIN                             | 1 |

| Peripheral   | DMA1                             | 2 |

|              | DMA2                             | 3 |

|              | SCANNER                          | 4 |

TABLE 3-2: SUMMARY OF REGISTERS ASSOCIATED WITH CPU

| Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2   | Bit 1   | Bit 0    | Register on page |

|--------|-------|-------|-------|-------|-------|---------|---------|----------|------------------|

| ISRPR  | _     | _     | _     | _     | _     | ISRPR2  | ISRPR1  | ISRPR0   | 20               |

| MAINPR | _     | _     | _     | _     | _     | MAINPR2 | MAINPR1 | MAINPR0  | 20               |

| DMA1PR | _     | _     | _     | _     | _     | DMA1PR2 | DMA1PR1 | DMA1PR0  | 20               |

| DMA2PR | _     | _     | _     | _     | _     | DMA2PR2 | DMA2PR1 | DMA2PR0  | 21               |

| SCANPR | _     | _     | _     | _     | _     | SCANPR2 | SCANPR1 | SCANPR0  | 21               |

| PRLOCK | _     | _     | _     | _     | _     | _       | _       | PRLOCKED | 21               |

**Legend:** — = Unimplemented location, read as '0'.

## REGISTER 4-4: STKPTR: STACK POINTER REGISTER

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-------------|-------|-------|

| _     | _   | _   |       |       | STKPTR<4:0> |       |       |

| bit 7 |     |     |       |       |             |       | bit 0 |

| Legend:           |                  |                      |                        |

|-------------------|------------------|----------------------|------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | C = Clearable only bit |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown     |

bit 7-5 **Unimplemented:** Read as '0'

bit 4-0 STKPTR<4:0>: Stack Pointer Location bits

#### 4.3.1 FAST REGISTER STACK

There are three levels of fast stack registers available one for CALL type instructions and two for interrupts. A fast register stack is provided for the Status, WREG and BSR registers, to provide a "fast return" option for interrupts. It is loaded with the current value of the corresponding register when the processor vectors for an interrupt. All interrupt sources will push values into the stack registers. The values in the registers are then loaded back into their associated registers if the RETFIE, FAST instruction is used to return from the interrupt. Refer to Section 4.5.6 "Call Shadow Register" for interrupt call shadow registers.

Example 4-1 shows a source code example that uses the fast register stack during a subroutine call and return.

# EXAMPLE 4-1: FAST REGISTER STACK CODE EXAMPLE

```

CALL SUB1, FAST ;STATUS, WREG, BSR;SAVED IN FAST REGISTER;STACK

SUB1

RETURN, FAST ;RESTORE VALUES SAVED; IN FAST REGISTER STACK

```

| GURE 9-8: INTERRUPT TIMING DIAGRAM - TWO WORD INSTRUCTION |                                                 |                                          |       |                 |                       |        |                      |                         |

|-----------------------------------------------------------|-------------------------------------------------|------------------------------------------|-------|-----------------|-----------------------|--------|----------------------|-------------------------|

| 1                                                         | 2 3                                             | 4 5                                      | 6     | 7               | 8                     | 9      | 10                   | Rev. 10-00@6<br>9/12/20 |

| System Clock                                              |                                                 |                                          | M     | www.            | Ň                     | u<br>M | $\tilde{\mathbf{M}}$ |                         |

| Program Y Counter                                         | Y+2 Y+2                                         | Y+2 0x82                                 | 0x218 | 0x21A           | 0x21C                 | Y+2    | Y+4                  | Y+6                     |

| Instruction Register                                      | Inst @ Y <sup>(1)</sup> Inst @ Y <sup>(1)</sup> | FNOP FNOP                                | FNOP  | Inst @ 0x218 Ir | nst @ 0x21A<br>RETFIE | FNOP   | Inst @ Y+2           | Inst @ Y+4              |

| Interrupt                                                 |                                                 |                                          |       |                 |                       |        |                      |                         |

| Routine (                                                 | MAIN                                            | FNOP                                     |       | ISR             | X                     | FNOP   | МА                   | IN                      |

| IVTBASE                                                   |                                                 | 0x80                                     |       | $\neg$          |                       |        |                      |                         |

| Vector                                                    |                                                 | 1                                        |       |                 |                       |        |                      |                         |

| Number<br>Program Memory                                  |                                                 | •                                        |       |                 |                       |        |                      |                         |

| 0x82                                                      | ′                                               | 0x86                                     |       |                 |                       |        |                      |                         |

|                                                           | Interrupt Location =<br>=                       | Interrupt vector ta<br>0x86 << 2 = 0x218 |       | 2               |                       |        |                      |                         |

|                                                           |                                                 |                                          |       |                 |                       |        |                      |                         |

| Note 1: Instruction @ Y is a two                          | o-cycle instruction.                            |                                          |       |                 |                       |        |                      |                         |

|                                                           |                                                 |                                          |       |                 |                       |        |                      |                         |

PIC18(L)F25/26K83

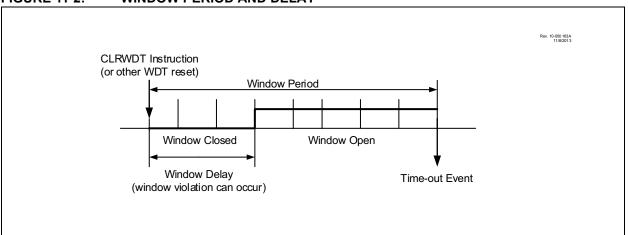

## 11.6 Operation During Sleep

When the device enters Sleep, the WWDT is cleared. If the WWDT is enabled during Sleep, the WWDT resumes counting. When the device exits Sleep, the WWDT is cleared again.

The WWDT remains clear until the Oscillator Start-up Timer (OST) completes, if enabled. See **Section 7.2.1.3 "Oscillator Start-up Timer (OST)"** for more information on the OST.

When a WWDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits in the STATUS register are changed to indicate the event. The  $\overline{\text{RWDT}}$  bit in the PCON0 register can also be used. See **Section 4.0 "Memory Organization"** for more information.

TABLE 11-2: WWDT CLEARING CONDITIONS

| Conditions                                              | WWDT                         |  |  |  |  |

|---------------------------------------------------------|------------------------------|--|--|--|--|

| WDTE<1:0> = 00                                          |                              |  |  |  |  |

| WDTE<1:0> = 01 and SEN = 0                              |                              |  |  |  |  |

| WDTE<1:0> = 10 and enter Sleep                          | Cleared                      |  |  |  |  |

| CLRWDT Command                                          | Cleared                      |  |  |  |  |

| Oscillator Fail Detected                                |                              |  |  |  |  |

| Exit Sleep + System Clock = SOSC, EXTRC, INTOSC, EXTCLK |                              |  |  |  |  |

| Exit Sleep + System Clock = XT, HS, LP                  | Cleared until the end of OST |  |  |  |  |

| Change INTOSC divider (IRCF bits)                       | Unaffected                   |  |  |  |  |

FIGURE 11-2: WINDOW PERIOD AND DELAY

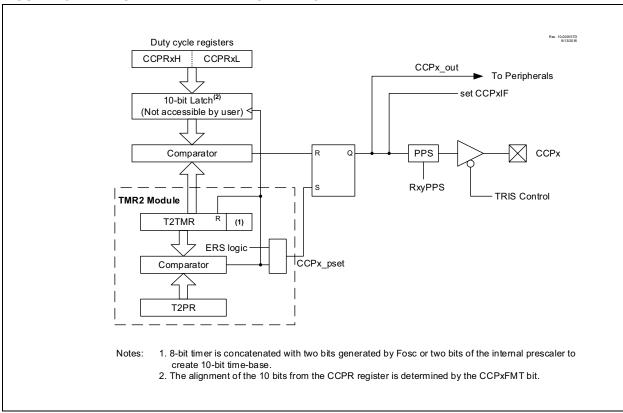

## FIGURE 23-4: SIMPLIFIED PWM BLOCK DIAGRAM

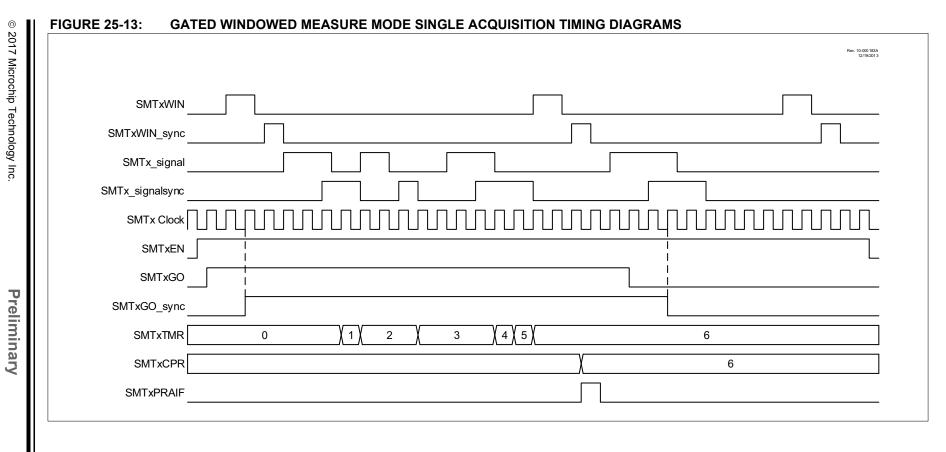

## 25.8 Register Definitions: SMT Control

Long bit name prefixes for the Signal Measurement Timer peripherals are shown in **Section 1.3** "**Register and Bit naming conventions**".

TABLE 25-2: LONG BIT NAMES PREFIXES FOR SMT PERIPHERALS

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| SMT1       | SMT1            |

| SMT2       | SMT2            |

## REGISTER 25-1: SMTxCON0: SMT CONTROL REGISTER 0

| R/W-0/0           | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------------------|-----|---------|---------|---------|---------|---------|---------|

| EN <sup>(1)</sup> | _   | STP     | WPOL    | SPOL    | CPOL    | PS<1:0> |         |

| bit 7             |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | EN: SMT Enable bit <sup>(1)</sup> 1 = SMT is enabled                                                                                                                                        |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 '' 0  | 0 = SMT is disabled; internal states are reset, clock requests are disabled                                                                                                                 |

| bit 6   | Unimplemented: Read as '0'                                                                                                                                                                  |

| bit 5   | STP: SMT Counter Halt Enable bit                                                                                                                                                            |

|         | When SMTxTMR = SMTxPR:  1 = Counter remains SMTxPR; period match interrupt occurs when clocked  0 = Counter resets to 24'h000000; period match interrupt occurs when clocked                |

| bit 4   | WPOL: SMTxWIN Input Polarity Control bit  1 = SMTxWIN signal is active-low/falling edge enabled  0 = SMTxWIN signal is active-high/rising edge enabled                                      |

| bit 3   | SPOL: SMTxSIG Input Polarity Control bit  1 = SMTx_signal is active-low/falling edge enabled  0 = SMTx_signal is active-high/rising edge enabled                                            |

| bit 2   | CPOL: SMT Clock Input Polarity Control bit  1 = SMTxTMR increments on the falling edge of the selected clock signal  0 = SMTxTMR increments on the rising edge of the selected clock signal |

| bit 1-0 | PS<1:0>: SMT Prescale Select bits  11 = Prescaler = 1:8  10 = Prescaler = 1:4  01 = Prescaler = 1:2  00 = Prescaler = 1:1                                                                   |

**Note 1:** Setting EN to '0' does not affect the register contents.

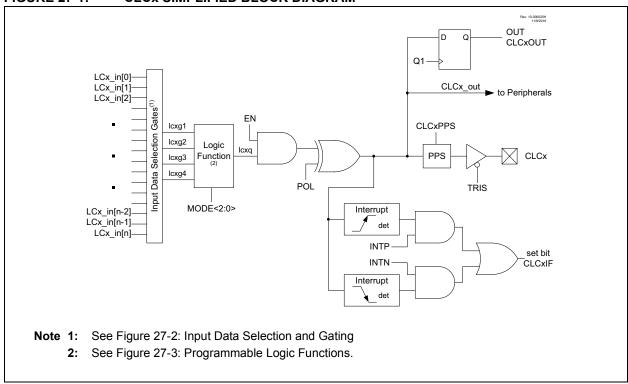

FIGURE 27-1: CLCx SIMPLIFIED BLOCK DIAGRAM

## 27.1 CLCx Setup

Programming the CLCx module is performed by configuring the four stages in the logic signal flow. The four stages are:

- · Data selection

- · Data gating

- · Logic function selection

- · Output polarity

Each stage is setup at run time by writing to the corresponding CLCx Special Function Registers. This has the added advantage of permitting logic reconfiguration on-the-fly during program execution.

#### 27.1.1 DATA SELECTION

There are 32 signals available as inputs to the configurable logic. Four 32-input multiplexers are used to select the inputs to pass on to the next stage.

Data selection is through four multiplexers as indicated on the left side of Figure 27-2. Data inputs in the figure are identified by a generic numbered input name.

Table 27-1 correlates the generic input name to the actual signal for each CLC module. The column labeled 'DyS<4:0> Value' indicates the MUX selection code for the selected data input. DyS is an abbreviation for the MUX select input codes: D1S<4:0> through D4S<4:0>.

Data inputs are selected with CLCxSEL0 through CLCxSEL3 registers (Register 27-3 through Register 27-6).

**Note:** Data selections are undefined at power-up.

## REGISTER 27-10: CLCxGLS3: GATE 3 LOGIC SELECT REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| G4D4T   | G4D4N   | G4D3T   | G4D3N   | G4D2T   | G4D2N   | G4D1T   | G4D1N   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7 | G4D4T: Gate 3 Data 4 True (non-inverted) bit        |  |  |  |  |  |

|-------|-----------------------------------------------------|--|--|--|--|--|

|       | 1 = CLCIN3 (true) is gated into CLCx Gate 3         |  |  |  |  |  |

|       | 0 = CLCIN3 (true) is not gated into CLCx Gate 3     |  |  |  |  |  |

| bit 6 | G4D4N: Gate 3 Data 4 Negated (inverted) bit         |  |  |  |  |  |

|       | 1 = CLCIN3 (inverted) is gated into CLCx Gate 3     |  |  |  |  |  |

|       | 0 = CLCIN3 (inverted) is not gated into CLCx Gate 3 |  |  |  |  |  |

| bit 5 | G4D3T: Gate 3 Data 3 True (non-inverted) bit        |  |  |  |  |  |

|       | 1 = CLCIN2 (true) is gated into CLCx Gate 3         |  |  |  |  |  |

|       | 0 = CLCIN2 (true) is not gated into CLCx Gate 3     |  |  |  |  |  |

| bit 4 | G4D3N: Gate 3 Data 3 Negated (inverted) bit         |  |  |  |  |  |

|       | 1 = CLCIN2 (inverted) is gated into CLCx Gate 3     |  |  |  |  |  |

|       | 0 = CLCIN2 (inverted) is not gated into CLCx Gate 3 |  |  |  |  |  |

| bit 3 | <b>G4D2T:</b> Gate 3 Data 2 True (non-inverted) bit |  |  |  |  |  |

|       | 1 = CLCIN1 (true) is gated into CLCx Gate 3         |  |  |  |  |  |

|       | 0 = CLCIN1 (true) is not gated into CLCx Gate 3     |  |  |  |  |  |

| bit 2 | <b>G4D2N:</b> Gate 3 Data 2 Negated (inverted) bit  |  |  |  |  |  |

|       | 1 = CLCIN1 (inverted) is gated into CLCx Gate 3     |  |  |  |  |  |

|       | 0 = CLCIN1 (inverted) is not gated into CLCx Gate 3 |  |  |  |  |  |

| bit 1 | <b>G4D1T:</b> Gate 4 Data 1 True (non-inverted) bit |  |  |  |  |  |

|       | 1 = CLCIN0 (true) is gated into CLCx Gate 3         |  |  |  |  |  |

|       | 0 = CLCIN0 (true) is not gated into CLCx Gate 3     |  |  |  |  |  |

| bit 0 | <b>G4D1N:</b> Gate 3 Data 1 Negated (inverted) bit  |  |  |  |  |  |

|       | 1 = CLCIN0 (inverted) is gated into CLCx Gate 3     |  |  |  |  |  |

|       | 0 = CLCIN0 (inverted) is not gated into CLCx Gate 3 |  |  |  |  |  |

TABLE 30-2: MD1SRC SELECTION MUX CONNECTIONS

| MS<4:0 | >  | Connection               |  |  |  |

|--------|----|--------------------------|--|--|--|

|        |    |                          |  |  |  |

| 1 1111 | 31 | Reserved                 |  |  |  |

| 1 1000 | 24 |                          |  |  |  |

| 1 0111 | 23 | CAN tx0                  |  |  |  |

| 1 0110 | 22 | SPI1 SDO                 |  |  |  |

| 1 0101 | 21 | Reserved                 |  |  |  |

| 1 0100 | 20 | UART2 TX                 |  |  |  |

| 1 0011 | 19 | UART1 TX                 |  |  |  |

| 1 0010 | 18 | CLC4 OUT                 |  |  |  |

| 1 0001 | 17 | CLC3 OUT                 |  |  |  |

| 1 0000 | 16 | CLC2 OUT                 |  |  |  |

| 0 1111 | 15 | CLC1 OUT                 |  |  |  |

| 0 1110 | 14 | CMP2 OUT                 |  |  |  |

| 0 1101 | 13 | CMP1 OUT                 |  |  |  |

| 0 1100 | 12 | NCO1 OUT                 |  |  |  |

| 0 1011 | 11 | Reserved                 |  |  |  |

| 0 1010 | 10 | Reserved                 |  |  |  |

| 0 1001 | 9  | PWM8 OUT                 |  |  |  |

| 0 1000 | 8  | PWM7 OUT                 |  |  |  |

| 0 0111 | 7  | PWM6 OUT                 |  |  |  |

| 0 0110 | 6  | PWM5 OUT                 |  |  |  |

| 0 0101 | 5  | CCP4 OUT                 |  |  |  |

| 0 0100 | 4  | CCP3 OUT                 |  |  |  |

| 0 0011 | 3  | CCP2 OUT                 |  |  |  |

| 0 0010 | 2  | CCP1 OUT                 |  |  |  |

| 0 0001 | 1  | DSM1 BIT                 |  |  |  |

| 0 0000 | 0  | Pin selected by MDSRCPPS |  |  |  |

TABLE 30-3: SUMMARY OF REGISTERS ASSOCIATED WITH DATA SIGNAL MODULATOR MODE

| Name    | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3      | Bit 2      | Bit 1 | Bit 0  | Register on Page |

|---------|-------|-------|-------|--------|------------|------------|-------|--------|------------------|

| MD1CON0 | EN    | _     | OUT   | OPOL   |            |            | _     | BIT    | 455              |

| MD1CON1 | _     | _     | CHPOL | CHSYNC |            |            | CLPOL | CLSYNC | 456              |

| MD1CARH | _     | _     | _     | _      | _          | — CHS<2:0> |       | 457    |                  |

| MD1CARL | _     | _     | _     | _      | — CLS<2:0> |            | 457   |        |                  |

| MDSRC   | _     | _     | _     | _      | SRCS<3:0>  |            | 458   |        |                  |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used in the Data Signal Modulator mode.

When TXMTIF goes true, indicating the transmit shift register has completed sending the last byte in the frame, the TX output is held in the Idle state for the number of half-bit periods selected by the STP bits in the UxCON2 register.

After the last Stop bit, the TX output is held in the Idle state for an additional wait time determined by the half-bit period count in the UxP1 register. For example, a 2450  $\mu$ s delay (~6 half-bit times) requires a value of 6 in UxP1L.

Any writes to the UxTXB register that occur after TXMTIF goes true, but before the UxP1 wait time, will be held and then transmitted immediately following the wait time. If a backward frame is received during the wait time, any bytes that may have been written to UxTXB will be transmitted after completion of the backward frame reception the backward frame plus the UxP1 wait time.

The wait timer is reset by the backward frame and starts over immediately following the Stop bits of the backward frame. Data pending in the transmit shift register will be sent when the wait time elapses.

To replace or delete any pending forward frame data, the TXBE bit needs to be set to flush the shift register and transmit buffer, then write the new control byte to the UxTXB register. The new control byte will be held in the buffer and sent as the beginning of the next forward frame following the UxP1 wait time.

In Control Device mode, PERIF is set when a forward frame is received. This helps the software distinguish whether the received byte is part of a forward frame from a Control Device (either from the Control Device under consideration or from another Control Device on the bus) or a backward frame from a Control Gear.

#### 31.6.2 CONTROL GEAR

The Control Gear mode is configured with the following settings:

- MODE<3:0> = 1001

- TXEN = 1

- RXEN = 1

- UxP1 = Backward frames are held for transmission this number of half-bit periods after the completion of a forward frame.

- UxP2 = Forward/backward frame threshold delimiter. Idle periods more than this number of half-bit periods are detected as forward frames.

- UxBRGH:L = Value to achieve 1200 baud rate

- TXPOL = appropriate polarity for interface circuit

- RXPOL = same as TXPOL

- STP = 10 for two Stop bits

- RxyPPS = TX pin output code

- TX pin TRIS control = 0

- RXPPS = RX pin selection code

- RX pin TRIS control = 1

- Input pin ANSEL bit = 0

- ON = 1

The UART starts listening for a forward frame when the Control Gear mode is entered. Only the frames that follow an Idle period longer than UxP2 half-bit periods are detected as forward frames. Backward frames from other Control Gear are ignored. Only forward frames will be stored in UxRXB. This is necessary because a backward frame can be sent only as a response to a forward frame.

The forward frame is received one byte at a time in the receive FIFO and retrieved by reading the UxRXB register. The end of the forward frame starts a timer to delay the backward frame response by wait time equal to the number of half-bit periods stored in UxP1. The data received in the forward frame is processed by the application software. If the application decides to send a backward frame in response to the forward frame, the value of the backward frame is written to UxTXB. This value is held for transmission in the transmit shift register until the wait time expires and is then transmitted.

If the backward frame data is written to UxTXB after the wait time has expired, it is held in the UxTXB register until the end of the wait time following the next forward frame. The TXMTIF bit is false when the backward frame data is held in the transmit shift register. Receiving a UxRXIF interrupt before the TXMTIF goes true indicates that the backward frame write was too late and another forward frame was received before sending the backward frame. The pending backward frame has to be flushed by setting the TXBE bit, to prevent it from being sent after the next Forward Frame.

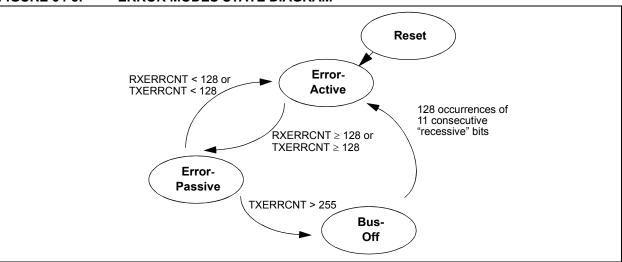

Additionally, there is an Error State Warning flag bit, EWARN, which is set if at least one of the error counters equals or exceeds the error warning limit of 96. EWARN is reset if both error counters are less than the error warning limit.

FIGURE 34-8: ERROR MODES STATE DIAGRAM

#### 37.6.1 DIGITAL FILTER/AVERAGE

The digital filter/average module consists of an accumulator with data feedback options, and control logic to determine when threshold tests need to be applied. The accumulator is a 16-bit wide register which can be accessed through the ADACCH:ADACCL register pair.

Upon each trigger event (the GO bit set or external event trigger), the ADC conversion result is added to the accumulator. If the accumulated result exceeds  $2^{(accumulator\_width)}-1 = 18 = 262143$ , the overflow bit ADAOV in the ADSTAT register is set.

The number of samples to be accumulated is determined by the RPT (A/D Repeat Setting) register. Each time a sample is added to the accumulator, the ADCNT register is incremented. Once RPT samples are accumulated (CNT = RPT), an Accumulator Clear command can be issued by the software by setting the ADACLR bit in the ADCON2 register. Setting the ADACLR bit will also clear the ADAOV (Accumulator overflow) bit in the ADSTAT register, as well as the

ADCNT register. The ADACLR bit is cleared by the hardware when accumulator clearing action is complete.

**Note:** When ADC is operating from FRC, five FRC clock cycles are required to execute the ACC clearing operation.

The ADCRS <2:0> bits in the ADCON2 register control the data shift on the accumulator result, which effectively divides the value in accumulator (ADACCU:ADACCH:ADACCL) register pair. For the Accumulate mode of the digital filter, the shift provides a simple scaling operation. For the Average/Burst Average mode, the shift bits are used to determine the number of logical right shifts to be performed on the accumulated result. For the Low-pass Filter mode, the shift is an integral part of the filter, and determines the cut-off frequency of the filter. Table 37-3 shows the -3 dB cut-off frequency in  $\omega T$  (radians) and the highest signal attenuation obtained by this filter at nyquist frequency ( $\omega T=\pi$ ).

TABLE 37-3: LOW-PASS FILTER -3 dB CUT-OFF FREQUENCY

| ADCRS | ωT (radians) @ -3 dB Frequency | dB @ F <sub>nyquist</sub> =1/(2T) |

|-------|--------------------------------|-----------------------------------|

| 1     | 0.72                           | -9.5                              |

| 2     | 0.284                          | -16.9                             |

| 3     | 0.134                          | -23.5                             |

| 4     | 0.065                          | -29.8                             |

| 5     | 0.032                          | -36.0                             |

| 6     | 0.016                          | -42.0                             |

| 7     | 0.0078                         | -48.1                             |

## 37.6.2 BASIC MODE

Basic mode (ADMD = 000) disables all additional computation features. In this mode, no accumulation occurs but threshold error comparison is performed. Double sampling, Continuous mode, and all CVD features are still available, but no features involving the digital filter/average features are used.

#### 37.6.3 ACCUMULATE MODE

In Accumulate mode (ADMD = 001), after every conversion, the ADC result is added to the ADACC register. The ADACC register is right-shifted by the value of the ADCRS bits in the ADCON2 register. This right-shifted value is copied in to the ADFLT register. The Formatting mode does not affect the right-justification of the ACC value. Upon each sample, CNT is also incremented, incrementing the number of samples accumulated. After each sample and accumulation, the ACC value has a threshold comparison performed on it (see Section 37.6.7 "Threshold Comparison") and the ADTIF interrupt may trigger.

## 37.6.4 AVERAGE MODE

In Average mode (ADMD = 010), the ADACC registers accumulate with each ADC sample, much as in Accumulate mode, and the ADCNT register increments with each sample. The ADFLT register is also updated with the right-shifted value of the ADACC register. The value of the ADCRS bits governs the number of right shifts. However, in Average mode, the threshold comparison is performed upon CNT being greater than or equal to a user-defined RPT value. In this mode when RPT = 2^CNT, then the final accumulated value will be divided by number of samples, allowing for a threshold comparison operation on the average of all gathered samples.

|         | •     |  |

|---------|-------|--|

| Syntax: | SLEEP |  |

|         |       |  |

Operands: None

**SLEEP**

Operation:  $00h \rightarrow WDT$ ,

$0 \to \underline{WD}T \text{ postscaler,}$

**Enter Sleep mode**

$\begin{array}{c}

1 \to \overline{TO}, \\

0 \to \overline{PD}

\end{array}$

Status Affected: TO, PD

Encoding:

0000

0000

0000

0011

Description:

The Power-down Status bit (PD) is

cleared. The Time-out Status bit (TO)

is set. Watchdog Timer and its postscaler are cleared.

The processor is put into Sleep mode

with the oscillator stopped.

Words: 1

Cycles: 1

Q Cycle Activity:

| Q1     | Q2        | Q3      | Q4    |  |  |

|--------|-----------|---------|-------|--|--|

| Decode | No        | Process | Go to |  |  |

|        | operation | Data    | Sleep |  |  |

Example: SLEEP

Before Instruction

<u>TO</u> = ?

After Instruction

$\frac{\overline{\text{TO}}}{\text{PD}} = 0$

† If WDT causes wake-up, this bit is cleared.

| SUBFSR | Subtract Literal from FSR |

|--------|---------------------------|

|--------|---------------------------|

$\label{eq:SUBFSR} \begin{tabular}{lll} Syntax: & SUBFSR f, k \\ Operands: & 0 \le k \le 63 \\ & f \in [\ 0,\ 1,\ 2\ ] \end{tabular}$

$FSR(f) - k \rightarrow FSRf$

Status Affected: None

Encoding: 1110 1001 ffkk kkkk

Description: The 6-bit literal 'k' is subtracted from

the contents of the FSR specified by 'f'.

Words: 1 Cycles: 1

Q Cycle Activity:

Operation:

| Q1     | Q2           | Q3      | Q4          |  |  |

|--------|--------------|---------|-------------|--|--|

| Decode | Read         | Process | Write to    |  |  |

|        | register 'f' | Data    | destination |  |  |

Example: SUBFSR 2, 23h

Before Instruction

FSR2 = 03FFh

After Instruction

FSR2 = 03DCh

ADD W to Indexed **ADDWF** (Indexed Literal Offset mode)

> **ADDWF** [k] {,d}

Operands:  $0 \le k \le 95$

Syntax:

$d \in \left[0,1\right]$

Operation: (W) + ((FSR2) + k)  $\rightarrow$  dest

Status Affected: N, OV, C, DC, Z

Encoding: 0010 01d0 kkkk kkkk

Description: The contents of W are added to the

contents of the register indicated by FSR2, offset by the value 'k'.

If 'd' is '0', the result is stored in W. If 'd'

is '1', the result is stored back in

register 'f' (default).

Words: 1 Cycles: 1

Q Cycle Activity:

Q1 Q2 Q3 Q4 Decode Read 'k' **Process** Write to destination Data

Example: ADDWF [OFST], 0

Before Instruction

17h **OFST** 2Ch FSR2 0A00h Contents 20h

of 0A2Ch After Instruction

37h

Contents 20h of 0A2Ch

Bit Set Indexed **BSF**

(Indexed Literal Offset mode)

Syntax: BSF [k], b Operands:  $0 \le f \le 95$

$0 \le b \le 7$

Operation:  $1 \rightarrow ((FSR2) + k) < b >$

Status Affected: None

Encoding: 1000 bbb0 kkkk kkkk

Description: Bit 'b' of the register indicated by FSR2,

offset by the value 'k', is set.

Words: Cycles: 1

Q Cycle Activity:

Q1 Q2 Q3 Q4 Decode Read **Process** Write to register 'f' Data destination

Example: [FLAG\_OFST], 7

Before Instruction

FLAG\_OFST 0Ah FSR2 0A00h Contents 55h of 0A0Ah

After Instruction

Contents of 0A0Ah D5h

Set Indexed **SETF** (Indexed Literal Offset mode)

Syntax: SETF [k] Operands:  $0 \le k \le 95$

Operation:  $FFh \rightarrow ((FSR2) + k)$

Status Affected: None

Encoding: 0110 1000 kkkk kkkk

Description: The contents of the register indicated

by FSR2, offset by 'k', are set to FFh.

Words: Cycles: 1

Q Cycle Activity:

Q1 Q3 Q4 Ω2 Decode Read 'k' **Process** Write Data register

Example: SETF [OFST]

Before Instruction

**OFST** 2Ch 0A00h FSR2 Contents 00h of 0A2Ch

After Instruction

Contents of 0A2Ch FFh

TABLE 43-1: REGISTER FILE SUMMARY FOR PIC18(L)F25/26K83 DEVICES (CONTINUED)

| Addr             | Name        | Bit 7                                                                         | Bit 6     | Bit 5  | Bit 4                   | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register on page |

|------------------|-------------|-------------------------------------------------------------------------------|-----------|--------|-------------------------|--------|--------|--------|--------|------------------|

| 3980h            | IPR0        | IOCIP                                                                         | CRCIP     | SCANIP | NVMIP                   | CSWIP  | OSFIP  | HLVDIP | SWIP   | 147              |

| 397Fh -<br>397Eh | _           | Unimplemented                                                                 |           |        |                         |        |        |        |        | _                |

| 397Dh            | SCANTRIG    | ı                                                                             | _         | _      | - TSEL                  |        |        |        |        |                  |

| 397Ch            | SCANCON0    | EN                                                                            | TRIGEN    | SGO    | SGO — MREG BURSTMD BUSY |        |        |        |        |                  |

| 397Bh            | SCANHADRU   | _                                                                             | _         |        |                         | HA     | ADR    |        |        | 214              |

| 397Ah            | SCANHADRH   |                                                                               |           |        | HAD                     | )R     |        |        |        | 215              |

| 3979h            | SCANHADRL   |                                                                               |           |        | HAD                     | )R     |        |        |        | 215              |

| 3978h            | SCANLADRU   | _                                                                             | _         |        |                         | LA     | NDR    |        |        | 213              |

| 3977h            | SCANLADRH   |                                                                               | •         |        | LAD                     | R      |        |        |        | 213              |

| 3976h            | SCANLADRL   |                                                                               |           |        | LAD                     | R      |        |        |        | 214              |

| 3975h -<br>396Ah | _           |                                                                               |           |        | Unimplei                | mented |        |        |        | _                |

| 3969h            | CRCCON1     |                                                                               | DL        | EN     |                         |        | Р      | LEN    |        | 208              |

| 3968h            | CRCCON0     | EN                                                                            | CRCGO     | BUSY   | ACCM                    | _      | _      | SHIFTM | FULL   | 208              |

| 3967h            | CRCXORH     | X15                                                                           | X14       | X13    | X12                     | X11    | X10    | X9     | X8     | 211              |

| 3966h            | CRCXORL     | X7                                                                            | X6        | X5     | X4                      | Х3     | X2     | X1     | _      | 211              |

| 3965h            | CRCSHIFTH   | SHFT15                                                                        | SHFT14    | SHFT13 | SHFT12                  | SHFT11 | SHFT10 | SHFT9  | SHFT8  | 210              |

| 3964h            | CRCSHIFTL   | SHFT7                                                                         | SHFT6     | SHFT5  | SHFT4                   | SHFT3  | SHFT2  | SHFT1  | SHFT0  | 210              |

| 3963h            | CRCACCH     | ACC15                                                                         | ACC14     | ACC13  | ACC12                   | ACC11  | ACC10  | ACC9   | ACC8   | 209              |

| 3962h            | CRCACCL     | ACC7                                                                          | ACC6      | ACC5   | ACC4                    | ACC3   | ACC2   | ACC1   | ACC0   | 210              |

| 3961h            | CRCDATH     | DATA15                                                                        | DATA14    | DATA13 | DATA12                  | DATA11 | DATA10 | DATA9  | DATA8  | 209              |

| 3960h            | CRCDATL     | DATA7                                                                         | DATA6     | DATA5  | DATA4                   | DATA3  | DATA2  | DATA1  | DATA0  | 209              |

| 395Fh            | WDTTMR      |                                                                               |           | WDTTMR |                         | ·      | STATE  | PS     | SCNT   | 175              |

| 395Eh            | WDTPSH      |                                                                               |           |        | PSC                     | NT     |        | l      |        | 174              |

| 395Dh            | WDTPSL      |                                                                               |           |        | PSC                     | NT     |        |        |        | 174              |

| 395Ch            | WDTCON1     | 1                                                                             |           | WDTCS  |                         | _      |        | WINDOW |        | 173              |

| 395Bh            | WDTCON0     | 1                                                                             | _         |        |                         | WDTPS  |        |        | SEN    | 172              |

| 395Ah -<br>38A0h | _           |                                                                               |           |        | Unimple                 | mented |        |        |        | _                |

| 389Fh            | IVTADU      |                                                                               |           |        | ΑI                      | )      |        |        |        | 158              |

| 389Eh            | IVTADH      |                                                                               |           |        | ΑI                      | )      |        |        |        | 158              |

| 389Dh            | IVTADL      |                                                                               |           |        | ΑI                      | )      |        |        |        | 158              |

| 389Ch -<br>3891h | _           |                                                                               |           |        | Unimplei                | mented |        |        |        | _                |

| 3890h            | PRODH_SHAD  |                                                                               |           |        | PRO                     | DH     |        |        |        | 115              |

| 388Fh            | PRODL_SHAD  |                                                                               |           |        | PRO                     | DL     |        |        |        | 115              |

| 388Eh            | FSR2H_SHAD  | _                                                                             | _         |        |                         | FS     | R2H    |        |        | 115              |

| 388Dh            | FSR2L_SHAD  |                                                                               |           |        | FSR                     | 2L     |        |        |        | 115              |

| 388Ch            | FSR1H_SHAD  | _                                                                             | _         |        |                         | FS     | R1H    |        |        | 115              |

| 388Bh            | FSR1L_SHAD  |                                                                               |           |        | FSR                     | 1L     |        |        |        | 115              |

| 388Ah            | FSR0H_SHAD  | _                                                                             | — — FSR0H |        |                         |        |        |        |        | 115              |

| 3889h            | FSR0L_SHAD  | FSR0L                                                                         |           |        |                         |        |        |        | 115    |                  |

| 3888h            | PCLATU_SHAD | PCU                                                                           |           |        |                         |        |        |        | 115    |                  |

| 3887h            | PCLATH_SHAD | PCH                                                                           |           |        |                         |        |        |        | 115    |                  |

| 3886h            | BSR_SHAD    | _                                                                             | _         |        |                         | В      | SR     |        |        | 115              |

| 3885h            | WREG_SHAD   | WREG                                                                          |           |        |                         |        |        | 115    |        |                  |

| 3884h            | STATUS_SHAD | _                                                                             | TO        | PD     | N                       | OV     | Z      | DC     | С      | 115              |

| 3883h            | SHADCON     | _                                                                             | _         | _      | _                       | _      | _      | _      | SHADLO | 159              |

| 3882h            | BSR_CSHAD   | _                                                                             | _         |        |                         |        | SR     |        |        | 47               |

| 3881h            | WREG_CSHAD  |                                                                               | WREG      |        |                         |        |        |        |        |                  |

| Legend:          | _           | x = unknown, u = unchanged. — = unimplemented, g = value depends on condition |           |        |                         |        |        |        |        |                  |

$\textbf{Legend:} \qquad \textbf{x} = \text{unknown, u = unchanged,} \\ \textbf{—} = \text{unimplemented, q = value depends on condition}$

Note 1: Not present in LF devices.

# TABLE 45-3: POWER-DOWN CURRENT (IPD)(1,2)

| PIC18LF        | 25/26K83  |                                           |              | Standard Operating Conditions (unless otherwise stated)            |               |                      |       | otherwise stated) |                       |

|----------------|-----------|-------------------------------------------|--------------|--------------------------------------------------------------------|---------------|----------------------|-------|-------------------|-----------------------|

| PIC18F25/26K83 |           |                                           |              | Standard Operating Conditions (unless otherwise stated) VREGPM = 1 |               |                      |       |                   | otherwise stated)     |

| Param.<br>No.  | Symbol    | Device Characteristics                    | Min.         | Typ.†                                                              | Max.<br>+85°C | Max.<br>+125°C       | Units | VDD               | Conditions            |

| D200           | IPD       | IPD Base                                  | _            | 0.07                                                               | 2             | 6                    | μΑ    | 3.00              |                       |

| D200           | IPD       | IPD Base                                  | _            | 0.4                                                                | 2.5           | 8                    | /HA_  | 3.0V              |                       |

| D200A          |           |                                           | -            | 20                                                                 | 37            | 45 <                 | pp.   | 3.04              | VREĞPM = 0            |

| D201           | IPD_WDT   | Low-Frequency Internal Oscillator/<br>WDT | 1            | 0.9                                                                | 2.9           | 9                    | μĀ    | 3.04              |                       |

| D201           | IPD_WDT   | Low-Frequency Internal Oscillator/<br>WDT | _            | 1.1                                                                | 3.3 <         | 9                    | μA    | 3.0V              |                       |

| D202           | IPD_SOSC  | Secondary Oscillator (Sosc)               | _            | 0.6                                                                | /2.8          | )<br> <br> <br> <br> | μA    | 3.0V              | LP mode               |

| D202           | IPD_SOSC  | Secondary Oscillator (Sosc)               | -            | 0.8                                                                | 3.2 -         | 15                   | μA    | 3.0V              | LP mode               |

| D203           | IPD_FVR   | FVR                                       | _            | 37                                                                 | 70            | 75                   | μA    | 3.0V              | FVRCON = 0x81 or 0x84 |

| D203           | IPD_FVR   | FVR                                       |              | 38                                                                 | 70            | 76                   | μΑ    | 3.0V              | FVRCON = 0x81 or 0x84 |

| D204           | IPD_BOR   | Brown-out Reset (BOR)                     | _/^          | 9.4                                                                | 16            | 18                   | μΑ    | 3.0V              |                       |

| D204           | IPD_BOR   | Brown-out Reset (BOR)                     | 7            | 9.4                                                                | 17            | > 19                 | μΑ    | 3.0V              |                       |

| D205           | IPD_LPBOR | Low-Power Brown-out Reset (LPBOR)         | _/           | 0.2                                                                | 3             | 6                    | μΑ    | 3.0V              |                       |

| D205           | IPD_LPBOR | Low-Power Brown-out Reset (LPBQR)         |              | 0.5                                                                | √3            | 5                    | μΑ    | 3.0V              |                       |

| D206           | IPD_HLVD  | High/Low Voltage Detect (HLVD)            | 7            | 9.5                                                                | 16            | 19                   | μΑ    | 3.0V              |                       |

| D206           | IPD_HLVD  | High/Low Voltage Detect (HLVD)            | /            | 9.7                                                                | 17            | 20                   | μΑ    | 3.0V              |                       |

| D207           | IPD_ADCA  | ADC - Active                              | _\           | <b>A</b> 00                                                        | _             | _                    | μΑ    | 3.0V              | ADC is converting (4) |

| D207           | IPD_ADCA  | ADC - Active                              | 7            | 400                                                                | _             | _                    | μΑ    | 3.0V              | ADC is converting (4) |

| D208           | IPD_CMP   | Comparator                                | $\checkmark$ | 33                                                                 | 50            | 55                   | μΑ    | 3.0V              |                       |

| D208           | IPD_CMP   | Comparator                                | _            | 30                                                                 | 50            | 60                   | μΑ    | 3.0V              |                       |

† Data in "Typ." column is at 3.6V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base IDD and the additional current consumed when this peripheral is enabled. The peripheral \( \Delta \) current can be determined by subtracting the base IDD or IPD current from this limit. Max. values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode with all I/O pins in high-impedance state and tied to Vss.

3: All peripheral currents listed are on a per-peripheral basis if more than one instance of a peripheral is available.

4: ADC clock source is FRC.

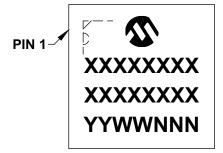

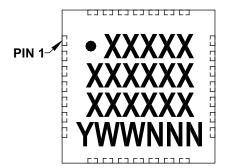

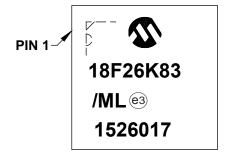

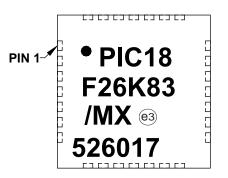

## **Package Marking Information (Continued)**

28-Lead QFN (6x6 mm)

28-Lead UQFN (6x6x0.5 mm)

Example

Example

**Legend:** XX...X Customer-specific information or Microchip part number

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

Pb-free JEDEC® designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (@3)

can be found on the outer packaging for this package.

**Note**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.