#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                  |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 2K x 8                                                                      |

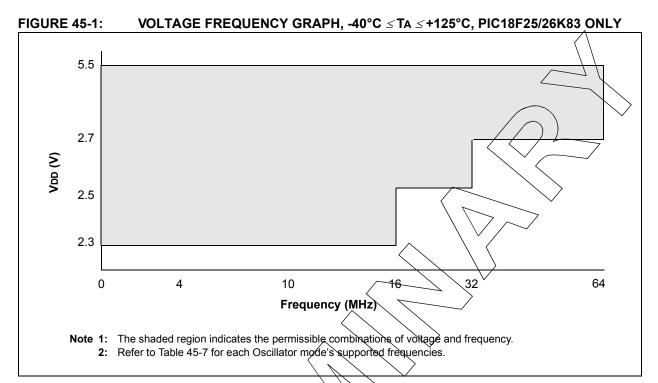

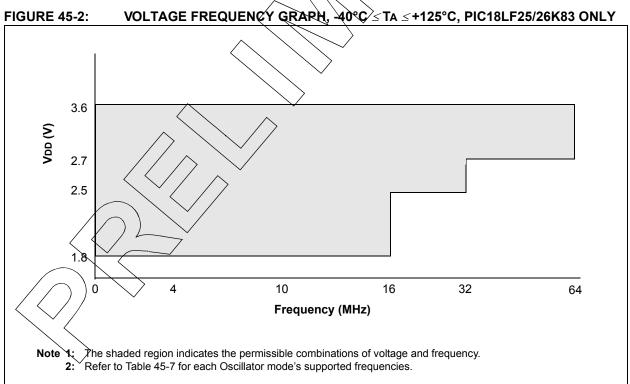

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

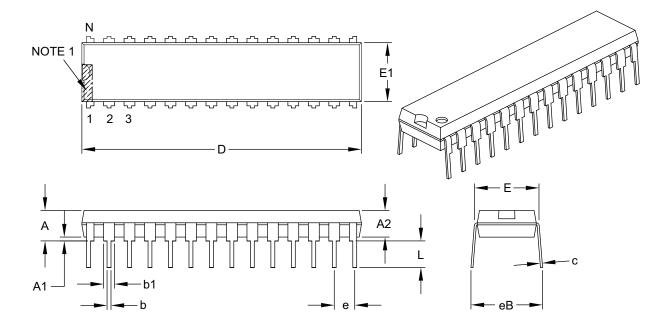

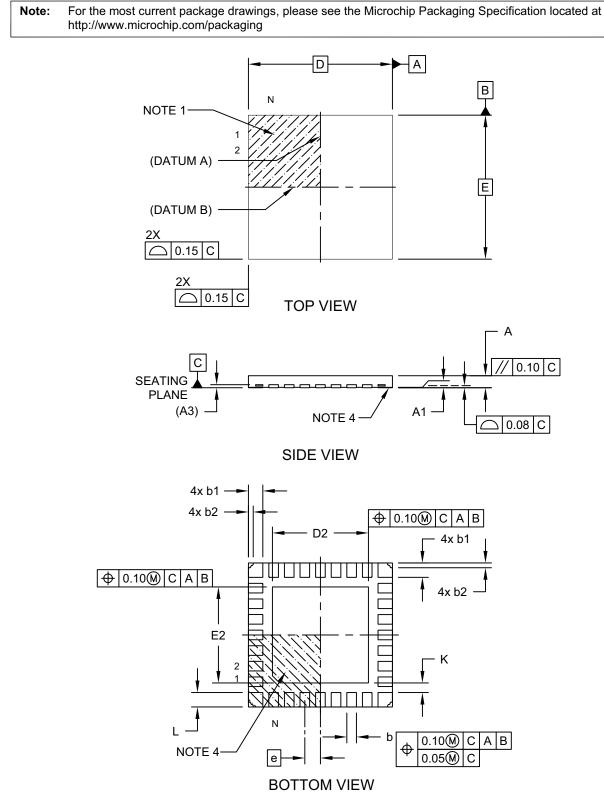

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f25k83t-i-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 3-2: SUMMARY OF REGISTERS ASSOCIATED WITH CPU

| Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2   | Bit 1   | Bit 0    | Register on page |

|--------|-------|-------|-------|-------|-------|---------|---------|----------|------------------|

| ISRPR  | —     | _     | _     | _     | -     | ISRPR2  | ISRPR1  | ISRPR0   | 20               |

| MAINPR | —     | _     | _     | _     | _     | MAINPR2 | MAINPR1 | MAINPR0  | 20               |

| DMA1PR | —     | _     | _     | _     | _     | DMA1PR2 | DMA1PR1 | DMA1PR0  | 20               |

| DMA2PR | —     | _     | _     | _     | _     | DMA2PR2 | DMA2PR1 | DMA2PR0  | 21               |

| SCANPR | —     | _     | _     | _     | _     | SCANPR2 | SCANPR1 | SCANPR0  | 21               |

| PRLOCK | _     | _     | _     | _     | —     | _       | _       | PRLOCKED | 21               |

**Legend:** — = Unimplemented location, read as '0'.

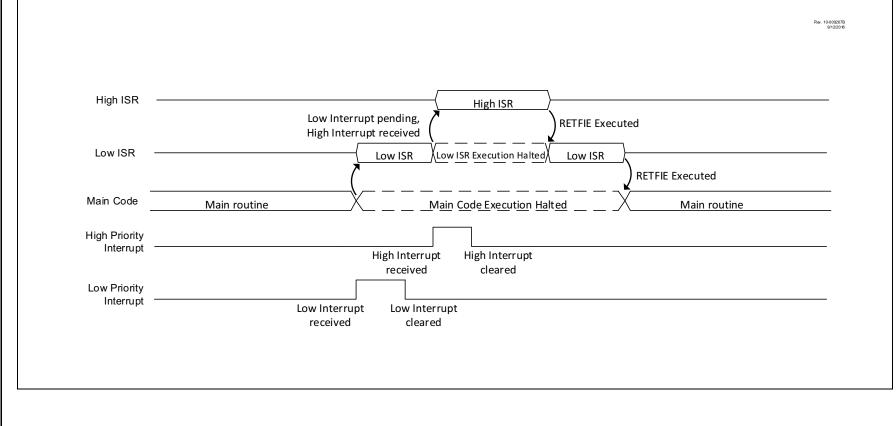

#### 9.4.3 PREEMPTING LOW PRIORITY INTERRUPTS

Low-priority interrupts can be preempted by high priority interrupts. While in the low priority ISR, if a high-priority interrupt arrives, the high priority interrupt request is generated and the low priority ISR is suspended, while the high priority ISR is executed, see Figure 9-4.

After the high priority ISR is complete and if any other high priority interrupt requests are not active, the execution returns to the preempted low priority ISR.

- **Note 1:** The high priority interrupt flag must be cleared to avoid recursive interrupts.

- 2: If a low-priority ISR was already serviced halfway before moving on to a high priority ISR, then the low priority ISR is completely serviced even if user code clears GIEL.

#### FIGURE 9-4: INTERRUPT EXECUTION: HIGH PRIORITY INTERRUPT PREEMPTING LOW PRIORITY INTERRUPTS

#### 10.1.2 INTERRUPTS DURING DOZE

If an interrupt occurs and the Recover-On-Interrupt bit is clear (ROI = 0) at the time of the interrupt, the Interrupt Service Routine (ISR) continues to execute at the rate selected by DOZE<2:0>. Interrupt latency is extended by the DOZE<2:0> ratio.

If an interrupt occurs and the ROI bit is set (ROI = 1) at the time of the interrupt, the DOZEN bit is cleared and the CPU executes at full speed. The prefetched instruction is executed and then the interrupt vector sequence is executed. In Figure 10-1, the interrupt occurs during the 2<sup>nd</sup> instruction cycle of the Doze period, and immediately brings the CPU out of Doze. If the Doze-On-Exit (DOE) bit is set (DOE = 1) when the RETFIE operation is executed, DOZEN is set, and the CPU executes at the reduced rate based on the DOZE<2:0> ratio.

#### EXAMPLE 10-1: DOZE SOFTWARE EXAMPLE

```

//Mainline operation

bool somethingToDo = FALSE:

void main()

initializeSystem();

// DOZE = 64:1 (for example)

// ROI = 1;

GIE = 1; // enable interrupts

while (1)

{

// If ADC completed, process data

if (somethingToDo)

{

doSomething();

DOZEN = 1; // resume low-power

}

}

// Data interrupt handler

void interrupt()

// DOZEN = 0 because ROI = 1

if (ADIF)

{

somethingToDo = TRUE;

DOE = 0; // make main() go fast

ADIF = 0;

// else check other interrupts...

if (TMROIF)

{

timerTick++;

DOE = 1; // make main() go slow

TMROIF = 0;

}

```

#### 10.2 Sleep Mode

Sleep mode is entered by executing the SLEEP instruction, while the Idle Enable (IDLEN) bit of the CPUDOZE register is clear (IDLEN = 0).

Upon entering Sleep mode, the following conditions exist:

- 1. WDT will be cleared but keeps running if enabled for operation during Sleep

- 2. The PD bit of the STATUS register is cleared (Register 4-2)

- 3. The TO bit of the STATUS register is set (Register 4-2)

- 4. The CPU clock is disabled

- 5. LFINTOSC, SOSC, HFINTOSC and ADCRC are unaffected and peripherals using them may continue operation in Sleep.

- I/O ports maintain the status they had before Sleep was executed (driving high, low, or highimpedance)

- 7. Resets other than WDT are not affected by Sleep mode

Refer to individual chapters for more details on peripheral operation during Sleep.

To minimize current consumption, the following conditions should be considered:

- I/O pins should not be floating

- External circuitry sinking current from I/O pins

- Internal circuitry sourcing current from I/O pins

- Current draw from pins with internal weak pull-ups

- Modules using any oscillator

I/O pins that are high-impedance inputs should be pulled to VDD or Vss externally to avoid switching currents caused by floating inputs.

Examples of internal circuitry that might be sourcing current include modules such as the DAC and FVR modules. See Section 38.0 "5-Bit Digital-to-Analog Converter (DAC) Module" and Section 35.0 "Fixed Voltage Reference (FVR)" for more information on these modules.

#### 12.0 8x8 HARDWARE MULTIPLIER

#### 12.1 Introduction

All PIC18 devices include an 8x8 hardware multiplier as part of the ALU. The multiplier performs an unsigned operation and yields a 16-bit result that is stored in the product register pair, PRODH:PRODL. The multiplier's operation does not affect any flags in the STATUS register.

Making multiplication a hardware operation allows it to be completed in a single instruction cycle. This has the advantages of higher computational throughput and reduced code size for multiplication algorithms and allows the PIC18 devices to be used in many applications previously reserved for digital signal processors. A comparison of various hardware and software multiply operations, along with the savings in memory and execution time, is shown in Table 12-1.

#### 12.2 Operation

Example 12-1 shows the instruction sequence for an 8x8 unsigned multiplication. Only one instruction is required when one of the arguments is already loaded in the WREG register.

Example 12-2 shows the sequence to do an 8x8 signed multiplication. To account for the sign bits of the arguments, each argument's Most Significant bit (MSb) is tested and the appropriate subtractions are done.

#### EXAMPLE 12-1: 8x8 UNSIGNED MULTIPLY ROUTINE

| MOVF  | ARG1, | W | ; |       |     |       |    |

|-------|-------|---|---|-------|-----|-------|----|

| MULWF | ARG2  |   | ; | ARG1  | *   | ARG2  | -> |

|       |       |   | ; | PRODE | 1:1 | PRODL |    |

|       |       |   |   |       |     |       |    |

### EXAMPLE 12-2: 8x8 SIGNED MULTIPLY

|       |          | 1. | JOHNE          |

|-------|----------|----|----------------|

| MOVF  | ARG1, W  |    |                |

| MULWF | ARG2     | ;  | ARG1 * ARG2 -> |

|       |          | ;  | PRODH:PRODL    |

| BTFSC | ARG2, SB | ;  | Test Sign Bit  |

| SUBWF | PRODH, F | ;  | PRODH = PRODH  |

|       |          | ;  | - ARG1         |

| MOVF  | ARG2, W  |    |                |

| BTFSC | ARG1, SB | ;  | Test Sign Bit  |

| SUBWF | PRODH, F | ;  | PRODH = PRODH  |

|       |          | ;  | - ARG2         |

|       |          |    |                |

|                |                           | Program           | Cycles | Time     |          |          |         |  |

|----------------|---------------------------|-------------------|--------|----------|----------|----------|---------|--|

| Routine        | Multiply Method           | Memory<br>(Words) | (Max)  | @ 64 MHz | @ 40 MHz | @ 10 MHz | @ 4 MHz |  |

| 9v9 unsigned   | Without hardware multiply | 13                | 69     | 4.3 μs   | 6.9 μs   | 27.6 μs  | 69 μs   |  |

| 8x8 unsigned   | Hardware multiply         | 1                 | 1      | 62.5 ns  | 100 ns   | 400 ns   | 1 μs    |  |

| 9v9 signed     | Without hardware multiply | 33                | 91     | 5.7 μs   | 9.1 μs   | 36.4 μs  | 91 μs   |  |

| 8x8 signed     | Hardware multiply         | 6                 | 6      | 375 ns   | 600 ns   | 2.4 μs   | 6 μs    |  |

| 16v16 unsigned | Without hardware multiply | 21                | 242    | 15.1 μs  | 24.2 μs  | 96.8 μs  | 242 μs  |  |

| 16x16 unsigned | Hardware multiply         | 28                | 28     | 1.8 μs   | 2.8 μs   | 11.2 μs  | 28 μs   |  |

| 16x16 signed   | Without hardware multiply | 52                | 254    | 15.9 μs  | 25.4 μs  | 102.6 μs | 254 μs  |  |

|                | Hardware multiply         | 35                | 40     | 2.5 μs   | 4.0 μs   | 16.0 μs  | 40 μs   |  |

#### TABLE 12-1: PERFORMANCE COMPARISON FOR VARIOUS MULTIPLY OPERATIONS

#### 13.1.5 ERASING PROGRAM FLASH MEMORY

The minimum erase block is 64 words (refer to Table 5-4). Only through the use of an external programmer, or through ICSP™ control, can larger blocks of program memory be bulk erased. Word erase in the program memory array is not supported.

For example, when initiating an erase sequence from a microcontroller with erase row size of 64 words, a block of 64 words (128 bytes) of program memory is erased. The Most Significant 16 bits of the TBLPTR<21:6> point to the block being erased. The TBLPTR<5:0> bits are ignored.

The NVMCON1 register commands the erase operation. The REG<1:0> bits must be set to point to the Program Flash Memory. The WREN bit must be set to enable write operations. The FREE bit is set to select an erase operation.

The NVM unlock sequence described in **Section 13.1.4 "NVM Unlock Sequence**" should be used to guard against accidental writes. This is sometimes referred to as a long write.

A long write is necessary for erasing program memory. Instruction execution is halted during the long write cycle. The long write is terminated by the internal programming timer.

#### 13.1.5.1 Program Flash Memory Erase Sequence

The sequence of events for erasing a block of internal program memory is:

- 1. REG bits of the NVMCON1 register point to PFM

- 2. Set the FREE and WREN bits of the NVMCON1 register

- 3. Perform the unlock sequence as described in Section 13.1.4 "NVM Unlock Sequence"

If the PFM address is write-protected, the WR bit will be cleared and the erase operation will not take place, WRERR is signaled in this scenario.

The operation erases the memory row indicated by masking the LSBs of the current TBLPTR.

While erasing PFM, CPU operation is suspended and it resumes when the operation is complete. Upon completion the WR bit is cleared in hardware, the NVMIF is set and an interrupt will occur if the NVMIE bit is also set.

Write latch data is not affected by erase operations and WREN will remain unchanged.

Note 1: If a write or erase operation is terminated by an unexpected event, WRERR bit will be set which the user can check to decide whether a rewrite of the location(s) is needed.

- 2: WRERR is set if WR is written to '1' while TBLPTR points to a write-protected address.

- **3:** WRERR is set if WR is written to '1' while TBLPTR points to an invalid address location (Table 13-1).

## 15.9.6 ABORT TRIGGER, MESSAGE COMPLETE

Г

The AIRQEN needs to be set in order for the DMA to sample Abort Interrupt sources. When an abort interrupt is received the SIRQEN bit is cleared and the AIRQEN bit is cleared to avoid receiving further abort triggers.

| FIGURE 15-10: | ABORT AT THE END OF MESSAGE |

|---------------|-----------------------------|

|               |                             |

|                            | (j)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Instruction<br>Clock       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| EN                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SIRQEN                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| AIRQEN                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Source Hardware<br>Trigger |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Abort Hardware<br>Trigger  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DGO                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DMAxSPTR                   | Ox3EEF         Ox3EF0         Society         Ox3EEF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| DMAxDPTR                   | 0x100         0x101         5         0x109         0x10A         0x100         0x100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DMAxSCNT                   | $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DMAxDCNT                   | $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DMA STATE                  | $ \left( \begin{array}{c} \text{IDLE} \end{array} \right) \left( SR^{(1)} \right) DW^{(2)} \right) SR^{(1)} \left( DW^{(2)} \right) \left( SR^{(1)} \right) DW^{(2)} \left( SR^{(1)} \right) DW^{(2)} \right) OW^{(2)} \left( SR^{(1)} \right) DW^{(2)} \right) OW^{(2)} \left( SR^{(1)} \right) DW^{(2)} \left( SR^{(1)} \right) DW^{(2)} \right) OW^{(2)} \left( SR^{(1)} \right) DW^{(2)} \left( SR^{(1)} \right) $ |

| DMAxSCNTIF _               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DMAxDCNTIF -               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DMAxAIF -                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                            | DMAxSSA 0x3EEF DMAxDSA 0x100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                            | DMAxSSZ 0x2 DMAxDSZ 0xA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Note 1:                    | SR – Source Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2:                         | DW – Destination Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| R/W-0/0          | R/W-0/0                                               | R/W-0/0           | R/W-0/0 | R/W-0/0                            | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |  |

|------------------|-------------------------------------------------------|-------------------|---------|------------------------------------|---------|---------|---------|--|--|--|

| WPUx7            | WPUx6                                                 | WPUx5             | WPUx4   | WPUx3                              | WPUx2   | WPUx1   | WPUx0   |  |  |  |

| bit 7            | ·                                                     |                   |         |                                    |         |         | bit 0   |  |  |  |

|                  |                                                       |                   |         |                                    |         |         |         |  |  |  |

| Legend:          |                                                       |                   |         |                                    |         |         |         |  |  |  |

| R = Readable     | R = Readable bit W = Writable bit                     |                   |         | U = Unimplemented bit, read as '0' |         |         |         |  |  |  |

| '1' = Bit is set |                                                       | '0' = Bit is clea | ared    | x = Bit is unkr                    | nown    |         |         |  |  |  |

| -n/n = Value a   | -n/n = Value at POR and BOR/Value at all other Resets |                   |         |                                    |         |         |         |  |  |  |

#### REGISTER 16-5: WPUx: WEAK PULL-UP REGISTER

bit 7-0

WPUx<7:0>: Weak Pull-up PORTx Control bits

1 = Weak Pull-up enabled

0 = Weak Pull-up disabled

#### TABLE 16-6: WEAK PULL-UP PORT REGISTERS

| Name | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 |

|------|-------|-------|-------|-------|----------------------|-------|-------|-------|

| WPUA | WPUA7 | WPUA6 | WPUA5 | WPUA4 | WPUA3                | WPUA2 | WPUA1 | WPUA0 |

| WPUB | WPUB7 | WPUB6 | WPUB5 | WPUB4 | WPUB3                | WPUB2 | WPUB1 | WPUB0 |

| WPUC | WPUC7 | WPUC6 | WPUC5 | WPUC4 | WPUC3                | WPUC2 | WPUC1 | WPUC0 |

| WPUE | _     | _     | _     | _     | WPUE3 <sup>(1)</sup> | _     | —     | —     |

**Note 1:** If MCLRE = 1, the weak pull-up in RE3 is always enabled; bit WPUE3 is not affected.

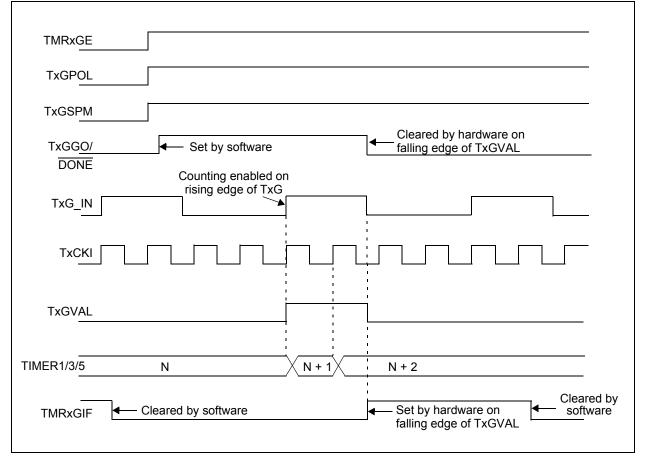

| FIGURE 21-5:   | TIMER1/3/5 GATE TOGGLE MODE                     |

|----------------|-------------------------------------------------|

|                |                                                 |

| TMRxGE         |                                                 |

| TxGPOL         |                                                 |

| TxGTM          |                                                 |

| TxTxG_IN       |                                                 |

| ТхСКІ          |                                                 |

| TxGV <u>AL</u> |                                                 |

| TIMER1/3/5     | N $(N+1)(N+2)(N+3)(N+4)$ $(N+5)(N+6)(N+7)(N+8)$ |

#### FIGURE 21-6: TIMER1/3/5 GATE SINGLE-PULSE MODE

#### 28.8 NCO Control Registers

| EN       —         bit 7         Legend:         R = Readable bit       W =         u = Bit is unchanged       x = 1         '1' = Bit is set       '0' =         bit 7       EN: NCO1 Enable         1 = NCO1 module       0 = NCO1 module         0 = NCO1 module       0 = NCO1 module         bit 6       Unimplemented:         bit 5       OUT: NCO1 Output         Displays the current       1 = NCO1 output st         0 = NCO1 output st       0 = NCO1 output st         bit 3-1       Unimplemented:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                    |                  |                |                  |                  |              |  |  |  |