### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f26k83-i-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

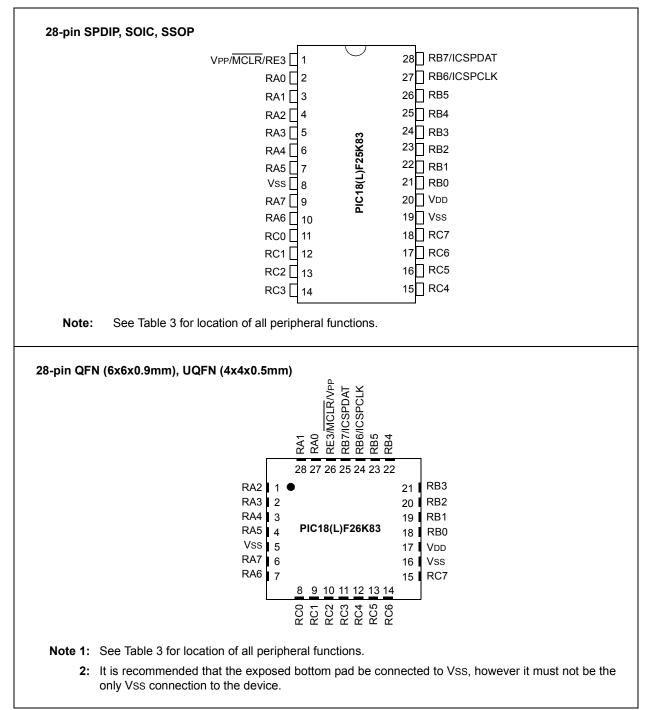

### TABLE 2: PACKAGES

| Device         | SPDIP | SOIC | SSOP | UQFN | QFN |

|----------------|-------|------|------|------|-----|

| PIC18(L)F25K83 | •     | •    | •    | •    | •   |

| PIC18(L)F26K83 | •     | •    | •    | •    | •   |

Note 1: Pin details are subject to change.

### **Pin Diagrams**

### 4.5.5 STATUS REGISTER

The STATUS register, shown in Register 4-2, contains the arithmetic status of the ALU. As with any other SFR, it can be the operand for any instruction.

If the STATUS register is the destination for an instruction that affects the Z, DC, C, OV or N bits, the results of the instruction are not written; instead, the STATUS register is updated according to the instruction performed. Therefore, the result of an instruction with the STATUS register as its destination may be different than intended. As an example, CLRF STATUS will set the Z bit and leave the remaining Status bits unchanged ('0uuu u1uu').

It is recommended that only BCF, BSF, SWAPF, MOVFF, MOVWF and MOVFFL instructions are used to alter the STATUS register, because these instructions do not affect the Z, C, DC, OV or N bits in the STATUS register.

For other instructions that do not affect Status bits, see the instruction set summaries in **Section 42.2 "Extended Instruction Set**" and Table 42-3.

**Note:** The C and DC bits operate as the borrow and digit borrow bits, respectively, in subtraction.

### 4.5.6 CALL SHADOW REGISTER

When CALL, CALLW, RCALL instructions are used, the WREG, BSR and STATUS are automatically saved in hardware and can be accessed using the WREG\_C-SHAD, BSR\_CSHAD and STATUS\_CSHAD registers.

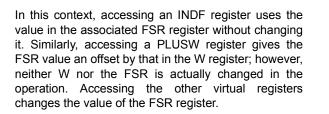

### 4.7.3.2 FSR Registers, POSTINC, POSTDEC, PREINC and PLUSW

In addition to the INDF operand, each FSR register pair also has four additional indirect operands. Like INDF, these are "virtual" registers which cannot be directly read or written. Accessing these registers actually accesses the location to which the associated FSR register pair points, and also performs a specific action on the FSR value. They are:

- POSTDEC: accesses the location to which the FSR points, then automatically decrements the FSR by 1 afterwards

- POSTINC: accesses the location to which the FSR points, then automatically increments the FSR by 1 afterwards

- PREINC: automatically increments the FSR by 1, then uses the location to which the FSR points in the operation

- PLUSW: adds the signed value of the W register (range of -127 to 128) to that of the FSR and uses the location to which the result points in the operation.

### FIGURE 4-6: INDIRECT ADDRESSING

### 5.2 Register Definitions: Configuration Words

| REGISTER     | K 5-1: CONI                                                   | FIGURATION W                                                                  | ORD 1L (3    | 30 0000h)        |                 |                 |       |  |  |  |  |

|--------------|---------------------------------------------------------------|-------------------------------------------------------------------------------|--------------|------------------|-----------------|-----------------|-------|--|--|--|--|

| U-1          | R/W-1                                                         | R/W-1                                                                         | R/W-1        | U-1              | R/W-1           | R/W-1           | R/W-1 |  |  |  |  |

| _            |                                                               | RSTOSC<2:0>                                                                   |              |                  |                 | EXTOSC<2:0>     | >     |  |  |  |  |

| bit 7        | ·                                                             |                                                                               |              |                  |                 |                 | bit ( |  |  |  |  |

| 1            |                                                               |                                                                               |              |                  |                 |                 |       |  |  |  |  |

| Legend:      |                                                               |                                                                               | .,           |                  |                 |                 |       |  |  |  |  |

| R = Readal   | ble bit                                                       | W = Writable I                                                                | oit          | •                | mented bit, rea | id as '1'       |       |  |  |  |  |

| -n = Value f | for blank device                                              | '1' = Bit is set                                                              |              | '0' = Bit is cle | ared            | x = Bit is unki | nown  |  |  |  |  |

|              |                                                               |                                                                               |              |                  |                 |                 |       |  |  |  |  |

| bit 7        | Unimpleme                                                     | ented: Read as '1'                                                            |              |                  |                 |                 |       |  |  |  |  |

| bit 6-4      | RSTOSC<2                                                      | RSTOSC<2:0>: Power-up Default Value for COSC bits                             |              |                  |                 |                 |       |  |  |  |  |

|              | 111 <b>= EXT</b> (                                            | 111 = EXTOSC operating per FEXTOSC<2:0> bits                                  |              |                  |                 |                 |       |  |  |  |  |

|              |                                                               | 110 = HFINTOSC with HFFRQ = 4 MHz and CDIV = 4:1                              |              |                  |                 |                 |       |  |  |  |  |

|              | 101 = LFIN                                                    | 101 = LFINTOSC                                                                |              |                  |                 |                 |       |  |  |  |  |

|              | 100 <b>= SOS</b>                                              | 100 = SOSC                                                                    |              |                  |                 |                 |       |  |  |  |  |

|              | 011 = Rese                                                    | 011 = Reserved                                                                |              |                  |                 |                 |       |  |  |  |  |

|              | 010 = EXTO                                                    | 010 = EXTOSC with 4x PLL, with EXTOSC operating per FEXTOSC<2:0> bits         |              |                  |                 |                 |       |  |  |  |  |

|              | 001 = Rese                                                    | 001 = Reserved                                                                |              |                  |                 |                 |       |  |  |  |  |

|              | 000 <b>= HFIN</b>                                             | 000 = HFINTOSC with HFFRQ = 64 MHz and CDIV = 1:1; resets COSC/NOSC to 3'b110 |              |                  |                 |                 |       |  |  |  |  |

| bit 3        | Unimpleme                                                     | ented: Read as '1'                                                            |              |                  |                 |                 |       |  |  |  |  |

| bit 2-0      | FEXTOSC<2:0>: FEXTOSC External Oscillator Mode Selection bits |                                                                               |              |                  |                 |                 |       |  |  |  |  |

|              | 111 = EC (E                                                   | 111 = EC (External Clock) above 8 MHz; PFM set to high power                  |              |                  |                 |                 |       |  |  |  |  |

|              | · · ·                                                         | 110 = EC (External Clock) for 500 kHz to 8 MHz; PFM set to medium power       |              |                  |                 |                 |       |  |  |  |  |

|              | 101 = EC (E                                                   | 101 = EC (External Clock) below 500 kHz; PFM set to low power                 |              |                  |                 |                 |       |  |  |  |  |

|              | 100 = Oscil                                                   | lator is not enable                                                           | d            |                  |                 |                 |       |  |  |  |  |

|              | 011 = Rese                                                    | erved (do not use)                                                            |              |                  |                 |                 |       |  |  |  |  |

|              |                                                               | crystal oscillator) a                                                         |              |                  |                 |                 |       |  |  |  |  |

|              |                                                               | crystal oscillator) a                                                         |              |                  |                 |                 |       |  |  |  |  |

|              | 000 = LP (c                                                   | rystal oscillator) o                                                          | ptimized for | 32.768 kHz; PF   | FM set to low p | ower            |       |  |  |  |  |

|              |                                                               |                                                                               |              |                  |                 |                 |       |  |  |  |  |

### REGISTER 5-1: CONFIGURATION WORD 1L (30 0000h)

$\ensuremath{\textcircled{}^{\circ}}$  2017 Microchip Technology Inc.

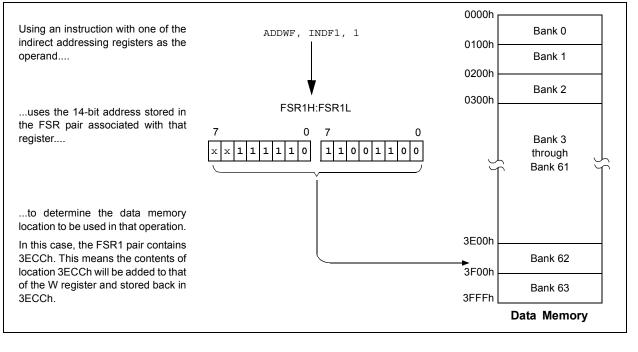

### 6.11 Start-up Sequence

Upon the release of a POR or BOR, the following must occur before the device will begin executing:

- 1. Power-up Timer runs to completion (if enabled).

- 2. Oscillator start-up timer runs to completion (if required for selected oscillator source).

- 3. MCLR must be released (if enabled).

The total time out will vary based on oscillator configuration and Power-up Timer configuration. See Section 7.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for more information.

The Power-up Timer and oscillator start-up timer run independently of MCLR Reset. If MCLR is kept low long enough, the Power-up Timer and oscillator Start-up Timer will expire. Upon bringing MCLR high, the device will begin execution after 10 Fosc cycles (see Figure 6-4). This is useful for testing purposes or to synchronize more than one device operating in parallel.

### FIGURE 6-4: RESET START-UP SEQUENCE

### 12.0 8x8 HARDWARE MULTIPLIER

### 12.1 Introduction

All PIC18 devices include an 8x8 hardware multiplier as part of the ALU. The multiplier performs an unsigned operation and yields a 16-bit result that is stored in the product register pair, PRODH:PRODL. The multiplier's operation does not affect any flags in the STATUS register.

Making multiplication a hardware operation allows it to be completed in a single instruction cycle. This has the advantages of higher computational throughput and reduced code size for multiplication algorithms and allows the PIC18 devices to be used in many applications previously reserved for digital signal processors. A comparison of various hardware and software multiply operations, along with the savings in memory and execution time, is shown in Table 12-1.

### 12.2 Operation

Example 12-1 shows the instruction sequence for an 8x8 unsigned multiplication. Only one instruction is required when one of the arguments is already loaded in the WREG register.

Example 12-2 shows the sequence to do an 8x8 signed multiplication. To account for the sign bits of the arguments, each argument's Most Significant bit (MSb) is tested and the appropriate subtractions are done.

### EXAMPLE 12-1: 8x8 UNSIGNED MULTIPLY ROUTINE

| MOVF  | ARG1, | W | ; |       |     |       |    |

|-------|-------|---|---|-------|-----|-------|----|

| MULWF | ARG2  |   | ; | ARG1  | *   | ARG2  | -> |

|       |       |   | ; | PRODE | 1:1 | PRODL |    |

|       |       |   |   |       |     |       |    |

## EXAMPLE 12-2: 8x8 SIGNED MULTIPLY

|       |          | 1. | JOHNE          |

|-------|----------|----|----------------|

| MOVF  | ARG1, W  |    |                |

| MULWF | ARG2     | ;  | ARG1 * ARG2 -> |

|       |          | ;  | PRODH:PRODL    |

| BTFSC | ARG2, SB | ;  | Test Sign Bit  |

| SUBWF | PRODH, F | ;  | PRODH = PRODH  |

|       |          | ;  | - ARG1         |

| MOVF  | ARG2, W  |    |                |

| BTFSC | ARG1, SB | ;  | Test Sign Bit  |

| SUBWF | PRODH, F | ;  | PRODH = PRODH  |

|       |          | ;  | - ARG2         |

|       |          |    |                |

|                |                           | Program           | Cycles | Time     |          |          |         |  |

|----------------|---------------------------|-------------------|--------|----------|----------|----------|---------|--|

| Routine        | Multiply Method           | Memory<br>(Words) | (Max)  | @ 64 MHz | @ 40 MHz | @ 10 MHz | @ 4 MHz |  |

| 9v9 unsigned   | Without hardware multiply | 13                | 69     | 4.3 μs   | 6.9 μs   | 27.6 μs  | 69 μs   |  |

| 8x8 unsigned   | Hardware multiply         | 1                 | 1      | 62.5 ns  | 100 ns   | 400 ns   | 1 μs    |  |

| 9v9 signed     | Without hardware multiply | 33                | 91     | 5.7 μs   | 9.1 μs   | 36.4 μs  | 91 μs   |  |

| 8x8 signed     | Hardware multiply         | 6                 | 6      | 375 ns   | 600 ns   | 2.4 μs   | 6 μs    |  |

| 16v16 unsigned | Without hardware multiply | 21                | 242    | 15.1 μs  | 24.2 μs  | 96.8 μs  | 242 μs  |  |

| 16x16 unsigned | Hardware multiply         | 28                | 28     | 1.8 μs   | 2.8 μs   | 11.2 μs  | 28 μs   |  |

| 16x16 aignod   | Without hardware multiply | 52                | 254    | 15.9 μs  | 25.4 μs  | 102.6 μs | 254 μs  |  |

| 16x16 signed   | Hardware multiply         | 35                | 40     | 2.5 μs   | 4.0 μs   | 16.0 μs  | 40 μs   |  |

### TABLE 12-1: PERFORMANCE COMPARISON FOR VARIOUS MULTIPLY OPERATIONS

#### WRITING TO PROGRAM FLASH MEMORY MOVLW D'64′ ; number of bytes in erase block MOVWF COUNTER MOVIW BUFFER\_ADDR\_HIGH ; point to buffer MOVWF FSR0H BUFFER\_ADDR\_LOW MOVLW MOVWF FSR0L MOVLW CODE\_ADDR\_UPPER ; Load TBLPTR with the base MOVWF TBLPTRU ; address of the memory block MOVLW CODE\_ADDR\_HIGH MOVWF TBLPTRH CODE\_ADDR\_LOW MOVLW MOVWF TBLPTRL READ\_BLOCK TBLRD\*+ ; read into TABLAT, and inc TABLAT, W MOVF ; get data MOVWF POSTINCO ; store data DECFSZ COUNTER ; done? READ\_BLOCK BRA ; repeat MODIFY WORD MOVLW BUFFER\_ADDR\_HIGH ; point to buffer MOVWF FSR0H MOVLW BUFFER\_ADDR\_LOW MOVWF FSR0L MOVLW NEW\_DATA\_LOW ; update buffer word MOVWF POSTINC0 MOVLW NEW\_DATA\_HIGH MOVWE INDF0 ERASE BLOCK MOVLW CODE\_ADDR\_UPPER ; load TBLPTR with the base MOVWF TBLPTRU ; address of the memory block MOVLW CODE\_ADDR\_HIGH MOVWE TBLPTRH MOVLW CODE\_ADDR\_LOW MOVWF TBLPTRL BCF NVMCON1, REG0 ; point to Program Flash Memory NVMCON1, REG1 ; point to Program Flash Memory BSF NVMCON1, WREN BSF ; enable write to memory NVMCON1, FREE ; enable Erase operation BSF INTCON0, GIE ; disable interrupts BCF MOVLW 55h Required MOVWF NVMCON2 ; write 55h Sequence MOVLW AAh MOVWF NVMCON2 ; write OAAh NVMCON1, WR ; start erase (CPU stall) BSF INTCON0, GIE BSF ; re-enable interrupts TBLRD\*-; dummy read decrement BUFFER\_ADDR\_HIGH ; point to buffer MOVLW MOVWF FSR0H MOVLW BUFFER\_ADDR\_LOW MOVWF FSROL WRITE\_BUFFER\_BACK MOVLW BlockSize ; number of bytes in holding register MOVWF COUNTER MOVLW D'64'/BlockSize ; number of write blocks in 64 bytes MOVWF COUNTER2

### EXAMPLE 13-4:

### 20.8 Register Definitions: Timer0 Control

| R/W-0/0          | U-0                                                                                                                                                                                                                                                      | R-0                                                                                                                                                                                                                                                                                  | R/W-0/0        | R/W-0/0         | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------|------------------|------------------|--------------|--|--|

| EN               | —                                                                                                                                                                                                                                                        | OUT                                                                                                                                                                                                                                                                                  | MD16           |                 | OUTP             | S<3:0>           |              |  |  |

| bit 7            |                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                      |                |                 |                  |                  | bit          |  |  |

|                  |                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                      |                |                 |                  |                  |              |  |  |

| Legend:          |                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                      |                |                 |                  |                  |              |  |  |

| R = Readable     | bit                                                                                                                                                                                                                                                      | W = Writable                                                                                                                                                                                                                                                                         | bit            | U = Unimpler    | mented bit, read | l as '0'         |              |  |  |

| u = Bit is unch  | nanged                                                                                                                                                                                                                                                   | x = Bit is unkr                                                                                                                                                                                                                                                                      | iown           | -n/n = Value    | at POR and BO    | R/Value at all o | other Resets |  |  |

| '1' = Bit is set |                                                                                                                                                                                                                                                          | '0' = Bit is clea                                                                                                                                                                                                                                                                    | ared           |                 |                  |                  |              |  |  |

| bit 7            |                                                                                                                                                                                                                                                          | able bit<br>ule is enabled a<br>ule is disabled                                                                                                                                                                                                                                      |                |                 | de               |                  |              |  |  |

| bit 6            | Unimplement                                                                                                                                                                                                                                              | ted: Read as '                                                                                                                                                                                                                                                                       | )'             |                 |                  |                  |              |  |  |

| bit 5            |                                                                                                                                                                                                                                                          | OUT: TMR0 Output bit (read-only)<br>TMR0 output bit                                                                                                                                                                                                                                  |                |                 |                  |                  |              |  |  |

| bit 4            | <b>MD16:</b> TMR0<br>1 = TMR0 is<br>0 = TMR0 is                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                      | I6-Bit Timer S | elect bit       |                  |                  |              |  |  |

| bit 3-0          | OUTPS<3:0><br>1111 = 1:16 F<br>1110 = 1:15 F<br>1101 = 1:14 F<br>1001 = 1:12 F<br>1011 = 1:12 F<br>1001 = 1:10 F<br>1000 = 1:9 Pc<br>0111 = 1:8 Pc<br>0110 = 1:7 Pc<br>0101 = 1:6 Pc<br>0101 = 1:4 Pc<br>0011 = 1:3 Pc<br>0011 = 1:2 Pc<br>0001 = 1:2 Pc | Postscaler<br>Postscaler<br>Postscaler<br>Postscaler<br>Postscaler<br>Postscaler<br>Dostscaler<br>Dostscaler<br>Dostscaler<br>Dostscaler<br>Dostscaler<br>Dostscaler<br>Dostscaler<br>Dostscaler<br>Dostscaler<br>Dostscaler<br>Dostscaler<br>Dostscaler<br>Dostscaler<br>Dostscaler | Postscaler (I  | Divider) Select | bits             |                  |              |  |  |

### REGISTER 20-1: T0CON0: TIMER0 CONTROL REGISTER 0

# PIC18(L)F25/26K83

### REGISTER 20-2: T0CON1: TIMER0 CONTROL REGISTER 1

| Lanandı |         |         |         |         |         |         |         |

|---------|---------|---------|---------|---------|---------|---------|---------|

| bit 7   |         |         |         |         |         |         | bit 0   |

|         | CS<2:0> |         | ASYNC   |         | CKPS    | <3:0>   |         |

| R/W-0/0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-5 | CS<2:0>:Timer0 Clock Source Select bits<br>111 = CLC1<br>110 = SOSC<br>101 = MFINTOSC (500 kHz)<br>100 = LFINTOSC<br>011 = HFINTOSC<br>010 = Fosc/4<br>001 = Pin selected by T0CKIPPS (Inverted)<br>000 = Pin selected by T0CKIPPS (Non-inverted)                                                 |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | <ul> <li>ASYNC: TMR0 Input Asynchronization Enable bit</li> <li>1 = The input to the TMR0 counter is not synchronized to system clocks</li> <li>0 = The input to the TMR0 counter is synchronized to Fosc/4</li> </ul>                                                                            |

| bit 3-0 | CKPS<3:0>: Prescaler Rate Select bit<br>1111 = 1:32768<br>1110 = 1:16384<br>1101 = 1:8192<br>1100 = 1:4096<br>1011 = 1:2048<br>1010 = 1:1024<br>1001 = 1:512<br>1000 = 1:256<br>0111 = 1:128<br>0110 = 1:64<br>0101 = 1:32<br>0100 = 1:16<br>0011 = 1:8<br>0010 = 1:4<br>0001 = 1:2<br>0000 = 1:1 |

### 22.0 TIMER2/4/6 MODULE

The Timer2/4/6 modules are 8-bit timers that can operate as free-running period counters or in conjunction with external signals that control start, run, freeze, and reset operation in One-Shot and Monostable modes of operation. Sophisticated waveform control such as pulse density modulation are possible by combining the operation of these timers with other internal peripherals such as the comparators and CCP modules. Features of the timer include:

- 8-bit timer register

- 8-bit period register

- · Selectable external hardware timer resets

- Programmable prescaler (1:1 to 1:128)

- Programmable postscaler (1:1 to 1:16)

- Selectable synchronous/asynchronous operation

- · Alternate clock sources

- Interrupt on period

- Three modes of operation:

- Free Running Period

- One-Shot

- Monostable

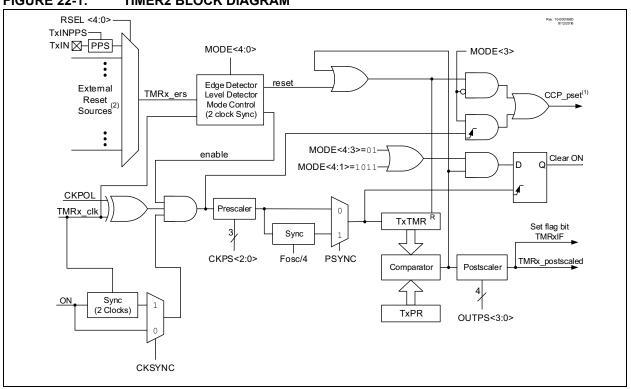

See Figure 22-1 for a block diagram of Timer2. See Figure 22-2 for the clock source block diagram.

**Note:** Three identical Timer2 modules are implemented on this device. The timers are named Timer2, Timer4, and Timer6. All references to Timer2 apply as well to Timer4 and Timer6. All references to T2PR apply as well to T4PR and T6PR.

### FIGURE 22-1: TIMER2 BLOCK DIAGRAM

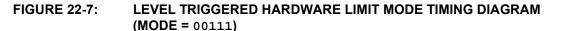

## 22.5.4 LEVEL-TRIGGERED HARDWARE LIMIT MODE

In the level triggered Hardware Limit Timer modes the counter is reset by high or low levels of the external signal TMR2\_ers, as shown in Figure 22-7. Selecting MODE<4:0> = 00110 will cause the timer to reset on a low level external signal. Selecting MODE<4:0> = 00111 will cause the timer to reset on a high level external signal. In the example, the counter is reset while TMR2\_ers = 1. ON is controlled by BSF and BCF instructions. When ON=0 the external signal is ignored.

When the CCP uses the timer as the PWM time base then the PWM output will be set high when the timer starts counting and then set low only when the timer count matches the CCPRx value. The timer is reset when either the timer count matches the T2PR value or two clock periods after the external Reset signal goes true and stays true.

The timer starts counting, and the PWM output is set high, on either the clock following the T2PR match or two clocks after the external Reset signal relinquishes the Reset. The PWM output will remain high until the timer counts up to match the CCPRx pulse width value. If the external Reset signal goes true while the PWM output is high then the PWM output will remain high until the Reset signal is released allowing the timer to count up to match the CCPRx value.

|                              | Re: 10.0001965<br>9122018                                                                                                                                                              |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODE                         | 0b00111                                                                                                                                                                                |

| TMRx_clk                     |                                                                                                                                                                                        |

| TxPR                         | 5                                                                                                                                                                                      |

| Instruction <sup>(1)</sup> - | (BSF) (BSF)                                                                                                                                                                            |

| ON                           |                                                                                                                                                                                        |

| TMRx_ers                     |                                                                                                                                                                                        |

| TxTMR(                       | $0 \ 1 \ 2 \ 0 \ 1 \ 2 \ 3 \ 4 \ 5 \ 0 \ 0 \ 1 \ 2 \ 3 \ 4 \ 5 \ 0 \ 0 \ 1 \ 2 \ 3 \ 4 \ 5 \ 0 \ 0 \ 0 \ 0 \ 0 \ 0 \ 0 \ 0 \ 0$                                                        |

| TMRx_postscaled              |                                                                                                                                                                                        |

| PWM Duty<br>Cycle            | 3                                                                                                                                                                                      |

| PWM Output                   |                                                                                                                                                                                        |

|                              | I: BSF and BCF represent Bit-Set File and Bit-Clear File instructions executed by the CPU to set or clear the ON bit of TxCON. CPU execution is asynchronous to the timer clock input. |

|                |                                      |                                                           |                                    |                                    |                 | -11              |                |

|----------------|--------------------------------------|-----------------------------------------------------------|------------------------------------|------------------------------------|-----------------|------------------|----------------|

| R/W-0/0        | R/W-0/0                              | R/W-0/0                                                   | R/W-0/0                            | R/W-0/0                            | R/W-0/0         | R/W-0/0          | R/W-0/0        |

| PSYNC          | CKPOL                                | CKSYNC                                                    |                                    |                                    | MODE<4:0>       |                  |                |

| bit 7          | ·                                    |                                                           | •                                  |                                    |                 |                  | bit (          |

| Legend:        |                                      |                                                           |                                    |                                    |                 |                  |                |

| R = Reada      | ble bit                              | W = Writable                                              | hit                                | II – Unimpler                      | nented bit, rea | d as '0'         |                |

|                |                                      | x = Bit is unkr                                           |                                    |                                    |                 | R/Value at all   | othor Docote   |

| u = Bit is u   | •                                    |                                                           |                                    |                                    | at FOR and BC   | r/value at all   |                |

| '1' = Bit is s | sel                                  | '0' = Bit is cle                                          | areo                               |                                    |                 |                  |                |

| bit 7          | 1 = TxTMR<br>0 = TxTMR               | erx Prescaler S<br>Prescaler Outp<br>Prescaler Outp       | ut is synchroni<br>ut is not synch | ized to Fosc/4<br>ironized to Foso |                 |                  |                |

| bit 6          | 1 = Falling e                        | erx Clock Polar<br>edge of input clo<br>dge of input clo  | ock clocks time                    | er/prescaler                       |                 |                  |                |

| bit 5          | 1 = ON regis                         | merx Clock Syr<br>ster bit is synch<br>ster bit is not sy | ronized to T27                     | FMR_clk input                      | out             |                  |                |

| bit 4-0        |                                      | : Timerx Contro<br>-1 for all operation                   |                                    | tion bits <sup>(6, 7)</sup>        |                 |                  |                |

|                | Setting this bit er                  |                                                           | •                                  |                                    | data value.     |                  |                |

|                | When this bit is '                   | -                                                         | •                                  | •                                  |                 |                  |                |

|                | CKPOL should r                       | •                                                         |                                    |                                    |                 |                  |                |

| 4:             | Setting this bit er                  | nsures glitch-fre                                         | e operation w                      | hen the ON is e                    | enabled or disa | bled.            |                |

| 5:             | When this bit is set.                | set then the time                                         | er operation w                     | ill be delayed by                  | y two TxTMR ir  | nput clocks afte | r the ON bit i |

| 6:             | Unless otherwise affecting the value |                                                           | modes start u                      | upon ON = 1 a                      | nd stop upon    | ON = 0 (stops    | occur withou   |

| 7.             | When TxTMR =                         | TxPR the next                                             | clock clears T                     | xTMR regardle                      | ess of the oner | ating mode       |                |

### **REGISTER 22-6:** TxHLT: TIMERX HARDWARE LIMIT CONTROL REGISTER

7: When TxTMR = TxPR, the next clock clears TxTMR, regardless of the operating mode.

# PIC18(L)F25/26K83

| Name      | Bit 7      | Bit 6  | Bit 5   | Bit 4  | Bit 3   | Bit 2            | Bit 1    | Bit 0  | Register<br>on page |

|-----------|------------|--------|---------|--------|---------|------------------|----------|--------|---------------------|

| I2CxBTO   | —          |        | _       |        | —       |                  | BTO<2:0> |        | 567                 |

| I2CxCLK   | _          | _      | —       | _      | —       | CLK<2:0>         |          |        | 566                 |

| I2CxPIE   | CNTIE      | ACKTIE | —       | WRIE   | ADRIE   | PCIE             | RSCIE    | SCIE   | 573                 |

| I2CxPIR   | CNTIF      | ACKTIF | —       | WRIF   | ADRIF   | PCIF             | RSCIF    | SCIF   | 572                 |

| I2CxERR   | _          | BTOIF  | BCLIF   | NACKIF | —       | BTOIE            | BCLIE    | NACKIE | 570                 |

| I2CxSTAT0 | BFRE       | SMA    | MMA     | R      | D       | —                | —        | —      | 568                 |

| I2CxSTAT1 | TXWE       | _      | TXBE    | _      | RXRE    | CLRBF            | —        | RXBF   | 569                 |

| I2CxCON0  | EN         | RSEN   | S       | CSTR   | MDR     | MODE<2:0>        |          |        | 562                 |

| I2CxCON1  | ACKCNT     | ACKDT  | ACKSTAT | ACKT   | —       | RXOV             | TXU      | CSD    | 564                 |

| I2CxCON2  | ACNT       | GCEN   | FME     | ADB    | SDAHT   | <3:2> BFRET<1:0> |          | 565    |                     |

| I2CxADR0  |            |        |         | Al     | DR<7:0> |                  |          |        | 574                 |

| I2CxADR1  |            |        |         | A      | DR<7:1> |                  | 575      |        |                     |

| I2CxADR2  | ADR<7:0>   |        |         |        |         |                  |          | 576    |                     |

| I2CxADR3  | ADR<7:1> — |        |         |        |         |                  |          | 577    |                     |

| I2CxADB0  | ADB<7:0>   |        |         |        |         |                  |          | 578    |                     |

| I2CxADB1  | ADB<7:0>   |        |         |        |         |                  |          |        | 579                 |

| I2CxCNT   | CNT<7:0>   |        |         |        |         |                  |          | 571    |                     |

| I2CxRXB   | RXB<7:0>   |        |         |        |         |                  |          | —      |                     |

| I2CxTXB   | TXB<7:0>   |        |         |        |         |                  |          | —      |                     |

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the  $l^2C$  module.

### EXAMPLE 34-3: TRANSMITTING A CAN MESSAGE USING BANKED METHOD

; Need to transmit Standard Identifier message 123h using TXB0 buffer. ; To successfully transmit, CAN module must be either in Normal or Loopback mode. ; TXBO buffer is not in access bank. And since we want banked method, we need to make sure ; that correct bank is selected. BANKSEL TXB0CON ; One BANKSEL in beginning will make sure that we are ; in correct bank for rest of the buffer access. ; Now load transmit data into TXB0 buffer. MOVLW MY\_DATA\_BYTE1 ; Load first data byte into buffer MOVWF TXB0D0 ; Compiler will automatically set "BANKED" bit ; Load rest of data bytes - up to 8 bytes into TXBO buffer. . . . ; Load message identifier MOVLW 60H ; Load SID2:SID0, EXIDE = 0 MOVWF TXB0SIDL MOVLW 24H ; Load SID10:SID3 MOVWF TXB0SIDH ; No need to load TXB0EIDL:TXB0EIDH, as we are transmitting Standard Identifier Message only. ; Now that all data bytes are loaded, mark it for transmission. MOVLW B'00001000' ; Normal priority; Request transmission MOVWF TXB0CON ; If required, wait for message to get transmitted BTFSC TXB0CON, TXREQ ; Is it transmitted? BRA \$-2 ; No. Continue to wait ... ; Message is transmitted.

# 42.2.5 SPECIAL CONSIDERATIONS WITH MICROCHIP MPLAB<sup>®</sup> IDE TOOLS

The latest versions of Microchip's software tools have been designed to fully support the extended instruction set of the PIC18(L)F25/26K83 family of devices. This includes the MPLAB C18 C compiler, MPASM assembly language and MPLAB Integrated Development Environment (IDE).

When selecting a target device for software development, MPLAB IDE will automatically set default Configuration bits for that device. The default setting for the XINST Configuration bit is '0', disabling the extended instruction set and Indexed Literal Offset Addressing mode. For proper execution of applications developed to take advantage of the extended instruction set, XINST must be set during programming.

To develop software for the extended instruction set, the user must enable support for the instructions and the Indexed Addressing mode in their language tool(s). Depending on the environment being used, this may be done in several ways:

- A menu option, or dialog box within the environment, that allows the user to configure the language tool and its settings for the project

- A command line option

- A directive in the source code

These options vary between different compilers, assemblers and development environments. Users are encouraged to review the documentation accompanying their development systems for the appropriate information.

| Addr             | Name           | Bit 7         | Bit 6             | Bit 5     | Bit 4   | Bit 3        | Bit 2    | Bit 1  | Bit 0  | Register<br>on page |  |

|------------------|----------------|---------------|-------------------|-----------|---------|--------------|----------|--------|--------|---------------------|--|

| 3FCEh            | PORTE          | _             | —                 | _         | _       | RE3          | —        | _      | _      | 252                 |  |

| 3FCDh            | _              |               |                   |           | Unimple | mented       |          |        |        | _                   |  |

| 3FCCh            | PORTC          | RC7           | RC6               | RC5       | RC4     | RC3          | RC2      | RC1    | RC0    | 252                 |  |

| 3FCBh            | PORTB          | RB7           | RB6               | RB5       | RB4     | RB3          | RB2      | RB1    | RB0    | 252                 |  |

| 3FCAh            | PORTA          | RA7           | RA6               | RA5       | RA4     | RA3          | RA2      | RA1    | RA0    | 252                 |  |

| 3FC9h -<br>3FC5h | —              | Unimplemented |                   |           |         |              |          |        | _      |                     |  |

| 3FC4h            | TRISC          | TRISC7        | TRISC6            | TRISC5    | TRISC4  | TRISC3       | TRISC2   | TRISC1 | TRISC0 | 253                 |  |

| 3FC3h            | TRISB          | TRISB7        | TRISB6            | TRISB5    | TRISB4  | TRISB3       | TRISB2   | TRISB1 | TRISB0 | 253                 |  |

| 3FC2h            | TRISA          | TRISA7        | TRISA6            | TRISA5    | TRISA4  | TRISA3       | TRISA2   | TRISA1 | TRISA0 | 253                 |  |

| 3FC1h-<br>3FBDh  | —              |               |                   |           | Unimple | nimplemented |          |        |        |                     |  |

| 3FBCh            | LATC           | LATC7         | LATC6             | LATC5     | LATC4   | LATC3        | LATC2    | LATC1  | LATC0  | 254                 |  |

| 3FBBh            | LATB           | LATB7         | LATB6             | LATB5     | LATB4   | LATB3        | LATB2    | LATB1  | LATB0  | 254                 |  |

| 3FBAh            | LATA           | LATA7         | LATA6             | LATA5     | LATA4   | LATA3        | LATA2    | LATA1  | LATA0  | 254                 |  |

| 3FB9h            | T0CON1         |               | CS<2:0>           | •         | ASYNC   |              | CKPS     | 8<3:0> |        | 287                 |  |

| 3FB8h            | T0CON0         | EN            |                   | OUT       | MD16    |              | 286      |        |        |                     |  |

| 3FB7h            | TMR0H          |               |                   |           | TMF     | ROH          | 288      |        |        |                     |  |

| 3FB6h            | TMR0L          |               | TMR0L             |           |         |              |          |        | 288    |                     |  |

| 3FB5h            | T1CLK          |               | CS                |           |         |              |          |        | 300    |                     |  |

| 3FB4h            | T1GATE         |               |                   |           | GS      | SS           |          |        |        | 301                 |  |

| 3FB3h            | T1GCON         | GE            | GPOL              | GTM       | GSPM    | GGO          | GVAL     | _      | _      | 299                 |  |

| 3FB2h            | T1CON          | _             |                   | CKP       | S<1:0>  | _            | SYNC     | RD16   | ON     | 323                 |  |

| 3FB1h            | TMR1H          |               |                   |           | TMF     | R1H          |          |        |        | 302                 |  |

| 3FB0h            | TMR1L          | TMRIL         |                   |           |         |              |          |        | 302    |                     |  |

| 3FAFh            | T2RST          | _             | _                 | _         |         |              | RSEL     |        |        | 321                 |  |

| 3FAEh            | T2CLK          | _             |                   | _         |         |              |          | S      |        | 300                 |  |

| 3FADh            | T2HLT          | PSYNC         | CKPOL             | CKSYNC    |         |              | MODE     | -      |        | 324                 |  |

| 3FACh            | T2CON          | ON            |                   | CKPS      |         |              | 298      |        |        |                     |  |

| 3FABh            | T2PR           |               |                   |           | PF      | 1            | 322      |        |        |                     |  |

| 3FAAh            | T2TMR          |               | PR2<br>TMR2       |           |         |              |          |        | 322    |                     |  |

| 3FA9h            | T3CLK          |               |                   |           |         |              |          |        |        | 300                 |  |

| 3FA8h            | T3GATE         |               |                   | CS<br>GSS |         |              |          |        |        | 301                 |  |

| 3FA7h            | T3GCON         | GE            | GPOL              | GTM       | GSPM    | GGO          | GVAL     | _      | _      | 299                 |  |

| 3FA6h            | T3CON          |               |                   |           | KPS     |              | NOT_SYNC | RD16   | ON     | 323                 |  |

|                  | TMR3H          |               |                   | U U       |         | <br>R3H      |          | 1,010  |        | 302                 |  |

| 3FA4h            | TMR3L          |               |                   |           | TMF     |              |          |        |        | 302                 |  |

| 3FA3h            | T4RST          | _             |                   | _         |         |              | RSEL     |        |        | 302                 |  |

| 3FA2h            | T4RST<br>T4CLK |               |                   |           |         |              |          | s      |        | 321                 |  |

| 3FA2II<br>3FA1h  | T4ULK          | PSYNC         | CKPOL             | CKSYNC    | _       |              | MODE     |        |        | 320                 |  |

| 3FA0h            | T4CON          | +             | CREOL             |           |         |              |          | тре    |        | 324                 |  |

| 3F9Fh            | T4CON<br>T4PR  | ON CKPS OUTPS |                   |           |         |              |          |        | 323    |                     |  |

|                  | T4FR<br>T4TMR  | PR4 TMR4      |                   |           |         |              |          |        | 322    |                     |  |

| 3F9Eh            |                |               |                   |           | C       |              |          |        |        | 322                 |  |

| 3F9Dh            | T5CLK          |               |                   |           |         |              |          |        |        |                     |  |

| 3F9Ch            | T5GATE         | 05            |                   | OTM       | GS      | 1            | 0)///    |        |        | 301                 |  |

| 3F9Bh            | T5GCON         | GE            | GPOL              | GTM       | GSPM    | GGO          | GVAL     | -      | -      | 299                 |  |

| 3F9Ah            | T5CON          | -             | —                 | C         | KPS     | -            | NOT_SYNC | RD16   | ON     | 323                 |  |

| 3F99h            | TMR5H          |               |                   |           | TMF     |              |          |        |        | 302                 |  |

| 3F98h            | TMR5L          | TMR5L         |                   |           |         |              |          | 302    |        |                     |  |

| 3F97h            | T6RST          | _             | <br>d, = unimplem |           |         |              | RSEL     |        |        | 321                 |  |

**Legend:** x = unknown, u = unchanged, — = unimplemented, q = value depends on condition

Note 1: Not present in LF devices.

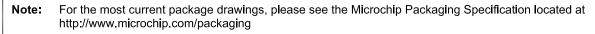

### 28-Lead Plastic Quad Flat, No Lead Package (ML) - 6x6 mm Body [QFN] With 0.55 mm Terminal Length

Microchip Technology Drawing C04-105C Sheet 1 of 2

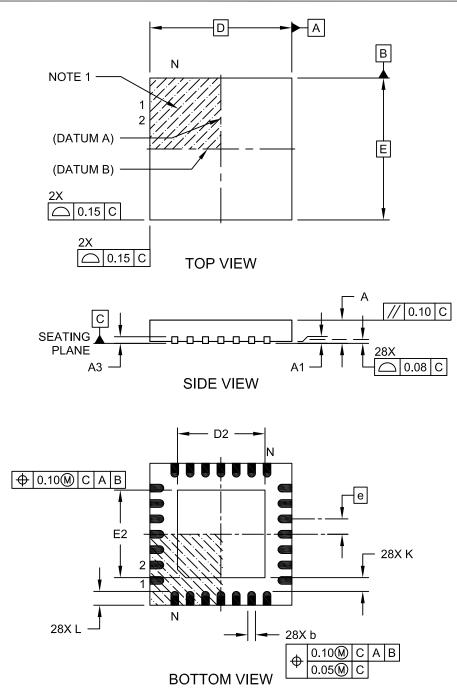

### 28-Lead Plastic Quad Flat, No Lead Package (MX) - 6x6 mm Body [UQFN] With 0.60mm Contact Length And Corner Anchors

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

### RECOMMENDED LAND PATTERN

|                            | MILLIMETERS |      |      |      |

|----------------------------|-------------|------|------|------|

| Dimensio                   | MIN         | NOM  | MAX  |      |

| Contact Pitch              | E 0.65 BSC  |      |      |      |

| Optional Center Pad Width  | W1          |      |      | 4.05 |

| Optional Center Pad Length | T2          |      |      | 4.05 |

| Contact Pad Spacing        | C1          |      | 5.70 |      |

| Contact Pad Spacing        | C2          |      | 5.70 |      |

| Contact Pad Width (X28)    | X1          |      |      | 0.45 |

| Contact Pad Length (X28)   | Y1          |      |      | 1.00 |

| Corner Pad Width (X4)      | X2          |      |      | 0.90 |

| Corner Pad Length (X4)     | Y2          |      |      | 0.90 |

| Distance Between Pads      | G           | 0.20 |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2209B