#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                  |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 4K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f26k83t-i-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.5.2 GENERAL PURPOSE REGISTER FILE

General Purpose RAM is available starting Bank 0 of data memory. GPRs are not initialized by a Power-on Reset and are unchanged on all other Resets.

### 4.5.3 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. SFRs start at the top of data memory (3FFFh) and extend downward to occupy Bank 56 through 63 (3800h to 3FFFh). A list of these registers is given in Table 4-3 to Table 4-10. A bitwise summary of these registers can be found in **Section 43.0 "Register Summary"**.

# 4.5.4 ACCESS BANK

To streamline access for the most commonly used data memory locations, the data memory is configured with an Access Bank, which allows users to access a mapped block of memory without specifying a BSR. The Access Bank consists of the first 96 bytes of memory (00h-5Fh) in Bank 0 and the last 160 bytes of memory (60h-FFh) in Bank 63. The lower half is known as the "Access RAM" and is composed of GPRs. This upper half is also where some of the SFRs of the device are mapped. These two areas are mapped contiguously in the Access Bank and can be addressed linearly by an 8-bit address (Figure 4-5).

The Access Bank is used by core PIC18 instructions that include the Access RAM bit (the 'a' parameter in the instruction). When 'a' is equal to '1', the instruction uses the BSR and the 8-bit address included in the opcode for the data memory address. When 'a' is '0', however, the instruction uses the Access Bank address map; the current value of the BSR is ignored.

Using this "forced" addressing allows the instruction to operate on a data address in a single cycle, without updating the BSR first. For 8-bit addresses of 60h and above, this means that users can evaluate and operate on SFRs more efficiently. The Access RAM below 60h is a good place for data values that the user might need to access rapidly, such as immediate computational results or common program variables. Access RAM also allows for faster and more code efficient and switching of variables.

The mapping of the Access Bank is slightly different when the extended instruction set is enabled (XINST Configuration bit = 1). This is discussed in more detail in Section 4.8.3 "Mapping the Access Bank in Indexed Literal Offset Mode".

| R/W-0/0          | R/W-0/0                     | R/W-0/0           | R/W-0/0        | R/W-0/0      | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|------------------|-----------------------------|-------------------|----------------|--------------|------------------|------------------|-------------|

| INT1IE           | CLC1IE                      | CWG1IE            | NCO1IE         | CCP1IE       | TMR2IE           | TMR1GIE          | TMR1IE      |

| bit 7            | •                           |                   | •              |              |                  |                  | bit (       |

| Legend:          |                             |                   |                |              |                  |                  |             |

| R = Readable     | bit                         | W = Writable      | bit            | U = Unimpler | nented bit, read | 1 as '0'         |             |

| u = Bit is unch  |                             | x = Bit is unkr   |                | •            |                  | R/Value at all o | ther Resets |

| '1' = Bit is set |                             | '0' = Bit is clea |                |              |                  |                  |             |

|                  |                             |                   |                |              |                  |                  |             |

| bit 7            | INT1IE: Exter               | rnal Interrupt 1  | Interrupt Enat | ole bit      |                  |                  |             |

|                  | 1 = Enabled<br>0 = Disabled |                   |                |              |                  |                  |             |

| bit 6            | CLC1IE: CLC                 | C1 Interrupt Ena  | able bit       |              |                  |                  |             |

|                  | 1 = Enabled<br>0 = Disabled |                   |                |              |                  |                  |             |

| bit 5            | CWG1IE: CV                  | VG1 Interrupt E   | nable bit      |              |                  |                  |             |

|                  | 1 = Enabled<br>0 = Disabled |                   |                |              |                  |                  |             |

| bit 4            | NCO1IE: NC                  | O1 Interrupt Er   | able bit       |              |                  |                  |             |

|                  | 1 = Enabled<br>0 = Disabled |                   |                |              |                  |                  |             |

| bit 3            | CCP1IE: CCI                 | P1 Interrupt En   | able bit       |              |                  |                  |             |

|                  | 1 = Enabled<br>0 = Disabled |                   |                |              |                  |                  |             |

| bit 2            | TMR2IE: TMI                 | R2 Interrupt En   | able bit       |              |                  |                  |             |

|                  | 1 = Enabled<br>0 = Disabled |                   |                |              |                  |                  |             |

| bit 1            | TMR1GIE: TI                 | MR1 Gate Inter    | rupt Enable bi | it           |                  |                  |             |

|                  | 1 = Enabled<br>0 = Disabled |                   |                |              |                  |                  |             |

| bit 0            | TMR1IE: TM                  | R1 Interrupt En   | able bit       |              |                  |                  |             |

|                  | 1 = Enabled<br>0 = Disabled |                   |                |              |                  |                  |             |

|                  |                             |                   |                |              |                  |                  |             |

## REGISTER 9-17: PIE4: PERIPHERAL INTERRUPT ENABLE REGISTER 4

| U-0             | R/W-1/1                            | R/W-1/1            | R/W-1/1      | R/W-1/1        | R/W-1/1          | R/W-1/1          | R/W-1/1      |

|-----------------|------------------------------------|--------------------|--------------|----------------|------------------|------------------|--------------|

| -               | CLC4IP                             | CCP4IP             | CLC3IP       | CWG3IP         | CCP3IP           | TMR6IP           | TMR5GIP      |

| bit 7           |                                    |                    |              |                |                  |                  | bit          |

|                 |                                    |                    |              |                |                  |                  |              |

| Legend:         |                                    |                    |              |                |                  |                  |              |

| R = Readab      | le bit                             | W = Writable       | bit          | U = Unimpler   | nented bit, read | as '0'           |              |

| u = Bit is un   | changed                            | x = Bit is unkr    | nown         | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is se | et                                 | '0' = Bit is clea  | ared         |                |                  |                  |              |

| bit 7           | Unimplemer                         | nted: Read as '    | כ,           |                |                  |                  |              |

| bit 6           | -                                  | C4 Interrupt Pric  |              |                |                  |                  |              |

|                 | 1 = High price                     | •                  | j            |                |                  |                  |              |

|                 | 0 = Low prio                       | •                  |              |                |                  |                  |              |

| bit 5           | CCP4IP: CC                         | P4 Interrupt Pri   | ority bit    |                |                  |                  |              |

|                 | 1 = High pric                      |                    |              |                |                  |                  |              |

|                 | 0 = Low prio                       | •                  |              |                |                  |                  |              |

| bit 4           |                                    | C3 Interrupt Price | ority bit    |                |                  |                  |              |

|                 | 1 = High pric                      | •                  |              |                |                  |                  |              |

| bit 3           | 0 = Low prio                       | -                  | riarity bit  |                |                  |                  |              |

| DIL S           | 1 = High price                     | VG3 Interrupt P    | nonty bit    |                |                  |                  |              |

|                 | 0 = Low prio                       |                    |              |                |                  |                  |              |

| bit 2           | •                                  | P3 Interrupt Pri   | ority bit    |                |                  |                  |              |

|                 | 1 = High pric                      | •                  |              |                |                  |                  |              |

|                 | 0 = Low prio                       | rity               |              |                |                  |                  |              |

| bit 1           | bit 1 TMR6IP: TMR6IP Interrupt Pri |                    | Priority bit |                |                  |                  |              |

|                 | 1 = High price                     |                    |              |                |                  |                  |              |

|                 | 0 = Low prio                       | •                  |              |                |                  |                  |              |

| bit 0           |                                    | MR5 Interrupt F    | Priority bit |                |                  |                  |              |

|                 | 1 = High pric<br>0 = Low prio      |                    |              |                |                  |                  |              |

|                 |                                    | iii.y              |              |                |                  |                  |              |

## REGISTER 9-32: IPR9: PERIPHERAL INTERRUPT PRIORITY REGISTER 9

# PIC18(L)F25/26K83

| TADLE 15-5. | JUIWINA |           |                 | ,     |           |         |        |       |                     |

|-------------|---------|-----------|-----------------|-------|-----------|---------|--------|-------|---------------------|

| Name        | Bit 7   | Bit 6     | Bit 5           | Bit 4 | Bit 3     | Bit 2   | Bit 1  | Bit 0 | Register<br>on Page |

| DMAxCON0    | EN      | SIRQEN    | DGO             | _     | _         | AIRQEN  |        | XIP   | 238                 |

| DMAxCON1    | DMOD    | E<1:0>    | DSTP            | SMR   | <1:0>     | SMOD    | E<1:0> | SSTP  | 239                 |

| DMAxBUF     | DBUF7   | DBUF6     | DBUF5           | DBUF4 | DBUF3     | DBUF2   | DBUF1  | DBUF0 | 240                 |

| DMAxSSAL    |         |           |                 | SSA   | <7:0>     |         |        |       | 240                 |

| DMAxSSAH    |         |           |                 | SSA<  | :15:8>    |         |        |       | 240                 |

| DMAxSSAU    | _       | —         |                 |       | SSA<      | 21:16>  |        |       | 241                 |

| DMAxSPTRL   |         |           |                 | SPTR  | R<7:0>    |         |        |       | 241                 |

| DMAxSPTRH   |         |           |                 | SPTR  | <15:8>    |         |        |       | 241                 |

| DMAxSPTRU   | —       | _         |                 |       | SPTR<     | <21:16> |        |       | 242                 |

| DMAxSSZL    |         | -         |                 | SSZ   | <7:0>     |         |        |       | 242                 |

| DMAxSSZH    | —       |           | _               | —     |           | SSZ<    | 11:8>  |       | 242                 |

| DMAxSCNTL   |         | -         |                 | SCNT  | <7:0>     |         |        |       | 243                 |

| DMAxSCNTH   | —       |           | _               | —     |           | SCNT    | <11:8> |       | 243                 |

| DMAxDSAL    |         |           |                 | DSA   | <7:0>     |         |        |       | 243                 |

| DMAxDSAH    |         |           |                 | DSA<  | :15:8>    |         |        |       | 244                 |

| DMAxDPTRL   |         |           |                 | DPTF  | R<7:0>    |         |        |       | 244                 |

| DMAxDPTRH   |         |           |                 | DPTR  | <15:8>    |         |        |       | 244                 |

| DMAxDSZL    |         |           |                 | DSZ   | <7:0>     |         |        |       | 245                 |

| DMAxDSZH    | —       | —         | – – – DSZ<11:8> |       |           |         |        |       | 245                 |

| DMAxDCNTL   |         | DCNT<7:0> |                 |       |           |         |        | 245   |                     |

| DMAxDCNTH   | _       | _         |                 | _     |           | DCNT    | <11:8> |       | 246                 |

| DMAxSIRQ    | _       |           |                 |       |           |         |        |       | 246                 |

| DMAxAIRQ    | _       |           |                 |       | AIRQ<6:0> | •       |        |       | 246                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by DMA.

#### 16.3.6 INPUT THRESHOLD CONTROL

The INLVLx register (Register 16-8) controls the input voltage threshold for each of the available PORTx input pins. A selection between the Schmitt Trigger CMOS or the TTL compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTx register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 45-4 for more information on threshold levels.

**Note:** Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

#### 16.3.7 WEAK PULL-UP CONTROL

The WPUx register (Register 16-5) controls the individual weak pull-ups for each port pin.

#### 16.3.8 EDGE SELECTABLE INTERRUPT-ON-CHANGE

An interrupt can be generated by detecting a signal at the port pin that has either a rising edge or a falling edge. Any individual pin can be configured to generate an interrupt. The interrupt-on-change module is present on all the pins of Ports B, C, E and on pin RG5. For further details about the IOC module refer to **Section 18.0 "Interrupt-on-Change"**.

## 16.3.9 I<sup>2</sup>C PAD CONTROL

For the PIC18(L)F25/26K83 devices, the I<sup>2</sup>C specific pads are available on RB1, RB2, RC3, RC4, RD0<sup>(1)</sup> and RD1<sup>(1)</sup> pins. The I<sup>2</sup>C characteristics of each of these pins is controlled by the RxyI2C registers (see Register 16-9). These characteristics include enabling I<sup>2</sup>C specific slew rate (over standard GPIO slew rate), selecting internal pull-ups for I<sup>2</sup>C pins, and selecting appropriate input threshold as per SMBus specifications.

Note 1: RD0 and RD1 I<sup>2</sup>C pads are not available in PIC18(L)F25K83 parts.

**2:** Any peripheral using the I<sup>2</sup>C pins read the I<sup>2</sup>C ST inputs when enabled via RxyI2C.

### 16.4 PORTE Registers

#### 16.4.1 MASTER CLEAR INPUT (MCLR)

For PIC18(L)F2xK83 devices, PORTE is only available when Master Clear functionality is disabled (MCLRE = 0). In this case, PORTE is a single bit, input-only port comprised of RE3 only. The pin operates as previously described. RE3 in PORTE register is a read-only bit and will read '1' when MCLRE = 1 (i.e., Master Clear enabled).

#### 16.4.2 RE3 WEAK PULL-UP

The port RE3 pin has an individually controlled weak internal pull-up. When set, the WPUE3 bit enables the RE3 pin pull-up. When the RE3 port pin is configured as  $\overline{MCLR}$ , (CONFIG2L, MCLRE = 1 and CONFIG4H, LVP = 0), or configured for Low-Voltage Programming, (MCLRE = x and LVP = 1), the pull-up is always enabled and the WPUE3 bit has no effect.

#### 16.4.3 INTERRUPT-ON-CHANGE

The interrupt-on-change feature is available only on the RE3 pin of PORTE for all devices. If MCLRE = 1 or LVP = 1, RE3 port functionality is disabled and interrupt-on-change on RE3 is not available. For further details refer to **Section 18.0 "Interrupt-on-Change"**.

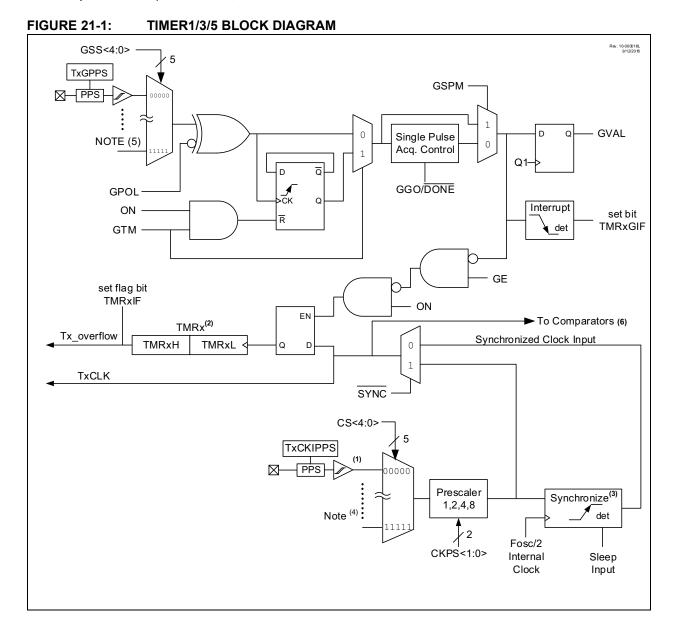

# 21.0 TIMER1/3/5 MODULE WITH GATE CONTROL

Timer1/3/5 module is a 16-bit timer/counter with the following features:

- 16-bit timer/counter register pair (TMRxH:TMRxL)

- Programmable internal or external clock source

- · 2-bit prescaler

- · Dedicated Secondary 32 kHz oscillator circuit

- · Optionally synchronized comparator out

- Multiple Timer1/3/5 gate (count enable) sources

- Interrupt-on-overflow

- · Wake-up on overflow (external clock,

Asynchronous mode only)

- 16-Bit Read/Write Operation

- Time base for the Capture/Compare function with the CCP modules

- Special Event Trigger (with CCP)

- · Selectable Gate Source Polarity

- Gate Toggle mode

- · Gate Single-pulse mode

- · Gate Value Status

- · Gate Event Interrupt

Figure 21-1 is a block diagram of the Timer1/3/5 module.

PIC18(L)F25/26K83

© 2017 Microchip Technology Inc.

Preliminary

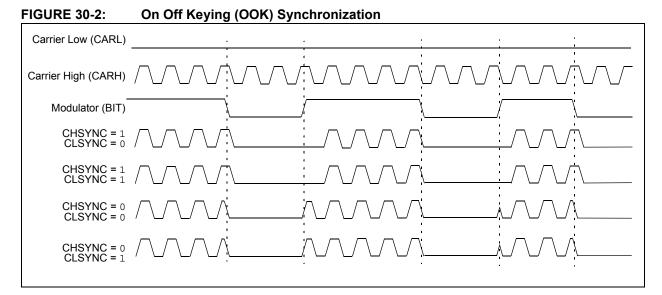

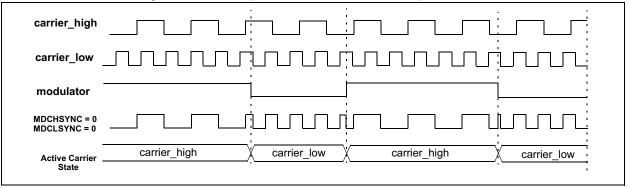

### FIGURE 30-3: No Synchronization (CHSYNC = 0, CLSYNC = 0)

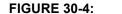

#### Carrier High Synchronization (CHSYNC = 1, CLSYNC = 0)

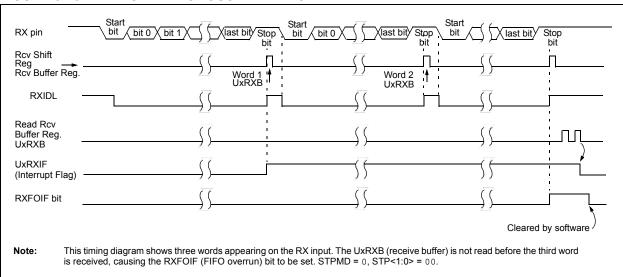

#### FIGURE 31-5: ASYNCHRONOUS RECEPTION

## 31.17.2 AUTO-BAUD OVERFLOW

During the course of automatic baud detection, the ABDOVF bit in the UxERRIR register will be set if the baud rate counter overflows before the fifth falling edge is detected on the RX pin. The ABDOVF bit indicates that the counter has exceeded the maximum count that can fit in the 16 bits of the UxBRGH:UxBRGL register pair. After the ABDOVF bit has been set, the state machine continues to search until the fifth falling edge is detected on the RX pin. Upon detecting the fifth falling RX edge, the hardware will set the ABDIF interrupt flag and clear the ABDEN bit in the UxCON0 register. The UxBRGH and UxBRGL register values retain their previous value. The ABDIF flag in the UxUIR register and ABDOVF flag in the UxERRIR register can be cleared by software directly. To generate an interrupt on an auto-baud overflow condition, all the following bits must be set:

- ABDOVE bit in the UxERRIE register

- UxEIE bit in the PIEx register

- PIE and GIE bits in the INTCON register

To terminate the auto-baud process before the ABDIF flag is set, clear the ABDEN bit, then clear the ABDOVF bit in the UxERRIR register.

#### 31.17.3 AUTO-WAKE-UP ON BREAK

During Sleep mode, all clocks to the UART are suspended. Because of this, the Baud Rate Generator is inactive and a proper character reception cannot be performed. The Auto-Wake-up feature allows the controller to wake-up due to activity on the RX line.

The Auto-Wake-up feature is enabled by setting both the WUE bit in the UxCON1 register and the UxIE bit in the PIEx register. Once set, the normal receive sequence on RX is disabled, and the UART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a transition out of the Idle state on the RX line. (This coincides with the start of a Break or a wake-up signal character for the LIN protocol.)

The UART module generates a WUIF interrupt coincident with the wake-up event. The interrupt is generated synchronously to the Q clocks in normal CPU operating modes (Figure 31-13), and asynchronously, if the device is in Sleep mode (Figure 31-14). The interrupt condition is cleared by clearing the WUIF bit in the UxUIR register. To generate an interrupt on a wake-up event, all the following bits must be set:

- UxIE bit in the PIEx register

- PIE and GIE bits in the INTCON register

The WUE bit is automatically cleared by the transition to the Idle state on the RX line at the end of the Break. This signals to the user that the Break event is over. At this point, the UART module is in Idle mode, waiting to receive the next character.

#### 31.17.3.1 Special Considerations

#### **Break Character**

To avoid character errors or character fragments during a wake-up event, the wake-up character must be all zeros.

When the wake-up is enabled, the function works independent of the low time on the data stream. If the WUE bit is set and a valid non-zero character is received, the low time from the Start bit to the first rising edge will be interpreted as the wake-up event. The remaining bits of the character will be received as a fragmented character and subsequent characters can result in framing or overrun errors.

Therefore, the initial character of the transmission must be all zeros. This must be eleven or more bit times, 13bit times recommended for LIN bus, or any number of bit times for standard RS-232 devices.

#### **Oscillator Start-up Time**

Oscillator start-up time must be considered, especially in applications using oscillators with longer start-up intervals (i.e., LP, XT or HS/PLL modes). The Sync Break (or wake-up signal) character must be of sufficient length, and be followed by a sufficient interval, to allow enough time for the selected oscillator to start and provide proper initialization of the UART.

#### WUE Bit

To ensure that no actual data is lost, check the RXIDL bit to verify that a receive operation is not in process before setting the WUE bit. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

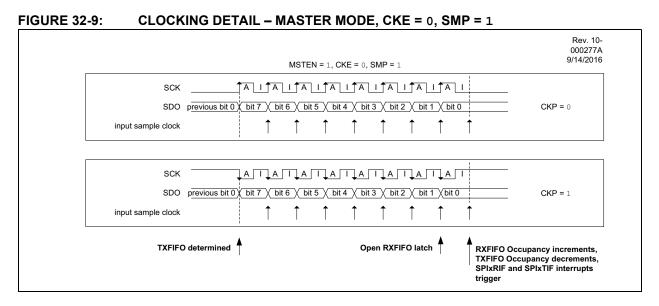

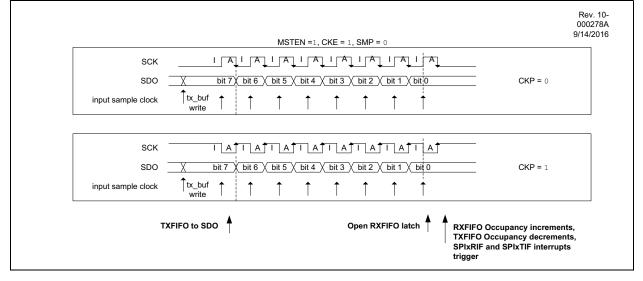

FIGURE 32-10: CLOCKING DETAIL – MASTER MODE, CKE = 1, SMP = 0

#### 32.5.6.3 SCK Start-Up Delay

When starting an SPI data exchange, the master device sets the SS output (either through hardware or software) and then triggers the module to send data. These data triggers are synchronized to the clock selected by the SPIxCLK register before the first SCK pulse appears, usually requiring one or two clocks of the selected clock.

The SPI module includes synchronization delays on SCK generation specifically designed to ensure that the Slave Select output timing is correct, without requiring precision software timing loops.

When the value of the SPIxBAUD register is a small number (indicating higher SCK frequencies), the synchronization delay can be relatively long between setting SS and the first SCK. With larger values of SPIxBAUD (indicating lower SCK frequencies), this delay is much smaller and the first SCK can appear relatively quickly after SS is set.

By default, the SPI module inserts a ½ baud delay (half of the period of the clock selected by the SPIxCLK register) before the first SCK pulse. This allows for systems with a high SPIxBAUD value to have extra setup time before the first clock. Setting the FST bit in SPIxCON1 removes this additional delay, allowing systems with low SPIxBAUD values (and thus, long synchronization delays) to forego this unnecessary extra delay.

#### 32.8.3.4 Receiver Overflow and Transmitter Underflow Interrupts

The receiver overflow interrupt triggers if data is received when the RXFIFO is already full and RXR = 1. In this case, the data will be discarded and the RXOIF bit will be set. The receiver overflow interrupt flag is the RXOIF bit of SPIxINTF. The receiver overflow interrupt enable bit is the RXOIE bit of SPIxINTE.

The Transmitter Underflow interrupt flag triggers if a data transfer begins when the TXFIFO is empty and TXR = 1. In this case, the most recently received data will be transmitted and the TXUIF bit will be set. The transmitter underflow interrupt flag is the TXUIF bit of SPIxINTF. The transmitter underflow interrupt enable bit is the TXUIE bit of SPIxINTE.

Both of these interrupts will only occur in Slave mode, as Master mode will not allow the RXFIFO to overflow or the TXFIFO to underflow.

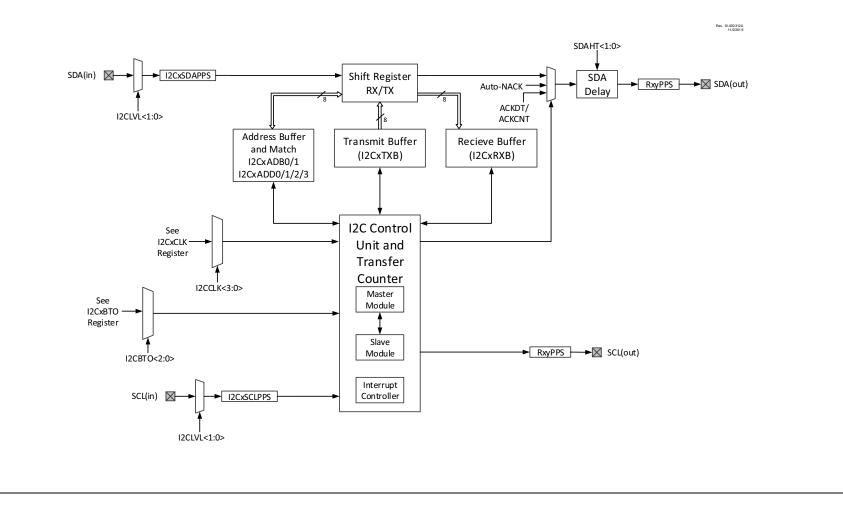

# 33.0 I<sup>2</sup>C MODULE

The device has two dedicated, independent I<sup>2</sup>C modules. Figure 33-1 is a block diagram of the I<sup>2</sup>C interface module. The figure shows both the Master and Slave modes together.

# EXAMPLE 34-2: WIN AND ICODE BITS USAGE IN INTERRUPT SERVICE ROUTINE TO ACCESS TX/RX BUFFERS (CONTINUED)

| ErrorInter | rrupt                     |                                        |

|------------|---------------------------|----------------------------------------|

| BCF        | PIR3, ERRIF               | ; Clear the interrupt flag             |

|            |                           | ; Handle error.                        |

| RETFIE     |                           |                                        |

| TXB2Interr | rupt                      |                                        |

| BCF        | PIR3, TXB2IF              | ; Clear the interrupt flag             |

| GOTO       | AccessBuffer              |                                        |

| TXBlInterr | rupt                      |                                        |

| BCF        | PIR3, TXB1IF              | ; Clear the interrupt flag             |

| GOTO       | AccessBuffer              |                                        |

| TXB0Interr | rupt                      |                                        |

| BCF        | PIR3, TXB0IF              | ; Clear the interrupt flag             |

| GOTO       | AccessBuffer              |                                        |

| RXBlInterr | rupt                      |                                        |

| BCF        | PIR3, RXB1IF              | ; Clear the interrupt flag             |

| GOTO       | Accessbuffer              |                                        |

| RXB0Interr | rupt                      |                                        |

| BCF        | PIR3, RXB0IF              | ; Clear the interrupt flag             |

| GOTO       | AccessBuffer              |                                        |

| AccessBuff | er                        | ; This is either TX or RX interrupt    |

| ; Copy     | CANSTAT.ICODE bits to CA  | NCON.WIN bits                          |

| MOVF       | TempCANCON, W             | ; Clear CANCON.WIN bits before copying |

|            |                           | ; new ones.                            |

| ANDLW      | B'11110001'               | ; Use previously saved CANCON value to |

|            |                           | ; make sure same value.                |

| MOVWF      | TempCANCON                | ; Copy masked value back to TempCANCON |

| MOVF       | TempCANSTAT, W            | ; Retrieve ICODE bits                  |

| ANDLW      | B'00001110'               | ; Use previously saved CANSTAT value   |

|            |                           | ; to make sure same value.             |

| IORWF      | TempCANCON                | ; Copy ICODE bits to WIN bits.         |

| MOVFF      | TempCANCON, CANCON        | ; Copy the result to actual CANCON     |

| ; Acce     | ss current buffer…        |                                        |

| ; User     | code                      |                                        |

| ; Rest     | ore CANCON.WIN bits       |                                        |

| MOVF       | CANCON, W                 | ; Preserve current non WIN bits        |

| ANDLW      | B'11110001'               |                                        |

| IORWF      | TempCANCON                | ; Restore original WIN bits            |

| ; Do n     | ot need to restore CANSTA | T - it is read-only register.          |

| ; Retu     | rn from interrupt or chec | k for another module interrupt source  |

|            |                           |                                        |

## REGISTER 37-11: ADACQL: ADC ACQUISITION TIME CONTROL REGISTER (LOW BYTE)

|                  |                                   |                  |         | -                                  |         | <b>\</b> - | ,            |  |

|------------------|-----------------------------------|------------------|---------|------------------------------------|---------|------------|--------------|--|

| R/W-0/0          | R/W-0/0                           | R/W-0/0          | R/W-0/0 | R/W-0/0                            | R/W-0/0 | R/W-0/0    | R/W-0/0      |  |

|                  |                                   |                  | ACQ     | <7:0>                              |         |            |              |  |

| bit 7            |                                   |                  |         |                                    |         |            | bit 0        |  |

|                  |                                   |                  |         |                                    |         |            |              |  |

| Legend:          |                                   |                  |         |                                    |         |            |              |  |

| R = Readable     | R = Readable bit W = Writable bit |                  |         | U = Unimplemented bit, read as '0' |         |            |              |  |

| u = Bit is uncha | anged                             | x = Bit is unk   | nown    | wn -n/n = Value at POR and BOR/\   |         |            | other Resets |  |

| '1' = Bit is set |                                   | '0' = Bit is cle | ared    |                                    |         |            |              |  |

bit 7-0 ACQ<7:0>: Acquisition (charge share time) Select bits See Table .

#### REGISTER 37-12: ADACQH: ADC ACQUISITION TIME CONTROL REGISTER (HIGH BYTE)

| U-0   | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0   | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|---------|---------|-----------|---------|---------|

| —     | —   |     |         |         | ACQ<12:8> |         |         |

| bit 7 |     |     |         |         |           |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 ACQ<12:8>: Acquisition (charge share time) Select bits See Table .

#### TABLE 37-5: ACQUISITION TIME

| ADACQ            | Acquisition time                                         |  |  |  |  |

|------------------|----------------------------------------------------------|--|--|--|--|

| 1 1111 1111 1111 | 8191 clocks of the selected ADC clock                    |  |  |  |  |

| 1 1111 1111 1110 | 8190 clocks of the selected ADC clock                    |  |  |  |  |

| 1 1111 1111 1101 | 8189 clocks of the selected ADC clock                    |  |  |  |  |

|                  |                                                          |  |  |  |  |

| 0 0000 0000 0010 | 2 clocks of the selected ADC clock                       |  |  |  |  |

| 0 0000 0000 0001 | 1 clock of the selected ADC clock                        |  |  |  |  |

| 0 0000 0000 0000 | Not included in the data conversion cycle <sup>(1)</sup> |  |  |  |  |

**Note 1:** If ADPRE is not equal to '0', then ADACQ = 0b0\_0000\_0000 means Acquisition time is 8192 clocks of the selected ADC clock.

# PIC18(L)F25/26K83

| TBL   | RD              | Table Rea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | d       |     |               |                                             |  |

|-------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|---------------|---------------------------------------------|--|

| Synta | ax:             | TBLRD ( *; *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | *+; *-; | +*) |               |                                             |  |

| Oper  | ands:           | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |     |               |                                             |  |

| Oper  |                 | if TBLRD *,<br>(Prog Mem (TBLPTR)) $\rightarrow$ TABLAT;<br>TBLPTR – No Change;<br>if TBLRD *+,<br>(Prog Mem (TBLPTR)) $\rightarrow$ TABLAT;<br>(TBLPTR) + 1 $\rightarrow$ TBLPTR;<br>if TBLRD *-,<br>(Prog Mem (TBLPTR)) $\rightarrow$ TABLAT;<br>(TBLPTR) – 1 $\rightarrow$ TBLPTR;<br>if TBLRD +*,<br>(TBLPTR) + 1 $\rightarrow$ TBLPTR;<br>(Prog Mem (TBLPTR)) $\rightarrow$ TABLAT;                                                                                                                                                                       |         |     |               |                                             |  |

| Statu | s Affected:     | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |     |               |                                             |  |

| Enco  | ding:           | 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 000     | 00  | 0000          | 0 10nn<br>nn=0 *<br>=1 *+<br>=2 *-<br>=3 +* |  |

| Desc  |                 | This instruction is used to read the contents<br>of Program Memory (P.M.). To address the<br>program memory, a pointer called Table<br>Pointer (TBLPTR) is used.<br>The TBLPTR (a 21-bit pointer) points to<br>each byte in the program memory. TBLPTR<br>has a 2-Mbyte address range.<br>TBLPTR[0] = 0: Least Significant Byte<br>of Program Memory<br>Word<br>TBLPTR[0] = 1: Most Significant Byte<br>of Program Memory<br>Word<br>The TBLRD instruction can modify the value<br>of TBLPTR as follows:<br>• no change<br>• post-increment<br>• pre-increment |         |     |               |                                             |  |

| Word  | ls:             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |     |               |                                             |  |

| Cycle | es:             | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |     |               |                                             |  |

|       | ycle Activity   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |     |               |                                             |  |

| ~ ~   | Q1              | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |     | Q3            | Q4                                          |  |

|       | Decode          | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |     | No            | No                                          |  |

|       | • •             | operatio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         | оре | eration       | operation                                   |  |

|       | No<br>operation | No opera<br>(Read Prog<br>Memor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | gram    | оре | No<br>eration | No operation<br>(Write TABLAT)              |  |

#### TBLRD **Table Read (Continued)**

| Example1:                            | TBLRD                | *+       | ;                |                              |

|--------------------------------------|----------------------|----------|------------------|------------------------------|

| Before Instruction                   | on                   |          |                  |                              |

| TABLAT<br>TBLPTR<br>MEMORY           | (00A356h             | 1)       | =<br>=<br>=      | 55h<br>00A356h<br>34h        |

| After Instruction                    | ı                    |          |                  |                              |

| TABLAT                               |                      |          | =                | 34h                          |

| TBLPTR                               |                      |          | =                | 00A357h                      |

| Example2:                            | TBLRD                | +*       | ;                |                              |

| Before Instruction                   | on                   |          |                  |                              |

| TABLAT<br>TBLPTR<br>MEMORY<br>MEMORY | (01A357h<br>(01A358h | ı)<br>ı) | =<br>=<br>=<br>= | AAh<br>01A357h<br>12h<br>34h |

| After Instruction                    | ı                    |          |                  |                              |

| TABLAT<br>TBL PTR                    |                      |          | =                | 34h                          |

| IBLPIR                               |                      |          | -                | 01A358h                      |

Memory)

| Addr            | Name       | Bit 7         | Bit 6 | Bit 5 | Bit 4              | Bit 3 | Bit 2     | Bit 1 | Bit 0     | Register<br>on page |

|-----------------|------------|---------------|-------|-------|--------------------|-------|-----------|-------|-----------|---------------------|

| 3BC8h-<br>3AEEh | —          | Unimplemented |       |       |                    |       |           |       |           | —                   |

| 3AEDh           | CANRXPPS   |               | —     | —     | CANRXPPS           |       |           |       |           |                     |

| 3AECh           | —          |               |       |       | Unimplemented      |       |           |       |           | —                   |

| 3AEBh           | U2CTSPPS   | _             | _     | —     | U2CTSPPS           |       |           |       |           |                     |

| 3AEAh           | U2RXPPS    | _             | _     | —     | U2RXPPS            |       |           |       |           |                     |

| 3AE9h           | _          |               |       |       | Unimplemented      |       |           |       |           | _                   |

| 3AE8h           | U1CTSPPS   | _             | _     | _     | U1CTSPPS           |       |           |       |           | 264                 |

| 3AE7h           | U1RXPPS    | _             | _     | _     | U1RXPPS            |       |           |       |           |                     |

| 3AE6h           | I2C2SDAPPS | _             | _     | _     | I2C2SDAPPS         |       |           |       |           |                     |

| 3AE5h           | I2C2SCLPPS | _             | _     | _     | I2C2SCLPPS         |       |           |       |           |                     |

| 3AE4h           | I2C1SDAPPS | _             |       | _     | I2C1SDAPPS         |       |           |       |           |                     |

| 3AE3h           | I2C1SCLPPS | _             | _     | _     | I2C1SCLPPS         |       |           |       |           |                     |

| 3AE2h           | SPI1SSPPS  | _             | _     | _     | SPI1SSPPS          |       |           |       |           |                     |

| 3AE1h           | SPI1SDIPPS | _             | _     | _     | SPI1SDIPPS         |       |           |       |           | 264                 |

| 3AE0h           | SPI1SCKPPS | _             | _     | _     | SPI1SCKPPS         |       |           |       |           | 264                 |

| 3ADFh           | ADACTPPS   | _             | _     | _     | ADACTPPS           |       |           |       |           | 264                 |

| 3ADEh           | CLCIN3PPS  | _             | _     | _     | CLCIN3PPS          |       |           |       |           | 264                 |

| 3ADDh           | CLCIN2PPS  | _             | _     | _     | CLCIN2PPS          |       |           |       |           | 264                 |

| 3ADCh           | CLCIN1PPS  | _             | _     | _     | CLCIN1PPS          |       |           |       |           | 264                 |

| 3ADBh           | CLCIN0PPS  |               |       | _     | CLCINOPPS          |       |           |       |           | 264                 |

| 3ADAh           | MD1SRCPPS  |               | _     | _     | MD1SRCPPS          |       |           |       |           | 264                 |

| 3AD9h           | MD1CARHPPS |               | _     | _     | MD1CARHPPS         |       |           |       |           | 264                 |

| 3AD8h           | MD1CARLPPS |               |       |       | MD1CARLPPS         |       |           |       |           | 264                 |

| 3AD7h           | CWG3INPPS  |               |       |       |                    |       | CWG3INPPS |       |           | 264                 |

| 3AD6h           | CWG2INPPS  |               | _     | _     | CWG2INPPS          |       |           |       |           | 264                 |

| 3AD5h           | CWG1INPPS  |               |       |       | CWG1INPPS          |       |           |       |           | 264                 |

| 3AD4h           | SMT2SIGPPS |               |       |       | SMT2SIGPPS         |       |           |       |           | 264                 |

| 3AD3h           | SMT2WINPPS |               | _     |       | SMT2WINPPS         |       |           |       |           | 264                 |

| 3AD2h           | SMT1SIGPPS |               |       | _     | SMT1SIGPPS         |       |           |       |           | 264                 |

| 3AD1h           | SMT1WINPPS |               |       | _     | SMT1WINPPS         |       |           |       |           | 264                 |

| 3AD0h           | CCP4PPS    |               | _     | _     | CCP4PPS            |       |           |       |           | 264                 |

| 3ACFh           | CCP3PPS    |               |       | _     | CCP3PPS            |       |           |       |           | 264                 |

| 3ACEh           | CCP2PPS    |               |       | _     | CCP2PPS            |       |           |       |           | 264                 |

| 3ACDh           | CCP1PPS    |               |       | _     | CCP1PPS            |       |           |       |           | 264                 |

| 3ACCh           | T6INPPS    | _             | _     | _     | T6INPPS            |       |           |       |           | 264                 |

| 3ACBh           | T4INPPS    |               |       | _     | T4INPPS            |       |           |       |           | 264                 |

| 3ACAh           | T2INPPS    |               |       | _     | T2INPPS            |       |           |       |           | 264                 |

| 3AC9h           | T5GPPS     |               |       | _     | T5GPPS             |       |           |       |           | 264                 |

| 3AC8h           | T5CLKIPPS  |               |       | _     | T5CLKIPPS          |       |           |       |           | 264                 |

| 3AC7h           | T3GPPS     |               |       | _     | T3GPPS             |       |           |       |           | 264                 |

| 3AC6h           | T3CLKIPPS  |               |       | _     | T3CLKIPPS          |       |           |       |           | 264                 |

| 3AC5h           | T1GPPS     |               |       | _     | TIGPPS             |       |           |       |           | 264                 |

| 3AC4h           | T1CKIPPS   |               | _     | _     | TICKIPPS           |       |           |       |           | 264                 |

| 3AC3h           | TOCKIPPS   |               |       | _     | TOCKIPPS           |       |           |       |           | 264                 |

| 3AC2h           | INT2PPS    |               |       | _     | INT2PPS            |       |           |       |           | 264                 |

| 3AC1h           | INT1PPS    |               |       | _     | INT2PPS<br>INT1PPS |       |           |       |           | 264                 |

| 3AC0h           | INTOPPS    |               |       | _     | INTIPPS            |       |           |       |           | 264                 |

| 5, (0011        | PPSLOCK    |               |       |       |                    |       | INTOP FO  |       | PPSLOCKED | -                   |

# TABLE 43-1: REGISTER FILE SUMMARY FOR PIC18(L)F25/26K83 DEVICES (CONTINUED)

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition

Note 1: Not present in LF devices.

# **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

Raleigh, NC Tel: 919-844-7510

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110 Tel: 408-436-4270

Canada - Toronto Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

China - Chengdu Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

China - Guangzhou Tel: 86-20-8755-8029

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

China - Nanjing Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai Tel: 86-21-3326-8000 Fax: 86-21-3326-8021

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

China - Shenzhen Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

China - Xiamen Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

Japan - Tokyo Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

Korea - Daegu Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7830 Taiwan - Taipei

Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

Thailand - Bangkok Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

Finland - Espoo Tel: 358-9-4520-820

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

France - Saint Cloud Tel: 33-1-30-60-70-00

**Germany - Garching** Tel: 49-8931-9700 **Germany - Haan** Tel: 49-2129-3766400

**Germany - Heilbronn** Tel: 49-7131-67-3636

Germany - Karlsruhe Tel: 49-721-625370

Germany - Munich Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Rosenheim Tel: 49-8031-354-560

Israel - Ra'anana Tel: 972-9-744-7705

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Padova Tel: 39-049-7625286

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

Norway - Trondheim Tel: 47-7289-7561

Poland - Warsaw Tel: 48-22-3325737

Romania - Bucharest Tel: 40-21-407-87-50

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Gothenberg Tel: 46-31-704-60-40

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

5118 Fax: **Tha**i 252 Tel: