Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                  |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf25k83-e-ml |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                         |        |                  | •   | ,                |                 |                 |       |

|-------------------------|--------|------------------|-----|------------------|-----------------|-----------------|-------|

| U-1                     | U-1    | U-1              | U-1 | U-1              | U-1             | U-1             | R/W-1 |

| _                       | _      | —                | _   | _                | _               | _               | CP    |

| bit 7                   |        |                  |     |                  |                 |                 | bit 0 |

|                         |        |                  |     |                  |                 |                 |       |

| Legend:                 |        |                  |     |                  |                 |                 |       |

| R = Readable bit        |        | W = Writable     | bit | U = Unimple      | mented bit, rea | d as '1'        |       |

| -n = Value for blank of | device | '1' = Bit is set |     | '0' = Bit is cle | eared           | x = Bit is unkr | nown  |

#### REGISTER 5-9: CONFIGURATION WORD 5L (30 0008h)

#### bit 7-1 Unimplemented: Read as '1'

bit 0

CP: User Program Flash Memory and Data EEPROM Code Protection bit

1 = User Program Flash Memory and Data EEPROM code protection is disabled

0 = User Program Flash Memory and Data EEPROM code protection is enabled

#### REGISTER 5-10: CONFIGURATION WORD 5H (30 0009h)

| U-1   | U-1 | U-1 | U-1 | U-1 | U-1 | U-1 | U-1   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| _     | _   | _   | —   | _   | —   | —   | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

|       |     |     |     |     |     |     |       |

| Legend:                     |                  |                            |                    |  |

|-----------------------------|------------------|----------------------------|--------------------|--|

| R = Readable bit            | W = Writable bit | U = Unimplemented bit, rea | d as '1'           |  |

| -n = Value for blank device | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |  |

bit 7-0 Unimplemented: Read as '1'

#### TABLE 5-2:SUMMARY OF CONFIGURATION WORDS

| Address  | Name     | Bit 7  | Bit 6  | Bit 5      | Bit 4   | Bit 3   | Bit 2       | Bit 1      | Bit 0    | Default/<br>Unprogrammed<br>Value |

|----------|----------|--------|--------|------------|---------|---------|-------------|------------|----------|-----------------------------------|

| 30 0000h | CONFIG1L | —      | F      | RSTOSC<2:0 | >       | _       |             | FEXTOSC<2  | :0>      | 1111 1111                         |

| 30 0001h | CONFIG1H | _      | _      | FCMEN      | _       | CSWEN   | _           | PR1WAY     | CLKOUTEN | 1111 1111                         |

| 30 0002h | CONFIG2L | BORE   | N<1:0> | LPBOREN    | IVT1WAY | MVECEN  | PWR         | TS<1:0>    | MCLRE    | 1111 1111                         |

| 30 0003h | CONFIG2H | XINST  | _      | DEBUG      | STVREN  | PPS1WAY | ZCD         | BOR        | V<1:0>   | 1111 1111                         |

| 30 0004h | CONFIG3L | _      | WDTE   | WDTE<1:0>  |         |         | WDTCPS<4:0> |            |          | 1111 1111                         |

| 30 0005h | CONFIG3H | _      | _      | WDTCCS<2:0 |         | >       |             | WDTCWS<2:  | :0>      | 1111 1111                         |

| 30 0006h | CONFIG4L | WRTAPP | _      | _          | SAFEN   | BBEN    |             | BBSIZE<2:0 | )>       | 1111 1111                         |

| 30 0007h | CONFIG4H | _      | _      | LVP        | _       | WRTSAF  | WRTD        | WRTC       | WRTB     | 1111 1111                         |

| 30 0008h | CONFIG5L | _      | _      | _          | _       | _       | _           | _          | CP       | 1111 1111                         |

| 30 0009h | CONFIG5H | _      | _      | _          | _       | _       | _           | _          | _        | 1111 1111                         |

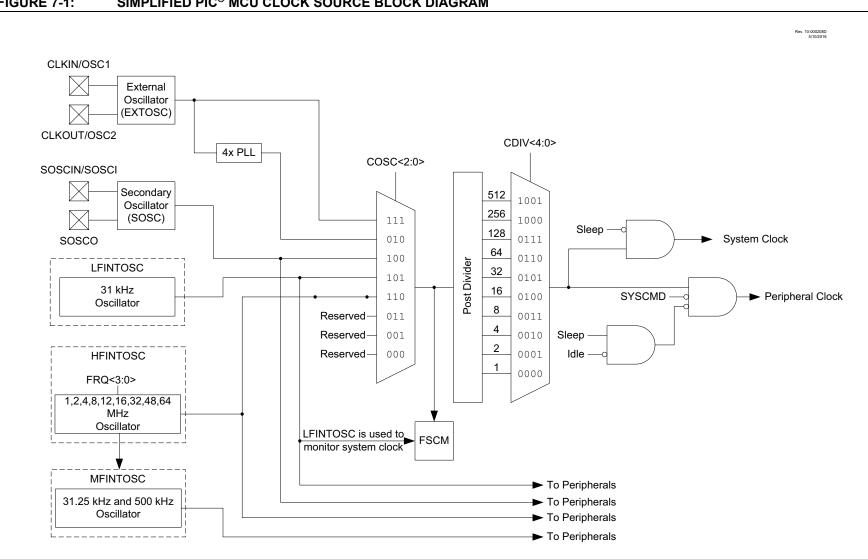

# FIGURE 7-1: SIMPLIFIED PIC<sup>®</sup> MCU CLOCK SOURCE BLOCK DIAGRAM

#### 7.2.2.6 Oscillator Status and Manual Enable

The Ready status of each oscillator (including the ADCRC oscillator) is displayed in OSCSTAT (Register 7-4). The oscillators (but not the PLL) may be explicitly enabled through OSCEN (Register 7-7).

#### 7.2.2.7 HFOR and MFOR Bits

The HFOR and MFOR bits indicate that the HFINTOSC and MFINTOSC is ready. These clocks are always valid for use at all times, but only accurate after they are ready.

When a new value is loaded into the OSCFRQ register, the HFOR and MFOR bits will clear, and set again when the oscillator is ready. During pending OSCFRQ changes the MFINTOSC clock will stall at a high or a low state, until the HFINTOSC resumes operation.

# 7.3 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the New Oscillator Source (NOSC) bits of the OSCCON1 register. The following clock sources can be selected using the following:

- External oscillator

- Internal Oscillator Block (INTOSC)

| Note: | The Clock Switch Enable bit in          |

|-------|-----------------------------------------|

|       | Configuration Word 1 can be used to     |

|       | enable or disable the clock switching   |

|       | capability. When cleared, the NOSC and  |

|       | NDIV bits cannot be changed by user     |

|       | software. When set, writing to NOSC and |

|       | NDIV is allowed and would switch the    |

|       | clock frequency.                        |

#### 7.3.1 NEW OSCILLATOR SOURCE (NOSC) AND NEW DIVIDER SELECTION REQUEST (NDIV) BITS

The New Oscillator Source (NOSC) and New Divider Selection Request (NDIV) bits of the OSCCON1 register select the system clock source and frequency that are used for the CPU and peripherals.

When new values of NOSC and NDIV are written to OSCCON1, the current oscillator selection will continue to operate while waiting for the new clock source to indicate that it is stable and ready. In some cases, the newly requested source may already be in use, and is ready immediately. In the case of a divideronly change, the new and old sources are the same, so the old source will be ready immediately. The device may enter Sleep while waiting for the switch as described in **Section 7.3.2 "Clock Switch and Sleep"**. When the new oscillator is ready, the New Oscillator Ready (NOSCR) bit of OSCCON3 and the Clock Switch Interrupt Flag (CSWIF) bit of the respective PIR register are set. If Clock Switch Interrupts are enabled (CSWIE = 1), an interrupt will be generated at that time. The Oscillator Ready (ORDY) bit of OSCCON3 can also be polled to determine when the oscillator is ready in lieu of an interrupt.

| Note: | The CSWIF interrupt will not wake the |

|-------|---------------------------------------|

|       | system from Sleep.                    |

If the Clock Switch Hold (CSWHOLD) bit of OSCCON3 is clear, the oscillator switch will occur when the New Oscillator is Ready bit (NOSCR) is set, and the interrupt (if enabled) will be serviced at the new oscillator setting.

If CSWHOLD is set, the oscillator switch is suspended, while execution continues using the current (old) clock source. When the NOSCR bit is set, software should:

- Set CSWHOLD = 0 so the switch can complete, or

- Copy COSC into NOSC to abandon the switch.

If DOZE is in effect, the switch occurs on the next clock cycle, whether or not the CPU is operating during that cycle.

Changing the clock post-divider without changing the clock source (i.e., changing Fosc from 1 MHz to 2 MHz) is handled in the same manner as a clock source change, as described previously. The clock source will already be active, so the switch is relatively quick. CSWHOLD must be clear (CSWHOLD = 0) for the switch to complete.

The current COSC and CDIV are indicated in the OSCCON2 register up to the moment when the switch actually occurs, at which time OSCCON2 is updated and ORDY is set. NOSCR is cleared by hardware to indicate that the switch is complete.

# 8.5 Register Definitions: Reference Clock

Long bit name prefixes for the Reference Clock peripherals are shown below. Refer to **Section 1.3.2.2 "Long Bit Names"** for more information.

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| CLKR       | CLKR            |

#### REGISTER 8-1: CLKRCON: REFERENCE CLOCK CONTROL REGISTER

| R/W-0/0 | U-0 | U-0 | R/W-1/1 | R/W-0/0 | R/W-0/0 | R/W-0/0  | R/W-0/0 |

|---------|-----|-----|---------|---------|---------|----------|---------|

| EN      | _   | _   | DC<     | :1:0>   |         | DIV<2:0> |         |

| bit 7   |     |     |         |         |         |          | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | EN: Reference Clock Module Enable bit                                                                                                                                                                                                                                                              |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul><li>1 = Reference clock module enabled</li><li>0 = Reference clock module is disabled</li></ul>                                                                                                                                                                                                |

| bit 6-5 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                         |

| bit 4-3 | DC<1:0>: Reference Clock Duty Cycle bits <sup>(1)</sup>                                                                                                                                                                                                                                            |

|         | <ul> <li>11 = Clock outputs duty cycle of 75%</li> <li>10 = Clock outputs duty cycle of 50%</li> <li>01 = Clock outputs duty cycle of 25%</li> <li>00 = Clock outputs duty cycle of 0%</li> </ul>                                                                                                  |

| bit 2-0 | DIV<2:0>: Reference Clock Divider bits                                                                                                                                                                                                                                                             |

|         | <pre>111 = Base clock value divided by 128 110 = Base clock value divided by 64 101 = Base clock value divided by 32 100 = Base clock value divided by 16 011 = Base clock value divided by 8 010 = Base clock value divided by 4 001 = Base clock value divided by 2 000 = Base clock value</pre> |

Note 1: Bits are valid for reference clock divider values of two or larger, the base clock cannot be further divided.

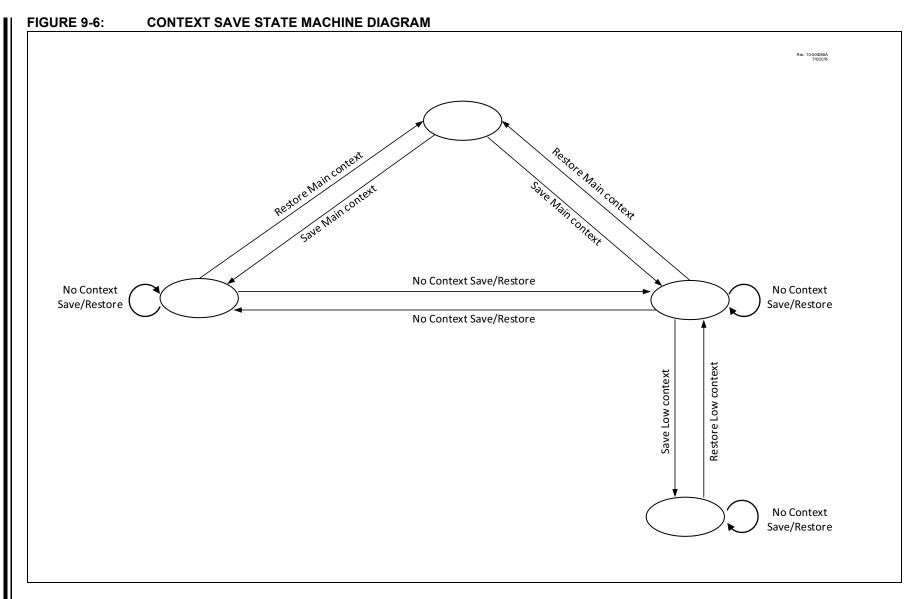

# 9.3 Interrupt Priority

The final priority level for any pending source of interrupt is determined first by the user-assigned priority of that source in the IPRx register, then by the natural order priority within the IVT. The sections below detail the operation of Interrupt priorities.

#### 9.3.1 USER (SOFTWARE) PRIORITY

User-assigned interrupt priority is enabled by setting the IPEN bit in the INTCON0 register (Register 9-1). Each peripheral interrupt source can be assigned a high or low priority level by the user. The userassignable interrupt priority control bits for each interrupt are located in the IPRx registers (Registers 9-23 through 9-32).

The interrupts are serviced based on predefined interrupt priority scheme defined below.

- 1. Interrupts set by the user as high-priority interrupt have higher precedence of execution. High-priority interrupts will override a low-priority request when:

- a) A low priority interrupt has been requested or its request is already pending.

- b) A low- and high-priority interrupt are triggered concurrently, i.e., on the same instruction cycle<sup>(1)</sup>.

- c) A low-priority interrupt was requested and the corresponding Interrupt Service Routine is currently executing. In this case, the lower priority interrupt routine will complete executing after the high-priority interrupt has been serviced<sup>(2)</sup>.

- 2. Interrupts set by the user as a low priority have the lower priority of execution and are preempted by any high-priority interrupt.

- Interrupts defined with the same software priority cannot preempt or interrupt each other. Concurrent pending interrupts with the same user priority are resolved using the natural order priority. (when MVECEN = ON) or in the order the interrupt flag bits are polled in the ISR (when MVECEN = OFF).

- Note 1: When a high priority interrupt preempts a concurrent low priority interrupt, the GIEL bit may be cleared in the high priority Interrupt Service Routine. If the GIEL bit is cleared, the low priority interrupt will NOT be serviced even if it was originally requested. The corresponding interrupt flag needs to be cleared in user code.

- 2: When a high priority interrupt is requested while a low priority Interrupt Service Routine is executing, the GIEL bit may be cleared in the high priority Interrupt Service Routine. The pending low priority interrupt will resume even if the GIEL bit is cleared.

PIC18(L)F25/26K83

# EXAMPLE 13-4: WRITING TO PROGRAM FLASH MEMORY (CONTINUED)

| WRITE_BYTE_ | TO_HREGS |                     |                                         |

|-------------|----------|---------------------|-----------------------------------------|

|             | MOVF     | POSTINCO, W         | ; get low byte of buffer data           |

|             | MOVWF    | TABLAT              | ; present data to table latch           |

|             | TBLWT+*  |                     | ; write data, perform a short write     |

|             |          |                     | ; to internal TBLWT holding register.   |

|             | DECFSZ   | COUNTER             | ; loop until holding registers are full |

|             | BRA      | WRITE_WORD_TO_HREGS |                                         |

| PROGRAM_MEN | IORY     |                     |                                         |

|             | BCF      | NVMCON1, REG0       | ; point to Program Flash Memory         |

|             | BSF      | NVMCON1, REG1       | ; point to Program Flash Memory         |

|             | BSF      | NVMCON1, WREN       | ; enable write to memory                |

|             | BCF      | NVMCON1, FREE       | ; enable write to memory                |

|             | BCF      | INTCON0, GIE        | ; disable interrupts                    |

|             | MOVLW    | 55h                 |                                         |

| Required    | MOVWF    | NVMCON2             | ; write 55h                             |

| Sequence    | MOVLW    | 0AAh                |                                         |

|             | MOVWF    | NVMCON2             | ; write OAAh                            |

|             | BSF      | NVMCON1, WR         | ; start program (CPU stall)             |

|             | DCFSZ    | COUNTER2            | ; repeat for remaining write blocks     |

|             | BRA      | WRITE_BYTE_TO_HREGS |                                         |

|             | BSF      | INTCON0, GIE        | ; re-enable interrupts                  |

|             | BCF      | NVMCON1, WREN       | ; disable write to memory               |

|             |          |                     |                                         |

# 13.4 Register Definitions: Nonvolatile Memory

# REGISTER 13-1: NVMCON1: NONVOLATILE MEMORY CONTROL 1 REGISTER

| R/W-0/                                            | 0 R/W-0/0                                                                                                                                                                                          | U-0                                                                                                                              | R/S/HC-0/0                                                                                                          | R/W/HS-x/q                                                                                          | R/W-0/0                                                        | R/S/HC-0/0                                             | R/S/HC-0/0 |

|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------|------------|

| F                                                 | REG<1:0>                                                                                                                                                                                           |                                                                                                                                  | FREE                                                                                                                | WRERR                                                                                               | WREN                                                           | WR                                                     | RD         |

| bit 7                                             |                                                                                                                                                                                                    |                                                                                                                                  |                                                                                                                     |                                                                                                     |                                                                |                                                        | bit C      |

|                                                   |                                                                                                                                                                                                    |                                                                                                                                  |                                                                                                                     |                                                                                                     |                                                                |                                                        |            |

| Legend:                                           |                                                                                                                                                                                                    |                                                                                                                                  |                                                                                                                     |                                                                                                     |                                                                |                                                        |            |

| R = Reada                                         |                                                                                                                                                                                                    | W = Writable                                                                                                                     |                                                                                                                     | HC = Bit is cle                                                                                     | -                                                              |                                                        |            |

| x = Bit is ι                                      |                                                                                                                                                                                                    | -n = Value at                                                                                                                    | -                                                                                                                   |                                                                                                     | -                                                              | are, but not clea                                      | ared       |

| '0' = Bit is                                      | cleared                                                                                                                                                                                            | '1' = Bit is se                                                                                                                  | t                                                                                                                   | U = Unimplen                                                                                        | nented bit, rea                                                | id as '0'                                              |            |

| bit 7-6                                           | 10 =Access  <br>x1 = Access                                                                                                                                                                        |                                                                                                                                  |                                                                                                                     |                                                                                                     | ID and Device                                                  | e ID                                                   |            |

| bit 5                                             | Unimplemer                                                                                                                                                                                         | nted: Read as                                                                                                                    | ʻ0'                                                                                                                 |                                                                                                     |                                                                |                                                        |            |

| bit 4                                             | 1 = Perform                                                                                                                                                                                        | ns an erase op                                                                                                                   | nory Erase Enal<br>eration on the n<br>nd performs a w                                                              | ext WR comm                                                                                         | and                                                            |                                                        |            |

|                                                   | or WR v<br>or WR v<br>or WR v                                                                                                                                                                      | was written to<br>was written to<br>was written to                                                                               | l'b1 when REG                                                                                                       | valid address i <1:0> and add te-protected ac                                                       | s accessed (T<br>ress do not po                                | able 4-1, Table<br>bint to the same<br>ssed (Table 4-2 | region     |

| bit 2                                             | 1 = Allows                                                                                                                                                                                         |                                                                                                                                  | able bit<br>and refresh cyo<br>erasing and use                                                                      |                                                                                                     | /M                                                             |                                                        |            |

| bit 1<br>bit 0                                    | When REG p1 = InitiatesWhen REG p1 = Initiates0 = NVM prRD: Read Co                                                                                                                                | an erase/prog<br>points to a PFM<br>the PFM write<br>rogram/erase o<br>pontrol bit <sup>(8)</sup>                                | l location:<br>operation with<br>peration is com                                                                    | e correspondin<br>data from the<br>pplete and inac                                                  | nolding registe                                                |                                                        |            |

| Note de                                           | 0 = NVM re                                                                                                                                                                                         | ad operation is                                                                                                                  | s complete and                                                                                                      |                                                                                                     | IADR, and loa                                                  | ads data into N∖                                       | INIDAT     |

| Note 1:<br>2:<br>3:<br>4:<br>5:<br>6:<br>7:<br>8: | This can only be u<br>This bit is set whe<br>completed success<br>Bit must be cleare<br>Bit may be written<br>This bit can only b<br>Operations are set<br>Once a write oper<br>The bit can only b | en WR = 1 and<br>safully.<br>ed by the user;<br>a to '1' by the u<br>be set by follow<br>elf-timed and the<br>ration is initiate | clears when the<br>hardware will n<br>ser in order to i<br>ving the unlock<br>e WR bit is clea<br>d, setting this b | ot clear this bit<br>mplement test<br>sequence of <b>S</b> o<br>ared by hardwa<br>it to zero will h | sequences.<br>ection 13.1.4<br>are when comp<br>ave no effect. | " <b>NVM Unlock</b> a<br>blete.                        | Sequence". |

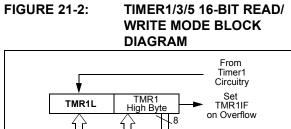

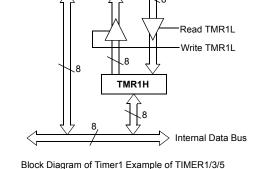

# 21.6 Timer1/3/5 Gate

Timer1/3/5 can be configured to count freely or the count can be enabled and disabled using Timer1/3/5 gate circuitry. This is also referred to as Timer1/3/5 gate enable.

Timer1/3/5 gate can also be driven by multiple selectable sources.

# 21.6.1 TIMER1/3/5 GATE ENABLE

The Timer1/3/5 Gate Enable mode is enabled by setting the TMRxGE bit of the TxGCON register. The polarity of the Timer1/3/5 Gate Enable mode is configured using the TxGPOL bit of the TxGCON register.

When Timer1/3/5 Gate Enable mode is enabled, Timer1/3/5 will increment on the rising edge of the Timer1/3/5 clock source. When Timer1/3/5 Gate signal is inactive, the timer will not increment and hold the current count. See Figure 21-4 for timing details.

# TABLE 21-2: TIMER1/3/5 GATE ENABLE SELECTIONS

| TMRxCLK    | TxGPOL | TxG | Timer1/3/5<br>Operation |

|------------|--------|-----|-------------------------|

| $\uparrow$ | 1      | 1   | Counts                  |

| $\uparrow$ | 1      | 0   | Holds Count             |

| $\uparrow$ | 0      | 1   | Holds Count             |

| $\uparrow$ | 0      | 0   | Counts                  |

#### 22.5.1 SOFTWARE GATE MODE

The timer increments with each clock input when ON = 1and does not increment when ON = 0. When the T2TMR count equals the T2PR period count the timer resets on the next clock and continues counting from 0. Operation with the ON bit software controlled is illustrated in Figure 22-4. With T2PR = 5, the counter advances until T2TMR = 5, and goes to zero with the next clock.

| MODE                          | 0b00000                                                                                                                                                                                                                                                                         |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TMRx_clk                      |                                                                                                                                                                                                                                                                                 |

| Instruction <sup>(1)</sup> —— | BCF BSF                                                                                                                                                                                                                                                                         |

| ON                            |                                                                                                                                                                                                                                                                                 |

| TxPR                          | 5                                                                                                                                                                                                                                                                               |

| TxTMR 0                       | $\left(1\right)\left(2\right)\left(3\right)\left(4\right)\left(5\right)\left(0\right)\left(1\right)\left(2\right)\left(3\right)\left(4\right)\left(5\right)\left(0\right)\left(1\right)\right) = \left(3\right)\left(4\right)\left(5\right)\left(0\right)\left(1\right)\right)$ |

| TMRx_postscaled               |                                                                                                                                                                                                                                                                                 |

| PWM Duty                      | 3                                                                                                                                                                                                                                                                               |

| PWM Output                    |                                                                                                                                                                                                                                                                                 |

#### 26.7 Rising Edge and Reverse Dead Band

In Half-Bridge mode, the rising edge dead band delays the turn-on of the CWGxA output after the rising edge of the CWG data input. In Full-Bridge mode, the reverse dead-band delay is only inserted when changing directions from Forward mode to Reverse mode, and only the modulated output CWGxB is affected.

The CWGxDBR register determines the duration of the dead-band interval on the rising edge of the input source signal. This duration is from 0 to 64 periods of the CWG clock.

Dead band is always initiated on the edge of the input source signal. A count of zero indicates that no dead band is present.

If the input source signal reverses polarity before the dead-band count is completed, then no signal will be seen on the respective output.

The CWGxDBR register value is double-buffered. When EN = 0 (Register 26-1), the buffer is loaded when CWGxDBR is written. If EN = 1, then the buffer will be loaded at the rising edge following the first falling edge of the data input, after the LD bit (Register 26-1) is set. Refer to Figure 26-12 for an example.

# 26.8 Falling Edge and Forward Dead Band

In Half-Bridge mode, the falling edge dead band delays the turn-on of the CWGxB output at the falling edge of the CWG data input. In Full-Bridge mode, the forward dead-band delay is only inserted when changing directions from Reverse mode to Forward mode, and only the modulated output CWGxD is affected.

The CWGxDBF register determines the duration of the dead-band interval on the falling edge of the input source signal. This duration is from zero to 64 periods of CWG clock.

Dead-band delay is always initiated on the edge of the input source signal. A count of zero indicates that no dead band is present.

If the input source signal reverses polarity before the dead-band count is completed, then no signal will be seen on the respective output.

The CWGxDBF register value is double-buffered. When EN = 0 (Register 26-1), the buffer is loaded when CWGxDBF is written. If EN = 1, then the buffer will be loaded at the rising edge following the first falling edge of the data input after the LD (Register 26-1) is set. Refer to Figure 26-13 for an example.

# REGISTER 28-3: NCO1ACCL: NCO1 ACCUMULATOR REGISTER – LOW BYTE

| R/W-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|----------|---------|---------|---------|---------|---------|---------|---------|--|

| ACC<7:0> |         |         |         |         |         |         |         |  |

| bit 7    |         |         |         |         |         |         | bit 0   |  |

|          |         |         |         |         |         |         |         |  |

| Legend:  |         |         |         |         |         |         |         |  |

| Logona.              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ACC<7:0>: NCO1 Accumulator, Low Byte

#### REGISTER 28-4: NCO1ACCH: NCO1 ACCUMULATOR REGISTER – HIGH BYTE

| R/W-0/0   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|-----------|---------|---------|---------|---------|---------|---------|---------|--|

| ACC<15:8> |         |         |         |         |         |         |         |  |

| bit 7     |         |         |         |         |         |         | bit 0   |  |

|           |         |         |         |         |         |         |         |  |

| Legend:   |         |         |         |         |         |         |         |  |

| Logonan              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ACC<15:8>: NCO1 Accumulator, High Byte

# 31.2.2 UART ASYNCHRONOUS RECEIVER

The Asynchronous mode is typically used in RS-232 systems. The receiver block diagram is shown in Figure 31-2. The data is received on the RX pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at 4 or 16 times the baud rate, whereas the serial Receive Shift Register (RSR) operates at the bit rate. When all bits of the character have been shifted in, they are immediately transferred to a two character First-In-First-Out (FIFO) memory. The FIFO buffering allows reception of two complete characters and the start of a third character before software must start servicing the UART receiver. The FIFO registers and RSR are not directly accessible by software. Access to the received data is via the UxRXB register.

#### 31.2.2.1 Enabling the Receiver

The UART receiver is enabled for asynchronous operation by configuring the following control bits:

- RXEN = 1

- MODE<3:0> = 0h through 3h

- UxBRGH:L = desired baud rate

- RXPPS = code for desired input pin

- Input pin ANSEL bit = 0

- ON = 1

All other UART control bits are assumed to be in their default state.

Setting the RXEN bit in the UxCON0 register enables the receiver circuitry of the UART. Setting the MODE<3:0> bits in the UxCON0 register configures the UART for the desired Asynchronous mode. Setting the ON bit in the UxCON1 register enables the UART. The TRIS bit corresponding to the selected RX I/O pin must be set to configure the pin as an input.

Note: If the RX function is on an analog pin, the corresponding ANSEL bit must be cleared for the receiver to function.

#### 31.2.2.2 Receiving Data

Data is recovered from the bit stream by timing to the center of the bits and sampling the input level. In High-Speed mode, there are four BRG clocks per bit and only one sample is taken per bit. In Normal-Speed mode, there are 16 BRG clocks per bit and three samples are taken per bit.

The receiver data recovery circuit initiates character reception on the falling edge of the Start bit. The Start bit, is always a '0'. The Start bit is qualified in the middle of the bit. In Normal-Speed mode only, the Start bit is also qualified at the leading edge of the bit. The following paragraphs describe the majority detect sampling of Normal-Speed mode.

The falling edge starts the baud rate generator (BRG) clock. The input is sampled at the first and second BRG clocks.

If both samples are high then the falling edge is deemed a glitch and the UART returns to the Start bit detection state without generating an error.

If either sample is low, the data recovery circuit continues counting BRG clocks and takes samples at clock counts 7, 8, and 9. When less than two samples are low, the Start bit is deemed invalid and the data recovery circuit aborts character reception, without generating an error, and resumes looking for the falling edge of the Start bit.

When two or more samples are low, the Start bit is deemed valid and the data recovery continues. After a valid Start bit is detected, the BRG clock counter continues and resets at count 16. This is the beginning of the first data bit.

The data recovery circuit counts BRG clocks from the beginning of the bit and takes samples at clocks 7, 8, and 9. The bit value is determined from the majority of the samples. The resulting '0' or '1' is shifted into the RSR.The BRG clock counter continues and resets at count 16. This sequence repeats until all data bits have been sampled and shifted into the RSR.

After all data bits have been shifted in, the first Stop bit is sampled. Stop bits are always a '1'. If the bit sampling determines that a '0' is in the Stop bit position, the framing error is set for this character. Otherwise, the framing error is cleared for this character. See **Section 31.2.2.4 "Receive Framing Error"** for more information on framing errors.

#### 31.2.2.3 Receive Interrupts

Immediately after all data bits and the Stop bit have been received, the character in the RSR is transferred to the UART receive FIFO. The UxRXIF interrupt flag in the respective PIR register is set at this time, provided it is not being suppressed.

The UxRXIF is suppressed by any of the following:

- FERIF if FERIE is set

- PERIF if PERIE is set

This suspends DMA transfer of data until software processes the error and reads UxRXB to advance the FIFO beyond the error.

UxRXIF interrupts are enabled by setting all of the following bits:

- UxRXIE, Interrupt Enable bit in the PIE register

- GIE, Global Interrupt Enable bits in the INTCON0

register

The UxRXIF interrupt flag bit will be set when not suppressed and there is an unread character in the FIFO, regardless of the state of interrupt enable bits. Reading the UxRXB register will transfer the top character out of the FIFO and reduce the FIFO contents by one. The UxRXIF interrupt flag bit is read-only, it cannot be set or cleared by software.

© 2017 Microchip Technology Inc.

#### 33.5.11 MASTER TRANSMISSION IN 10-BIT ADDRESSING MODE

This section describes the sequence of events for the  $I^2C$  module configured as an  $I^2C$  master in 10-bit Addressing mode and is transmitting data. Figure 33-21 is used as a visual reference for this description

1. If ABD = 0; i.e., Address buffers are enabled

Master software loads number of bytes to be transmitted in one sequence in I2CxCNT, high address byte of slave address in I2CxADB1 with R/W = 0, low address byte in I2CxADB0 and the first byte of data in I2CxTXB. Master software has to set the Start (S) bit to initiate communication.

If ABD = 1; i.e., Address buffers are disabled

Master software loads the number of bytes to be transmitted in one sequence in I2CxCNT and the high address byte of the slave address with R/W = 0 into the I2CxTXB register. Writing to the I2CxTXB will assert the start condition on the bus and sets the S bit. Software writes to the S bit are ignored in this case.

- 2. Master hardware waits for BFRE bit to be set; then shifts out the start and high address and waits for acknowledge.

- 3. If NACK, master hardware sends Stop.

- 4. If ABD = 0; i.e., Address buffer are enabled

If ACK, master hardware sends the low address byte from I2CxADB0.

If ABD = 1; i.e., Address buffer are disabled

If ACK, master hardware sets TXIF and MDR bits and the software has to write the low address byte into I2CxTXB. Writing to I2CxTXB sends the low address on the bus.

- If TXBE = 1 and I2CxCNT! = 0, I2CxTXIF and MDR bits are set. Clock is stretched on 8th falling SCL edge till master software writes next data byte to I2CxTXB.

- Master hardware sends ninth SCL pulse for ACK from slave and loads the shift register from I2CxTXB. I2CxCNT is decremented.

- 7. If slave sends a NACK, master hardware sends Stop and ends transmission.

- If slave sends an ACK, master hardware outputs data in the shift register on SDA. I2CxCNT value is checked on the 8th falling SCL edge. If I2CxCNT = 0; master hardware sends 9th SCL pulse for ACK and CNTIF is set.

- 9. If I2CxCNT != 0; go to step 5.

# EXAMPLE 34-2: WIN AND ICODE BITS USAGE IN INTERRUPT SERVICE ROUTINE TO ACCESS TX/RX BUFFERS (CONTINUED)

| ErrorInter | rrupt                     |                                        |

|------------|---------------------------|----------------------------------------|

| BCF        | PIR3, ERRIF               | ; Clear the interrupt flag             |

|            |                           | ; Handle error.                        |

| RETFIE     |                           |                                        |

| TXB2Interr | rupt                      |                                        |

| BCF        | PIR3, TXB2IF              | ; Clear the interrupt flag             |

| GOTO       | AccessBuffer              |                                        |

| TXBlInterr | rupt                      |                                        |

| BCF        | PIR3, TXB1IF              | ; Clear the interrupt flag             |

| GOTO       | AccessBuffer              |                                        |

| TXB0Interr | rupt                      |                                        |

| BCF        | PIR3, TXB0IF              | ; Clear the interrupt flag             |

| GOTO       | AccessBuffer              |                                        |

| RXBlInterr | rupt                      |                                        |

| BCF        | PIR3, RXB1IF              | ; Clear the interrupt flag             |

| GOTO       | Accessbuffer              |                                        |

| RXB0Interr | rupt                      |                                        |

| BCF        | PIR3, RXB0IF              | ; Clear the interrupt flag             |

| GOTO       | AccessBuffer              |                                        |

| AccessBuff | er                        | ; This is either TX or RX interrupt    |

| ; Copy     | CANSTAT.ICODE bits to CA  | NCON.WIN bits                          |

| MOVF       | TempCANCON, W             | ; Clear CANCON.WIN bits before copying |

|            |                           | ; new ones.                            |

| ANDLW      | B'11110001'               | ; Use previously saved CANCON value to |

|            |                           | ; make sure same value.                |

| MOVWF      | TempCANCON                | ; Copy masked value back to TempCANCON |

| MOVF       | TempCANSTAT, W            | ; Retrieve ICODE bits                  |

| ANDLW      | B'00001110'               | ; Use previously saved CANSTAT value   |

|            |                           | ; to make sure same value.             |

| IORWF      | TempCANCON                | ; Copy ICODE bits to WIN bits.         |

| MOVFF      | TempCANCON, CANCON        | ; Copy the result to actual CANCON     |

| ; Acce     | ss current buffer…        |                                        |

| ; User     | code                      |                                        |

| ; Rest     | ore CANCON.WIN bits       |                                        |

| MOVF       | CANCON, W                 | ; Preserve current non WIN bits        |

| ANDLW      | B'11110001'               |                                        |

| IORWF      | TempCANCON                | ; Restore original WIN bits            |

| ; Do n     | ot need to restore CANSTA | T - it is read-only register.          |

| ; Retu     | rn from interrupt or chec | k for another module interrupt source  |

|            |                           |                                        |

# 37.3 ADC Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 37-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), refer to Figure 37-4. **The maximum recommended impedance for analog sources is 10** k $\Omega$ . If the source impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an ADC acquisition must be completed before the conversion can be started. To calculate the minimum acquisition time, Equation 37-1 may be used. This equation assumes that 1/2 LSb error is used (4,096 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

# EQUATION 37-1: ACQUISITION TIME EXAMPLE

Assumptions: Temperature =

$$50^{\circ}C$$

and external impedance of  $10k\Omega 5.0V$  VDD

$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient$

$= TAMP + TC + TCOFF$

$= 2\mu s + TC + [(Temperature - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$

*The value for TC can be approximated with the following equations:*

$$V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) = V_{CHOLD} ; [1] V_{CHOLD} charged to within 1/2 lsb$$

$$V_{APPLIED}\left(1 - e^{\frac{-TC}{RC}}\right) = V_{CHOLD} ; [2] V_{CHOLD} charge response to V_{APPLIED} V_{APPLIED}\left(1 - e^{\frac{-TC}{RC}}\right) = V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) ; combining [1] and [2]$$

*Note:* Where n = number of bits of the ADC.

Solving for TC:

$$Tc = -C_{HOLD}(RIC + RSS + RS) \ln(1/8191)$$

=  $-28pF(1k\Omega + 7k\Omega + 10k\Omega) \ln(0.0001221)$

=  $4.54\mu s$

Therefore:

$$TACQ = 2\mu s + 4.54\mu s + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 7.79\mu s

**Note 1:** The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is  $10 \text{ k}\Omega$ . This is required to meet the pin leakage specification.

| R/W-0/0                                 | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0                                               | R/W-0/0          | R/W-0/0  | R/W-0/0 |  |

|-----------------------------------------|---------|-------------------|---------|-------------------------------------------------------|------------------|----------|---------|--|

|                                         |         |                   | STPT    | <15:8>                                                |                  |          |         |  |

| bit 7                                   |         |                   |         |                                                       |                  |          | bit 0   |  |

|                                         |         |                   |         |                                                       |                  |          |         |  |

| Legend:                                 |         |                   |         |                                                       |                  |          |         |  |

| R = Readable                            | bit     | W = Writable I    | bit     | U = Unimpler                                          | nented bit, read | d as '0' |         |  |

| u = Bit is unchanged x = Bit is unknown |         |                   | iown    | -n/n = Value at POR and BOR/Value at all other Resets |                  |          |         |  |

| '1' = Bit is set                        |         | '0' = Bit is clea | ared    |                                                       |                  |          |         |  |

#### REGISTER 37-27: ADSTPTH: ADC THRESHOLD SETPOINT REGISTER HIGH

bit 7-0 **STPT<15:8>**: ADC Threshold Setpoint MSB. Upper byte of ADC threshold setpoint, depending on ADCALC, may be used to determine ERR, see Register 37-29 for more details.

#### REGISTER 37-28: ADSTPTL: ADC THRESHOLD SETPOINT REGISTER LOW

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | STPT    | <7:0>   |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **STPT<7:0>**: ADC Threshold Setpoint LSB. Lower byte of ADC threshold setpoint, depending on ADCALC, may be used to determine ERR, see Register 37-30 for more details.

© 2017 Microchip Technology Inc.

| U-0              | U-0                                                            | U-0                                                             | R/W-0/0         | R/W-0/0          | R/W-0/0            | R/W-0/0 | R/W-0/0 |  |  |  |

|------------------|----------------------------------------------------------------|-----------------------------------------------------------------|-----------------|------------------|--------------------|---------|---------|--|--|--|

| _                | _                                                              | _                                                               |                 |                  | ACT<4:0>           |         |         |  |  |  |

| oit 7            | •                                                              |                                                                 |                 |                  |                    |         | bit     |  |  |  |

|                  |                                                                |                                                                 |                 |                  |                    |         |         |  |  |  |

| Legend:          |                                                                |                                                                 |                 |                  |                    |         |         |  |  |  |

| R = Readable     | e hit                                                          | W = Writable                                                    | oit             | U = Unimpleme    | ented bit, read as | s 'O'   |         |  |  |  |

| u = Bit is unc   |                                                                | x = Bit is unkn                                                 |                 | •                | POR and BOR/       |         | Posots  |  |  |  |

|                  | -                                                              |                                                                 |                 |                  | FOR and BORN       |         | Resels  |  |  |  |

| '1' = Bit is set |                                                                | '0' = Bit is clea                                               | ared            |                  |                    |         |         |  |  |  |

|                  |                                                                |                                                                 |                 |                  |                    |         |         |  |  |  |

| bit 7-5          |                                                                | nted: Read as '0'                                               |                 |                  |                    |         |         |  |  |  |

| bit 4-0          |                                                                | >: Auto-Conversion                                              |                 | Bits             |                    |         |         |  |  |  |

|                  | 11111 <b>= Re</b>                                              | served, do not use                                              | 9               |                  |                    |         |         |  |  |  |

|                  | •                                                              |                                                                 |                 |                  |                    |         |         |  |  |  |

|                  | •                                                              |                                                                 |                 |                  |                    |         |         |  |  |  |

|                  | 11110 <b>= Re</b>                                              | served do not use                                               | 2               |                  |                    |         |         |  |  |  |

|                  |                                                                | 11110 = Reserved, do not use<br>11101 = Software write to ADPCH |                 |                  |                    |         |         |  |  |  |

|                  | 11100 = Reserved, do not use                                   |                                                                 |                 |                  |                    |         |         |  |  |  |

|                  | 1100 - Reserved, do not use<br>11011 = Software read of ADRESH |                                                                 |                 |                  |                    |         |         |  |  |  |

|                  | 11010 = Software read of ADERRH                                |                                                                 |                 |                  |                    |         |         |  |  |  |

|                  | 11001 = CL                                                     |                                                                 |                 |                  |                    |         |         |  |  |  |

|                  | 11000 = CL                                                     |                                                                 |                 |                  |                    |         |         |  |  |  |

|                  | 10111 <b>= CL</b>                                              |                                                                 |                 |                  |                    |         |         |  |  |  |

|                  | 10110 <b>= CL</b>                                              | -                                                               |                 |                  |                    |         |         |  |  |  |

|                  |                                                                | gical OR of all Inte                                            | rrupt-on-Change | Interrupt Flags  |                    |         |         |  |  |  |

|                  | 10100 = CN                                                     | -                                                               |                 | interrupt i lage |                    |         |         |  |  |  |

|                  | 10011 = CN                                                     |                                                                 |                 |                  |                    |         |         |  |  |  |

|                  |                                                                | 10011 - CMP1_000<br>10010 = NCO1 out                            |                 |                  |                    |         |         |  |  |  |

|                  | 10001 <b>= PW</b>                                              | /M8_out                                                         |                 |                  |                    |         |         |  |  |  |

|                  | 10000 <b>= PW</b>                                              | _                                                               |                 |                  |                    |         |         |  |  |  |

|                  | 01111 <b>=</b> PW                                              |                                                                 |                 |                  |                    |         |         |  |  |  |

|                  | 01110 = PW<br>01101 = CC                                       | -                                                               |                 |                  |                    |         |         |  |  |  |

|                  | 01100 = CC                                                     |                                                                 |                 |                  |                    |         |         |  |  |  |

|                  | 01011 <b>= CC</b>                                              |                                                                 |                 |                  |                    |         |         |  |  |  |

|                  | 01010 <b>= CC</b>                                              |                                                                 |                 |                  |                    |         |         |  |  |  |

|                  | 01001 = SM                                                     |                                                                 |                 |                  |                    |         |         |  |  |  |

|                  |                                                                | R6_postscaled                                                   |                 |                  |                    |         |         |  |  |  |

|                  |                                                                | R5_overflow                                                     |                 |                  |                    |         |         |  |  |  |

|                  |                                                                | R4_postscaled<br>R3_overflow                                    |                 |                  |                    |         |         |  |  |  |

|                  |                                                                | R2_postscaled                                                   |                 |                  |                    |         |         |  |  |  |

|                  |                                                                | R1_overflow                                                     |                 |                  |                    |         |         |  |  |  |

|                  | 00010 = TM                                                     | R0_overflow                                                     |                 |                  |                    |         |         |  |  |  |

|                  |                                                                | selected by ADA                                                 |                 |                  |                    |         |         |  |  |  |

|                  | 00000 = Ext                                                    | ernal Trigger Disa                                              | bled            |                  |                    |         |         |  |  |  |

# REGISTER 37-35: ADACT: ADC AUTO-CONVERSION TRIGGER CONTROL REGISTER

# **39.2** Comparator Control

Each comparator has two control registers: CMxCON0 and CMxCON1.

The CMxCON0 register (see Register 39-1) contains Control and Status bits for the following:

- Enable

- Output

- Output polarity

- · Hysteresis enable

- Timer1 output synchronization

The CMxCON1 register (see Register 39-2) contains Control bits for the following:

· Interrupt on positive/negative edge enables

The CMxPCH and CMxNCH registers are used to select the positive and negative input channels, respectively.

# 39.2.1 COMPARATOR ENABLE

Setting the EN bit of the CMxCON0 register enables the comparator for operation. Clearing the EN bit disables the comparator resulting in minimum current consumption.

# 39.2.2 COMPARATOR OUTPUT

The output of the comparator can be monitored by reading either the CxOUT bit of the CMxCON0 register or the CxOUT bit of the CMOUT register.

The comparator output can also be routed to an external pin through the RxyPPS register (Register 17-2). The corresponding TRIS bit must be clear to enable the pin as an output.

Note 1: The internal output of the comparator is latched with each instruction cycle. Unless otherwise specified, external outputs are not latched.

# 39.2.3 COMPARATOR OUTPUT POLARITY

Inverting the output of the comparator is functionally equivalent to swapping the comparator inputs. The polarity of the comparator output can be inverted by setting the POL bit of the CMxCON0 register. Clearing the POL bit results in a noninverted output.

Table 39-1 shows the output state versus input conditions, including polarity control.

# TABLE 39-1:COMPARATOR OUTPUT<br/>STATE VS. INPUT<br/>CONDITIONS

| Input Condition | POL | CxOUT |

|-----------------|-----|-------|

| CxVN > CxVP     | 0   | 0     |

| CxVN < CxVP     | 0   | 1     |

| CxVN > CxVP     | 1   | 1     |

| CxVN < CxVP     | 1   | 0     |