#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betuns                     |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                  |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Through Hole                                                                |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 28-SPDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf25k83-e-sp |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 3-2: SUMMARY OF REGISTERS ASSOCIATED WITH CPU

| Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2   | Bit 1   | Bit 0    | Register on page |

|--------|-------|-------|-------|-------|-------|---------|---------|----------|------------------|

| ISRPR  | —     | _     | _     | _     | -     | ISRPR2  | ISRPR1  | ISRPR0   | 20               |

| MAINPR | —     | _     | _     | _     | _     | MAINPR2 | MAINPR1 | MAINPR0  | 20               |

| DMA1PR | —     | _     | _     | _     | _     | DMA1PR2 | DMA1PR1 | DMA1PR0  | 20               |

| DMA2PR | —     | _     | _     | _     | _     | DMA2PR2 | DMA2PR1 | DMA2PR0  | 21               |

| SCANPR | —     | _     | _     | _     | _     | SCANPR2 | SCANPR1 | SCANPR0  | 21               |

| PRLOCK | _     | _     | _     | _     | —     | _       | _       | PRLOCKED | 21               |

**Legend:** — = Unimplemented location, read as '0'.

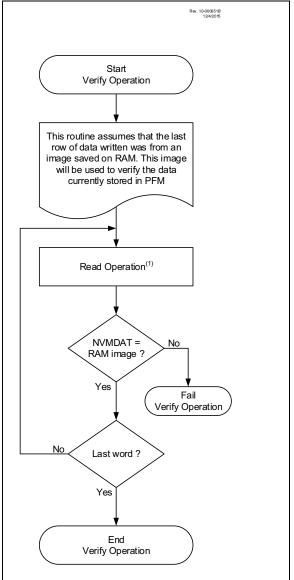

### 13.1.6.2 Write Verify

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit. Since program memory is stored as a full page, the stored program memory contents are compared with the intended data stored in RAM after the last write is complete.

#### FIGURE 13-10: PROGRAM FLASH MEMORY VERIFY FLOWCHART

## 13.1.6.3 Unexpected Termination of Write Operation

If a write is terminated by an unplanned event, such as loss of power or an unexpected Reset, the memory location just programmed should be verified and reprogrammed <u>if needed</u>. If the write operation is interrupted by a MCLR Reset or a WDT Time-out Reset during normal operation, the WRERR bit will be set which the user can check to decide whether a rewrite of the location(s) is needed.

### 13.1.6.4 Protection Against Spurious Writes

A write sequence is valid only when both the following conditions are met, this prevents spurious writes which might lead to data corruption.

- 1. The WR bit is gated through the WREN bit. It is suggested to have the WREN bit cleared at all times except during memory writes. This prevents memory writes if the WR bit gets set accidentally.

- 2. The NVM unlock sequence must be performed each time before a write operation.

# 13.2 Device Information Area, Device Configuration Area, User ID, Device ID and Configuration Word Access

When REG<1:0> = 0x01 or 0x11 in the NVMCON1 register, the Device Information Area, the Device Configuration Area, the User ID's, Device ID/ Revision ID and Configuration Words can be accessed. Different access may exist for reads and writes (see Table 13-1).

#### 13.2.1 Reading Access

The user can read from these blocks by setting the REG bits to 0x01 or 0x11. The user needs to load the address into the TBLPTR registers. Executing a TBLRD after that moves the byte pointed to the TABLAT register. The CPU operation is suspended during the read and resumes after. When read access is initiated on an address outside the parameters listed in Table 13-1, the TABLAT register is cleared, reading back '0's.

### 13.2.2 Writing Access

The WREN bit in NVMCON1 must be set to enable writes. This prevents accidental writes to the CONFIG words due to errant (unexpected) code execution. The WREN bit should be kept clear at all times, except when updating the CONFIG words. The WREN bit is not cleared by hardware. The WR bit will be inhibited from being set unless the WREN bit is set.

#### 15.9.2 DESTINATION STOP

When the Destination Stop bit is set (DSTP = 1) and the DMAxDCNT register reloads, the DMA clears the SIRQEN bit to stop receiving new start interrupt request signals and sets the DMAxDCNTIF flag.

| FIGURE 15-6:               | GPR-GPR TRANSA                           | CTIONS WIT                          | TH HARDWARE                              | TRIGGER                             | <b>S, DSTP =</b> 1 |

|----------------------------|------------------------------------------|-------------------------------------|------------------------------------------|-------------------------------------|--------------------|

| Instruction<br>Clock       |                                          | 6 7 8<br>MMMMMM                     |                                          |                                     |                    |

| EN                         |                                          |                                     |                                          |                                     |                    |

| Source Hardware<br>Trigger |                                          |                                     |                                          |                                     |                    |

| DGO                        |                                          |                                     |                                          |                                     |                    |

| DMAxSPTR                   | ()                                       | 0x101                               | 0x100                                    | 0x101                               | 0x100              |

| DMAxDPTR                   | (0x200)                                  | 0x201                               | 0x202                                    | 0x203                               | 0x200              |

| DMAxSCNT                   | 2                                        | 1                                   | 2                                        | 1                                   | 2                  |

| DMAxDCNT                   | 4                                        | 3                                   | 2                                        |                                     | 4                  |

| DMA STATE                  |                                          | SR <sup>(1)</sup> DW <sup>(2)</sup> | IDLE SR <sup>(1)</sup> DW <sup>(2)</sup> | SR <sup>(1)</sup> DW <sup>(2)</sup> | IDLE               |

| DMAxSCNTIF _               |                                          |                                     |                                          |                                     |                    |

| DMAxDCNTIF _               |                                          |                                     |                                          |                                     |                    |

|                            |                                          | MAxDSA 0x200<br>MAxDSZ 0x4          | ]                                        |                                     |                    |

|                            | R – Source Read<br>V – Destination Write |                                     |                                          |                                     |                    |

# REGISTER 15-1: DMAxCON0: DMAx CONTROL REGISTER 0

| R/W-0/0 | R/W/HC-0/0 | R/W/HS/HC-0/0 | U-0 | U-0 | R/W/HC-0/0 | U-0 | R/HS/HC-0/0 |

|---------|------------|---------------|-----|-----|------------|-----|-------------|

| EN      | SIRQEN     | DGO           | _   |     | AIRQEN     |     | XIP         |

| bit 7   |            |               |     |     |            |     | bit 0       |

| Legend:              |                  |                        |                      |

|----------------------|------------------|------------------------|----------------------|

| R = Readable bit     | W = Writable bit | U = Unimplemented bit, | read as '0'          |

| -n/n = Value at POR  |                  | 0 = bit is cleared     | x = bit is unknown   |

| and BOR/Value at all |                  |                        | u = bit is unchanged |

| other Resets         |                  |                        |                      |

| bit 7 EN: DMA Module Enable bi |

|--------------------------------|

|--------------------------------|

- 1 = Enables module

- 0 = Disables module

- SIRQEN: Start of Transfer Interrupt Request Enable bits

- 1 = Hardware triggers are allowed to start DMA transfers

- 0 = Hardware triggers are not allowed to start DMA transfers

#### bit 5 DGO: DMA transaction bit

bit 6

- 1 = DMA transaction is in progress

- 0 = DMA transaction is not in progress

- bit 4-3 Unimplemented: Read as '0'

#### bit 2 AIRQEN: Abort of Transfer Interrupt Request Enable bits

- 1 = Hardware triggers are allowed to abort DMA transfers

- 0 = Hardware triggers are not allowed to abort DMA transfers

#### bit 1 Unimplemented: Read as '0'

- bit 0 XIP: Transfer in Progress Status bit

- 1 = The DMAxBUF register currently holds contents from a read operation and has not transferred data to the destination.

- 0 = The DMAxBUF register is empty or has successfully transferred data to the destination address

# TABLE 17-2:PPS OUTPUT REGISTER<br/>DETAILS

|                          | DETAILS                 |                |              |        |  |  |

|--------------------------|-------------------------|----------------|--------------|--------|--|--|

| RxyPPS<5:0>              | Pin Rxy<br>Output       | Devid          | e Configu    | ration |  |  |

| 10x311 0x3.0×            | Source                  | PIC18(L)F2xK83 |              |        |  |  |

| 0b11 1111 -<br>0b11 0101 | Reserved                |                |              |        |  |  |

| 0b11 0101                | CANTX1                  |                | В            | С      |  |  |

| 0b11 0011                | CANTX0                  | _              | В            | C      |  |  |

| 0b11 0010                | ADGRDB                  | А              |              | c      |  |  |

| 0b11 0001                | ADGRDA                  | A              |              | c      |  |  |

| 0b11 0000                | CWG3D                   | A              |              | c      |  |  |

| 0b10 1111                | CWG3C                   | A              |              | C      |  |  |

| 0b10 1110                | CWG3B                   | A              |              | c      |  |  |

| 0b10 1101                | CWG3A                   |                | В            | c      |  |  |

| 0b10 1101                | CWG2D                   |                | В            | c      |  |  |

| 0b10 1011                | CWG2C                   |                | В            | c      |  |  |

| 0b10 1011                | CWG2B                   |                | В            | c      |  |  |

| 0b10 1010                | CWG2B<br>CWG2A          |                | В            | c      |  |  |

|                          | DSM1                    | <br>A          | D            | c      |  |  |

| 0b10 1000<br>0b10 0111   | CLKR                    | ~              |              | C      |  |  |

| 0b10 0111<br>0b10 0110   | NCO1                    |                | <del>ت</del> | c      |  |  |

|                          | TMR0                    | A              |              | c      |  |  |

| 0b10 0101                | I <sup>2</sup> C2 (SDA) |                | В            | C      |  |  |

| 0b10 0100                |                         |                |              | -      |  |  |

| 0b10 0011                | I <sup>2</sup> C2 (SCL) | _              | B            | C      |  |  |

| 0b10 0010                | I <sup>2</sup> C1 (SDA) |                | B            | C      |  |  |

| 0b10 0001                | I <sup>2</sup> C1 (SCL) |                | В            | C      |  |  |

| 0b10 0000                | SPI1 (SS)               | A              | _            | C      |  |  |

| 0b01 1111                | SPI1 (SDO)              |                | B            | C      |  |  |

| 0b01 1110                | SPI1 (SCK)              |                | В            | C      |  |  |

| 0b01 1101                | C2OUT                   | A              |              | C      |  |  |

| 0b01 1100                | C1OUT                   | A              | _            | С      |  |  |

| 0b01 1011 -<br>0b01 1001 |                         | Reserve        | ed           |        |  |  |

| 0b01 1000                | UART2 (RTS)             | _              | В            | С      |  |  |

| 0b01 0111                | UART2 (TXDE)            | _              | В            | С      |  |  |

| 0b01 0110                | UART2 (TX)              | _              | В            | С      |  |  |

| 0b01 0101                | UART1 (RTS)             | _              | В            | С      |  |  |

| 0b01 0100                | UART1 (TXDE)            | _              | В            | С      |  |  |

| 0b01 0011                | UART1 (TX)              | _              | В            | С      |  |  |

| 0b01 0010 -<br>0b01 0001 |                         | Reserve        | ed           |        |  |  |

| 0b01 0001                | PWM8                    | A              | _            | С      |  |  |

| 0b00 1111                | PWM7                    | A              |              | C      |  |  |

| 0b00 1110                | PWM6                    | A              | _            | C      |  |  |

| 0b00 1101                | PWM5                    | A              | _            | C      |  |  |

| 0b00 1100                | CCP4                    | _              | В            | C      |  |  |

| 0b00 1011                | CCP3                    | _              | В            | С      |  |  |

| 0b00 1010                | CCP2                    | _              | В            | C      |  |  |

| 0b00 1001                | CCP1                    | _              | В            | С      |  |  |

| 0b00 1000                | CWG1D                   |                | В            | С      |  |  |

| 0b00 0111                | CWG1C                   |                | В            | С      |  |  |

|                          |                         |                |              |        |  |  |

# TABLE 17-2: PPS OUTPUT REGISTER DETAILS

| D           | Pin Rxy          | Device Configuration<br>PIC18(L)F2xK83 |   |   |  |

|-------------|------------------|----------------------------------------|---|---|--|

| RxyPPS<5:0> | Output<br>Source |                                        |   |   |  |

| 0b00 0101   | CWG1A            | —                                      | В | С |  |

| 0b00 0100   | CLC4OUT          |                                        | В | С |  |

| 0b00 0011   | CLC3OUT          |                                        | В | С |  |

| 0b00 0010   | CLC2OUT          | А                                      |   | С |  |

| 0b00 0001   | CLC1OUT          | А                                      | _ | С |  |

| 0000 0000   | LATxy            | А                                      | В | С |  |

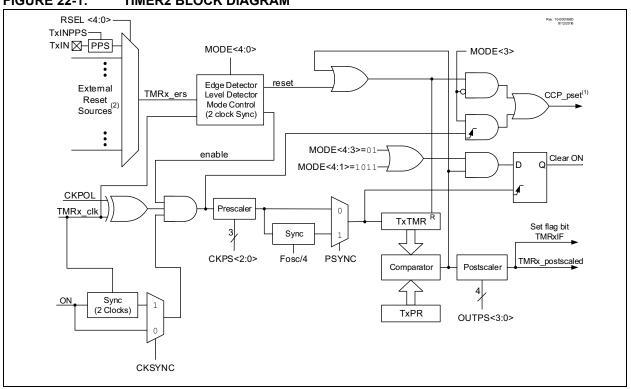

# 22.0 TIMER2/4/6 MODULE

The Timer2/4/6 modules are 8-bit timers that can operate as free-running period counters or in conjunction with external signals that control start, run, freeze, and reset operation in One-Shot and Monostable modes of operation. Sophisticated waveform control such as pulse density modulation are possible by combining the operation of these timers with other internal peripherals such as the comparators and CCP modules. Features of the timer include:

- 8-bit timer register

- 8-bit period register

- · Selectable external hardware timer resets

- Programmable prescaler (1:1 to 1:128)

- Programmable postscaler (1:1 to 1:16)

- Selectable synchronous/asynchronous operation

- · Alternate clock sources

- Interrupt on period

- Three modes of operation:

- Free Running Period

- One-Shot

- Monostable

See Figure 22-1 for a block diagram of Timer2. See Figure 22-2 for the clock source block diagram.

**Note:** Three identical Timer2 modules are implemented on this device. The timers are named Timer2, Timer4, and Timer6. All references to Timer2 apply as well to Timer4 and Timer6. All references to T2PR apply as well to T4PR and T6PR.

### FIGURE 22-1: TIMER2 BLOCK DIAGRAM

|                   | Rev. 10-001/86A<br>4/22/2016                                                                                                                                                |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SMTxWIN           |                                                                                                                                                                             |

| SMTxWIN_sync      |                                                                                                                                                                             |

| SMTx_signal       |                                                                                                                                                                             |

| SMTx_signalsync _ |                                                                                                                                                                             |

| SMTx Clock        |                                                                                                                                                                             |

| SMTxEN            |                                                                                                                                                                             |

| SMTxGO            |                                                                                                                                                                             |

| SMTxGO_sync _     |                                                                                                                                                                             |

| SMTxTMR           | $0 \qquad 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 5 \\ 1 \\ 2 \\ 3 \\ 4 \\ 5 \\ 6 \\ 7 \\ 8 \\ 9 \\ 10 \\ 11 \\ 12 \\ 13 \\ 1 \\ 2 \\ 3 \\ 1 \\ 2 \\ 1 \\ 2 \\ 1 \\ 2 \\ 1 \\ 2 \\ 1 \\ 1$ |

| SMTxCPW           | 13                                                                                                                                                                          |

| SMTxCPR           | ٨ ٩                                                                                                                                                                         |

| SMTxPWAIF         |                                                                                                                                                                             |

|                   |                                                                                                                                                                             |

|                   |                                                                                                                                                                             |

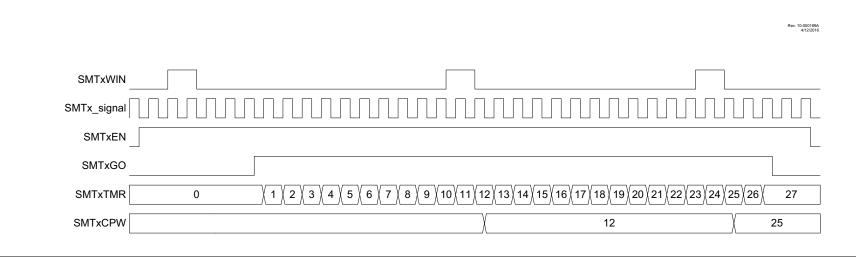

# 25.6.9 COUNTER MODE

This mode increments the timer on each pulse of the SMTx\_signal input. This mode is asynchronous to the SMT clock and uses the SMTx\_signal as a time source. The SMTxCPW register will be updated with the current SMTxTMR value on the rising edge of the SMTxWIN input. See Figure 25-18.

## FIGURE 25-18: COUNTER MODE TIMING DIAGRAM

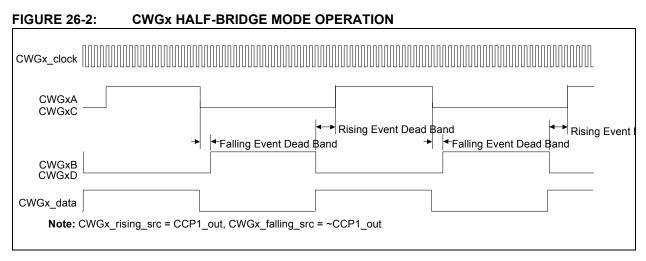

### 26.2.2 PUSH-PULL MODE

In Push-Pull mode, two output signals are generated, alternating copies of the input as illustrated in Figure 26-4. This alternation creates the push-pull effect required for driving some transformer-based power supply designs. Steering modes are not used in Push-Pull mode. A basic block diagram for the Push-Pull mode is shown in Figure 26-3.

The push-pull sequencer is reset whenever EN = 0 or if an auto-shutdown event occurs. The sequencer is clocked by the first input pulse, and the first output appears on CWGxA.

The unused outputs CWGxC and CWGxD drive copies of CWGxA and CWGxB, respectively, but with polarity controlled by the POLC and POLD bits of the CWGxCON1 register, respectively.

© 2017 Microchip Technology Inc.

Preliminary

-n/n = Value at POR and BOR/Value at all other Resets

q = Value depends on condition

| U-0          | U-0 | U-0          | R/W-0/0 | R/W-0/0      | R/W-0/0          | R/W-0/0  | R/W-0/0 |

|--------------|-----|--------------|---------|--------------|------------------|----------|---------|

| —            | —   | —            |         |              | IS<4:0>          |          |         |

| bit 7        |     |              | •       |              |                  |          | bit 0   |

|              |     |              |         |              |                  |          |         |

| Legend:      |     |              |         |              |                  |          |         |

| R = Readable | bit | W = Writable | bit     | U = Unimpler | nented bit, read | l as '0' |         |

#### REGISTER 26-4: CWGxISM: CWGx INPUT SELECTION REGISTER

#### bit 7-5 Unimplemented Read as '0'

u = Bit is unchanged

'1' = Bit is set

bit 4-0 IS<4:0>: CWG Data Input Selection Multiplexer Select bits

x = Bit is unknown

'0' = Bit is cleared

| IS<4:0>     | CWG1                       | CWG2                       | CWG3                       |

|-------------|----------------------------|----------------------------|----------------------------|

| 15<4:0>     | Input Selection            | Input Selection            | Input Selection            |

| 11111-10011 | Reserved                   | Reserved                   | Reserved                   |

| 10010       | CLC4_out                   | CLC4_out                   | CLC4_out                   |

| 10001       | CLC3_out                   | CLC3_out                   | CLC3_out                   |

| 10000       | CLC2_out                   | CLC2_out                   | CLC2_out                   |

| 01111       | CLC1_out                   | CLC1_out                   | CLC1_out                   |

| 01110       | DSM_out                    | DSM_out                    | DSM_out                    |

| 01101       | CMP2OUT                    | CMP2OUT                    | CMP2OUT                    |

| 01100       | CMP1OUT                    | CMP1OUT                    | CMP1OUT                    |

| 01011       | NCO1OUT                    | NCO10UT                    | NCO10UT                    |

| 01010-01001 | Reserved                   | Reserved                   | Reserved                   |

| 01000       | PWM8OUT                    | PWM8OUT                    | PWM8OUT                    |

| 00111       | PWM7OUT                    | PWM7OUT                    | PWM7OUT                    |

| 00110       | PWM6OUT                    | PWM6OUT                    | PWM6OUT                    |

| 00101       | PWM5OUT                    | PWM5OUT                    | PWM5OUT                    |

| 00100       | CCP4_out                   | CCP4_out                   | CCP4_out                   |

| 00011       | CCP3_out                   | CCP3_out                   | CCP3_out                   |

| 00010       | CCP2_out                   | CCP2_out                   | CCP2_out                   |

| 00001       | CCP1_out                   | CCP1_out                   | CCP1_out                   |

| 00000       | Pin selected by<br>CWG1PPS | Pin selected by<br>CWG2PPS | Pin selected by<br>CWG3PPS |

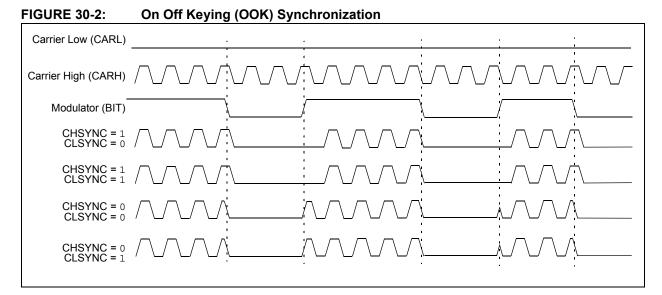

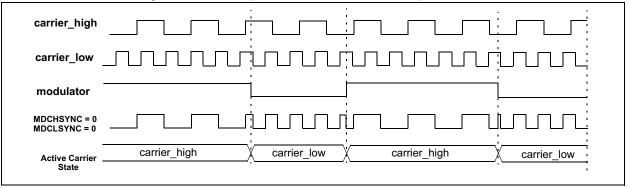

## FIGURE 30-3: No Synchronization (CHSYNC = 0, CLSYNC = 0)

### Carrier High Synchronization (CHSYNC = 1, CLSYNC = 0)

| carrier_high                 |                                                                     |

|------------------------------|---------------------------------------------------------------------|

| carrier_low                  |                                                                     |

| modulator                    |                                                                     |

| MDCHSYNC = 1<br>MDCLSYNC = 0 |                                                                     |

| Active Carrier<br>State      | carrier_high / both carrier_low / carrier_high / both \ carrier_low |

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|-------------|

|                  |         |                   | TXCH    | IK<7:0>        |                  |                  |             |

| bit 7            |         |                   |         |                |                  |                  | bit C       |

|                  |         |                   |         |                |                  |                  |             |

| Legend:          |         |                   |         |                |                  |                  |             |

| R = Readable     | bit     | W = Writable b    | oit     | U = Unimpler   | nented bit, read | 1 as '0'         |             |

| u = Bit is unch  | anged   | x = Bit is unkn   | own     | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                  |             |

# REGISTER 31-18: UxTXCHK: UART TRANSMIT CHECKSUM RESULT REGISTER

| bit 7-0 | TXCHK<7:0>: Checksum calculated from TX bytes |

|---------|-----------------------------------------------|

|         | LIN mode and C0EN = 1:                        |

|         | Sum of all transmitted bytes including PID    |

|         | LIN mode and C0EN = 0:                        |

|         | Sum of all transmitted bytes except PID       |

|         | All other modes and COEN = 1:                 |

|         | Sum of all transmitted bytes since last clear |

|         | All other modes and COEN = 0:                 |

|         | Not used                                      |

### REGISTER 31-19: UxRXCHK: UART RECEIVE CHECKSUM RESULT REGISTER

| R/W-0/0    | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|------------|---------|---------|---------|---------|---------|---------|---------|

| RXCHK<7:0> |         |         |         |         |         |         |         |

| bit 7      |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-0 | RXCHK<7:0>: Checksum calculated from RX bytes |

|---------|-----------------------------------------------|

|         | LIN mode and COEN = 1:                        |

|         | Sum of all received bytes including PID       |

|         | LIN mode and COEN = 0:                        |

|         | Sum of all received bytes except PID          |

|         | All other modes and C0EN = 1:                 |

|         | Sum of all received bytes since last clear    |

|         | All other modes and C0EN = 0:                 |

|         | Not used                                      |

# 34.15 CAN Module Registers

Note: Not all CAN registers are available in the Access Bank.

There are many control and data registers associated with the CAN module. For convenience, their descriptions have been grouped into the following sections:

- Control and Status Registers

- Dedicated Transmit Buffer Registers

- Dedicated Receive Buffer Registers

- Programmable TX/RX and Auto RTR Buffers

- Baud Rate Control Registers

- I/O Control Register

- Interrupt Status and Control Registers

Detailed descriptions of each register and their usage are described in the following sections.

#### 34.15.1 CAN CONTROL AND STATUS REGISTERS

The registers described in this section control the overall operation of the CAN module and show its operational status.

### REGISTER 34-13: RXB0CON: RECEIVE BUFFER 0 CONTROL REGISTER (CONTINUED)

| bit 2 | Mode 0:<br><b>RB0DBEN:</b> Receive Buffer 0 Double-Buffer Enable bit                                                                |

|-------|-------------------------------------------------------------------------------------------------------------------------------------|

|       | 1 = Receive Buffer 0 overflow will write to Receive Buffer 1<br>0 = No Receive Buffer 0 overflow to Receive Buffer 1                |

|       | Mode 1, 2:<br>FILHIT<4:0>: Filter Hit bit 2                                                                                         |

|       | This bit combines with other bits to form filter acceptance bits<4:0>.                                                              |

| bit 1 | Mode 0:<br>JTOFF: Jump Table Offset bit (read-only copy of RXB0DBEN) <sup>(2)</sup>                                                 |

|       | 1 = Allows jump table offset between 6 and 7                                                                                        |

|       | 0 = Allows jump table offset between 1 and 0                                                                                        |

|       | <u>Mode 1, 2:</u>                                                                                                                   |

|       | FILHIT<4:0>: Filter Hit bit 1                                                                                                       |

|       | This bit combines with other bits to form filter acceptance bits<4:0>.                                                              |

| bit 0 |                                                                                                                                     |

|       | <b>FILHIT0:</b> Filter Hit bit 0<br>This bit indicates which acceptance filter enabled the message reception into Receive Buffer 0. |

|       | 1 = Acceptance Filter 1 (RXF1)                                                                                                      |

|       | 0 = Acceptance Filter 0 (RXF0)                                                                                                      |

|       | Mode 1, 2:                                                                                                                          |

|       | FILHIT<4:0>: Filter Hit bit 0                                                                                                       |

|       | This bit, in combination with FILHIT<4:1>, indicates which acceptance filter enabled the message reception                          |

|       | into this receive buffer.                                                                                                           |

|       | 01111 = Acceptance Filter 15 (RXF15)                                                                                                |

|       | 01110 = Acceptance Filter 14 (RXF14)                                                                                                |

|       | 00000 = Acceptance Filter 0 (RXF0)                                                                                                  |

- **Note 1:** This bit is set by the CAN module upon receiving a message and must be cleared by software after the buffer is read. As long as RXFUL is set, no new message will be loaded and the buffer will be considered full. After clearing the RXFUL flag, the PIR5 bit, RXB0IF, can be cleared. If RXB0IF is cleared, but RXFUL is not cleared, then RXB0IF is set again.

- **2:** This bit allows the same filter jump table for both RXB0CON and RXB1CON.

# 37.2.5 AUTO-CONVERSION TRIGGER

The auto-conversion trigger allows periodic ADC measurements without software intervention. When a rising edge of the selected source occurs, the GO bit is set by hardware.

The auto-conversion trigger source is selected by the ADACT register.

Using the auto-conversion trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met. See Register 37-33 for auto-conversion sources.

#### 37.2.6 ADC CONVERSION PROCEDURE (BASIC MODE)

This is an example procedure for using the ADC to perform an analog-to-digital conversion:

- 1. Configure Port:

- Disable pin output driver (Refer to the TRISx register)

- Configure pin as analog (Refer to the ANSELx register)

- 2. Configure the ADC module:

- Select ADC conversion clock

- Select voltage reference

- · Select ADC input channel

# **EXAMPLE 37-1: ADC CONVERSION** /\*This code block configures the ADC

for polling, VDD and VSS references, FRC

```

Precharge and acquisition

```

- Turn on ADC module

- 3. Configure ADC interrupt (optional):

- Clear ADC interrupt flag

- Enable ADC interrupt

- Enable global interrupt (GIEL bit)<sup>(1)</sup>

- If ADACQ = 0, software must wait the required acquisition time<sup>(2)</sup>.

- 5. Start conversion by setting the GO bit.

- 6. Wait for ADC conversion to complete by one of the following:

- Polling the GO bit

- Polling the ADIF bit

- Waiting for the ADC interrupt (interrupts enabled)

- 7. Read ADC Result.

- 8. Clear the ADC interrupt flag (required if interrupt is enabled).

- **Note 1:** The global interrupt can be disabled if the user is attempting to wake-up from Sleep and resume in-line code execution.

- 2: Refer to Section 37.3 "ADC Acquisition Requirements".

oscillator and ANO input. Conversion start & polling for completion are included. \* / void main() { //System Initialize initializeSystem(); //Setup ADC ADCON0bits.FM = 1; //right justify ADCONObits.CS = 1; //FRC Clock ADPCH =  $0 \times 00$ ; //RAO is Analog channel TRISAbits.TRISA0 = 1; //Set RA0 to input ANSELAbits.ANSELA0 = 1; //Set RA0 to analog ADCONObits.ON = 1; //Turn ADC On while (1) { ADCONObits.GO = 1; //Start conversion while (ADCONObits.GO); //Wait for conversion done resultHigh = ADRESH; //Read result resultLow = ADRESL; //Read result }

}

**Branch if Not Zero**

$(PC) + 2 + 2n \rightarrow PC$

0001

incremented to fetch the next instruction, the new address will be

If the ZERO bit is '0', then the program

The 2's complement number '2n' is added to the PC. Since the PC will have

nnnn

nnnn

BNZ n

None 1110

will branch.

$-128 \le n \le 127$ if ZERO bit is '0'

| BNOV                                                                                     | Branch if                                                                 | Not Overflo                                                                             | w               | BNZ                                                                                        |

|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------|

| Syntax:                                                                                  | BNOV n                                                                    |                                                                                         |                 | Syntax:                                                                                    |

| Operands:                                                                                | -128 ≤ n ≤ 1                                                              | 27                                                                                      |                 | Operands:                                                                                  |

| Operation:                                                                               | if OVERFLO<br>(PC) + 2 + 2                                                |                                                                                         |                 | Operation:                                                                                 |

| Status Affected:                                                                         | None                                                                      |                                                                                         |                 | Status Affected:                                                                           |

| Encoding:                                                                                | 1110                                                                      | 0101 nni                                                                                | nn nnnn         | Encoding:                                                                                  |

| Description:                                                                             | program wil<br>The 2's con<br>added to the<br>incremented<br>instruction, | nplement num<br>e PC. Since th<br>d to fetch the r<br>the new addre<br>n. This instruct | Description:    |                                                                                            |

| Words:                                                                                   | 1                                                                         |                                                                                         |                 | Words:                                                                                     |

| Cycles:                                                                                  | 1(2)                                                                      |                                                                                         |                 | Cycles:                                                                                    |

| Q Cycle Activity:<br>If Jump:                                                            |                                                                           |                                                                                         |                 | Q Cycle Activity:<br>If Jump:                                                              |

| Q1                                                                                       | Q2                                                                        | Q3                                                                                      | Q4              | Q1                                                                                         |

| Decode                                                                                   | Read literal<br>'n'                                                       | Process<br>Data                                                                         | Write to PC     | Decode F                                                                                   |

| No<br>operation                                                                          | No<br>operation                                                           | No<br>operation                                                                         | No<br>operation | No<br>operation                                                                            |

| If No Jump:                                                                              |                                                                           |                                                                                         |                 | If No Jump:                                                                                |

| Q1                                                                                       | Q2                                                                        | Q3                                                                                      | Q4              | Q1                                                                                         |

| Decode                                                                                   | Read literal<br>'n'                                                       | Process<br>Data                                                                         | No<br>operation | Decode F                                                                                   |

| Example:<br>Before Instruc<br>PC<br>After Instructio<br>If OVERF<br>PC<br>If OVERF<br>PC | = ado<br>n<br>FLOW = 0;<br>= ado<br>FLOW = 1;                             | BNOV Jump<br>dress (HERE<br>dress (Jump<br>dress (HERE                                  | )               | Example:<br>Before Instructio<br>PC<br>After Instruction<br>If ZERO<br>PC<br>If ZERO<br>PC |

PC + 2 + 2n. This instruction is then a 2-cycle instruction. 1 1(2) Q3 Q2 Q4 Read literal Process Write to PC 'n' Data No No No operation operation operation Q2 Q3 Q4 Read literal Process No 'n' Data operation HERE BNZ Jump on address (HERE) = = 0;

address (Jump)

1; address (HERE + 2)

=

=

=

| INFS        | SNZ                                             | Increment f, skip if not 0                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                      |                         |  |  |  |

|-------------|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|--|--|

| Synta       | ax:                                             | INFSNZ f                                                                                                                                                                                                                                                                            | INFSNZ f {,d {,a}}                                                                                                                                                                                                                                                                                                                                                                   |                         |  |  |  |

| Oper        | ands:                                           | $0 \leq f \leq 255$                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                      |                         |  |  |  |

|             |                                                 | d ∈ [0,1]<br>a ∈ [0,1]                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                      |                         |  |  |  |

| Oper        | ation:                                          | (f) + 1 $\rightarrow$ de skip if resul                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                      |                         |  |  |  |

| Ctat        | s Affected:                                     | None                                                                                                                                                                                                                                                                                | <b>1</b> ≠ 0                                                                                                                                                                                                                                                                                                                                                                         |                         |  |  |  |

|             |                                                 |                                                                                                                                                                                                                                                                                     | 101 550                                                                                                                                                                                                                                                                                                                                                                              |                         |  |  |  |

|             | ding:<br>cription:                              | 0100                                                                                                                                                                                                                                                                                | 10da fff<br>ts of register 'f                                                                                                                                                                                                                                                                                                                                                        |                         |  |  |  |

| Word        |                                                 | placed in W<br>placed back<br>If the result<br>instruction,<br>discarded a<br>instead, ma<br>instruction.<br>If 'a' is '0', tt<br>If 'a' is '0', tt<br>If 'a' is '0', tt<br>GPR bank.<br>If 'a' is '0' a<br>set is enabl<br>in Indexed I<br>mode when<br>tion 42.2.3<br>Oriented Ir | If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the GPR bank.<br>If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever $f \le 95$ (5Fh). See Section 42.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode" for details.<br>1 |                         |  |  |  |

| -           |                                                 | Note: 3 d                                                                                                                                                                                                                                                                           | cycles if skip a a 2-word instr                                                                                                                                                                                                                                                                                                                                                      |                         |  |  |  |

| QC          | ycle Activity:                                  |                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                      |                         |  |  |  |

|             | Q1                                              | Q2                                                                                                                                                                                                                                                                                  | Q3                                                                                                                                                                                                                                                                                                                                                                                   | Q4                      |  |  |  |

|             | Decode                                          | Read<br>register 'f'                                                                                                                                                                                                                                                                | Process<br>Data                                                                                                                                                                                                                                                                                                                                                                      | Write to<br>destination |  |  |  |

| lf sk       | in:                                             | register i                                                                                                                                                                                                                                                                          | Dala                                                                                                                                                                                                                                                                                                                                                                                 | destination             |  |  |  |

| ii on       | Q1                                              | Q2                                                                                                                                                                                                                                                                                  | Q3                                                                                                                                                                                                                                                                                                                                                                                   | Q4                      |  |  |  |

|             | No                                              | No                                                                                                                                                                                                                                                                                  | No                                                                                                                                                                                                                                                                                                                                                                                   | No                      |  |  |  |

|             | operation                                       | operation                                                                                                                                                                                                                                                                           | -                                                                                                                                                                                                                                                                                                                                                                                    | operation               |  |  |  |

| lf sk       | ip and followe                                  |                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                      |                         |  |  |  |

|             | Q1                                              | Q2                                                                                                                                                                                                                                                                                  | Q3                                                                                                                                                                                                                                                                                                                                                                                   | Q4                      |  |  |  |

|             | No                                              | No                                                                                                                                                                                                                                                                                  | No                                                                                                                                                                                                                                                                                                                                                                                   | No                      |  |  |  |

|             | operation                                       | operation                                                                                                                                                                                                                                                                           | operation                                                                                                                                                                                                                                                                                                                                                                            | operation               |  |  |  |

|             | No                                              | No                                                                                                                                                                                                                                                                                  | No                                                                                                                                                                                                                                                                                                                                                                                   | No                      |  |  |  |

|             | operation                                       | operation                                                                                                                                                                                                                                                                           | operation                                                                                                                                                                                                                                                                                                                                                                            | operation               |  |  |  |

| <u>Exar</u> | Example: HERE INFSNZ REG, 1, 0<br>ZERO<br>NZERO |                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                      |                         |  |  |  |

|             | Before Instruc                                  | tion                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                      |                         |  |  |  |

|             | PC                                              |                                                                                                                                                                                                                                                                                     | (HERE)                                                                                                                                                                                                                                                                                                                                                                               |                         |  |  |  |

|             | After Instruction<br>REG                        | on<br>= REG + 1                                                                                                                                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                                                                                                    |                         |  |  |  |

|             | If REG                                          | - REG+<br>≠ 0;                                                                                                                                                                                                                                                                      | I                                                                                                                                                                                                                                                                                                                                                                                    |                         |  |  |  |

|             | PC<br>If REG                                    | = Address<br>= 0;                                                                                                                                                                                                                                                                   | <b>3</b> (NZERO)                                                                                                                                                                                                                                                                                                                                                                     |                         |  |  |  |

|             | PC                                              |                                                                                                                                                                                                                                                                                     | (ZERO)                                                                                                                                                                                                                                                                                                                                                                               |                         |  |  |  |

|             |                                                 |                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                      |                         |  |  |  |

| IORLW             | Inclusive           | OR lite                                                                               | ral with | w          |  |  |

|-------------------|---------------------|---------------------------------------------------------------------------------------|----------|------------|--|--|

| Syntax:           | IORLW k             |                                                                                       |          |            |  |  |

| Operands:         | $0 \le k \le 255$   | 5                                                                                     |          |            |  |  |

| Operation:        | (W) .OR. k          | $\rightarrow W$                                                                       |          |            |  |  |

| Status Affected:  | N, Z                |                                                                                       |          |            |  |  |

| Encoding:         | 0000                | 1001                                                                                  | kkkk     | kkkk       |  |  |

| Description:      |                     | The contents of W are ORed with the 8-<br>bit literal 'k'. The result is placed in W. |          |            |  |  |

| Words:            | 1                   |                                                                                       |          |            |  |  |

| Cycles:           | 1                   |                                                                                       |          |            |  |  |

| Q Cycle Activity: |                     |                                                                                       |          |            |  |  |

| Q1                | Q2                  | Q3                                                                                    |          | Q4         |  |  |

| Decode            | Read<br>literal 'k' | Proce<br>Data                                                                         |          | Write to W |  |  |

|                   | •                   | •                                                                                     |          |            |  |  |

| Example:          | IORLW               | 35h                                                                                   |          |            |  |  |

| Before Instruc    | ction               |                                                                                       |          |            |  |  |

| W                 | = 9Ah               |                                                                                       |          |            |  |  |

BFh

=

After Instruction W

| RET        | FIE                                                                                                                | Return fro                                                                                                                                                                                                      | om Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | :                                                                     |  |  |  |

|------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--|--|--|

| Synta      | ax:                                                                                                                | RETFIE {s                                                                                                                                                                                                       | RETFIE {s}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                       |  |  |  |

| Oper       | ands:                                                                                                              | s ∈ [0,1]                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                       |  |  |  |

| Operation: |                                                                                                                    | if s = 1, con<br>STATUS, B<br>FSR1H, FS<br>PRODH, PI<br>PCLATU re                                                                                                                                               | $(TOS) \rightarrow PC$ ,<br>if s = 1, context is restored into WREG,<br>STATUS, BSR, FSR0H, FSR0L,<br>FSR1H, FSR1L, FSR2H, FSR2L,<br>PRODH, PRODL, PCLATH and<br>PCLATU registers from the<br>corresponding shadow registers.                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                       |  |  |  |