Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                  |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf25k83-i-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC18(L)F25/26K83

| U-0                | U-0                                 | R/W-0/0                                                                                                     | R/W-0/0                                   | R/W-0/0        | R/W-0/0          | R/W-0/0        | R/W-0/0      |

|--------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------|----------------|------------------|----------------|--------------|

| _                  |                                     |                                                                                                             |                                           | TUN            | <5:0>            |                |              |

| bit 7              |                                     |                                                                                                             |                                           |                |                  |                | bit C        |

| Legend:            |                                     |                                                                                                             |                                           |                |                  |                |              |

| R = Readabl        | le bit                              | W = Writable                                                                                                | bit                                       | U = Unimplen   | nented bit, read | d as '0'       |              |

| u = Bit is und     | changed                             | x = Bit is unkr                                                                                             | nown                                      | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is se    | et                                  | '0' = Bit is clea                                                                                           | ared                                      |                |                  |                |              |

| bit 7-6<br>bit 5-0 | TUN<5:0>:<br>01 1111 =<br>00 0000 = | nted: Read as '<br>HFINTOSC Free<br>Maximum freque<br>Center frequenc<br>(default value).<br>Minimum freque | quency Tuning<br>ency<br>:y. Oscillator n |                | g at the calibra | ited frequency |              |

#### 9.8 Interrupt Setup Procedure

1. When using interrupt priority levels, set the IPEN bit in INTCON0 register and then select the user-assigned priority level for the interrupt source by writing the control bits in the appropriate IPRx Control register.

| Note: | At a device Reset, the IPRx registers are |

|-------|-------------------------------------------|

|       | initialized, such that all user interrupt |

|       | sources are assigned to high priority.    |

- 2. Clear the Interrupt Flag Status bit associated with the peripheral in the associated PIRx Status register.

- 3. Enable the interrupt source by setting the interrupt enable control bit associated with the source in the appropriate PIEx Control register.

- If the vector table is used (MVECEN = 1), then setup the start address for the Interrupt Vector Table using the IVTBASE register. See Section 9.2.2 "Interrupt Vector Table Contents".

- 5. Once the IVTBASE is written to, set the Interrupt enable bits in INTCON0 register.

- An example of setting up interrupts and ISRs using assembly and C can be found in Examples 9-3 and 9-4.

#### 9.9 External Interrupt Pins

The PIC18(L)F26/27/45/46/47/55/56/57K42 devices have three external interrupt sources which can be assigned to any pin on different ports based on the PPS settings. Refer Section 17.0 "Peripheral Pin Select (PPS) Module" for possible rerouting options. The external interrupt sources are edge-triggered. If the corresponding INTxEDG bit in the INTCON0 register is set (= 1), the interrupt is triggered by a rising edge. If the bit is clear, the trigger is on the falling edge.

When a valid edge appears on the INTx pin, the corresponding flag bit, INTxF in the PIRx registers, is set. This interrupt can be disabled by clearing the corresponding enable bit, INTxE. Flag bit, INTxF, must be cleared by software in the Interrupt Service Routine before re-enabling the interrupt.

All external interrupts (INT0, INT1 and INT2) can wakeup the processor from Idle or Sleep modes if bit INTxE was set prior to going into those modes. If the Global Interrupt Enable bit, GIE/GIEH, is set, the processor will branch to the interrupt vector following wake-up. Interrupt priority is determined by the value contained in the interrupt priority bits, INT0IP, INT1IP and INT2IP of the IPRx registers.

#### 9.10 Wake-up from Sleep

The interrupt controller provides a wake-up request to the CPU whenever an interrupt event occurs, if the interrupt event is enabled. This occurs regardless of whether the part is in Run, Idle/Doze or Sleep modes. The status of the GIEH/GIEL bits has no effect on the wake-up request. The wake-up request will be asynchronous to all clocks.

#### 9.11 Interrupt Compatibility

When the MVECEN bit in Configuration Word 2L is cleared (Register 5-3), the Interrupt Vector Table feature is disabled and interrupts are compatible with previous high performance 8-bit PIC18 microcontroller devices. In this mode, the Interrupt Vector Table priority has no effect.

When the IPEN bit is also cleared, the interrupt priority feature is disabled and interrupts are compatible with PIC<sup>®</sup>16 microcontroller mid-range devices. All interrupts branch to address 0008h since the interrupt priority is disabled.

| R/W-1/1                 | R/W-1/1                                                         | R/W-1/1           | R/W-1/1          | R/W-1/1         | R/W-1/1          | R/W-1/1          | R/W-1/1     |  |  |  |

|-------------------------|-----------------------------------------------------------------|-------------------|------------------|-----------------|------------------|------------------|-------------|--|--|--|

| TMR5IP                  | INT2IP                                                          | CLC2IP            | CWG2IP           | CCP2IP          | TMR4IP           | TMR3GIP          | TMR3IP      |  |  |  |

| bit 7                   |                                                                 |                   |                  |                 |                  |                  | bit (       |  |  |  |

|                         |                                                                 |                   |                  |                 |                  |                  |             |  |  |  |

| Legend:<br>R = Readable | , hit                                                           | W = Writable      | hit              | II – I Inimpler | nented bit, read | 1 ac 'O'         |             |  |  |  |

| u = Bit is uncl         |                                                                 | x = Bit is unki   |                  | •               |                  | R/Value at all o | thar Resets |  |  |  |

| '1' = Bit is set        | •                                                               | '0' = Bit is cle  |                  |                 |                  |                  |             |  |  |  |

|                         |                                                                 |                   | areu             |                 |                  |                  |             |  |  |  |

| bit 7                   | TMR5IP: TM                                                      | IR5 Interrupt Pr  | ority bit        |                 |                  |                  |             |  |  |  |

|                         | 1 = High pri                                                    | •                 |                  |                 |                  |                  |             |  |  |  |

|                         | 0 = Low price                                                   | ority             |                  |                 |                  |                  |             |  |  |  |

| bit 6                   | INT2IP: Exte                                                    | ernal Interrupt 2 | Interrupt Prior  | ity bit         |                  |                  |             |  |  |  |

|                         | 1 = High pri                                                    | •                 |                  |                 |                  |                  |             |  |  |  |

|                         | 0 = Low price                                                   | •                 |                  |                 |                  |                  |             |  |  |  |

| bit 5                   | CLC2IP: CLC2 Interrupt Priority bit                             |                   |                  |                 |                  |                  |             |  |  |  |

|                         | <ul> <li>1 = High priority</li> <li>0 = Low priority</li> </ul> |                   |                  |                 |                  |                  |             |  |  |  |

| bit 4                   | CWG2IP: CWG2 Interrupt Priority bit                             |                   |                  |                 |                  |                  |             |  |  |  |

|                         | 1 = High pri                                                    |                   |                  |                 |                  |                  |             |  |  |  |

|                         | 0 = Low pric                                                    |                   |                  |                 |                  |                  |             |  |  |  |

| bit 3                   | CCP2IP: CC                                                      | P2 Interrupt Pri  | ority bit        |                 |                  |                  |             |  |  |  |

|                         | 1 = High pri                                                    | •                 |                  |                 |                  |                  |             |  |  |  |

|                         | 0 = Low price                                                   | •                 |                  |                 |                  |                  |             |  |  |  |

| bit 2                   |                                                                 | 1R4 Interrupt Pr  | ority bit        |                 |                  |                  |             |  |  |  |

|                         | 1 = High priority<br>0 = Low priority                           |                   |                  |                 |                  |                  |             |  |  |  |

| bit 1                   | -                                                               | MR3 Gate Inter    | runt Priority hi | t               |                  |                  |             |  |  |  |

|                         | 1 = High pri                                                    |                   | rupt i nonty bi  | L               |                  |                  |             |  |  |  |

|                         | 0 = Low price                                                   |                   |                  |                 |                  |                  |             |  |  |  |

| bit 0                   | TMR3IP: TM                                                      | IR3 Interrupt Pr  | ority bit        |                 |                  |                  |             |  |  |  |

|                         | 1 = High pri                                                    | •                 | -                |                 |                  |                  |             |  |  |  |

|                         | 0 = Low price                                                   | ority             |                  |                 |                  |                  |             |  |  |  |

#### REGISTER 9-31: IPR8: PERIPHERAL INTERRUPT PRIORITY REGISTER 8

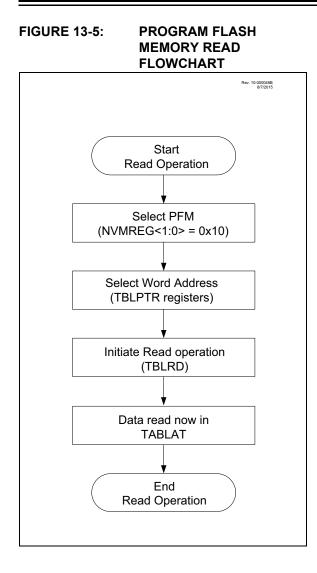

#### 13.0 NONVOLATILE MEMORY (NVM) CONTROL

Nonvolatile Memory (NVM) is separated into two types: Program Flash Memory (PFM) and Data EEPROM Memory.

PFM, Data EEPROM, User IDs and Configuration bits can all be accessed using the REG<1:0> bits of the NVMCON1 register.

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the operating voltage range of the device.

NVM can be protected in two ways, by either code protection or write protection. Code protection (CP and CPD bits in Configuration Word 5L) disables access, reading and writing to both PFM and Data EEPROM Memory via external device programmers. Code protection does not affect the self-write and erase functionality. Code protection can only be reset by a device programmer performing a Bulk Erase to the device, clearing all nonvolatile memory, Configuration bits and User IDs.

Write protection prohibits self-write and erase to a portion or all of the PFM, as defined by the WRT bits of Configuration Word 4H. Write protection does not affect a device programmer's ability to read, write or erase the device.

|                                           | PC<20:0>                                         | Execution        |     | User Access                   | ;                             |

|-------------------------------------------|--------------------------------------------------|------------------|-----|-------------------------------|-------------------------------|

| Memory                                    | ICSP™ Addr<21:0><br>TBLPTR<21:0><br>NVMADDR<9:0> | CPU<br>Execution | REG | TABLAT                        | NVMDAT                        |

| Program Flash Memory<br>(PFM)             | 00 0000h<br>•••<br>01 FFFFh                      | Read             | 10  | Read/<br>Write <sup>(1)</sup> | (3)                           |

| User IDs <sup>(2)</sup>                   | 20 0000h<br>•••<br>20 000Fh                      | No Access        | xl  | Read/<br>Write                | (3)                           |

| Reserved                                  | 20 0010h<br>2F FFFFh                             | No Access        |     | (3)                           |                               |

| Configuration                             | 30 0000h<br>•••<br>30 0009h                      | No Access        | xl  | Read/<br>Write <sup>(1)</sup> | (3)                           |

| Reserved                                  | 30 000Ah<br>30 FFFFh                             | No Access        | (3) |                               |                               |

| User Data Memory<br>(Data EEPROM)         | 31 0000h<br>•••<br>31 03FFh                      | No Access        | 00  | (3)                           | Read/<br>Write <sup>(1)</sup> |

| Reserved                                  | 31 0400h<br>3E FFFFh                             | No Access        |     | (3)                           |                               |

| Device Information Area<br>(DIA)          | 3F 0000h<br>•••<br>3F 003Fh                      | No Access        | xl  | Read                          | (3)                           |

| Reserved                                  | 3F 0040h<br>3F FF09h                             | No Access        |     | (3)                           |                               |

| Device Configuration Information<br>(DCI) | 3F FF00h<br>•••<br>3F FF09h                      | No Access        | xl  | Read                          | (3)                           |

| Reserved                                  | 3F FF0Ah<br>3F FFFBh                             | No Access        | (3) |                               |                               |

| Revision ID/<br>Device ID                 | 3F FFFCh<br>•••<br>3F FFFFh                      | No Access        | x1  | Read                          | (3)                           |

#### TABLE 13-1: NVM ORGANIZATION AND ACCESS INFORMATION

Note 1: Subject to Memory Write Protection settings.

2: User IDs are eight words ONLY. There is no code protection, table read protection or write protection implemented for this region.

3: Reads as '0', writes clear the WR bit and WRERR bit is set.

## PIC18(L)F25/26K83

#### REGISTER 14-9: CRCXORH: CRC XOR HIGH BYTE REGISTER

| R/W-x/x         | R/W-x/x | R/W-x/x         | R/W-x/x | R/W-x/x        | R/W-x/x          | R/W-x/x          | R/W-x/x     |

|-----------------|---------|-----------------|---------|----------------|------------------|------------------|-------------|

|                 |         |                 | X<1     | 5:8>           |                  |                  |             |

| bit 7           |         |                 |         |                |                  |                  | bit 0       |

|                 |         |                 |         |                |                  |                  |             |

| Legend:         |         |                 |         |                |                  |                  |             |

| R = Readable    | bit     | W = Writable    | bit     | U = Unimpler   | nented bit, read | as '0'           |             |

| u = Bit is unch | anged   | x = Bit is unkr | nown    | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |

bit 7-0 X<15:8>: XOR of Polynomial Term X<sup>n</sup> Enable bits

#### REGISTER 14-10: CRCXORL: CRC XOR LOW BYTE REGISTER

'0' = Bit is cleared

| R/W-x/x | U-1   |

|---------|---------|---------|---------|---------|---------|---------|-------|

|         |         |         | X<7:1>  |         |         |         | —     |

| bit 7   |         |         |         |         |         |         | bit 0 |

|         |         |         |         |         |         |         |       |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit                                 |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-1 X<7:1>: XOR of Polynomial Term X<sup>n</sup> Enable bits

bit 0 Unimplemented: Read as '1'

'1' = Bit is set

#### REGISTER 15-21: DMAxDCNTH: DMAx DESTINATION COUNT HIGH REGISTER

| U-0   | U-0 | U-0 | U-0 | R-0        | R-0 | R-0 | R-0   |  |

|-------|-----|-----|-----|------------|-----|-----|-------|--|

| —     | —   | —   | —   | DCNT<11:8> |     |     |       |  |

| bit 7 |     |     |     |            |     |     | bit 0 |  |

# Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n/n = Value at POR and 1 = bit is set 0 = bit is cleared x = bit is unknown BOR/Value at all other u = bit is unchanged u = bit is unchanged

bit 7-4 Unimplemented: Read as '0'

bit 3-0 DCNT<11:8>: Current Destination Byte Count

#### REGISTER 15-22: DMAxSIRQ: DMAx START INTERRUPT REQUEST SOURCE SELECTION REGISTER

| U-0   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0   | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|---------|---------|---------|-----------|---------|---------|---------|

| _     |         |         |         | SIRQ<6:0> |         |         |         |

| bit 7 |         |         |         |           |         |         | bit 0   |

| Legend:                                                     |                  |                        |                                            |

|-------------------------------------------------------------|------------------|------------------------|--------------------------------------------|

| R = Readable bit                                            | W = Writable bit | U = Unimplemented bit, | read as '0'                                |

| -n/n = Value at POR<br>and BOR/Value at all<br>other Resets | 1 = bit is set   | 0 = bit is cleared     | x = bit is unknown<br>u = bit is unchanged |

#### bit 7 Unimplemented: Read as '0'

bit 6-0 **SIRQ<6:0>:** DMAx Start Interrupt Request Source Selection bits Please refer to Table 15-2 for more information.

#### REGISTER 15-23: DMAxAIRQ: DMAx ABORT INTERRUPT REQUEST SOURCE SELECTION REGISTER

| U-0   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0   | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|---------|---------|---------|-----------|---------|---------|---------|

|       |         |         |         | AIRQ<6:0> |         |         |         |

| bit 7 |         |         |         |           |         |         | bit 0   |

| Legend:                                                     |                  |                           |                                            |

|-------------------------------------------------------------|------------------|---------------------------|--------------------------------------------|

| R = Readable bit                                            | W = Writable bit | U = Unimplemented bit, re | ad as '0'                                  |

| -n/n = Value at POR<br>and BOR/Value at all<br>other Resets | 1 = bit is set   | 0 = bit is cleared        | x = bit is unknown<br>u = bit is unchanged |

bit 7 Unimplemented: Read as '0'

bit 6-0 **AIRQ<6:0>:** DMAx Interrupt Request Source Selection bits Please refer to Table 15-2 for more information.

| R/W-1/1          | R/W-1/1                               | R/W-1/1          | R/W-1/1 | R/W-1/1                            | R/W-1/1 | R/W-1/1 | R/W-1/1 |  |  |  |  |

|------------------|---------------------------------------|------------------|---------|------------------------------------|---------|---------|---------|--|--|--|--|

| ANSELx7          | ANSELx6                               | ANSELx5          | ANSELx4 | ANSELx3                            | ANSELx2 | ANSELx1 | ANSELx0 |  |  |  |  |

| bit 7            |                                       |                  |         |                                    |         |         | bit 0   |  |  |  |  |

|                  |                                       |                  |         |                                    |         |         |         |  |  |  |  |

| Legend:          | Legend:                               |                  |         |                                    |         |         |         |  |  |  |  |

| R = Readable bit |                                       | W = Writable bit |         | U = Unimplemented bit, read as '0' |         |         |         |  |  |  |  |

| '1' = Bit is set | '1' = Bit is set '0' = Bit is cleared |                  |         | x = Bit is unknown                 |         |         |         |  |  |  |  |

#### REGISTER 16-4: ANSELX: ANALOG SELECT REGISTER

bit 7-0

ANSELx<7:0>: Analog Select on Pins Rx<7:0>

- 1 = Digital Input buffers are disabled.

- 0 = ST and TTL input devices are enabled

#### TABLE 16-5: ANALOG SELECT PORT REGISTERS

-n/n = Value at POR and BOR/Value at all other Resets

| Name   | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|--------|---------|---------|---------|---------|---------|---------|---------|---------|

| ANSELA | ANSELA7 | ANSELA6 | ANSELA5 | ANSELA4 | ANSELA3 | ANSELA2 | ANSELA1 | ANSELA0 |

| ANSELB | ANSELB7 | ANSELB6 | ANSELB5 | ANSELB4 | ANSELB3 | ANSELB2 | ANSELB1 | ANSELB0 |

| ANSELC | ANSELC7 | ANSELC6 | ANSELC5 | ANSELC4 | ANSELC3 | ANSELC2 | ANSELC1 | ANSELC0 |

#### FIGURE 25-6: PERIOD AND DUTY-CYCLE REPEAT ACQUISITION MODE TIMING DIAGRAM

-n/n = Value at POR and BOR/Value at all other Resets

q = Value depends on condition

| U-0                             | U-0 | U-0 | R/W-0/0 | R/W-0/0      | R/W-0/0          | R/W-0/0 | R/W-0/0 |

|---------------------------------|-----|-----|---------|--------------|------------------|---------|---------|

| —                               | —   | —   |         |              | IS<4:0>          |         |         |

| bit 7                           |     |     |         |              |                  |         | bit 0   |

|                                 |     |     |         |              |                  |         |         |

| Legend:                         |     |     |         |              |                  |         |         |

| R = Readable bit W = Writable b |     |     | bit     | U = Unimpler | mented bit, read | as '0'  |         |

#### REGISTER 26-4: CWGxISM: CWGx INPUT SELECTION REGISTER

#### bit 7-5 Unimplemented Read as '0'

u = Bit is unchanged

'1' = Bit is set

bit 4-0 IS<4:0>: CWG Data Input Selection Multiplexer Select bits

x = Bit is unknown

'0' = Bit is cleared

| IS<4:0>     | CWG1                       | CWG2                       | CWG3                       |

|-------------|----------------------------|----------------------------|----------------------------|

| 15<4:0>     | Input Selection            | Input Selection            | Input Selection            |

| 11111-10011 | Reserved                   | Reserved                   | Reserved                   |

| 10010       | CLC4_out                   | CLC4_out                   | CLC4_out                   |

| 10001       | CLC3_out                   | CLC3_out                   | CLC3_out                   |

| 10000       | CLC2_out                   | CLC2_out                   | CLC2_out                   |

| 01111       | CLC1_out                   | CLC1_out                   | CLC1_out                   |

| 01110       | DSM_out                    | DSM_out                    | DSM_out                    |

| 01101       | CMP2OUT                    | CMP2OUT                    | CMP2OUT                    |

| 01100       | CMP1OUT                    | CMP1OUT                    | CMP1OUT                    |

| 01011       | NCO1OUT                    | NCO10UT                    | NCO10UT                    |

| 01010-01001 | Reserved                   | Reserved                   | Reserved                   |

| 01000       | PWM8OUT                    | PWM8OUT                    | PWM8OUT                    |

| 00111       | PWM7OUT                    | PWM7OUT                    | PWM7OUT                    |

| 00110       | PWM6OUT                    | PWM6OUT                    | PWM6OUT                    |

| 00101       | PWM5OUT                    | PWM5OUT                    | PWM5OUT                    |

| 00100       | CCP4_out                   | CCP4_out                   | CCP4_out                   |

| 00011       | CCP3_out                   | CCP3_out                   | CCP3_out                   |

| 00010       | CCP2_out                   | CCP2_out                   | CCP2_out                   |

| 00001       | CCP1_out                   | CCP1_out                   | CCP1_out                   |

| 00000       | Pin selected by<br>CWG1PPS | Pin selected by<br>CWG2PPS | Pin selected by<br>CWG3PPS |

#### 27.0 CONFIGURABLE LOGIC CELL (CLC)

The Configurable Logic Cell (CLCx) module provides programmable logic that operates outside the speed limitations of software execution. The logic cell takes up to 32 input signals and, through the use of configurable gates, reduces the 32 inputs to four logic lines that drive one of eight selectable single-output logic functions.

Input sources are a combination of the following:

- · I/O pins

- Internal clocks

- · Peripherals

- Register bits

The output can be directed internally to peripherals and to an output pin.

There are four CLC modules available on this device - CLC1, CLC2, CLC3 and CLC4.

Note: The CLC1, CLC2, CLC3 and CLC4 are four separate module instances of the same CLC module design. Throughout this section, the lower case 'x' in register names is a generic reference to the CLC number (which should be substituted with 1, 2, 3, or 4 during code development). For example, the control register is generically described in this chapter as CLCxCON, but the actual device registers are CLC1CON, CLC2CON, CLC3CON and CLC4CON.

Refer to Figure 27-1 for a simplified diagram showing signal flow through the CLCx.

Possible configurations include:

- Combinatorial Logic

- AND

- NAND

- AND-OR

- AND-OR-INVERT

- OR-XOR

- OR-XNOR

- Latches

- S-R

- Clocked D with Set and Reset

- Transparent D with Set and Reset

© 2017 Microchip Technology Inc.

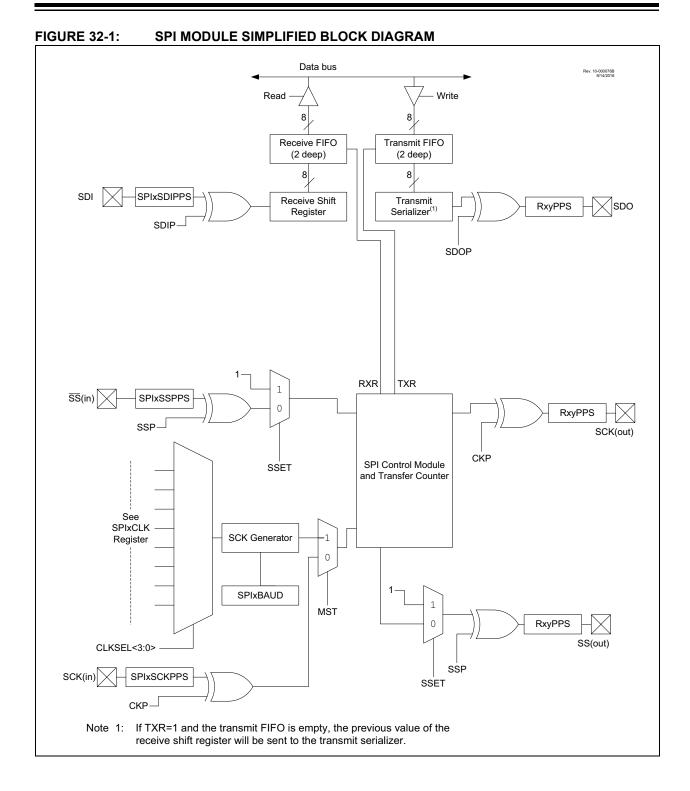

#### 32.7 SPI Operation in Sleep Mode

SPI Master mode will operate in Sleep, provided the clock source selected by SPIxCLK is active in Sleep mode. FIFOs will operate as they would when the part is awake. When TXR = 1, the TXFIFO will need to contain data in order for transfers to take place in Sleep. All interrupts will still set the interrupt flags in Sleep but only enabled interrupts will wake the device from Sleep.

SPI Slave mode will operate in Sleep, because the clock is provided by an external master device. FIFOs will still operate and interrupts will set interrupt flags, and enabled interrupts will wake the device from Sleep.

#### 32.8 SPI Interrupts

There are three top level SPI interrupts in the PIRx register:

- SPI Transmit

- SPI Receive

- · SPI Module status

The status interrupts are enabled at the module level in the SPIxINTE register. Only enabled status interrupts will cause the single top level SPIxIF flag to be set.

#### 32.8.1 SPI RECEIVER DATA INTERRUPT

The SPI Receiver Data Interrupt is set when RXFIFO contains data, and is cleared when the RXFIFO is empty. The interrupt flag SPI1RXIF is located in PIRx and the interrupt enable SPI1RXIE is located in PIEx. This interrupt flag is read-only.

#### 32.8.2 SPI TRANSMITTER DATA INTERRUPT

The SPI Transmitter Data Interrupt is set when TXFIFO is not full, and is cleared when the TXFIFO is full. The interrupt flag SPI1TXIF is located in PIRx and the interrupt enable SPI1TXIE is located in PIEx. The interrupt flag is read-only.

#### 32.8.3 SPI MODULE STATUS INTERRUPTS

The SPIxIF flag in the respective PIR register is set when any of the individual status flags in SPIxINTF and their respective SPIxINTE bits are set. In order for the setting of any specific interrupt flag to interrupt normal program flow both the SPIxIE bit as well as the specific bit in SPIxINTE associated with that interrupt must be set.

The Status Interrupts are:

- Shift Register Empty Interrupt

- Transfer Counter is Zero Interrupt

- Start of Slave Select Interrupt

- · End of Slave Select Interrupt

- · Receiver Overflow Interrupt

- Transmitter Underflow Interrupt

# PIC18(L)F25/26K83

HC = Hardware clear

| R/W-x/u                 | R/W-x/u | R/W-x/u      | R/W-x/u | R/W-x/u      | R/W-x/u          | R/W-x/u       | R/W-x/u |

|-------------------------|---------|--------------|---------|--------------|------------------|---------------|---------|

| ADB7                    | ADB6    | ADB5         | ADB4    | ADB3         | ADB2             | ADB1          | ADB0    |

| bit 7                   |         |              |         |              |                  |               | bit 0   |

|                         |         |              |         |              |                  |               |         |

|                         |         |              |         |              |                  |               |         |

| Legend:                 |         |              |         |              |                  |               |         |

| Legend:<br>R = Readable | bit     | W = Writable | bit     | U = Unimplen | nented bit, read | <b>as</b> '0' |         |

HS = Hardware set

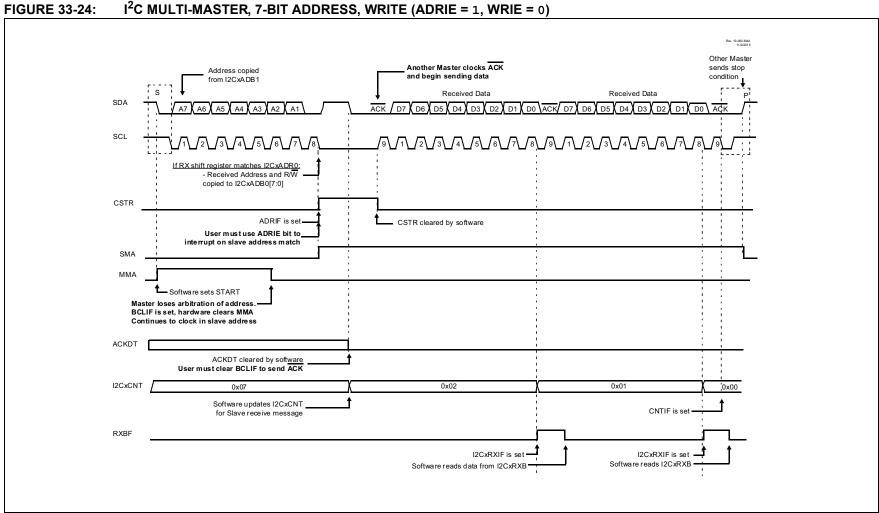

#### REGISTER 33-16: I2CxADB0: I<sup>2</sup>C ADDRESS DATA BUFFER 0 REGISTER<sup>(1)</sup>

'0' = Bit is cleared

| bit 7-0 | <u>MODE&lt;2:0&gt; = 00x</u>                                    |

|---------|-----------------------------------------------------------------|

|         | ADB<7:1>: Address Data byte                                     |

|         | Received matching 7-bit slave address data                      |

|         | R/W: Read/not-Write Data bit                                    |

|         | Received read/write value from 7-bit address byte               |

|         | MODE<2:0> = 01x                                                 |

|         | ADB<7:0>: Address Data byte                                     |

|         | Received matching lower eight bits of 10-bit slave address data |

|         | MODE<2:0> = 100                                                 |

|         | Unused in this mode; bit state is a "don't care"                |

|         | MODE<2:0> = 101                                                 |

|         | ADB<7:0>: Low Address Data byte                                 |

|         | Low 10-bit address value copied to transmit shift register      |

|         | MODE<2:0> = 11x                                                 |

|         | ADB<7:1>: Address Data byte                                     |

|         | Received matching 7-bit slave address                           |

|         | R/W: Read/not-Write Data bit                                    |

|         | Received read/write value received 7-bit slave address byte     |

|         |                                                                 |

#### Note 1: This register is read only except in master, 10-bit Address mode (MODE<2:0> = 101).

'1' = Bit is set

#### 34.2.4 LISTEN ONLY MODE

Listen Only mode provides a means for the CAN module to receive all messages, including messages with errors. This mode can be used for bus monitor applications or for detecting the baud rate in 'hot plugging' situations. For auto-baud detection, it is necessary that there are at least two other nodes which are communicating with each other. The baud rate can be detected empirically by testing different values until valid messages are received. The Listen Only mode is a silent mode, meaning no messages will be transmitted while in this state, including error flags or Acknowledge signals. In Listen Only mode, both valid and invalid messages will be received, regardless of RXMn bit settings. The filters and masks can still be used to allow only particular valid messages to be loaded into the Receive registers, or the filter masks can be set to all zeros to allow a message with any identifier to pass. All invalid messages will be received in this mode, regardless of filters and masks or RXMn Receive Buffer mode bits. The error counters are reset and deactivated in this state. The Listen Only mode is activated by setting the mode request bits in the CANCON register to 0b011.

#### 34.2.5 LOOPBACK MODE

This mode will allow internal transmission of messages from the transmit buffers to the receive buffers without actually transmitting messages on the CAN bus. This mode can be used in system development and testing. In this mode, the ACK bit is ignored and the device will allow incoming messages from itself, just as if they were coming from another node. The Loopback mode is a silent mode, meaning no messages will be transmitted while in this state, including error flags or Acknowledge signals. The TXCAN pin will revert to port I/O while the device is in this mode. The filters and masks can be used to allow only particular messages to be loaded into the receive registers. The masks can be set to all zeros to provide a mode that accepts all messages. The Loopback mode is activated by setting the mode request bits in the CANCON register to 0b010.

#### 34.2.6 ERROR RECOGNITION MODE

The module can be set to ignore all errors and receive any message. In functional Mode 0, the Error Recognition mode is activated by setting the RXM<1:0> bits in the RXBnCON registers to '11'. In this mode, the data which is in the message assembly buffer until the error time, is copied in the receive buffer and can be read via the CPU interface.

#### 34.3 CAN Module Functional Modes

In addition to CAN modes of operation, the CAN module offers a total of three functional modes. Each of these modes are identified as Mode 0, Mode 1 and Mode 2.

#### 34.3.1 MODE 0 – LEGACY MODE

Mode 0 is designed to be fully compatible with CAN modules used in PIC18CXX8 and PIC18FXX8 devices. This is the default mode of operation on all Reset conditions. As a result, module code written for the PIC18XX8 CAN module may be used on the CAN module with only very minor code changes.

The following is the list of resources available in Mode 0:

- Three transmit buffers: TXB0, TXB1 and TXB2

- Two receive buffers: RXB0 and RXB1

- Two acceptance masks, one for each receive buffer: RXM0, RXM1

- Six acceptance filters, 2 for RXB0 and 4 for RXB1: RXF0, RXF1, RXF2, RXF3, RXF4, RXF5

#### 34.3.2 MODE 1 – ENHANCED LEGACY MODE

Mode 1 is similar to Mode 0, with the exception that more resources are available in Mode 1. There are 16 acceptance filters and two acceptance mask registers. Acceptance Filter 15 can be used as either an acceptance filter or an acceptance mask register. In addition to three transmit and two receive buffers, there are six more message buffers. One or more of these additional buffers can be programmed as transmit or receive buffers. These additional buffers can also be programmed to automatically handle RTR messages.

Fourteen of sixteen acceptance filter registers can be dynamically associated to any receive buffer and acceptance mask register. One can use this capability to associate more than one filter to any one buffer.

When a receive buffer is programmed to use standard identifier messages, part of the full acceptance filter register can be used as a data byte filter. The length of the data byte filter is programmable from 0 to 18 bits. This functionality simplifies implementation of high-level protocols, such as the DeviceNet<sup>™</sup> protocol.

The following is the list of resources available in Mode 1:

- Three transmit buffers: TXB0, TXB1 and TXB2

- Two receive buffers: RXB0 and RXB1

- · Six buffers programmable as TX or RX: B0-B5

- · Automatic RTR handling on B0-B5

- Sixteen dynamically assigned acceptance filters: RXF0-RXF15

- Two dedicated acceptance mask registers; RXF15 programmable as third mask: RXM0-RXM1, RXF15

- · Programmable data filter on standard identifier

### 34.15.3.1 Programmable TX/RX and Auto-RTR Buffers

The ECAN module contains six message buffers that can be programmed as transmit or receive buffers. Any of these buffers can also be programmed to automatically handle RTR messages.

**Note:** These registers are not used in Mode 0.

## REGISTER 34-22: BnCON: TX/RX BUFFER 'n' CONTROL REGISTERS IN RECEIVE MODE $[0 \le n \le 5, TXnEN (BSEL0 < n >) = 0]^{(1)}$

| R/W-0                | R/W-0 | R-0     | R-0     | R-0     | R-0     | R-0     | R-0     |

|----------------------|-------|---------|---------|---------|---------|---------|---------|

| RXFUL <sup>(2)</sup> | RXM1  | RXRTRRO | FILHIT4 | FILHIT3 | FILHIT2 | FILHIT1 | FILHIT0 |

| bit 7                |       |         |         |         |         |         | bit 0   |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 7   | RXFUL: Receive Full Status bit <sup>(2)</sup>                                                                                                                                 |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = Receive buffer contains a received message                                                                                                                                |

|         | 0 = Receive buffer is open to receive a new message                                                                                                                           |

| bit 6   | RXM1: Receive Buffer Mode bit                                                                                                                                                 |

|         | <ul> <li>1 = Receive all messages including partial and invalid (acceptance filters are ignored)</li> <li>0 = Receive all valid messages as per acceptance filters</li> </ul> |

| bit 5   | RXRTRRO: Read-Only Remote Transmission Request for Received Message bit                                                                                                       |

|         | 1 = Received message is a remote transmission request                                                                                                                         |

|         | 0 = Received message is not a remote transmission request                                                                                                                     |

| bit 4-0 | FILHIT<4:0>: Filter Hit bits                                                                                                                                                  |

|         | These bits indicate which acceptance filter enabled the last message reception into this buffer.                                                                              |

|         | 01111 = Acceptance Filter 15 (RXF15)                                                                                                                                          |

|         | 01110 = Acceptance Filter 14 (RXF14)                                                                                                                                          |

|         |                                                                                                                                                                               |

|         | 00001 = Acceptance Filter 1 (RXF1)                                                                                                                                            |

|         | 00000 = Acceptance Filter 0 (RXF0)                                                                                                                                            |

|         |                                                                                                                                                                               |

- **Note 1:** These registers are available in Mode 1 and 2 only.

- 2: This bit is set by the CAN module upon receiving a message and must be cleared by software after the buffer is read. As long as RXFUL is set, no new message will be loaded and the buffer will be considered full.

| bit 7 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as 'C                                                           | RSEG1 PRSEG0                                                               |  |  |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as 'C                                                              |                                                                            |  |  |  |  |  |  |  |  |  |

|                                                                                                                                             | bit (                                                                      |  |  |  |  |  |  |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as 'C                                                                         |                                                                            |  |  |  |  |  |  |  |  |  |

|                                                                                                                                             | )'                                                                         |  |  |  |  |  |  |  |  |  |

|                                                                                                                                             | ,<br>Bit is unknown                                                        |  |  |  |  |  |  |  |  |  |

|                                                                                                                                             |                                                                            |  |  |  |  |  |  |  |  |  |

| bit 7 SEG2PHTS: Phase Segment 2 Time Select bit                                                                                             |                                                                            |  |  |  |  |  |  |  |  |  |

| 1 = Freely programmable                                                                                                                     |                                                                            |  |  |  |  |  |  |  |  |  |

| 0 = Maximum of PHEG1 or Information Processing Time (IPT), whichever is g                                                                   | greater                                                                    |  |  |  |  |  |  |  |  |  |

| ·                                                                                                                                           | SAM: Sample of the CAN bus Line bit                                        |  |  |  |  |  |  |  |  |  |

| <ul> <li>1 = Bus line is sampled three times prior to the sample point</li> <li>0 = Bus line is sampled once at the sample point</li> </ul> |                                                                            |  |  |  |  |  |  |  |  |  |

|                                                                                                                                             |                                                                            |  |  |  |  |  |  |  |  |  |

|                                                                                                                                             | SEG1PH<2:0>: Phase Segment 1 bits                                          |  |  |  |  |  |  |  |  |  |

| 110 = Phase Segment 1 time = 7 x TQ                                                                                                         | 111 = Phase Segment 1 time = 8 x TQ                                        |  |  |  |  |  |  |  |  |  |

| 101 = Phase Segment 1 time = 6 x TQ                                                                                                         |                                                                            |  |  |  |  |  |  |  |  |  |

| 100 = Phase Segment 1 time = 5 x TQ                                                                                                         |                                                                            |  |  |  |  |  |  |  |  |  |

| 011 = Phase Segment 1 time = 4 x TQ                                                                                                         | 011 = Phase Segment 1 time = 4 x TQ                                        |  |  |  |  |  |  |  |  |  |

| 5                                                                                                                                           | 010 = Phase Segment 1 time = 3 x To                                        |  |  |  |  |  |  |  |  |  |

|                                                                                                                                             | 001 = Phase Segment 1 time = 2 x TQ<br>000 = Phase Segment 1 time = 1 x TQ |  |  |  |  |  |  |  |  |  |

|                                                                                                                                             |                                                                            |  |  |  |  |  |  |  |  |  |

|                                                                                                                                             | PRSEG<2:0>: Propagation Time Select bits                                   |  |  |  |  |  |  |  |  |  |

|                                                                                                                                             | 111 = Propagation time = 8 x TQ<br>110 = Propagation time = 7 x TQ         |  |  |  |  |  |  |  |  |  |

|                                                                                                                                             | $101 = Propagation time = 6 \times TQ$                                     |  |  |  |  |  |  |  |  |  |

| $100 = Propagation time = 5 \times TQ$                                                                                                      |                                                                            |  |  |  |  |  |  |  |  |  |

| 011 = Propagation time = 4 x TQ                                                                                                             |                                                                            |  |  |  |  |  |  |  |  |  |

| 010 = Propagation time = $3 \times T_Q$                                                                                                     |                                                                            |  |  |  |  |  |  |  |  |  |

| $001 = Propagation time = 2 \times TQ$                                                                                                      |                                                                            |  |  |  |  |  |  |  |  |  |

| $000 = Propagation time = 1 \times TQ$                                                                                                      |                                                                            |  |  |  |  |  |  |  |  |  |

#### REGISTER 34-53: BRGCON2: BAUD RATE CONTROL REGISTER 2

| REGISTER 40-2: HEVDCONT. LOW-VOLTAGE DETECT CONTROL REGISTER 1 |     |     |     |          |         |         |         |  |

|----------------------------------------------------------------|-----|-----|-----|----------|---------|---------|---------|--|

| U-0                                                            | U-0 | U-0 | U-0 | R/W-0/u  | R/W-0/u | R/W-0/u | R/W-0/u |  |

| _                                                              | —   | _   | _   | SEL<3:0> |         |         |         |  |

| bit 7                                                          |     |     |     |          |         |         | bit 0   |  |

#### REGISTER 40-2: HLVDCON1: LOW-VOLTAGE DETECT CONTROL REGISTER 1

| Legend:           |                  |                       |                      |

|-------------------|------------------|-----------------------|----------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'       |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | u = Bit is unchanged |

#### bit 7-4 Unimplemented: Read as '0'

bit 3-0

SEL<3:0>: High/Low Voltage Detection Limit Selection bits

| SEL<3:0> | Typical Voltage |

|----------|-----------------|

| 1111     | Reserved        |

| 1110     | 4.65V           |

| 1101     | 4.35V           |

| 1100     | 4.20V           |

| 1011     | 4.00V           |

| 1010     | 3.75V           |

| 1001     | 3.60V           |

| 1000     | 3.35V           |

| 0111     | 3.15V           |

| 0110     | 2.90V           |

| 0101     | 2.75V           |

| 0100     | 2.60V           |

| 0011     | 2.50V           |

| 0010     | 2.25V           |

| 0001     | 2.10V           |

| 0000     | 1.90V           |

## TABLE 40-2: SUMMARY OF REGISTERS ASSOCIATED WITH HIGH/LOW-VOLTAGE DETECT MODULE MODULE

| Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3    | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |

|----------|-------|-------|-------|-------|----------|-------|-------|-------|---------------------|

| HLVDCON0 | EN    | _     | OUT   | RDY   | _        | -     | INTH  | INTL  | 709                 |

| HLVDCON1 | -     | -     | -     | -     | SEL<3:0> |       |       |       | 710                 |

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the HLVD module.

| Addr           | Name             | Bit 7      | Bit 6                 | Bit 5  | Bit 4         | Bit 3   | Bit 2   | Bit 1        | Bit 0   | Register<br>on page |  |

|----------------|------------------|------------|-----------------------|--------|---------------|---------|---------|--------------|---------|---------------------|--|

| 3880h          | STATUS_CSHAD     | _          | TO                    | PD     | N             | OV      | Z       | DC           | С       | 47                  |  |

| 387Fh          |                  |            |                       |        |               |         |         |              |         |                     |  |

| -<br>3800h     | —                |            |                       |        | Unimpler      | nented  |         |              |         | -                   |  |

| 37FFh          | CANCON_RO0       | CANCON_RO0 |                       |        |               |         |         |              |         |                     |  |

| 37FEh          | CANSTAT_RO0      |            |                       |        | CANSTA        | _       |         |              |         | 603<br>604          |  |

| 37FDh          | RXB1D7           |            |                       |        | RXB1          |         |         |              |         | 620                 |  |

| 37FCh          | RXB1D6           |            |                       |        | RXB1          |         |         |              |         | 620                 |  |

| 37FBh          | RXB1D5           |            |                       |        | RXB1          |         |         |              |         | 620                 |  |

| 37FAh          | RXB1D4           |            |                       |        | RXB1          |         |         |              |         | 620                 |  |

| 37F9h          | RXB1D3           |            |                       |        | RXB1          |         |         |              |         | 620                 |  |

| 37F8h          | RXB1D2           |            |                       |        | RXB1          |         |         |              |         | 620                 |  |

| 37F7h          | RXB1D1           |            |                       |        | RXB1          |         |         |              |         | 620                 |  |

| 37F6h          | RXB1D0           |            |                       |        | RXB1          |         |         |              |         | 620                 |  |

| 37F5h          | RXB1DLC          | _          | RXRTR                 | RB1    | R0            | DLC3    | DLC2    | DLC1         | DLC0    | 620                 |  |

| 37F4h          | RXB1EIDL         | EID7       | EID6                  | EID5   | EID4          | EID3    | EID2    | EID1         | EID0    | 619                 |  |

| 37F3h          | RXB1EIDH         | EID15      | EID14                 | EID13  | EID4<br>EID12 | EID11   | EID10   | EID9         | EID8    | 619                 |  |

| 37F2h          | RXB1SIDL         | SID2       | SID1                  | SID0   | SRR           | EXID    |         | EID17        | EID16   | 619                 |  |

| 37F1h          | RXB1SIDH         | SID10      | SID9                  | SID8   | SID7          | SID6    | SID5    | SID4         | SID3    | 618                 |  |

| 37F0h          | RXB1CON          | RXFUL      | RXM1                  | RXM0   |               | RXRTRRO | FILHIT2 | FILHIT1      | FILHITO | 617                 |  |

| 37F0h          | RXB1CON          |            | 1                     |        | FILHIT4       |         |         |              |         | 617                 |  |

| 37EFh          | CANCON_RO1       |            |                       |        |               |         |         |              |         |                     |  |

| 37EEh          | CANSTAT_RO1      |            | CANCON_RO1            |        |               |         |         |              |         |                     |  |

| 37EDh          | TXB0D7           |            | CANSTAT_RO1<br>TXB0D7 |        |               |         |         |              |         |                     |  |

| 37ECh          | TXB0D6           |            |                       |        |               |         |         |              |         | 611<br>611          |  |

| 37EBh          | TXB0D5           |            | TXB0D6                |        |               |         |         |              |         | 611                 |  |

| 37EAh          | TXB0D4           |            | TXB0D5<br>TXB0D4      |        |               |         |         |              |         | 611                 |  |

| 37E9h          | TXB0D3           |            |                       |        | ТХВС          |         |         |              |         | 611                 |  |

| 37E8h          | TXB0D2           |            |                       |        | ТХВС          |         |         |              |         | 611                 |  |

| 37E7h          | TXB0D2           |            |                       |        | ТХВС          |         |         |              |         | 611                 |  |

| 37E6h          | TXB0D0           |            |                       |        | ТХВС          |         |         |              |         | 611                 |  |

| 37E5h          | TXB0DLC          |            | TXRTR                 | _      |               | DLC3    | DLC2    | DLC1         | DLC0    | 612                 |  |

| 37E4h          | TXB0EIDL         | EID7       | EID6                  | EID5   | EID4          | EID3    | EID2    | EID1         | EID0    | 611                 |  |

| 37E3h          | TXB0EIDE         | EID15      | EID14                 | EID13  | EID4<br>EID12 | EID11   | EID10   | EID1<br>EID9 | EID8    | 610                 |  |

| 37E2h          | TXB0SIDL         | SID2       | SID1                  | SID0   |               | EXIDE   |         | EID3         | EID16   | 610                 |  |

| 37E1h          | TXBOSIDE         | SID10      | SID1                  | SID8   | SID7          | SID6    | SID5    | SID4         | SID3    | 610                 |  |

| 37E0h          | TXB0CON          | TXBIF      | TXABT                 | TXLARB | TXERR         | TXREQ   | 0100    | TXPRI1       | TXPRI0  | 609                 |  |

| 37DFh          | CANCON RO2       | TADII      | IXADI                 | TALAND | CANCO         |         |         |              |         | 603                 |  |

| 37DEh          | CANSTAT RO2      |            |                       |        | CANCO         | -       |         |              |         | 604                 |  |

| 37DDh          | TXB1D7           |            |                       |        |               | -       |         |              |         | 611                 |  |

| 37DCh          | TXB1D7<br>TXB1D6 |            | TXB1D7<br>TXB1D6      |        |               |         |         |              |         |                     |  |

| 37DCh<br>37DBh | TXB1D6<br>TXB1D5 |            |                       |        | TXB1          |         |         |              |         | 611<br>611          |  |

| 37DBh<br>37DAh | TXB1D5<br>TXB1D4 |            |                       |        | TXB1          |         |         |              |         | 611                 |  |

| 37DAn<br>37D9h | TXB1D4<br>TXB1D3 |            |                       |        | TXB1          |         |         |              |         | 611                 |  |

| 37D9h<br>37D8h | TXB1D3<br>TXB1D2 |            |                       |        |               |         |         |              |         |                     |  |

|                | 1                | TXB1D2     |                       |        |               |         |         |              |         | 611                 |  |

| 37D7h          | TXB1D1           | TXB1D1     |                       |        |               |         |         |              |         | 611                 |  |

| 37D6h          | TXB1D0           | TXB1D0     |                       |        |               |         |         | 611          |         |                     |  |

| 37D5h          | TXB1DLC          |            | TXRTR                 |        |               | DLC3    | DLC2    | DLC1         | DLC0    | 612                 |  |

| 37D4h          | TXB1EIDL         | EID7       | EID6                  | EID5   | EID4          | EID3    | EID2    | EID1         | EID0    | 611                 |  |

| 37D3h          | TXB1EIDH         | EID15      | EID14                 | EID13  | EID12         | EID11   | EID10   | EID9         | EID8    | 610                 |  |

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition

Note 1: Not present in LF devices.