Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

•XF

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 64MHz                                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                   |

| Number of I/O              | 25                                                                           |

| Program Memory Size        | 32KB (16K x 16)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 1K x 8                                                                       |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-VQFN Exposed Pad                                                          |

| Supplier Device Package    | 28-QFN (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf25k83t-i-ml |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| R-q/q           | R-q/q     | R-q/q                                     | R-q/q           | R-q/q             | R-q/q            | U-0            | R-q/q        |

|-----------------|-----------|-------------------------------------------|-----------------|-------------------|------------------|----------------|--------------|

| EXTOR           | HFOR      | MFOR                                      | LFOR            | SOR               | ADOR             | —              | PLLR         |

| bit 7           |           |                                           |                 |                   |                  |                | bit (        |

|                 |           |                                           |                 |                   |                  |                |              |

| Legend:         |           |                                           |                 |                   |                  |                |              |

| R = Readable    |           | W = Writable                              | bit             | •                 | mented bit, read |                |              |

| u = Bit is unc  | hanged    | x = Bit is unk                            | nown            | -n/n = Value      | at POR and BO    | R/Value at all | other Resets |

| '1' = Bit is se | t         | '0' = Bit is cle                          | ared            | q = Reset va      | lue is determine | d by hardware  | ;            |

|                 |           |                                           |                 |                   |                  |                |              |

| bit 7           |           | (TOSC (external                           | ·               | eady bit          |                  |                |              |

|                 |           | scillator is ready<br>scillator is not er |                 | ot vet ready to h | ne used          |                |              |

| bit 6           |           | NTOSC Oscillat                            |                 |                   |                  |                |              |

| Sit 0           |           | scillator is ready                        | •               |                   |                  |                |              |

|                 |           | scillator is not er                       |                 | ot yet ready to b | be used          |                |              |

| bit 5           | MFOR: MF  | INTOSC Oscillat                           | or Ready bit    |                   |                  |                |              |

|                 |           | scillator is ready                        |                 |                   |                  |                |              |

|                 | 0 = The o | scillator is not er                       | abled, or is no | ot yet ready to b | be used          |                |              |

| bit 4           |           | NTOSC Oscillato                           | •               |                   |                  |                |              |

|                 |           | scillator is ready                        |                 |                   |                  |                |              |

|                 |           | scillator is not en                       |                 |                   | be used          |                |              |

| bit 3           |           | ndary (Timer1) (<br>scillator is ready    |                 | dy bit            |                  |                |              |

|                 |           | scillator is not er                       |                 | ot vet ready to   | he used          |                |              |

| bit 2           |           | C Oscillator Rea                          |                 | or yet ready to   |                  |                |              |

|                 |           | scillator is ready                        | •               |                   |                  |                |              |

|                 |           | scillator is not er                       |                 | ot yet ready to   | be used          |                |              |

| bit 1           | Unimpleme | ented: Read as                            | 0'              |                   |                  |                |              |

| bit 0           | PLLR: PLL | is Ready bit                              |                 |                   |                  |                |              |

|                 |           | LL is ready to b                          | e used          |                   |                  |                |              |

|                 |           |                                           | c uscu          |                   |                  |                |              |

#### REGISTER 7-4: OSCSTAT: OSCILLATOR STATUS REGISTER 1

# PIC18(L)F25/26K83

#### 13.1.5 ERASING PROGRAM FLASH MEMORY

The minimum erase block is 64 words (refer to Table 5-4). Only through the use of an external programmer, or through ICSP™ control, can larger blocks of program memory be bulk erased. Word erase in the program memory array is not supported.

For example, when initiating an erase sequence from a microcontroller with erase row size of 64 words, a block of 64 words (128 bytes) of program memory is erased. The Most Significant 16 bits of the TBLPTR<21:6> point to the block being erased. The TBLPTR<5:0> bits are ignored.

The NVMCON1 register commands the erase operation. The REG<1:0> bits must be set to point to the Program Flash Memory. The WREN bit must be set to enable write operations. The FREE bit is set to select an erase operation.

The NVM unlock sequence described in **Section 13.1.4 "NVM Unlock Sequence**" should be used to guard against accidental writes. This is sometimes referred to as a long write.

A long write is necessary for erasing program memory. Instruction execution is halted during the long write cycle. The long write is terminated by the internal programming timer.

#### 13.1.5.1 Program Flash Memory Erase Sequence

The sequence of events for erasing a block of internal program memory is:

- 1. REG bits of the NVMCON1 register point to PFM

- 2. Set the FREE and WREN bits of the NVMCON1 register

- 3. Perform the unlock sequence as described in Section 13.1.4 "NVM Unlock Sequence"

If the PFM address is write-protected, the WR bit will be cleared and the erase operation will not take place, WRERR is signaled in this scenario.

The operation erases the memory row indicated by masking the LSBs of the current TBLPTR.

While erasing PFM, CPU operation is suspended and it resumes when the operation is complete. Upon completion the WR bit is cleared in hardware, the NVMIF is set and an interrupt will occur if the NVMIE bit is also set.

Write latch data is not affected by erase operations and WREN will remain unchanged.

Note 1: If a write or erase operation is terminated by an unexpected event, WRERR bit will be set which the user can check to decide whether a rewrite of the location(s) is needed.

- 2: WRERR is set if WR is written to '1' while TBLPTR points to a write-protected address.

- **3:** WRERR is set if WR is written to '1' while TBLPTR points to an invalid address location (Table 13-1).

#### 13.4 Register Definitions: Nonvolatile Memory

#### REGISTER 13-1: NVMCON1: NONVOLATILE MEMORY CONTROL 1 REGISTER

| R/W-0/                                            | 0 R/W-0/0                                                                                                                                                                                          | U-0                                                                                                                              | R/S/HC-0/0                                                                                                          | R/W/HS-x/q                                                                                           | R/W-0/0                                                        | R/S/HC-0/0                                             | R/S/HC-0/0 |

|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------|------------|

| F                                                 | REG<1:0>                                                                                                                                                                                           |                                                                                                                                  | FREE                                                                                                                | WRERR                                                                                                | WREN                                                           | WR                                                     | RD         |

| bit 7                                             |                                                                                                                                                                                                    |                                                                                                                                  |                                                                                                                     |                                                                                                      |                                                                |                                                        | bit C      |

|                                                   |                                                                                                                                                                                                    |                                                                                                                                  |                                                                                                                     |                                                                                                      |                                                                |                                                        |            |

| Legend:                                           |                                                                                                                                                                                                    |                                                                                                                                  |                                                                                                                     |                                                                                                      |                                                                |                                                        |            |

| R = Reada                                         |                                                                                                                                                                                                    | W = Writable                                                                                                                     |                                                                                                                     | HC = Bit is cle                                                                                      | -                                                              |                                                        |            |

| x = Bit is ι                                      |                                                                                                                                                                                                    | -n = Value at                                                                                                                    | -                                                                                                                   |                                                                                                      | -                                                              | are, but not clea                                      | ared       |

| '0' = Bit is                                      | cleared                                                                                                                                                                                            | '1' = Bit is se                                                                                                                  | t                                                                                                                   | U = Unimplen                                                                                         | nented bit, rea                                                | id as '0'                                              |            |

| bit 7-6                                           | 10 =Access  <br>x1 = Access                                                                                                                                                                        |                                                                                                                                  |                                                                                                                     |                                                                                                      | ID and Device                                                  | e ID                                                   |            |

| bit 5                                             | Unimplemer                                                                                                                                                                                         | nted: Read as                                                                                                                    | ʻ0'                                                                                                                 |                                                                                                      |                                                                |                                                        |            |

| bit 4                                             | 1 = Perform                                                                                                                                                                                        | ns an erase op                                                                                                                   | nory Erase Enal<br>eration on the n<br>nd performs a w                                                              | ext WR comm                                                                                          | and                                                            |                                                        |            |

|                                                   | or WR v<br>or WR v<br>or WR v                                                                                                                                                                      | was written to<br>was written to<br>was written to                                                                               | l'b1 when REG                                                                                                       | valid address i <1:0> and add te-protected ac                                                        | s accessed (T<br>ress do not po                                | able 4-1, Table<br>bint to the same<br>ssed (Table 4-2 | region     |

| bit 2                                             | 1 = Allows                                                                                                                                                                                         |                                                                                                                                  | able bit<br>and refresh cyo<br>erasing and use                                                                      |                                                                                                      | /M                                                             |                                                        |            |

| bit 1<br>bit 0                                    | When REG p1 = InitiatesWhen REG p1 = Initiates0 = NVM prRD: Read Co                                                                                                                                | an erase/prog<br>points to a PFM<br>the PFM write<br>rogram/erase c<br>pontrol bit <sup>(8)</sup>                                | l location:<br>operation with<br>peration is com                                                                    | e correspondin<br>data from the<br>pplete and inac                                                   | nolding registe                                                |                                                        |            |

| Note de                                           | 0 = NVM re                                                                                                                                                                                         | ad operation is                                                                                                                  | s complete and                                                                                                      |                                                                                                      | IADR, and loa                                                  | ads data into N∖                                       | INIDAT     |

| Note 1:<br>2:<br>3:<br>4:<br>5:<br>6:<br>7:<br>8: | This can only be u<br>This bit is set whe<br>completed success<br>Bit must be cleare<br>Bit may be written<br>This bit can only b<br>Operations are set<br>Once a write oper<br>The bit can only b | en WR = 1 and<br>safully.<br>ed by the user;<br>a to '1' by the u<br>be set by follow<br>elf-timed and the<br>ration is initiate | clears when the<br>hardware will n<br>ser in order to i<br>ving the unlock<br>e WR bit is clea<br>d, setting this b | ot clear this bit<br>mplement test<br>sequence of <b>S</b> o<br>ared by hardwa<br>it to zero will ha | sequences.<br>ection 13.1.4<br>are when comp<br>ave no effect. | " <b>NVM Unlock</b> a<br>blete.                        | Sequence". |

The following sections describe with visual reference the sequence of events for different configurations of the DMA module

#### 15.9.1 SOURCE STOP

When the Source Stop bit is set (SSTP = 1) and the DMAxSCNT register reloads, the DMA clears the SIRQEN bit to stop receiving new start interrupt request signals and sets the DMAxSCNTIF flag.

#### FIGURE 15-5: GPR-GPR TRANSACTIONS WITH HARDWARE TRIGGERS, SSTP = 1

|                              | (1)        | 2      | 3     | (4) (5)              | 6 (                                | 2                | 8 (   | ) 10  | 11                | 12                | 13                | 14                | 15         | 16 | 6)    | 13 | Rev. 10-00275A<br>819/2016 |

|------------------------------|------------|--------|-------|----------------------|------------------------------------|------------------|-------|-------|-------------------|-------------------|-------------------|-------------------|------------|----|-------|----|----------------------------|

| Instruction<br>Clock         |            | Ŵ      | ŴM    | MM                   | www                                | )<br>M           | ŴŴ    |       | MM                | Ŵ                 | Ŵ                 | Ŵ                 | NÑ         | M  | ŇŇ    | Ŵ  | M                          |

| EN                           |            |        |       |                      |                                    |                  |       |       |                   |                   |                   |                   |            |    |       |    |                            |

| SIRQEN                       |            |        |       |                      |                                    |                  |       |       |                   |                   |                   |                   |            |    |       |    |                            |

| Source Hardware<br>Trigger – |            |        |       | 1                    |                                    |                  |       |       |                   |                   |                   |                   |            |    |       |    |                            |

| DGO_                         |            |        |       |                      |                                    |                  |       |       |                   |                   |                   |                   |            |    |       |    |                            |

| DMAxSPTR                     | $\langle $ |        | 0x100 |                      | X 0x101                            | )                |       | 0x102 |                   | X                 | 0x10              | з                 |            |    | 0x100 | )  |                            |

| DMAxDPTR                     |            |        | 0x200 |                      | X 0x201                            | )                | /     | 0x201 |                   | _χ                | 0x20              | 01                |            |    | 0x200 | )  |                            |

| DMAxSCNT                     | $\langle $ |        | 4     |                      | Х 3                                |                  |       | 2     |                   | X                 | 1                 | )                 | $\langle $ |    | 4     |    |                            |

| DMAxDCNT                     |            |        | 2     |                      | 1                                  | )                | (     | 2     |                   | χ                 | 1                 |                   |            |    | 2     |    |                            |

| DMA STATE                    |            | IDLE   |       | SR <sup>(1)</sup> DW | <sup>2)</sup> SR <sup>(1)</sup> DV | N <sup>(2)</sup> | I     | DLE   | SR <sup>(1)</sup> | DW <sup>(2)</sup> | SR <sup>(1)</sup> | DW <sup>(2)</sup> |            |    | IDLE  |    |                            |

| DMAxSCNTIF                   |            |        |       |                      |                                    |                  |       |       |                   |                   |                   |                   |            |    |       |    |                            |

| DMAxDCNTIF —                 |            |        |       |                      |                                    |                  |       |       |                   |                   |                   |                   |            |    |       |    |                            |

|                              | DMA        | xSSA   | 0x100 | )                    | DMAxDSA                            | C                | )x200 |       |                   |                   |                   |                   |            |    |       |    |                            |

|                              | DMA        | xSSZ   | 0x4   |                      | DMAxDSZ                            |                  | 0x2   |       |                   |                   |                   |                   |            |    |       |    |                            |

| Note 1: S                    | SR – S     | ource  | e Rea | d                    |                                    |                  |       |       |                   |                   |                   |                   |            |    |       |    |                            |

| <b>2:</b> □                  | DW – D     | Destin | ation | Write                |                                    |                  |       |       |                   |                   |                   |                   |            |    |       |    |                            |

| U-0            | U-0                        | U-0                   | R/W-0/0       | R/W-0/0       | R/W-0/0          | R/W-0/0  | R/W-0/0      |  |  |  |  |

|----------------|----------------------------|-----------------------|---------------|---------------|------------------|----------|--------------|--|--|--|--|

| _              | —                          | —                     |               |               | WSEL<4:0>        |          |              |  |  |  |  |

| bit 7          | ·                          |                       | <u>.</u>      |               |                  |          | bit          |  |  |  |  |

|                |                            |                       |               |               |                  |          |              |  |  |  |  |

| Legend:        |                            |                       |               |               |                  |          |              |  |  |  |  |

| R = Readal     | ble bit                    | W = Writable          | e bit         | U = Unimpler  | mented bit, read | d as '0' |              |  |  |  |  |

| u = Bit is u   |                            | x = Bit is unk        |               | •             | at POR and BC    |          | other Resets |  |  |  |  |

| '1' = Bit is s | -                          | '0' = Bit is cle      |               |               | pends on condi   |          |              |  |  |  |  |

|                | Set                        |                       | eareu         | q – value del |                  | uon      |              |  |  |  |  |

| bit 7-5        | Unimplemen                 | ted: Read as '0'      |               |               |                  |          |              |  |  |  |  |

| bit 4-0        |                            | SMTx Window S         | election bits |               |                  |          |              |  |  |  |  |

|                | 11111 = Res                |                       |               |               |                  |          |              |  |  |  |  |

|                | •                          |                       |               |               |                  |          |              |  |  |  |  |

|                | •                          |                       |               |               |                  |          |              |  |  |  |  |

|                | •<br>11011 = Res           | erved                 |               |               |                  |          |              |  |  |  |  |

|                |                            | 11010 = CLC4_out      |               |               |                  |          |              |  |  |  |  |

|                | 11001 <b>= CLC</b>         | _                     |               |               |                  |          |              |  |  |  |  |

|                | 11000 = CLC                |                       |               |               |                  |          |              |  |  |  |  |

|                | 10111 = CLC                | —                     |               |               |                  |          |              |  |  |  |  |

|                | 10110 = ZCE                | —                     |               |               |                  |          |              |  |  |  |  |

|                | 10101 = CM<br>10100 = CM   |                       |               |               |                  |          |              |  |  |  |  |

|                | 10011 = NC                 |                       |               |               |                  |          |              |  |  |  |  |

|                | 10010 = Res                |                       |               |               |                  |          |              |  |  |  |  |

|                | 10001 = Res                | erved                 |               |               |                  |          |              |  |  |  |  |

|                | 10000 <b>= PW</b>          |                       |               |               |                  |          |              |  |  |  |  |

|                | 01111 <b>= PW</b>          | —                     |               |               |                  |          |              |  |  |  |  |

|                | 01110 = PW                 | —                     |               |               |                  |          |              |  |  |  |  |

|                | 01101 = PW<br>01100 = CCF  | —                     |               |               |                  |          |              |  |  |  |  |

|                | 01011 = CC                 |                       |               |               |                  |          |              |  |  |  |  |

|                | 01010 = CCF                |                       |               |               |                  |          |              |  |  |  |  |

|                | 01001 = CC                 |                       |               |               |                  |          |              |  |  |  |  |

|                |                            | R6_postscaled         |               |               |                  |          |              |  |  |  |  |

|                |                            | R4_postscaled         |               |               |                  |          |              |  |  |  |  |

|                |                            | R2_postscaled         |               |               |                  |          |              |  |  |  |  |

|                | 00101 = TM                 | _                     |               |               |                  |          |              |  |  |  |  |

|                | 00100 = CLK<br>00011 = SOS |                       |               |               |                  |          |              |  |  |  |  |

|                |                            | SC<br>NTOSC/16 (32 kl | Hz)           |               |                  |          |              |  |  |  |  |

|                | 00001 = LFI                |                       | ,             |               |                  |          |              |  |  |  |  |

|                | 00000 = SM                 |                       |               |               |                  |          |              |  |  |  |  |

#### REGISTER 25-5: SMTxWIN: SMTx WINDOW INPUT SELECT REGISTER

| R/W-x/1          | R/W-x/1 | R/W-x/1           | R/W-x/1 | R/W-x/1        | R/W-x/1          | R/W-x/1        | R/W-x/1      |

|------------------|---------|-------------------|---------|----------------|------------------|----------------|--------------|

|                  |         |                   | SMTxF   | PR<7:0>        |                  |                |              |

| bit 7            |         |                   |         |                |                  |                | bit 0        |

|                  |         |                   |         |                |                  |                |              |

| Legend:          |         |                   |         |                |                  |                |              |

| R = Readable     | bit     | W = Writable I    | bit     | U = Unimpler   | nented bit, read | d as '0'       |              |

| u = Bit is unch  | anged   | x = Bit is unkn   | iown    | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                |              |

#### **REGISTER 25-16: SMTxPRL: SMT PERIOD REGISTER – LOW BYTE**

bit 7-0 SMTxPR<7:0>: Significant bits of the SMT Timer Value for Period Match – Low Byte

#### **REGISTER 25-17: SMTxPRH: SMT PERIOD REGISTER – HIGH BYTE**

| R/W-x/1        | R/W-x/1 | R/W-x/1          | R/W-x/1 | R/W-x/1      | R/W-x/1          | R/W-x/1  | R/W-x/1 |

|----------------|---------|------------------|---------|--------------|------------------|----------|---------|

|                |         |                  | SMTxPF  | R<15:8>      |                  |          |         |

| bit 7          |         |                  |         |              |                  |          | bit 0   |

|                |         |                  |         |              |                  |          |         |

| Legend:        |         |                  |         |              |                  |          |         |

| R = Readable b | oit     | W = Writable bit | ł       | U = Unimpler | mented bit, read | 1 as '0' |         |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SMTxPR<15:8>: Significant bits of the SMT Timer Value for Period Match – High Byte

#### REGISTER 25-18: SMTxPRU: SMT PERIOD REGISTER – UPPER BYTE

| R/W-x/1       | R/W-x/1 | R/W-x/1 | R/W-x/1 | R/W-x/1 | R/W-x/1 | R/W-x/1 | R/W-x/1 |  |  |  |  |

|---------------|---------|---------|---------|---------|---------|---------|---------|--|--|--|--|

| SMTxPR<23:16> |         |         |         |         |         |         |         |  |  |  |  |

| bit 7 bit     |         |         |         |         |         |         |         |  |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SMTxPR<23:16>: Significant bits of the SMT Timer Value for Period Match – Upper Byte

| R/W-0/0                                                                                       | U-0          | U-0                                     | U-0            | R/W-x/u          | R/W-x/u    | R/W-x/u | R/W-x/u |  |  |  |

|-----------------------------------------------------------------------------------------------|--------------|-----------------------------------------|----------------|------------------|------------|---------|---------|--|--|--|

| POL                                                                                           | —            | —                                       | _              | G4POL            | G3POL      | G2POL   | G1POL   |  |  |  |

| bit 7                                                                                         |              |                                         |                |                  |            |         | bit 0   |  |  |  |

|                                                                                               |              |                                         |                |                  |            |         |         |  |  |  |

| Legend:                                                                                       |              |                                         |                |                  |            |         |         |  |  |  |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'                            |              |                                         |                |                  |            |         |         |  |  |  |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets |              |                                         |                |                  |            |         |         |  |  |  |

| '1' = Bit is set '0' = Bit is cleared                                                         |              |                                         |                |                  |            |         |         |  |  |  |

|                                                                                               |              |                                         |                |                  |            |         |         |  |  |  |

| bit 7                                                                                         | POL: CLCxO   | UT Output Pola                          | arity Control  | bit              |            |         |         |  |  |  |

|                                                                                               |              | ut of the logic c                       |                |                  |            |         |         |  |  |  |

|                                                                                               | 0 = The outp | ut of the logic c                       | ell is not inv | erted            |            |         |         |  |  |  |

| bit 6-4                                                                                       | Unimplemen   | ted: Read as 'o                         | )'             |                  |            |         |         |  |  |  |

| bit 3                                                                                         | G4POL: Gate  | e 3 Output Pola                         | rity Control b | bit              |            |         |         |  |  |  |

|                                                                                               |              | ut of gate 3 is ir<br>ut of gate 3 is n |                | n applied to the | logic cell |         |         |  |  |  |

| <b>h</b> # 0                                                                                  | •            | •                                       |                | :4               |            |         |         |  |  |  |

| bit 2                                                                                         |              | e 2 Output Pola                         |                |                  |            |         |         |  |  |  |

|                                                                                               |              | ut of gate 2 is in<br>ut of gate 2 is n |                | n applied to the | logic cell |         |         |  |  |  |

| bit 1                                                                                         |              | e 1 Output Pola                         |                | it               |            |         |         |  |  |  |

| bit i                                                                                         |              |                                         | ,              | n applied to the | logic cell |         |         |  |  |  |

|                                                                                               |              | ut of gate 1 is n                       |                |                  | logic cen  |         |         |  |  |  |

| bit 0                                                                                         | G1POL: Gate  | e 0 Output Pola                         | rity Control b | oit              |            |         |         |  |  |  |

|                                                                                               |              | •                                       | 2              | n applied to the | logic cell |         |         |  |  |  |

|                                                                                               | •            | ut of gate 0 is n                       |                | ••               | J          |         |         |  |  |  |

#### REGISTER 27-2: CLCxPOL: SIGNAL POLARITY CONTROL REGISTER

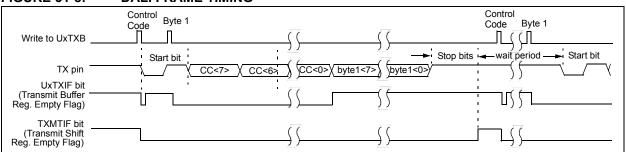

#### FIGURE 31-8: DALI FRAME TIMING

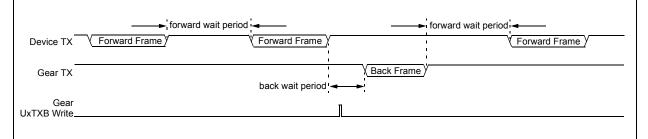

#### FIGURE 31-9: DALI FORWARD/BACK FRAME TIMING

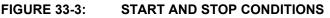

#### 33.3.2 BYTE FORMAT

All communication in  $I^2C$  is done in 9-bit segments. A byte is sent from a master to a slave or vice-versa, followed by an Acknowledge bit sent by the receiver. After the 8th falling edge of the SCL line, the device transmitting data on the SDA line releases control of that pin to an input, and reads in an acknowledge value on the next clock pulse. The clock signal is provided by the master. Data is valid to change while the SCL line is low, and sampled on the rising edge of the clock. Changes on the SDA line while the SCL line is high define Start and Stop conditions on the bus which are explained further in the chapter.

#### 33.3.3 SDA AND SCL PINS

The user must configure these pins as open-drain outputs. This is done by clearing the appropriate TRIS bits and setting the appropriate ODCON bits. The user may also select the input threshold, slew-rate and internal pull-up settings using the Rxyl2C control registers (Register 16-9).

#### 33.3.4 SDA HOLD TIME

The hold time of the SDA pin is selected by the SDAHT<1:0> bits of the I2CxCON2 register. Hold time is the time SDA is held valid after the falling edge of SCL. A longer hold time setting may help on buses with large capacitance.

#### 33.3.5 START CONDITION

The I<sup>2</sup>C specification defines a Start condition as a transition of SDA line from a high to a low state while SCL line is high. A Start condition is always generated by the master and signifies the transition of the bus from an Idle to an Active state. Figure 33-3 shows waveforms for Start conditions. Master hardware waits for the BFRE bit of I2CxSTAT0 to be set, before asserting a Start condition on the SCL and SDA lines. If two masters assert a start at the same time, a collision will occur during the addressing phase.

#### 33.3.6 STOP CONDITION

A Stop condition is a transition of the SDA line from low to high while the SCL line is high. Figure 33-3 shows waveforms for Stop conditions.

**Note:** At least one SCL low time must appear before a Stop is valid. Therefore, if the SDA line goes low then high again while the SCL line is high, only the Start condition is detected.

| Mode 0                   | R/W-1                                                                                              | R/W-0                           | R/W-0                          | R/S-0                   | R/W-0                     | R/W-0                                          | R/W-0           | U-0   |  |  |  |  |  |

|--------------------------|----------------------------------------------------------------------------------------------------|---------------------------------|--------------------------------|-------------------------|---------------------------|------------------------------------------------|-----------------|-------|--|--|--|--|--|

|                          | REQOP2                                                                                             | REQOP1                          | REQOP0                         | ABAT                    | WIN2                      | WIN1                                           | WIN0            |       |  |  |  |  |  |

|                          | R/W-1                                                                                              | R/W-0                           | R/W-0                          | R/S-0                   | UO                        | U-0                                            | U-0             | U-0   |  |  |  |  |  |

| Mode 1                   | REQOP2                                                                                             | REQOP1                          | REQOP0                         | ABAT                    |                           | <u> </u>                                       | <u> </u>        | -0    |  |  |  |  |  |

|                          | REGOLE                                                                                             | REGOLI                          | ILL QUI U                      | <i>i</i> (B <i>i</i> (1 |                           |                                                |                 |       |  |  |  |  |  |

| Mode 2                   | R/W-1                                                                                              | R/W-0                           | R/W-0                          | R/S-0                   | R-0                       | R-0                                            | R-0             | R-0   |  |  |  |  |  |

| Mode 2                   | REQOP2                                                                                             | REQOP1                          | REQOP0                         | ABAT                    | FP3                       | FP2                                            | FP1             | FP0   |  |  |  |  |  |

|                          | bit 7                                                                                              |                                 |                                |                         |                           |                                                |                 | bit 0 |  |  |  |  |  |

| Legend: S = Settable bit |                                                                                                    |                                 |                                |                         |                           |                                                |                 |       |  |  |  |  |  |

| R = Readal               | ble bit                                                                                            |                                 | W = Writable                   |                         | U = Unimpl                | emented bit, r                                 | ead as '0'      |       |  |  |  |  |  |

| -n = Value a             | at POR                                                                                             |                                 | '1' = Bit is se                | et                      | '0' = Bit is c            |                                                | x = Bit is unl  | known |  |  |  |  |  |

|                          |                                                                                                    |                                 |                                |                         |                           |                                                |                 |       |  |  |  |  |  |

| bit 7-5                  |                                                                                                    | -                               | CAN Operation                  | n Mode bits             | 6                         |                                                |                 |       |  |  |  |  |  |

|                          |                                                                                                    | ests Configur                   |                                |                         |                           |                                                |                 |       |  |  |  |  |  |

|                          |                                                                                                    | ests Listen O<br>ests Loopbac   |                                |                         |                           |                                                |                 |       |  |  |  |  |  |

|                          |                                                                                                    | led/Sleep mc                    |                                |                         |                           |                                                |                 |       |  |  |  |  |  |

|                          |                                                                                                    | ests Normal r                   |                                |                         |                           |                                                |                 |       |  |  |  |  |  |

| bit 4                    |                                                                                                    | -                               | Transmission                   |                         | (4)                       |                                                |                 |       |  |  |  |  |  |

|                          |                                                                                                    |                                 | smissions (in<br>eding as norm |                         | t buffers) <sup>(1)</sup> |                                                |                 |       |  |  |  |  |  |

| bit 3-1                  | <u>Mode 0:</u><br>WIN<2:0>: V                                                                      | Vindow Addr                     | ess bits                       |                         |                           |                                                |                 |       |  |  |  |  |  |

|                          | buffer registe<br>can be copie                                                                     | ers from any o<br>ed to the WIN | data memory                    | bank. After             | a frame has o             | cess Bank are<br>caused an inte<br>See Example | errupt, the ICC |       |  |  |  |  |  |

|                          | 111 = Recei<br>110 = Recei<br>101 = Recei                                                          | ve Buffer 0                     |                                |                         |                           |                                                |                 |       |  |  |  |  |  |

|                          | 100 <b>= Trans</b>                                                                                 |                                 |                                |                         |                           |                                                |                 |       |  |  |  |  |  |

|                          | 011 = Trans<br>010 = Trans                                                                         |                                 |                                |                         |                           |                                                |                 |       |  |  |  |  |  |

|                          | 010 = Transi<br>001 = Recei                                                                        |                                 |                                |                         |                           |                                                |                 |       |  |  |  |  |  |

|                          | 000 <b>= Rece</b> i                                                                                |                                 |                                |                         |                           |                                                |                 |       |  |  |  |  |  |

| bit 0                    | <u>Mode 0:</u><br>Unimpleme                                                                        | nted: Read a                    | <b>s</b> '0'                   |                         |                           |                                                |                 |       |  |  |  |  |  |

| bit 4-0                  | <u>Mode 1:</u>                                                                                     |                                 |                                |                         |                           |                                                |                 |       |  |  |  |  |  |

|                          | -                                                                                                  | nted: Read a                    | <b>s</b> '0'                   |                         |                           |                                                |                 |       |  |  |  |  |  |

|                          | Mode 2:                                                                                            | EO Bood Boi                     | ntor hito                      |                         |                           |                                                |                 |       |  |  |  |  |  |

|                          | <b>FP&lt;3:0&gt;:</b> FIFO Read Pointer bits<br>These bits point to the message buffer to be read. |                                 |                                |                         |                           |                                                |                 |       |  |  |  |  |  |

|                          | 0000 = Rece                                                                                        | eive Message                    | e Buffer 0                     |                         |                           |                                                |                 |       |  |  |  |  |  |

|                          |                                                                                                    | eive Message                    |                                |                         |                           |                                                |                 |       |  |  |  |  |  |

|                          |                                                                                                    | eive Message<br>eive Message    |                                |                         |                           |                                                |                 |       |  |  |  |  |  |

|                          |                                                                                                    | eive Message                    |                                |                         |                           |                                                |                 |       |  |  |  |  |  |

|                          | 0101 = Rece                                                                                        | eive Message                    | e Buffer 5                     |                         |                           |                                                |                 |       |  |  |  |  |  |

|                          |                                                                                                    | eive Message                    |                                |                         |                           |                                                |                 |       |  |  |  |  |  |

|                          | 1000:1111                                                                                          | eive Message<br>Reserved        |                                |                         |                           |                                                |                 |       |  |  |  |  |  |

|                          |                                                                                                    |                                 |                                |                         |                           |                                                |                 |       |  |  |  |  |  |

#### **REGISTER 34-1:** CANCON: CAN CONTROL REGISTER

Note 1: This bit will clear when all transmissions are aborted.

### 34.15.3.1 Programmable TX/RX and Auto-RTR Buffers

The ECAN module contains six message buffers that can be programmed as transmit or receive buffers. Any of these buffers can also be programmed to automatically handle RTR messages.

**Note:** These registers are not used in Mode 0.

## REGISTER 34-22: BnCON: TX/RX BUFFER 'n' CONTROL REGISTERS IN RECEIVE MODE $[0 \le n \le 5, TXnEN (BSEL0 < n >) = 0]^{(1)}$

| R/W-0                | R/W-0 | R-0     | R-0     | R-0     | R-0     | R-0     | R-0     |

|----------------------|-------|---------|---------|---------|---------|---------|---------|

| RXFUL <sup>(2)</sup> | RXM1  | RXRTRRO | FILHIT4 | FILHIT3 | FILHIT2 | FILHIT1 | FILHIT0 |

| bit 7                |       |         |         |         |         |         | bit 0   |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 7   | RXFUL: Receive Full Status bit <sup>(2)</sup>                                                                                                                                 |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = Receive buffer contains a received message                                                                                                                                |

|         | 0 = Receive buffer is open to receive a new message                                                                                                                           |

| bit 6   | RXM1: Receive Buffer Mode bit                                                                                                                                                 |

|         | <ul> <li>1 = Receive all messages including partial and invalid (acceptance filters are ignored)</li> <li>0 = Receive all valid messages as per acceptance filters</li> </ul> |

| bit 5   | RXRTRRO: Read-Only Remote Transmission Request for Received Message bit                                                                                                       |

|         | 1 = Received message is a remote transmission request                                                                                                                         |

|         | 0 = Received message is not a remote transmission request                                                                                                                     |

| bit 4-0 | FILHIT<4:0>: Filter Hit bits                                                                                                                                                  |

|         | These bits indicate which acceptance filter enabled the last message reception into this buffer.                                                                              |

|         | 01111 = Acceptance Filter 15 (RXF15)                                                                                                                                          |

|         | 01110 = Acceptance Filter 14 (RXF14)                                                                                                                                          |

|         |                                                                                                                                                                               |

|         | 00001 = Acceptance Filter 1 (RXF1)                                                                                                                                            |

|         | 00000 = Acceptance Filter 0 (RXF0)                                                                                                                                            |

|         |                                                                                                                                                                               |

- **Note 1:** These registers are available in Mode 1 and 2 only.

- 2: This bit is set by the CAN module upon receiving a message and must be cleared by software after the buffer is read. As long as RXFUL is set, no new message will be loaded and the buffer will be considered full.

| Mode 0     | R/W-0                                            | R/W-0                                                                     | R/W-0                                               | R/W-0                         | R/W-0                 | R/W-0                 | R/W-0         | R/W-0    |

|------------|--------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------|-------------------------------|-----------------------|-----------------------|---------------|----------|

|            | IRXIE                                            | WAKIE                                                                     | ERRIE                                               | TXB2IE                        | TXB1IE <sup>(1)</sup> | TXB0IE <sup>(1)</sup> | RXB1IE        | RXB0IE   |

|            | R/W-0                                            | R/W-0                                                                     | R/W-0                                               | R/W-0                         | R/W-0                 | R/W-0                 | R/W-0         | R/W-0    |

| Mode 1     | IRXIE                                            | WAKIE                                                                     | ERRIE                                               | TXBnIE                        | TXB1IE <sup>(1)</sup> | TXB0IE <sup>(1)</sup> | RXBnIE        | FIFOWMIE |

|            | bit 7                                            |                                                                           |                                                     |                               |                       |                       |               | bit 0    |

| Legend:    |                                                  |                                                                           |                                                     |                               |                       |                       |               |          |

| R = Reada  | blo bit                                          |                                                                           | W = Writabl                                         | o hit                         | II – Unimple          | montod bit r          | ood oo '0'    |          |

| -n = Value |                                                  |                                                                           | '1' = Bit is s                                      |                               | '0' = Bit is cl       | emented bit, re       | x = Bit is un | known    |

|            | alFUR                                            |                                                                           | I - DIL 15 5                                        | el                            |                       | eareu                 |               | KHOWH    |

| bit 7      | 1 = Enable i                                     | Bus Error Me<br>nvalid messa                                              | ge received i                                       | interrupt                     | ot Enable bit         |                       |               |          |

| hit C      |                                                  | invalid messa                                                             | •                                                   | •                             | la hit                |                       |               |          |

| bit 6      | 1 = Enable I                                     | N bus Activity<br>bus activity wa<br>bus activity w                       | ake-up interr                                       | upt                           | ie dit                |                       |               |          |

| bit 5      |                                                  | N bus Error In                                                            |                                                     | •                             |                       |                       |               |          |

|            |                                                  | CAN module<br>CAN module                                                  |                                                     |                               |                       |                       |               |          |

| bit 4      | TXB2IE: CA                                       | <u>is in Mode 0:</u><br>N Transmit B<br>Transmit Buffe<br>Transmit Buff   | er 2 interrupt                                      |                               | bit                   |                       |               |          |

|            | When CAN<br>TXBnIE: CA<br>1 = Enable t           | is in Mode 1 d<br>N Transmit B                                            | o <u>r 2:</u><br>suffer Interrup<br>r interrupt; in | ots Enable b<br>dividual inte | it<br>rrupt is enable | ed by TXBIE a         | and BIE0      |          |

| bit 3      | <b>TXB1IE:</b> CA                                | N Transmit B<br>Transmit Buffe<br>Transmit Buff                           | uffer 1 Interr<br>er 1 interrupt                    | upt Enable t                  | bit <sup>(1)</sup>    |                       |               |          |

| bit 2      | <b>TXB0IE:</b> CA                                | N Transmit Buffe<br>Transmit Buffe<br>Transmit Buffe                      | uffer 0 Interr<br>er 0 interrupt                    | upt Enable b                  | <sub>Dit</sub> (1)    |                       |               |          |

| bit 1      | <b>RXB1IE:</b> CA                                | <u>is in Mode 0:</u><br>AN Receive B<br>Receive Buffe<br>Receive Buffe    | r 1 interrupt                                       |                               | it                    |                       |               |          |

|            | <b>RXBnIE:</b> CA                                | <u>is in Mode 1 c</u><br>AN Receive B<br>receive buffer<br>all receive bu | uffer Interrup<br>interrupt; inc                    | dividual inter                | t<br>rupt is enable   | d by BIE0             |               |          |

| bit 0      | <b>RXB0IE:</b> CA<br>1 = Enable I<br>0 = Disable | <u>is in Mode 0:</u><br>AN Receive B<br>Receive Buffe<br>Receive Buffe    | r 0 interrupt                                       | •                             | it                    |                       |               |          |

|            | Unimpleme                                        | is in Mode 1:<br>nted: Read a                                             | <b>s</b> '0'                                        |                               |                       |                       |               |          |

|            | FIFOWMIE:                                        | <u>is in Mode 2:</u><br>FIFO Watern<br>FIFO waterma                       |                                                     | t Enable bit                  |                       |                       |               |          |

#### REGISTER 34-57: PIE5: PERIPHERAL INTERRUPT ENABLE REGISTER 5

Note 1: In CAN Mode 1 and 2, these bits are forced to '0'.

| Mode 0     | R/W-1                                                                                                                             | R/W-1 | R/W-1           | R/W-1          | R/W-1                 | R/W-1                 | R/W-1         | R/W-1    |  |  |  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------|-------|-----------------|----------------|-----------------------|-----------------------|---------------|----------|--|--|--|

| wode u     | IRXIP                                                                                                                             | WAKIP | ERRIP           | TXB2IP         | TXB1IP <sup>(1)</sup> | TXB0IP <sup>(1)</sup> | RXB1IP        | RXB0IP   |  |  |  |

|            | D 44/4                                                                                                                            |       |                 | <b>D</b> 44/ 4 |                       | D (14/ 4              |               |          |  |  |  |

| Mode 1,2   | R/W-1                                                                                                                             | R/W-1 | R/W-1           | R/W-1          | R/W-1                 | R/W-1                 | R/W-1         | R/W-1    |  |  |  |

|            |                                                                                                                                   | WAKIP | ERRIP           | TXBnIP         | TXB1IP <sup>(1)</sup> | TXB0IP <sup>(1)</sup> | RXBnIP        | FIFOWMIP |  |  |  |

|            | bit 7                                                                                                                             |       |                 |                |                       |                       |               | bit (    |  |  |  |

| Legend:    |                                                                                                                                   |       |                 |                |                       |                       |               |          |  |  |  |

| R = Reada  | ble bit                                                                                                                           |       | W = Writable    | e bit          | U = Unimple           | emented bit, re       | ead as '0'    |          |  |  |  |

| -n = Value | at POR                                                                                                                            |       | '1' = Bit is se | et             | '0' = Bit is cl       | eared                 | x = Bit is un | known    |  |  |  |

| bit 7      | IRXIP: CAN<br>1 = High pric<br>0 = Low pric                                                                                       |       | essage Recei    | ved Interrup   | ot Priority bit       |                       |               |          |  |  |  |

| bit 6      | <b>WAKIP:</b> CA<br>1 = High pric<br>0 = Low pric                                                                                 |       | / Wake-up In    | terrupt Prior  | ity bit               |                       |               |          |  |  |  |

| bit 5      | ERRIP: CAN<br>1 = High pric<br>0 = Low pric                                                                                       |       | or Interrupt P  | riority bit    |                       |                       |               |          |  |  |  |

| bit 4      | When CAN is in Mode 0:<br><b>TXB2IP:</b> CAN Transmit Buffer 2 Interrupt Priority bit<br>1 = High priority<br>0 = Low priority    |       |                 |                |                       |                       |               |          |  |  |  |

|            | When CAN is in Mode 1 or 2:<br><b>TXBnIP:</b> CAN Transmit Buffer Interrupt Priority bit<br>1 = High priority<br>0 = Low priority |       |                 |                |                       |                       |               |          |  |  |  |

| bit 3      | <b>TXB1IP:</b> CA<br>1 = High pric<br>0 = Low pric                                                                                |       | uffer 1 Interro | upt Priority b | bit(1)                |                       |               |          |  |  |  |

| bit 2      | <b>TXB0IP:</b> CA<br>1 = High pric<br>0 = Low pric                                                                                |       | uffer 0 Interro | upt Priority b | <sub>Dit</sub> (1)    |                       |               |          |  |  |  |