Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 64MHz                                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                   |

| Number of I/O              | 25                                                                           |

| Program Memory Size        | 32KB (16K x 16)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 1K x 8                                                                       |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

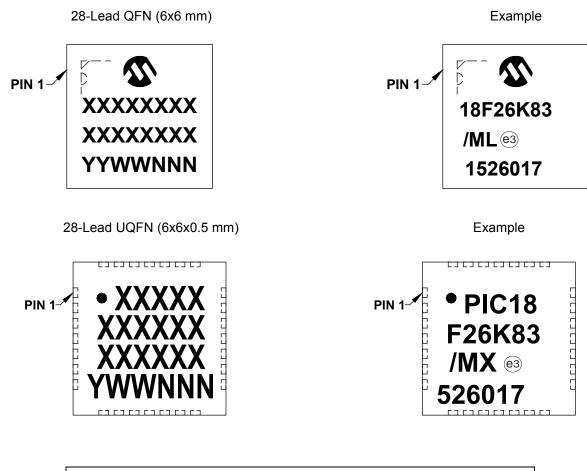

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-UQFN Exposed Pad                                                          |

| Supplier Device Package    | 28-UQFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf25k83t-i-mx |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.3 Register and Bit naming conventions

#### 1.3.1 REGISTER NAMES

When there are multiple instances of the same peripheral in a device, the peripheral control registers will be depicted as the concatenation of a peripheral identifier, peripheral instance, and control identifier. The control registers section will show just one instance of all the register names with an 'x' in the place of the peripheral instance number. This naming convention may also be applied to peripherals when there is only one instance of that peripheral in the device to maintain compatibility with other devices in the family that contain more than one.

#### 1.3.2 BIT NAMES

There are two variants for bit names:

- Short name: Bit function abbreviation

- Long name: Peripheral abbreviation + short name

#### 1.3.2.1 Short Bit Names

Short bit names are an abbreviation for the bit function. For example, some peripherals are enabled with the EN bit. The bit names shown in the registers are the short name variant.

Short bit names are useful when accessing bits in C programs. The general format for accessing bits by the short name is *RegisterName*bits.*ShortName*. For example, the enable bit, EN, in the TOCON0 register can be set in C programs with the instruction TOCON0bits.EN = 1.

Short names are generally not useful in assembly programs because the same name may be used by different peripherals in different bit positions. When this occurs, during the include file generation, all instances of that short bit name are appended with an underscore plus the name of the register in which the bit resides to avoid naming contentions.

#### 1.3.2.2 Long Bit Names

Long bit names are constructed by adding a peripheral abbreviation prefix to the short name. The prefix is unique to the peripheral thereby making every long bit name unique. The long bit name for the Timer0 enable bit is the Timer0 prefix, T0, appended with the enable bit short name, EN, resulting in the unique bit name T0EN.

Long bit names are useful in both C and assembly programs. For example, in C the T0CON0 enable bit can be set with the T0EN = 1 instruction. In assembly, this bit can be set with the BSF T0CON0, T0EN instruction.

## 1.3.2.3 Bit Fields

Bit fields are two or more adjacent bits in the same register. For example, the four Least Significant bits of the T0CON0 register contain the output prescaler select bits. The short name for this field is OUTPS and the long name is T0OUTPS. Bit field access is only possible in C programs. The following example demonstrates a C program instruction for setting the Timer0 output prescaler to the 1:6 Postscaler:

#### TOCONObits.OUTPS = 0x5;

Individual bits in a bit field can also be accessed with long and short bit names. Each bit is the field name appended with the number of the bit position within the field. For example, the Most Significant mode bit has the short bit name OUTPS3. The following two examples demonstrate assembly program sequences for setting the Timer0 output prescaler to 1:6 Postscaler:

#### Example 1:

MOVLW ~(1<<OUTPS3 | 1<<OUTPS1) ANDWF TOCON0,F MOVLW 1<COUTPS2 | 1<<OUTPS0 IORWF TOCON0,F

#### Example 2:

| BCF | TOCONO,OUTPS3 |

|-----|---------------|

| BSF | TOCONO,OUTPS2 |

| BCF | TOCON0,OUTPS1 |

| BSF | TOCON0,OUTPSO |

#### 1.3.3 REGISTER AND BIT NAMING EXCEPTIONS

#### 1.3.3.1 Status, Interrupt, and Mirror Bits

Status, interrupt enables, interrupt flags, and mirror bits are contained in registers that span more than one peripheral. In these cases, the bit name shown is unique so there is no prefix or short name variant.

## 4.4.3 INSTRUCTIONS IN PROGRAM MEMORY

The program memory is addressed in bytes. Instructions are stored as either two bytes or four bytes in program memory. The Least Significant Byte of an instruction word is always stored in a program memory location with an even address (LSb = 0). To maintain alignment with instruction boundaries, the PC increments in steps of two and the LSb will always read '0' (see Section 4.2.4 "Program Counter").

Figure 4-3 shows an example of how instruction words are stored in the program memory.

The CALL and GOTO instructions have the absolute program memory address embedded into the instruction. Since instructions are always stored on word boundaries, the data contained in the instruction is a word address. The word address is written to PC<20:1>, which accesses the desired byte address in program memory. Instruction #2 in Figure 4-3 shows how the instruction GOTO 0006h is encoded in the program memory. Program branch instructions, which encode a relative address offset, operate in the same manner. The offset value stored in a branch instruction represents the number of single-word instructions that the PC will be offset by. Section 42.0 "Instruction Set Summary" provides further details of the instruction set.

## 4.4.4 MULTI-WORD INSTRUCTIONS

The standard PIC18 instruction set has four two-word instructions: CALL, MOVFF, GOTO and LFSR and two three-word instructions: MOVFFL and MOVSFL. In all cases, the second and the third word of the instruction always has '1111' as its four Most Significant bits; the other 12 bits are literal data, usually a data memory address.

The use of '1111' in the four MSbs of an instruction specifies a special form of NOP. If the instruction is executed in proper sequence – immediately after the first word – the data in the second word is accessed and used by the instruction sequence. If the first word is skipped for some reason and the second or third word is executed by itself, a NOP is executed instead. This is necessary for cases when the multi-word instruction is preceded by a conditional instruction that changes the PC. Example 4-4 shows how this works.

## FIGURE 4-3: INSTRUCTIONS IN PROGRAM MEMORY

|                |             |                   | LSB = 1 | LSB = 0 | Word Address $\downarrow$ |

|----------------|-------------|-------------------|---------|---------|---------------------------|

|                | Program M   | emory             |         |         | 000000h                   |

|                | Byte Locati | ons $\rightarrow$ |         |         | 000002h                   |

|                |             |                   |         |         | 000004h                   |

|                |             |                   |         |         | 000006h                   |

| Instruction 1: | MOVLW       | 055h              | 0Fh     | 55h     | 000008h                   |

| Instruction 2: | GOTO        | 0006h             | EFh     | 03h     | 00000Ah                   |

|                |             |                   | F0h     | 00h     | 00000Ch                   |

| Instruction 3: | MOVFF       | 123h, 456h        | C1h     | 23h     | 00000Eh                   |

|                |             |                   | F4h     | 56h     | 000010h                   |

| Instruction 4: | MOVFFL      | 123h, 456h        | 00h     | 60h     | 000012h                   |

|                |             |                   | F4h     | 8Ch     | 000014h                   |

|                |             |                   | F4h     | 56h     | 000016h                   |

|                |             |                   |         |         | 000018h                   |

|                |             |                   |         |         | 00001Ah                   |

## 7.5 Register Definitions: Oscillator Control

REGISTER 7-1: OSCCON1: OSCILLATOR CONTROL REGISTER 1

| U-0     | R/W-f/f | R/W-f/f   | R/W-f/f | R/W-q/q   | R/W-q/q | R/W-q/q | R/W-q/q |

|---------|---------|-----------|---------|-----------|---------|---------|---------|

| —       |         | NOSC<2:0> |         | NDIV<3:0> |         |         |         |

| bit 7   | •       |           |         |           |         |         | bit 0   |

|         |         |           |         |           |         |         |         |

| Legend: |         |           |         |           |         |         |         |

| Logona.              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | f = determined by Configuration bit setting           |

|                      |                      | q = Reset value is determined by hardware             |

| bit 7   | Unimplemented: Read as '0'                                                  |

|---------|-----------------------------------------------------------------------------|

| bit 6-4 | NOSC<2:0>: New Oscillator Source Request bits <sup>(1,2,3)</sup>            |

|         | The setting requests a source oscillator and PLL combination per Table 7-1. |

|         | POR value = RSTOSC (Register 5-1).                                          |

| bit 3-0 | NDIV<3:0>: New Divider Selection Request bits <sup>(2,3)</sup>              |

The setting determines the new postscaler division ratio per Table 7-1.

- Note1: The default value (f/f) is determined by the RSTOSC Configuration bits. See Table 7-2 below.

- 2: If NOSC is written with a reserved value (Table 7-1), the operation is ignored and neither NOSC nor NDIV is written.

- **3:** When CSWEN = 0, this register is read-only and cannot be changed from the POR value.

| DETOEC | SF        | R Reset Value | S        | Initial Econo Exercisionay    |  |  |  |

|--------|-----------|---------------|----------|-------------------------------|--|--|--|

| RSTOSC | NOSC/COSC | CDIV          | OSCFRQ   | Initial Fosc Frequency        |  |  |  |

| 111    | 111       | 1:1           |          | EXTOSC per FEXTOSC            |  |  |  |

| 110    | 110       | 4:1           |          | Fosc = 1 MHz (4 MHz/4)        |  |  |  |

| 101    | 101       | 1:1           | 4 MHz    | LFINTOSC                      |  |  |  |

| 100    | 100       | 1:1           |          | SOSC                          |  |  |  |

| 011    |           |               | Reserved |                               |  |  |  |

| 010    | 010       | 1:1           | 4 MHz    | EXTOSC + 4xPLL <sup>(1)</sup> |  |  |  |

| 001    |           | Reserved      |          |                               |  |  |  |

| 000    | 110       | 1:1           | 64 MHz   | Fosc = 64 MHz                 |  |  |  |

### TABLE 7-2: DEFAULT OSCILLATOR SETTINGS

**Note 1:** EXTOSC must meet the PLL specifications (Table 45-9).

## 13.0 NONVOLATILE MEMORY (NVM) CONTROL

Nonvolatile Memory (NVM) is separated into two types: Program Flash Memory (PFM) and Data EEPROM Memory.

PFM, Data EEPROM, User IDs and Configuration bits can all be accessed using the REG<1:0> bits of the NVMCON1 register.

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the operating voltage range of the device.

NVM can be protected in two ways, by either code protection or write protection. Code protection (CP and CPD bits in Configuration Word 5L) disables access, reading and writing to both PFM and Data EEPROM Memory via external device programmers. Code protection does not affect the self-write and erase functionality. Code protection can only be reset by a device programmer performing a Bulk Erase to the device, clearing all nonvolatile memory, Configuration bits and User IDs.

Write protection prohibits self-write and erase to a portion or all of the PFM, as defined by the WRT bits of Configuration Word 4H. Write protection does not affect a device programmer's ability to read, write or erase the device.

|                                           | PC<20:0>                                         | Execution        |     | User Access                   | ;                             |  |

|-------------------------------------------|--------------------------------------------------|------------------|-----|-------------------------------|-------------------------------|--|

| Memory                                    | ICSP™ Addr<21:0><br>TBLPTR<21:0><br>NVMADDR<9:0> | CPU<br>Execution | REG | TABLAT                        | NVMDAT                        |  |

| Program Flash Memory<br>(PFM)             | 00 0000h<br>•••<br>01 FFFFh                      | Read             | 10  | Read/<br>Write <sup>(1)</sup> | (3)                           |  |

| User IDs <sup>(2)</sup>                   | 20 0000h<br>•••<br>20 000Fh                      | No Access        | xl  | Read/<br>Write                | (3)                           |  |

| Reserved                                  | 20 0010h<br>2F FFFFh                             | No Access        |     | (3)                           |                               |  |

| Configuration                             | 30 0000h<br>•••<br>30 0009h                      | No Access        | xl  | Read/<br>Write <sup>(1)</sup> | (3)                           |  |

| Reserved                                  | 30 000Ah<br>30 FFFFh                             | No Access        |     |                               |                               |  |

| User Data Memory<br>(Data EEPROM)         | 31 0000h<br>•••<br>31 03FFh                      | No Access        | 00  | (3)                           | Read/<br>Write <sup>(1)</sup> |  |

| Reserved                                  | 31 0400h<br>3E FFFFh                             | No Access        |     | (3)                           |                               |  |

| Device Information Area<br>(DIA)          | 3F 0000h<br>•••<br>3F 003Fh                      | No Access        | xl  | Read                          | (3)                           |  |

| Reserved                                  | 3F 0040h<br>3F FF09h                             | No Access        |     | (3)                           |                               |  |

| Device Configuration Information<br>(DCI) | 3F FF00h<br>•••<br>3F FF09h                      | No Access        | xl  | Read                          | (3)                           |  |

| Reserved                                  | 3F FF0Ah<br>3F FFFBh                             | No Access        | (3) |                               |                               |  |

| Revision ID/<br>Device ID                 | 3F FFFCh<br>•••<br>3F FFFFh                      | No Access        | x1  | Read                          | (3)                           |  |

## TABLE 13-1: NVM ORGANIZATION AND ACCESS INFORMATION

Note 1: Subject to Memory Write Protection settings.

2: User IDs are eight words ONLY. There is no code protection, table read protection or write protection implemented for this region.

3: Reads as '0', writes clear the WR bit and WRERR bit is set.

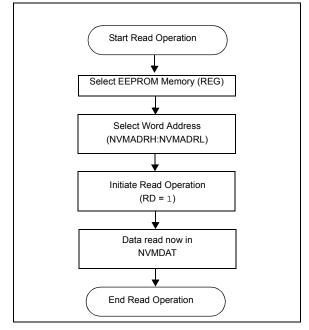

#### 13.3.3 READING THE DATA EEPROM MEMORY

To read a data memory location, the user must write the address to the NVMADRL and NVMADRH register pair, clear REG<1:0> control bit in NVMCON1 register to access Data EEPROM locations and then set control bit, RD. The data is available on the very next instruction cycle; therefore, the NVMDAT register can be read by the next instruction. NVMDAT will hold this value until another read operation, or until it is written to by the user (during a write operation).

The basic process is shown in Example 13-5.

#### FIGURE 13-11: DATA EEPROM READ FLOWCHART

## 13.3.4 WRITING TO THE DATA EEPROM MEMORY

To write an EEPROM data location, the address must first be written to the NVMADRL and NVMADRH register pair and the data written to the NVMDAT register. The sequence in Example 13-6 must be followed to initiate the write cycle.

The write will not begin if NVM Unlock sequence, described in **Section 13.1.4 "NVM Unlock Sequence"**, is not exactly followed for each byte. It is strongly recommended that interrupts be disabled during this code segment.

Additionally, the WREN bit in NVMCON1 must be set to enable writes. This mechanism prevents accidental writes to data EEPROM due to unexpected code execution (i.e., runaway programs). The WREN bit should be kept clear at all times, except when updating the EEPROM. The WREN bit is not cleared by hardware.

After a write sequence has been initiated, NVMCON1, NVMADRL, NVMADRH and NVMDAT cannot be modified. The WR bit will be inhibited from being set unless the WREN bit is set. Both WR and WREN cannot be set with the same instruction.

After a write sequence has been initiated, clearing the WREN bit will not affect this write cycle. A single Data EEPROM word is written and the operation includes an implicit erase cycle for that word (it is not necessary to set FREE). CPU execution continues in parallel and at the completion of the write cycle, the WR bit is cleared in hardware and the NVM Interrupt Flag bit (NVMIF) is set. The user can either enable this interrupt or poll this bit. NVMIF must be cleared by software.

#### **REGISTER 13-5: NVMDAT: DATA EEPROM MEMORY DATA**

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0          | R/W-0/0          | R/W-0/0  | R/W-0/0 |

|------------------|---------|-------------------|---------|------------------|------------------|----------|---------|

|                  |         |                   | DAT     | <7:0>            |                  |          |         |

| bit 7            |         |                   |         |                  |                  |          | bit 0   |

|                  |         |                   |         |                  |                  |          |         |

| Legend:          |         |                   |         |                  |                  |          |         |

| R = Readable     | bit     | W = Writable I    | oit     | U = Unimpler     | nented bit, read | d as '0' |         |

| x = Bit is unkno | own     | '0' = Bit is clea | ared    | '1' = Bit is set |                  |          |         |

| -n = Value at F  | POR     |                   |         |                  |                  |          |         |

bit 7-0 **DAT<7:0>:** The value of the data memory word returned from NVMADR after a Read command, or the data written by a Write command.

## TABLE 13-5: SUMMARY OF REGISTERS ASSOCIATED WITH NONVOLATILE MEMORY CONTROL

| Name    | Bit 7                            | Bit 6                 | Bit 5 | Bit 4 | Bit 3     | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |

|---------|----------------------------------|-----------------------|-------|-------|-----------|-------|-------|-------|---------------------|

| NVMCON1 | REG<1:0> — FREE WRERR WREN WR RD |                       |       |       |           |       | 200   |       |                     |

| NVMCON2 |                                  |                       |       | Unloc | k Pattern |       |       |       | 201                 |

| NVMADRL |                                  |                       |       | NVMA  | .DR<7:0>  |       |       |       | 201                 |

| NVMADRH | _                                | - — — — — NVMADR<9:8> |       |       |           |       | 201   |       |                     |

| NVMDAT  |                                  |                       |       | NVME  | OAT<7:0>  |       |       |       | 202                 |

Legend: — = unimplemented, read as '0'. Shaded bits are not used during EEPROM access.

\*Page provides register information.

## 14.8 Scanner Module Overview

The Scanner allows segments of the Program Flash Memory or Data EEPROM, to be read out (scanned) to the CRC Peripheral. The Scanner module interacts with the CRC module and supplies it data one word at a time. Data is fetched from the address range defined by SCANLADR registers up to the SCANHADR registers.

The Scanner begins operation when the SGO bit is set (SCANCON0 Register) and ends when either SGO is cleared by the user or when SCANLADR increments past SCANHADR. The SGO bit is also cleared by clearing the EN bit (CRCCON0 register).

## 14.9 Configuring the Scanner

The scanner module may be used in conjunction with the CRC module to perform a CRC calculation over a range of program memory or Data EEPROM addresses. In order to set up the scanner to work with the CRC, perform the following steps:

- Set up the CRC module (See Section 14.7 "Configuring the CRC") and enable the Scanner module by setting the EN bit in the SCANCON0 register.

- 2. Choose which memory region the Scanner module should operate on and set the MREG bit of the SCANCON0 register appropriately.

- 3. If trigger is used for scanner operation, set the TRIGEN bit of the SCANCON0 register and select the trigger source using SCANTRIG register. Select the trigger source using SCANTRIG register and then set the TRIGEN bit of the SCANCON0 register. See Table 14-1 for Scanner Operation.

- 4. If Burst mode of operation is desired, set the BURSTMD bit (SCANCON0 register). See Table 14-1 for Scanner Operation.

- 5. Set the SCANLADRL/H/U and SCANHADRL/H/ U registers with the beginning and ending locations in memory that are to be scanned.

- Select the priority level for the Scanner module (See Section 3.1 "System Arbitration") and lock the priorities (See Section 3.1.1 "Priority Lock").

- 7. Both CRCEN and CRCGO bits must be enabled to use the scanner. Setting the SGO bit will start the scanner operation.

## 14.10 Scanner Interrupt

The scanner will trigger an interrupt when the SCANLADR increments past SCANHADR. The SCANIF bit can only be cleared in software.

## 14.11 Scanning Modes

The interaction of the scanner with the system operation is controlled by the priority selection in the System Arbiter (see **Section 3.2 "Memory Access Scheme"**). Additionally, BURSTMD and TRIGEN also determine the operation of the Scanner.

14.11.1 TRIGEN = 0, BURSTMD = 0

In this case, the memory access request is granted to the scanner if no other higher priority source is requesting access.

All sources with lower priority than the scanner will get the memory access cycles that are not utilized by the scanner.

#### **14.11.2 TRIGEN =** 1, **BURSTMD =** 0

In this case, the memory access request is generated when the CRC module is ready to accept.

The memory access request is granted to the scanner if no other higher priority source is requesting access. All sources with lower priority than the scanner will get the memory access cycles that are not utilized by the scanner.

The memory access request is granted to the scanner if no other higher priority source is requesting access. All sources with lower priority than the scanner will get the memory access cycles that are not utilized by the scanner.

#### 14.11.3 TRIGEN = x, BURSTMD = 1

In this case, the memory access is always requested by the scanner.

The memory access request is granted to the scanner if no other higher priority source is requesting access. The memory access cycles will not be granted to lower priority sources than the scanner until it completes operation i.e., SGO = 0 (SCANCON0 register)

**Note:** If TRIGEN = 1 and BURSTMD = 1, the user should ensure that the trigger source is active for the Scanner operation to complete.

## **16.5** Register Definitions: Port Control

| R/W-x/u                 | R/W-x/u | R/W-x/u                           | R/W-x/u | R/W-x/u                         | R/W-x/u          | R/W-x/u  | R/W-x/u |

|-------------------------|---------|-----------------------------------|---------|---------------------------------|------------------|----------|---------|

| Rx7                     | Rx6     | Rx5                               | Rx4     | Rx3                             | Rx2              | Rx1      | Rx0     |

| bit 7                   | •       |                                   | •       | •                               |                  |          | bit     |

| Legend:                 |         |                                   |         |                                 |                  |          |         |

| Legend:<br>R = Readable | bit     | W = Writable                      | bit     | U = Unimplen                    | nented bit, read | d as '0' |         |

| •                       | bit     | W = Writable<br>'0' = Bit is clea |         | U = Unimplen<br>x = Bit is unkr |                  | d as '0' |         |

bit 7-0 **Rx<7:0>:** Rx7:Rx0 Port I/O Value bits 1 = Port pin is ≥ VIH 0 = Port pin is ≤ VIL

**Note 1:** Writes to PORTx are actually written to the corresponding LATx register. Reads from PORTx register return actual I/O pin values.

## TABLE 16-2: PORT REGISTERS

| Name  | Bit 7              | Bit 6              | Bit 5 | Bit 4 | Bit 3              | Bit 2 | Bit 1 | Bit 0 |

|-------|--------------------|--------------------|-------|-------|--------------------|-------|-------|-------|

| PORTA | RA7                | RA6                | RA5   | RA4   | RA3                | RA2   | RA1   | RA0   |

| PORTB | RB7 <sup>(1)</sup> | RB6 <sup>(1)</sup> | RB5   | RB4   | RB3                | RB2   | RB1   | RB0   |

| PORTC | RC7                | RC6                | RC5   | RC4   | RC3                | RC2   | RC1   | RC0   |

| PORTE | _                  | _                  | -     | -     | RE3 <sup>(2)</sup> | _     |       | _     |

Note 1: Bits RB6 and RB7 read '1' while in Debug mode.

2: Bit PORTE3 is read-only, and will read '1' when MCLRE = 1 (Master Clear enabled).

## 24.1.5 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is ten bits when T2PR is 255. The resolution is a function of the T2PR register value as shown by Equation 24-4.

## EQUATION 24-4: PWM RESOLUTION

Resolution =  $\frac{\log[4(T2PR + 1)]}{\log(2)}$  bits

**Note:** If the pulse-width value is greater than the period, the assigned PWM pin(s) will remain unchanged.

| <b>TABLE 24-1</b> : | EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz) |

|---------------------|---------------------------------------------------------|

|---------------------|---------------------------------------------------------|

| PWM Frequency             | 0.31 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale            | 64       | 4        | 1         | 1         | 1         | 1         |

| T2PR Value                | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

## TABLE 24-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 0.31 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale            | 64       | 4        | 1         | 1         | 1          | 1         |

| T2PR Value                | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

## 24.1.6 OPERATION IN SLEEP MODE

In Sleep mode, the T2TMR register will not increment and the state of the module will not change. If the PWMx pin is driving a value, it will continue to drive that value. When the device wakes up, T2TMR will continue from its previous state.

#### 24.1.7 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency (Fosc). Any changes in the system clock frequency will result in changes to the PWM frequency. Refer to Section 7.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for additional details.

#### 24.1.8 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the PWM registers to their Reset states.

#### 25.6.6 GATED WINDOWED MEASURE MODE

This mode measures the duty cycle of the SMTx\_signal input over a known input window. It does so by incrementing the timer on each pulse of the clock signal while the SMTx\_signal input is high, updating the SMTxCPR register and resetting the timer on every rising edge of the SMTWINx input after the first. See Figure 25-12 and Figure 25-13.

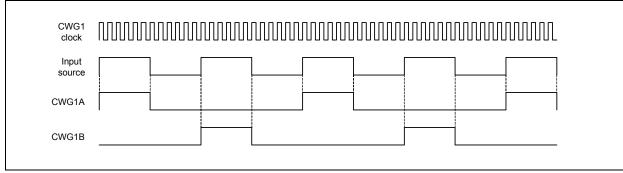

## 26.2.4 STEERING MODES

In both Synchronous and Asynchronous Steering modes, the modulated input signal can be steered to any combination of four CWG outputs and a fixed-value will be presented on all the outputs not used for the PWM output. Each output has independent polarity, steering, and shutdown options. Dead-band control is not used in either steering mode.

When STRx = 0 (Register 26-5), then the corresponding pin is held at the level defined by OVRx (Register 26-5). When STRx = 1, then the pin is driven by the modulated input signal.

The POLx bits (Register 26-2) control the signal polarity only when STRx = 1.

The CWG auto-shutdown operation also applies to steering modes as described in **Section 26.14 "Register Definitions: CWG Control"**.

Note: Only the STRx bits are synchronized; the SDATx (data) bits are not synchronized.

The CWG auto-shutdown operation also applies in Steering modes as described in **Section 26.10 "Auto-Shutdown"**. An auto-shutdown event will only affect pins that have STRx = 1.

#### 26.2.4.1 Synchronous Steering Mode

In Synchronous Steering mode (MODE<2:0> bits = 001, Register 26-1), changes to steering selection registers take effect on the next rising edge of the modulated data input (Figure 26-9). In Synchronous Steering mode, the output will always produce a complete waveform.

## FIGURE 26-9: EXAMPLE OF SYNCHRONOUS STEERING (MODE<2:0> = 001)

# PIC18(L)F25/26K83

| R/W-0          | R/W-0                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W-0                                                                             | R/W-0                                                                         | R/W-0                         | R/W-0                           | R/W-0                            |  |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------|---------------------------------|----------------------------------|--|

| ACNT           | GCEN                                                                                                                                                                                     | FME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ADB                                                                               | SDAHT<                                                                        | :1:0>                         | BFRE                            | T<1:0>                           |  |

| bit 7          |                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                   | -                                                                             |                               |                                 | bit (                            |  |

|                |                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                   |                                                                               |                               |                                 |                                  |  |

| Legend:        |                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                   |                                                                               |                               |                                 |                                  |  |

| R = Readal     | ble bit                                                                                                                                                                                  | W = Writable b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                   | U = Unimpleme                                                                 | nted bit, read                | <b>d as</b> '0'                 |                                  |  |

| u = Bit is ur  | nchanged                                                                                                                                                                                 | x = Bit is unkno                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | own                                                                               | -n/n = Value at F                                                             | POR and BC                    | R/Value at all c                | other Resets                     |  |

| '1' = Bit is s | set                                                                                                                                                                                      | '0' = Bit is clea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | red                                                                               | HS = Hardware                                                                 | set HC =                      | Hardware clea                   | r                                |  |

| bit 7          | 1 = The firs<br>ister.<br>ACKD<br>receiv<br>updat                                                                                                                                        | The I2CCNT regineration The I2CCNT regineration of the I2CCNT regineration | smitted byte al<br>ster is loaded a<br>ermine the ACI<br>is prevents a<br>gister. | ble bit<br>fter the address, is<br>at the same time a<br>I2CCNT <nack></nack> | s the value is<br>the address | s moved to/fron bytes and first | n the shifter.<br>data byte of a |  |

| bit 6          | 1 = Genera                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | (00, causes ac                                                                    | 1ODE<2:0> = 00x<br>Idress match even                                          | ,                             |                                 |                                  |  |

| bit 5          | 1 = SCL is                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                   | driving SCL low. (<br>ing SCL low. (Fsci                                      |                               | (/4)                            |                                  |  |

| bit 4          | 1 = Receiv<br>Trans<br>0 = Receiv                                                                                                                                                        | <ul> <li>0 = SCL is sampled high twice before driving SCL low. (FSCL = FCLK/5)</li> <li>ADB: Address Data Buffer Disable bit</li> <li>1 = Received address data is loaded into both the I2CADB and I2CRXB<br/>Transmitted address data is loaded from the I2CTXB</li> <li>0 = Received address data is loaded only into the I2CADB<br/>Transmitted address data is loaded from the I2CADB</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                   |                                                                               |                               |                                 |                                  |  |

| bit 3-2        | 11 = Reser<br>10 = Minim<br>01 = Minim                                                                                                                                                   | SDAHT<1:0>: SDA Hold Time Selection bits<br>11 = Reserved<br>10 = Minimum of 30 ns hold time on SDA after the falling edge of SCL<br>01 = Minimum of 100 ns hold time on SDA after the falling edge of SCL<br>00 = Minimum of 300 ns hold time on SDA after the falling edge of SCL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                   |                                                                               |                               |                                 |                                  |  |

| bit 1-0        | <b>BFRET&lt;1:0&gt;:</b> Bus Free Time Selection bits<br>$11 = 64 \ I^2C$ Clock pulses<br>$10 = 32 \ I^2C$ Clock pulses<br>$01 = 16 \ I^2C$ Clock pulses<br>$00 = 8 \ I^2C$ Clock pulses |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                   |                                                                               |                               |                                 |                                  |  |

# PIC18(L)F25/26K83

| REGISTER 3                                                                                                                                                          | 3-11: I2CxP                                                                                                                                                                                                           | E: I2CxIE IN                                             |              | AND HOLD E                                                           | NABLE RE       | GISTER              |             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------------|----------------------------------------------------------------------|----------------|---------------------|-------------|

| R/W-0                                                                                                                                                               | R/W-0                                                                                                                                                                                                                 | U-0                                                      | R/W-0        | R/W-0                                                                | R/W-0          | R/W-0               | R/W-0       |

| CNTIE                                                                                                                                                               | ACKTIE                                                                                                                                                                                                                | _                                                        | WRIE         | ADRIE                                                                | PCIE           | RSCIE               | SCIE        |

| bit 7                                                                                                                                                               |                                                                                                                                                                                                                       |                                                          |              |                                                                      |                |                     | bit 0       |

|                                                                                                                                                                     |                                                                                                                                                                                                                       |                                                          |              |                                                                      |                |                     |             |

| Legend:                                                                                                                                                             |                                                                                                                                                                                                                       |                                                          |              |                                                                      |                |                     |             |

| R = Readable                                                                                                                                                        | bit                                                                                                                                                                                                                   | W = Writable                                             | bit          | U = Unimpler                                                         | mented bit, re | ead as '0'          |             |

| u = Bit is unch                                                                                                                                                     | anged                                                                                                                                                                                                                 | x = Bit is unkr                                          | own          | -n/n = Value                                                         | at POR and I   | BOR/Value at all of | ther Resets |

| '1' = Bit is set                                                                                                                                                    |                                                                                                                                                                                                                       | '0' = Bit is clea                                        | ared         | HS = Hardwa                                                          | are set HC     | C = Hardware clear  |             |

| bit 7                                                                                                                                                               | 1 = When CN                                                                                                                                                                                                           | Count Interrupt<br>NTIF is set<br>nt interrupts are      |              |                                                                      |                |                     |             |

| bit 6                                                                                                                                                               | ACKTIE: Acknowledge Interrupt and Hold Enable bit<br>1 = When ACKTIF is set<br>If ACK is generated, CSTR is also set.<br>If NACK is generated, CSTR is unchanged<br>0 = Acknowledge holding and interrupt is disabled |                                                          |              |                                                                      |                |                     |             |

| bit 5                                                                                                                                                               | Unimplemen                                                                                                                                                                                                            | ted: Read as '                                           | )'           |                                                                      |                |                     |             |

| bit 4                                                                                                                                                               | 1 = When W                                                                                                                                                                                                            | Write Interrupt a<br>RIF is set; CST<br>te holding and i | R is set     |                                                                      |                |                     |             |

| bit 3                                                                                                                                                               | 1 = When AD                                                                                                                                                                                                           | ess Interrupt ar<br>DRIF is set; CS<br>holding and int   | TR is set    |                                                                      |                |                     |             |