Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2000.00                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                  |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 4K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-UQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-UQFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf26k83-e-mx |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| REGISTER 3-3 |           | SUNATION | NOND 3E (3 | 0 000411)  |       |       |       |

|--------------|-----------|----------|------------|------------|-------|-------|-------|

| U-1          | R/W-1     | R/W-1    | R/W-1      | R/W-1      | R/W-1 | R/W-1 | R/W-1 |

| —            | WDTE<1:0> |          |            | WDTCPS<4:0 |       | >     |       |

| bit 7        |           |          |            |            |       |       | bit 0 |

|              |           |          |            |            |       |       |       |

#### REGISTER 5-5: CONFIGURATION WORD 3L (30 0004h)

| Legend:                     |                  |                            |                    |

|-----------------------------|------------------|----------------------------|--------------------|

| R = Readable bit            | W = Writable bit | U = Unimplemented bit, rea | d as '1'           |

| -n = Value for blank device | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 7 Unimplemented: Read as '1'

Γ.

bit 6-5 WDTE<1:0>: WDT Operating Mode bits

00 = WDT is disabled, SWDTEN is ignored

01 = WDT is enabled/disabled by the SWDTEN bit in WDTCON0

10 = WDT is enabled while Sleep = 0, suspended when Sleep = 1; SWDTEN is ignored

11 = WDT is enabled regardless of Sleep; SWDTEN is ignored

bit 4-0 WDTCPS<4:0>: WDT Period Select bits

|             |           | O officiaria O o stand |                 |                                    |                                 |

|-------------|-----------|------------------------|-----------------|------------------------------------|---------------------------------|

| WDTCPS<4:0> | Value     | Divider Ra             | tio             | Typical Time-out<br>(Fın = 31 kHz) | - Software Control<br>of WDTPS? |

| 00000       | 00000     | 1:32                   | 2 <sup>5</sup>  | 1 ms                               |                                 |

| 00001       | 00001     | 1:64                   | 2 <sup>6</sup>  | 2 ms                               |                                 |

| 00010       | 00010     | 1:128                  | 2 <sup>7</sup>  | 4 ms                               |                                 |

| 00011       | 00011     | 1:256                  | 2 <sup>8</sup>  | 8 ms                               |                                 |

| 00100       | 00100     | 1:512                  | 2 <sup>9</sup>  | 16 ms                              |                                 |

| 00101       | 00101     | 1:1024                 | 2 <sup>10</sup> | 32 ms                              |                                 |

| 00110       | 00110     | 1:2048                 | 2 <sup>11</sup> | 64 ms                              |                                 |

| 00111       | 00111     | 1:4096                 | 2 <sup>12</sup> | 128 ms                             |                                 |

| 01000       | 01000     | 1:8192                 | 2 <sup>13</sup> | 256 ms                             |                                 |

| 01001       | 01001     | 1:16384                | 2 <sup>14</sup> | 512 ms                             | No                              |

| 01010       | 01010     | 1:32768                | 2 <sup>15</sup> | 1s                                 |                                 |

| 01011       | 01011     | 1:65536                | 2 <sup>16</sup> | 2s                                 |                                 |

| 01100       | 01100     | 1:131072               | 2 <sup>17</sup> | 4s                                 |                                 |

| 01101       | 01101     | 1:262144               | 2 <sup>18</sup> | 8s                                 |                                 |

| 01110       | 01110     | 1:524299               | 2 <sup>19</sup> | 16s                                |                                 |

| 01111       | 01111     | 1:1048576              | 2 <sup>20</sup> | 32s                                |                                 |

| 10000       | 10000     | 1:2097152              | 2 <sup>21</sup> | 64s                                |                                 |

| 10001       | 10001     | 1:4194304              | 2 <sup>22</sup> | 128s                               |                                 |

| 10010       | 10010     | 1:8388608              | 2 <sup>23</sup> | 256s                               | 1                               |

| 10011       | 10011     |                        | _               |                                    |                                 |

| <br>11110   | <br>11110 | 1:32                   | 2 <sup>5</sup>  | 1 ms                               | No                              |

| 11111       | 01011     | 1:65536                | 2 <sup>16</sup> | 2s                                 | Yes                             |

| R/W-1/1         | R/W-1/1                               | R/W-1/1                                                  | R/W-1/1         | R/W-1/1                | R/W-1/1           | R/W-1/1            | R/W-1/1   |  |  |  |  |

|-----------------|---------------------------------------|----------------------------------------------------------|-----------------|------------------------|-------------------|--------------------|-----------|--|--|--|--|

| I2C1RXIP        | SPI1IP                                | SPI1TXIP                                                 | SPI1RXIP        | DMA1AIP                | DMA10RIP          | DMA1DCNTIP         | DMA1SCNTI |  |  |  |  |

| bit 7           |                                       |                                                          |                 |                        |                   |                    | bit       |  |  |  |  |

|                 |                                       |                                                          |                 |                        |                   |                    |           |  |  |  |  |

| Legend:         |                                       |                                                          |                 |                        |                   |                    |           |  |  |  |  |

| R = Readab      | le bit                                | W = Writable                                             | bit             | U = Unimplem           | ented bit, read a | as 'O'             |           |  |  |  |  |

| u = Bit is un   | changed                               | x = Bit is unk                                           | nown            | -n/n = Value at        | POR and BOR       | /Value at all othe | er Resets |  |  |  |  |

| '1' = Bit is se | et                                    | '0' = Bit is cle                                         | eared           |                        |                   |                    |           |  |  |  |  |

|                 |                                       | _                                                        |                 |                        |                   |                    |           |  |  |  |  |

| bit 7           |                                       | l <sup>2</sup> C1 Receive I                              | nterrupt Prior  | ity bit                |                   |                    |           |  |  |  |  |

|                 | 1 = High pr                           | •                                                        |                 |                        |                   |                    |           |  |  |  |  |

|                 | 0 = Low pri                           | -                                                        |                 | 1.11                   |                   |                    |           |  |  |  |  |

| bit 6           | 1 = High pr                           | 11 Transmit Inte                                         | errupt Priority | DI                     |                   |                    |           |  |  |  |  |

|                 | 0 = Low pri                           |                                                          |                 |                        |                   |                    |           |  |  |  |  |

| bit 5           |                                       | <sup>2</sup> C1 Transmit I                               | nterrupt Prior  | ity bit                |                   |                    |           |  |  |  |  |

|                 | 1 = High pr                           |                                                          | ·               |                        |                   |                    |           |  |  |  |  |

|                 | 0 = Low priority                      |                                                          |                 |                        |                   |                    |           |  |  |  |  |

| bit 4           |                                       | SPI1 Receive                                             | nterrupt Prior  | rity bit               |                   |                    |           |  |  |  |  |

|                 | 1 = High pr                           | •                                                        |                 |                        |                   |                    |           |  |  |  |  |

| bit 3           | 0 = Low pri                           | •                                                        | onomit Intorr   | unt Driarity bit       |                   |                    |           |  |  |  |  |

| DIT 3           |                                       | DMA1 Abort Tr                                            | ansmit intern   | apt Priority bit       |                   |                    |           |  |  |  |  |

|                 | 1 = High priority<br>0 = Low priority |                                                          |                 |                        |                   |                    |           |  |  |  |  |

| bit 2           |                                       | : DMA1 Overn                                             | un Interrupt P  | riority bit            |                   |                    |           |  |  |  |  |

|                 | 1 = High pr                           |                                                          | ·               | -                      |                   |                    |           |  |  |  |  |

|                 | 0 = Low pri                           | ority                                                    |                 |                        |                   |                    |           |  |  |  |  |

| bit 1           |                                       | MA1DCNTIP: DMA1 Destination Count Interrupt Priority bit |                 |                        |                   |                    |           |  |  |  |  |

|                 | 1 = High priority                     |                                                          |                 |                        |                   |                    |           |  |  |  |  |

| <b>h</b> it 0   | 0 = Low pri                           | -                                                        | uraa Caunt In   | to unu unt Duio uitu d | :4                |                    |           |  |  |  |  |

| bit 0           | 1 = High pr                           |                                                          | arce Count In   | terrupt Priority b     | nt                |                    |           |  |  |  |  |

|                 | ⊥ – r⊐ign pr                          |                                                          |                 |                        |                   |                    |           |  |  |  |  |

#### REGISTER 9-25: IPR2: PERIPHERAL INTERRUPT PRIORITY REGISTER 2

## **10.4** Register Definitions: Voltage Regulator Control

| U-0              | U-0                                                   | U-0                                                      | U-0           | U-0                                                   | U-0              | R/W-0/0 | R/W-1/1  |  |  |  |

|------------------|-------------------------------------------------------|----------------------------------------------------------|---------------|-------------------------------------------------------|------------------|---------|----------|--|--|--|

| _                | —                                                     | —                                                        | —             | _                                                     | —                | VREGPM  | Reserved |  |  |  |

| bit 7            |                                                       |                                                          |               |                                                       |                  |         | bit 0    |  |  |  |

|                  |                                                       |                                                          |               |                                                       |                  |         |          |  |  |  |

| Legend:          |                                                       |                                                          |               |                                                       |                  |         |          |  |  |  |

| R = Readable     | e bit                                                 | W = Writable                                             | bit           | U = Unimpler                                          | mented bit, read | as '0'  |          |  |  |  |

| u = Bit is unc   | hanged                                                | x = Bit is unkr                                          | nown          | -n/n = Value at POR and BOR/Value at all other Resets |                  |         |          |  |  |  |

| '1' = Bit is set | t                                                     | '0' = Bit is clea                                        | ared          |                                                       |                  |         |          |  |  |  |

|                  |                                                       |                                                          |               |                                                       |                  |         |          |  |  |  |

| bit 7-2          | Unimplemen                                            | ted: Read as '                                           | 0'            |                                                       |                  |         |          |  |  |  |

| bit 1            | VREGPM: Vo                                            | oltage Regulato                                          | r Power Mode  | e Selection bit                                       |                  |         |          |  |  |  |

|                  | 1 = Low-Pow                                           | 1 = Low-Power Sleep mode enabled in Sleep <sup>(2)</sup> |               |                                                       |                  |         |          |  |  |  |

|                  | Draws lowest current in Sleep, slower wake-up         |                                                          |               |                                                       |                  |         |          |  |  |  |

|                  | 0 = Normal Power mode enabled in Sleep <sup>(2)</sup> |                                                          |               |                                                       |                  |         |          |  |  |  |

|                  | Draws hi                                              | gher current in                                          | Sleep, faster | wake-up                                               |                  |         |          |  |  |  |

| bit 0            | Reserved: R                                           | Reserved: Read as '1'. Maintain this bit set.            |               |                                                       |                  |         |          |  |  |  |

|                  |                                                       |                                                          |               |                                                       |                  |         |          |  |  |  |

#### **REGISTER 10-1:** VREGCON: VOLTAGE REGULATOR CONTROL REGISTER<sup>(1)</sup>

**Note 1:** Not present in LF parts.

2: See Section 45.0 "Electrical Specifications".

# PIC18(L)F25/26K83

| U-0              | R/W-0/0                                             | R/W-0/0           | U-0           | U-0                   | R/W-0/0          | R/W-0/0          | R/W-0/0              |

|------------------|-----------------------------------------------------|-------------------|---------------|-----------------------|------------------|------------------|----------------------|

| _                | DACMD                                               | ADCMD             | _             | —                     | CMP2MD           | CMP1MD           | ZCDMD <sup>(1)</sup> |

| bit 7            |                                                     |                   |               |                       |                  |                  | bit C                |

|                  |                                                     |                   |               |                       |                  |                  |                      |

| Legend:          |                                                     |                   |               |                       |                  |                  |                      |

| R = Readable     | e bit                                               | W = Writable      | bit           | U = Unimplen          | nented bit, read | l as '0'         |                      |

| u = Bit is unc   | hanged                                              | x = Bit is unkn   | own           | -n/n = Value a        | at POR and BO    | R/Value at all c | ther Resets          |

| '1' = Bit is set | t                                                   | '0' = Bit is clea | ared          | q = Value dep         | ends on condit   | ion              |                      |

|                  |                                                     |                   |               |                       |                  |                  |                      |

| bit 7            | Unimplemer                                          | nted: Read as 'd  | )'            |                       |                  |                  |                      |

| bit 6            | DACMD: Dis                                          | able DAC bit      |               |                       |                  |                  |                      |

|                  | 1 = DAC mo                                          | dule disabled     |               |                       |                  |                  |                      |

|                  | 0 = DAC mo                                          | dule enabled      |               |                       |                  |                  |                      |

| bit 5            | ADCMD: Dis                                          | able ADCC bit     |               |                       |                  |                  |                      |

|                  |                                                     | nodule disabled   |               |                       |                  |                  |                      |

|                  |                                                     | nodule enabled    |               |                       |                  |                  |                      |

| bit 4-3          | -                                                   | nted: Read as '0  |               |                       |                  |                  |                      |

| bit 2            |                                                     | isable Compara    | tor CMP2 bit  |                       |                  |                  |                      |

|                  |                                                     | nodule disabled   |               |                       |                  |                  |                      |

| bit 1            |                                                     |                   | tor CMD1 bit  |                       |                  |                  |                      |

| bit 1            |                                                     | isable Compara    | IOF CIMP I DI |                       |                  |                  |                      |

|                  | 1 = CMP1 module disabled<br>0 = CMP1 module enabled |                   |               |                       |                  |                  |                      |

| bit 0            |                                                     | able Zero-Cross   | Detect modu   | le bit <sup>(1)</sup> |                  |                  |                      |

|                  | 1 = ZCD mod                                         |                   |               |                       |                  |                  |                      |

|                  | 0 = ZCD mod                                         |                   |               |                       |                  |                  |                      |

| Noto 1: Si       | $\frac{1}{200}$                                     |                   |               |                       |                  |                  |                      |

#### REGISTER 19-3: PMD2: PMD CONTROL REGISTER 2

**Note 1:** Subject to ZCD bit in CONFIG2H.

# PIC18(L)F25/26K83

#### REGISTER 20-2: T0CON1: TIMER0 CONTROL REGISTER 1

| Lanandı |         |         |         |         |         |         |         |

|---------|---------|---------|---------|---------|---------|---------|---------|

| bit 7   |         |         |         |         |         |         | bit 0   |

|         | CS<2:0> |         | ASYNC   |         | CKPS    | <3:0>   |         |

| R/W-0/0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-5 | CS<2:0>:Timer0 Clock Source Select bits<br>111 = CLC1<br>110 = SOSC<br>101 = MFINTOSC (500 kHz)<br>100 = LFINTOSC<br>011 = HFINTOSC<br>010 = Fosc/4<br>001 = Pin selected by T0CKIPPS (Inverted)<br>000 = Pin selected by T0CKIPPS (Non-inverted)                                                 |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | <ul> <li>ASYNC: TMR0 Input Asynchronization Enable bit</li> <li>1 = The input to the TMR0 counter is not synchronized to system clocks</li> <li>0 = The input to the TMR0 counter is synchronized to Fosc/4</li> </ul>                                                                            |

| bit 3-0 | CKPS<3:0>: Prescaler Rate Select bit<br>1111 = 1:32768<br>1110 = 1:16384<br>1101 = 1:8192<br>1100 = 1:4096<br>1011 = 1:2048<br>1010 = 1:1024<br>1001 = 1:512<br>1000 = 1:256<br>0111 = 1:128<br>0110 = 1:64<br>0101 = 1:32<br>0100 = 1:16<br>0011 = 1:8<br>0010 = 1:4<br>0001 = 1:2<br>0000 = 1:1 |

|       | -                             | -                                             | -         | -     | _          | -     | -     | -     |                     |

|-------|-------------------------------|-----------------------------------------------|-----------|-------|------------|-------|-------|-------|---------------------|

| Name  | Bit 7                         | Bit 6                                         | Bit 5     | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |

| TxPR  | Timer2 Module Period Register |                                               |           |       |            |       |       |       |                     |

| TxTMR |                               | Holding Register for the 8-bit T2TMR Register |           |       |            |       |       |       |                     |

| TxCON | ON                            |                                               | CKPS<2:0> |       | OUTPS<3:0> |       |       |       | 323                 |

| TxCLK | —                             | —                                             | —         | —     | — CS<2:0>  |       |       |       | 320                 |

| TxRST | —                             | _                                             | _         | _     |            | 321   |       |       |                     |

| TxHLT | PSYNC                         | CPOL                                          | CSYNC     |       |            | 324   |       |       |                     |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for Timer2 module. \* Page provides register information.

© 2017 Microchip Technology Inc.

Preliminary

| U-0                                     | U-0       | R/W-x/u                                                | R/W-x/u      | R/W-x/u          | R/W-x/u          | R/W-x/u          | R/W-x/u      |

|-----------------------------------------|-----------|--------------------------------------------------------|--------------|------------------|------------------|------------------|--------------|

| _                                       | _         |                                                        |              |                  | <5:0>            |                  |              |

| bit 7                                   |           |                                                        |              |                  |                  |                  | bit 0        |

|                                         |           |                                                        |              |                  |                  |                  |              |

| Legend:                                 |           |                                                        |              |                  |                  |                  |              |

| R = Readable                            | e bit     | W = Writable                                           | bit          | U = Unimplen     | nented bit, read | l as '0'         |              |

| u = Bit is unchanged x = Bit is unknown |           |                                                        | nown         | -n/n = Value a   | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is se                         | t         | '0' = Bit is cle                                       | ared         | q = Value dep    | ends on condit   | ion              |              |

|                                         |           |                                                        |              |                  |                  |                  |              |

| bit 7-6                                 | Unimplem  | ented: Read as '                                       | 0'           |                  |                  |                  |              |

| bit 5-0                                 | DBR<5:0>: | CWG Rising Ed                                          | ge Triggered | Dead-Band Cou    | nt bits          |                  |              |

|                                         | 11 1111 = | 63-64 CWG clo                                          | ock periods  |                  |                  |                  |              |

|                                         | 11 1110 = | 62-63 CWG clo                                          | ock periods  |                  |                  |                  |              |

|                                         |           |                                                        |              |                  |                  |                  |              |

|                                         | •         |                                                        |              |                  |                  |                  |              |

|                                         | •         |                                                        |              |                  |                  |                  |              |

|                                         |           | 2-3 CWG clock                                          | •            |                  |                  |                  |              |

|                                         |           | <ul> <li>1-2 CWG clock</li> <li>0 CWC clock</li> </ul> | •            | hand concretion  | a ia hu naaaad   |                  |              |

|                                         | 00 0000 = |                                                        | enous. Dead- | -band generation | n is by-passed   |                  |              |

#### **REGISTER 26-8: CWGxDBR: CWG RISING DEAD-BAND COUNT REGISTER**

#### REGISTER 26-9: CWGxDBF: CWG FALLING DEAD-BAND COUNT REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   |         |         | DBF∙    | <5:0>   |         |         |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7-6 | Unimplemented: Read as '0'                                        |

|---------|-------------------------------------------------------------------|

| bit 5-0 | DBF<5:0>: CWG Falling Edge Triggered Dead-Band Count bits         |

|         | 11 1111 = 63-64 CWG clock periods                                 |

|         | 11 1110 = 62-63 CWG clock periods                                 |

|         |                                                                   |

|         |                                                                   |

|         | •                                                                 |

|         | 00 0010 = 2-3 CWG clock periods                                   |

|         | 00 0001 = 1-2 CWG clock periods                                   |

|         | 00 0000 = 0 CWG clock periods. Dead-band generation is by-passed. |

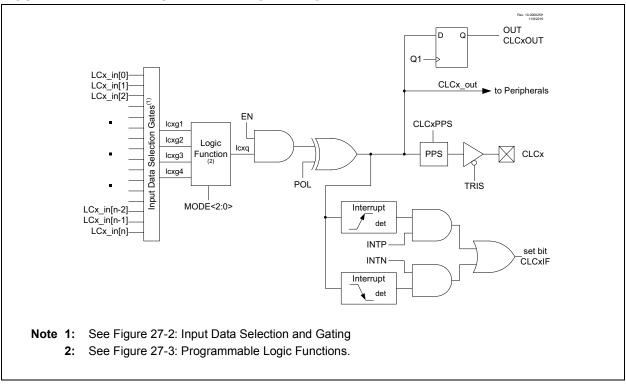

#### 27.1 CLCx Setup

Programming the CLCx module is performed by configuring the four stages in the logic signal flow. The four stages are:

- Data selection

- Data gating

- Logic function selection

- Output polarity

Each stage is setup at run time by writing to the corresponding CLCx Special Function Registers. This has the added advantage of permitting logic reconfiguration on-the-fly during program execution.

#### 27.1.1 DATA SELECTION

There are 32 signals available as inputs to the configurable logic. Four 32-input multiplexers are used to select the inputs to pass on to the next stage.

Data selection is through four multiplexers as indicated on the left side of Figure 27-2. Data inputs in the figure are identified by a generic numbered input name.

Table 27-1 correlates the generic input name to the actual signal for each CLC module. The column labeled 'DyS<4:0> Value' indicates the MUX selection code for the selected data input. DyS is an abbreviation for the MUX select input codes: D1S<4:0> through D4S<4:0>.

Data inputs are selected with CLCxSEL0 through CLCxSEL3 registers (Register 27-3 through Register 27-6).

**Note:** Data selections are undefined at power-up.

#### 32.4.2 VARIABLE TRANSFER SIZE MODE (BMODE = 1)

In this mode, SPIxTWIDTH specifies the width of every individual piece of the data transfer in bits. SPIxTCTH/ SPIxTCTL specifies the number of transfers of this bit length. If SPIxTWIDTH = 0, each piece is a full byte of data. If SPIxTWIDTH  $\neq$  0, then only the specified number of bits from the transmit FIFO are shifted out, with the unused bits ignored. Received data is padded with zeros in the unused bit areas when transfered into the receive FIFO. The LSBF bit of SPIxCON0 determines whether the Most Significant or Least Significant bits of the transfers are ignored/padded. In this mode, the transfer counter being zero only stops messages from being sent/received when in "Receive only" mode.

**Note:** With BMODE = 1, it is possible for the transfer counter (SPIxTCTH/L) to decrement below zero, although when in "Receive Only" Master mode, transfer clocks will cease when the transfer counter reaches zero.

## 32.4.3 TRANSFER COUNTER IN SLAVE MODE

In Slave mode, the transfer counter will still decrement as data is shifted in and out of the SPI module, but it will not control data transfers. In addition, in Slave mode, the BMODE bit along with the transfer counter is used to determine when the device should look for Slave Select faults. If BMODE = 0, the SSFLT bit will be set if Slave Select transitions from its active to inactive state during bytes of data, as well as if it transitions before the last bit sent during the final byte (if SPIxTWIDTH≠0). If BMODE=1, the SSFLT bit will be set if Slave Select transitions from its active to inactive state before the final bit of each individual transfer is completed. Note that SSFLT does not have an associated interrupt, so it should be checked in software. An ideal time to do this is when the End of Slave Select Interrupt (EOSIF) is triggered (see Section 32.8.3.3 "Start of Slave Select and End of Slave Select Interrupts").

#### 32.5 Master mode

In Master mode, the device controls the SCK line, and as such, initiates data transfers and determines when any slaves broadcast data onto the SPI bus.

Master mode of this device can be configured in four different modes, configured by the TXR and RXR bits:

- · Full-Duplex mode

- Receive Only mode

- · Transmit Only mode

- Transfer Off mode

The modes are illustrated in Table 32-1, below:

## 33.1 I<sup>2</sup>C Features

- Inter-Integrated Circuit (I<sup>2</sup>C) interface supports the following modes in hardware:

- Master mode

- Slave mode with byte NACKing

- Multi-Master mode

- · Dedicated Address, Receive and Transmit buffers

- Up to four slave addresses matching

- · General Call address matching

- 7-bit and 10-bit addressing with masking

- Start, Restart, Stop, Address, Write, and ACK

Interrupts

- Clock Stretching hardware for:

- RX Buffer Full

- TX Buffer Empty

- After Address, Write, and ACK

- Bus Collision Detection with arbitration

- Bus Timeout Detection

- SDA hold time selection

- I<sup>2</sup>C, SMBus 2.0, and SMBus 3.0 input level selections

## 33.2 I<sup>2</sup>C Module Overview

The I<sup>2</sup>C module provides a synchronous interface between the microcontroller and other I<sup>2</sup>C-compatible devices using the two-wire I<sup>2</sup>C serial bus. Devices communicate in a master/slave environment. The I<sup>2</sup>C bus specifies two signal connections:

- Serial Clock (SCL)

- Serial Data (SDA)

Both the SCL and SDA connections are bidirectional open-drain lines, each requiring pull-up resistors to the supply voltage. Pulling the line to ground is considered a logical zero and letting the line float is considered a logical one. Every transaction on the I<sup>2</sup>C bus has to be initiated by the master.

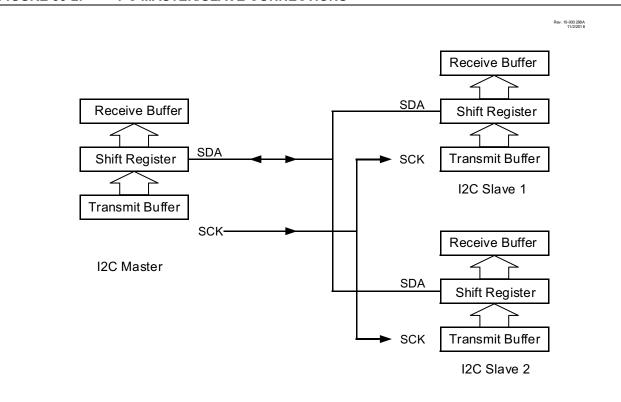

Figure 33-2 shows a typical connection between a master and more than one slave.

#### FIGURE 33-2: I<sup>2</sup>C MASTER/SLAVE CONNECTIONS

messages regardless of the values of the acceptance filters. Also, if a message has an error before the end of frame, that portion of the message assembled in the MAB before the error frame will be loaded into the buffer. This mode may serve as a valuable debugging tool for a given CAN network. It should not be used in an actual system environment as the actual system will always have some bus errors and all nodes on the bus are expected to ignore them.

In Mode 1 and 2, when a programmable buffer is configured as a transmit buffer and one or more acceptance filters are associated with it, all incoming messages matching this acceptance filter criteria will be discarded. To avoid this scenario, user firmware must make sure that there are no acceptance filters associated with a buffer configured as a transmit buffer.

#### 34.6.2 RECEIVE PRIORITY

When in Mode 0, RXB0 is the higher priority buffer and has two message acceptance filters associated with it. RXB1 is the lower priority buffer and has four acceptance filters associated with it. The lower number of acceptance filters makes the match on RXB0 more restrictive and implies a higher priority for that buffer. Additionally, the RXB0CON register can be configured such that if RXB0 contains a valid message and another valid message is received, an overflow error will not occur and the new message will be moved into RXB1 regardless of the acceptance criteria of RXB1. There are also two programmable acceptance filter masks available, one for each receive buffer (see **Section 34.4 "CAN Message Buffers"**).

In Mode 1 and 2, there are a total of 16 acceptance filters available and each can be dynamically assigned to any of the receive buffers. A buffer with a lower number has higher priority. Given this, if an incoming message matches with two or more receive buffer acceptance criteria, the buffer with the lower number will be loaded with that message.

#### 34.6.3 ENHANCED FIFO MODE

When configured for Mode 2, two of the dedicated receive buffers in combination with one or more programmable transmit/receive buffers, are used to create a maximum of an eight buffers deep FIFO buffer. In this mode, there is no direct correlation between filters and receive buffer registers. Any filter that has been enabled can generate an acceptance. When a message has been accepted, it is stored in the next available receive buffer register and an internal Write Pointer is incremented. The FIFO can be a maximum of eight buffers deep. The entire FIFO must consist of contiguous receive buffers. The FIFO head begins at RXB0 buffer and its tail spans toward B5. The maximum length of the FIFO is limited by the presence or absence of the first transmit buffer starting from B0. If a buffer is configured as a transmit buffer, the FIFO length is reduced accordingly. For instance, if B3 is

configured as a transmit buffer, the actual FIFO will consist of RXB0, RXB1, B0, B1 and B2, a total of five buffers. If B0 is configured as a transmit buffer, the FIFO length will be two. If none of the programmable buffers are configured as a transmit buffer, the FIFO will be eight buffers deep. A system that requires more transmit buffers should try to locate transmit buffers at the very end of B0-B5 buffers to maximize available FIFO length.

When a message is received in FIFO mode, the Interrupt Flag Code bits (EICODE<4:0>) in the CANSTAT register will have a value of '10000', indicating the FIFO has received a message. FIFO Pointer bits, FP<3:0> in the CANCON register, point to the buffer that contains data not yet read. The FIFO Pointer bits, in this sense, serve as the FIFO Read Pointer. The user should use the FP bits and read corresponding buffer data. When receive data is no longer needed, the RXFUL bit in the current buffer must be cleared, causing FP<3:0> to be updated by the module.

To determine whether FIFO is empty or not, the user may use the FP<3:0> bits to access the RXFUL bit in the current buffer. If RXFUL is cleared, the FIFO is considered to be empty. If it is set, the FIFO may contain one or more messages. In Mode 2, the module also provides a bit called FIFO High Water Mark (FIFOWM) in the ECANCON register. This bit can be used to cause an interrupt whenever the FIFO contains only one or four empty buffers. The FIFO high water mark interrupt can serve as an early warning to a full FIFO condition.

#### 34.6.4 TIME-STAMPING

The CAN module can be programmed to generate a time-stamp for every message that is received. When enabled, the module generates a capture signal for the CCP modules, which in turn captures the value of Timer1, Timer3 or Timer5. This value can be used as the message time-stamp.

To use the time-stamp capability, set the CTS<3:0> bits of the appropriate CCPxCAP register to '1000' to configure the CCP module capture input to the CAN\_rx\_- timestamp signal.

In addition, the CAN\_rx\_timestamp can be chosen as a signal input for the Signal Measurement Timer, which can be used for a variety of other timing applications.

#### **39.2** Comparator Control

Each comparator has two control registers: CMxCON0 and CMxCON1.

The CMxCON0 register (see Register 39-1) contains Control and Status bits for the following:

- Enable

- Output

- Output polarity

- · Hysteresis enable

- Timer1 output synchronization

The CMxCON1 register (see Register 39-2) contains Control bits for the following:

· Interrupt on positive/negative edge enables

The CMxPCH and CMxNCH registers are used to select the positive and negative input channels, respectively.

#### 39.2.1 COMPARATOR ENABLE

Setting the EN bit of the CMxCON0 register enables the comparator for operation. Clearing the EN bit disables the comparator resulting in minimum current consumption.

#### 39.2.2 COMPARATOR OUTPUT

The output of the comparator can be monitored by reading either the CxOUT bit of the CMxCON0 register or the CxOUT bit of the CMOUT register.

The comparator output can also be routed to an external pin through the RxyPPS register (Register 17-2). The corresponding TRIS bit must be clear to enable the pin as an output.

Note 1: The internal output of the comparator is latched with each instruction cycle. Unless otherwise specified, external outputs are not latched.

#### 39.2.3 COMPARATOR OUTPUT POLARITY

Inverting the output of the comparator is functionally equivalent to swapping the comparator inputs. The polarity of the comparator output can be inverted by setting the POL bit of the CMxCON0 register. Clearing the POL bit results in a noninverted output.

Table 39-1 shows the output state versus input conditions, including polarity control.

# TABLE 39-1:COMPARATOR OUTPUT<br/>STATE VS. INPUT<br/>CONDITIONS

| Input Condition | POL | CxOUT |

|-----------------|-----|-------|

| CxVN > CxVP     | 0   | 0     |

| CxVN < CxVP     | 0   | 1     |

| CxVN > CxVP     | 1   | 1     |

| CxVN < CxVP     | 1   | 0     |

#### 42.1.1 STANDARD INSTRUCTION SET

| ADDF     | SR           | Add Literal to FSR                |                                                                                |            |     |          |  |  |  |

|----------|--------------|-----------------------------------|--------------------------------------------------------------------------------|------------|-----|----------|--|--|--|

| Syntax:  |              | ADDFSR                            | f, k                                                                           |            |     |          |  |  |  |

| Operan   | ds:          | $0 \le k \le 63$                  |                                                                                |            |     |          |  |  |  |

| _        |              | f ∈ [ 0, 1,                       | -                                                                              |            |     |          |  |  |  |

| Operati  |              | FSR(f) +                          | $k \rightarrow FSR($                                                           | (f)        |     |          |  |  |  |

|          | Affected:    | None                              |                                                                                |            |     |          |  |  |  |

| Encodir  | •            | 1110                              | 1000                                                                           | ffk        |     | kkkk     |  |  |  |

| Descrip  | tion:        |                                   | The 6-bit literal 'k' is added to the<br>contents of the FSR specified by 'f'. |            |     |          |  |  |  |

| Words:   |              | 1                                 |                                                                                |            |     |          |  |  |  |

| Cycles:  |              | 1                                 |                                                                                |            |     |          |  |  |  |

| Q Cycle  | e Activity:  |                                   |                                                                                |            |     |          |  |  |  |

|          |              | Q1                                | Q2                                                                             | Q3         |     | Q4       |  |  |  |

|          |              | Decod                             | Read                                                                           | Pro        |     | Write to |  |  |  |

|          |              | е                                 | literal<br>'k'                                                                 | Ces        |     | FSR      |  |  |  |

|          |              | Decod                             | Read                                                                           | Dat<br>Pro |     | Write to |  |  |  |

|          |              | e                                 | literal                                                                        | ces        |     | FSR      |  |  |  |

|          |              |                                   | 'k'                                                                            | Dat        | a   |          |  |  |  |

|          | FSR2         | = 0422h                           |                                                                                |            |     |          |  |  |  |

|          |              | ADD liter                         |                                                                                |            |     |          |  |  |  |

| Syntax:  |              | ADDLW                             | k                                                                              |            |     |          |  |  |  |

| Operan   | ds:          | $0 \le k \le 255$                 | 5                                                                              |            |     |          |  |  |  |

| Operati  | on:          | (W) + k $\rightarrow$             | $(W) + k \to W$                                                                |            |     |          |  |  |  |

| Status A | Affected:    | N, OV, C, I                       | DC, Z                                                                          |            |     |          |  |  |  |

| Encodir  | ng:          | 0000                              | 1111                                                                           | kk}        | ck  | kkkk     |  |  |  |

| Descrip  | ition:       | The conter<br>8-bit literal<br>W. |                                                                                |            |     |          |  |  |  |

| Words:   |              | 1                                 |                                                                                |            |     |          |  |  |  |

| Cycles:  |              | 1                                 |                                                                                |            |     |          |  |  |  |

| Q Cvcl   | le Activity: |                                   |                                                                                |            |     |          |  |  |  |

|          | Q1           | Q2                                | Q3                                                                             |            |     | Q4       |  |  |  |

|          | Decode       | Read                              | Proce                                                                          | SS         | Wri | te to W  |  |  |  |

| Example:   |         | ADDLW | 15h |

|------------|---------|-------|-----|

| Before Ir  | nstruc  | ction |     |

| W          | =       | 10h   |     |

| After Inst | tructio | on    |     |

| W          | =       | 25h   |     |

| ADDWF            | ADD W to f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |      |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|--|--|

| Syntax:          | ADDWF f {,d {,a}}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |      |  |  |

| Operands:        | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |      |  |  |

| Operation:       | $(W) + (f) \to dest$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |      |  |  |

| Status Affected: | N, OV, C, DC, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |      |  |  |

| Encoding:        | 0010 01da fi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | fff | ffff |  |  |

| Description:     | Add W to register 'f'. If 'd' is '0', the<br>result is stored in W. If 'd' is '1', the<br>result is stored back in register 'f'<br>(default).<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See Sec-<br>tion 42.2.3 "Byte-Oriented and Bit-<br>Oriented Instructions in Indexed Lit-<br>eral Offset Mode" for details. |     |      |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |      |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |      |  |  |

#### Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4          |

|--------|--------------|---------|-------------|

| Decode | Read         | Process | Write to    |

|        | register 'f' | Data    | destination |

REG, 0, 0 Example: ADDWF

Before Instruction

| W<br>REG        | =<br>= | 17h<br>0C2h |

|-----------------|--------|-------------|

| After Instructi | on     |             |

| W               | =      | 0D9h        |

| REG             | =      | 0C2h        |

Note: All PIC18 instructions may take an optional label argument preceding the instruction mnemonic for use in symbolic addressing. If a label is used, the instruction format then becomes: {label} instruction argument(s)

literal 'k'

Data

# PIC18(L)F25/26K83

| CPFSEQ                    | SEQ Compare f with W, skip if f = W CPFSGT                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                        | Compare                                                                                                                                                                                               | e f with W, sk              | tip if f > W                                                                                                                                                                                                                               |                                                                                                                                                                                 |                                                                                                                                                                                                                                    |  |  |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:                   | CPFSEQ                                                                                                                                                                                                                                        | f {,a}                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                       | Syntax:                     | CPFSGT                                                                                                                                                                                                                                     | CPFSGT f {,a}                                                                                                                                                                   |                                                                                                                                                                                                                                    |  |  |

| Operands:                 | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                       | Operands:                   | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                                                                                                                                                                                   | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                                                                                                                        |                                                                                                                                                                                                                                    |  |  |

| Operation:                | (f) – (W),<br>skip if (f) = (W)<br>(unsigned comparison)                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                        | Operation:                                                                                                                                                                                            | (f) – (W),<br>skip if (f) > | (W)<br>comparison)                                                                                                                                                                                                                         |                                                                                                                                                                                 |                                                                                                                                                                                                                                    |  |  |

| Status Affected:          | None                                                                                                                                                                                                                                          | . ,                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                       | Status Affected             |                                                                                                                                                                                                                                            | ,                                                                                                                                                                               |                                                                                                                                                                                                                                    |  |  |

| Encoding:                 | 0110                                                                                                                                                                                                                                          | 001a ffi                                                                                                                                                                                                                                                                                               | f ffff                                                                                                                                                                                                | Encoding:                   | 0110                                                                                                                                                                                                                                       | 010a ff:                                                                                                                                                                        | ff ffff                                                                                                                                                                                                                            |  |  |

| Description:              | location 'f' t<br>performing<br>If 'f' = W, th<br>discarded a<br>instead, ma<br>instruction.<br>If 'a' is '0', t<br>If 'a' is '0', t<br>GPR bank.<br>If 'a' is '0' a<br>set is enabl<br>in Indexed<br>mode wher<br>tion 42.2.3<br>Oriented Ir | the contents of<br>the contents of<br>the contents<br>an unsigned s<br>en the fetched<br>and a NOP is ey<br>aking this a 2-c<br>he Access Bar<br>he BSR is use<br>nd the extende<br>ed, this instruct<br>Literal Offset A<br>never $f \le 95$ (5f<br>"Byte-Orientut<br>nstructions in<br>Mode" for dei | of W by<br>ubtraction.<br>I instruction is<br>accuted<br>ycle<br>hk is selected.<br>d to select the<br>ed instruction<br>ction operates<br>addressing<br>Fh). See Sec-<br>ed and Bit-<br>Indexed Lit- | Description:                | Compares<br>location 'f'<br>performing<br>If the contents of<br>instruction<br>executed i<br>2-cycle ins<br>If 'a' is '0',<br>If 'a' is '1',<br>GPR bank<br>If 'a' is '0' a<br>set is enat<br>in Indexed<br>mode whe<br><b>tion 42.2.3</b> | the contents of<br>to the contents<br>an unsigned s<br>ents of 'f' are gr<br>f WREG, then<br>is discarded an<br>istead, making<br>truction.<br>the Access Bar<br>the BSR is use | f data memory<br>is of the W by<br>subtraction.<br>reater than the<br>the fetched<br>and a NOP is<br>this a<br>nk is selected<br>d to select the<br>ed instruction<br>ction operates<br>Addressing<br>Fh). See Sec-<br>ed and Bit- |  |  |

| Words:                    | 1                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                       |                             |                                                                                                                                                                                                                                            | t Mode" for de                                                                                                                                                                  |                                                                                                                                                                                                                                    |  |  |

| Cycles:                   | 1(2)                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                       | Words:                      | 1                                                                                                                                                                                                                                          |                                                                                                                                                                                 |                                                                                                                                                                                                                                    |  |  |

| Q Cycle Activity:         |                                                                                                                                                                                                                                               | ycles if skip an<br>a 2-word instru                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                       | Cycles:                     | by                                                                                                                                                                                                                                         | ycles if skip an<br>a 2-word instru                                                                                                                                             |                                                                                                                                                                                                                                    |  |  |

| Q1                        | Q2                                                                                                                                                                                                                                            | Q3                                                                                                                                                                                                                                                                                                     | Q4                                                                                                                                                                                                    | Q Cycle Activi              | -                                                                                                                                                                                                                                          |                                                                                                                                                                                 | _                                                                                                                                                                                                                                  |  |  |