Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                  |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 4K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

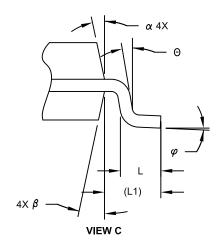

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf26k83-i-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

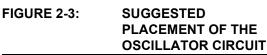

### 2.5 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to Section 7.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for details).

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-3. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins, and other signals in close proximity to the oscillator, are benign (i.e., free of high frequencies, short rise and fall times, and other similar noise).

For additional information and design guidance on oscillator circuits, refer to these Microchip Application Notes, available at the corporate website (www.microchip.com):

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices"

- AN849, "Basic PICmicro<sup>®</sup> Oscillator Design"

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

### 2.6 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state. Alternatively, connect a 1 k $\Omega$  to 10 k $\Omega$  resistor to Vss on unused pins and drive the output to logic low.

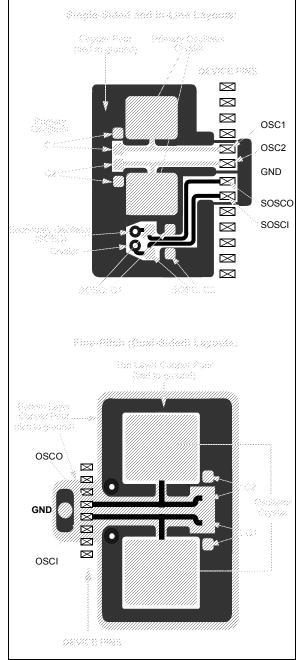

### FIGURE 7-1: SIMPLIFIED PIC<sup>®</sup> MCU CLOCK SOURCE BLOCK DIAGRAM

| REGISTER 9-39: | IVTLOCK: INTERRUPT VECTOR TABLE LOCK REGISTER |

|----------------|-----------------------------------------------|

|----------------|-----------------------------------------------|

| U-0      | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0                    |

|----------|-----|-----|-----|-----|-----|-----|----------------------------|

| _        | —   | _   | _   | —   | _   | _   | IVTLOCKED <sup>(1,2)</sup> |

| bit 7    |     |     |     |     |     |     | bit 0                      |

|          |     |     |     |     |     |     |                            |

| l egend: |     |     |     |     |     |     |                            |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-1 Unimplemented: Read as '0 |

|-----------------------------------|

|-----------------------------------|

bit 0 IVTLOCKED: IVT Registers Lock bits<sup>(1,2)</sup> 1 = IVTBASE Registers are locked and cannot be written 0 = IVTBASE Registers can be modified by write operations

#### REGISTER 9-40: SHADCON: SHADOW CONTROL REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0 |

|-------|-----|-----|-----|-----|-----|-----|---------|

| —     | -   | -   | -   | -   | _   | _   | SHADLO  |

| bit 7 |     |     |     |     |     |     | bit 0   |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-1 Unimplemented: Read as '0'

bit 0 SHADLO: Interrupt Shadow Register Access Switch bit

0 = Access Main Context for Interrupt Shadow Registers

1 = Access Low-Priority Interrupt Context for Interrupt Shadow Registers

<sup>Note 1: The IVTLOCK bit can only be set or cleared after the unlock sequence in Example 9-1.

2: If IVT1WAY = 1, the IVTLOCK bit cannot be cleared after it has been set. See Register 5-3.</sup>

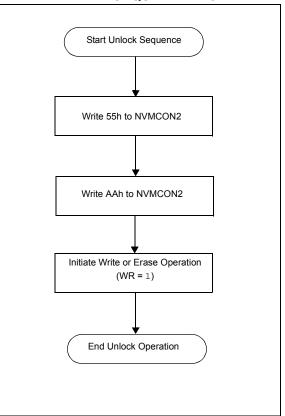

### 13.1.4 NVM UNLOCK SEQUENCE

The unlock sequence is a mechanism that protects the NVM from unintended self-write programming or erasing. The sequence must be executed and completed without interruption to successfully complete any of the following operations:

- PFM Row Erase

- Write of PFM write latches to PFM memory

- Write of PFM write latches to User IDs

- Write to Data EEPROM Memory

- · Write to Configuration Words

The unlock sequence consists of the following steps and must be completed in order:

- Write 55h to NVMCON2

- Write AAh to NMVCON2

- · Set the WR bit of NVMCON1

Once the WR bit is set, the processor will stall internal operations until the operation is complete and then resume with the next instruction.

Since the unlock sequence must not be interrupted, global interrupts should be disabled prior to the unlock sequence and re-enabled after the unlock sequence is completed.

| CARIVIFLE      | 13-2. INVIVIUNLUCK SEQUENCE                  |                                                                                                                |

|----------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| BCF<br>BANKSEL | INTCON0,GIE<br>NVMCON1                       | ; Recommended so sequence is not interrupted                                                                   |

| BSF            | NVMCON1,WREN                                 | ; Enable write/erase                                                                                           |

| MOVLW          | 55h                                          | ; Load 55h                                                                                                     |

| MOVWF          | NVMCON2                                      | ; Step 1: Load 55h into NVMCON2                                                                                |

| MOVLW          | AAh                                          | ; Step 2: Load W with AAh                                                                                      |

| MOVWF          | NVMCON2                                      | ; Step 3: Load AAh into NVMCON2                                                                                |

| BSF            | INTCON1,WR                                   | ; Step 4: Set WR bit to begin write/erase                                                                      |

| BSF            | INTCON0,GIE                                  | ; Re-enable interrupts                                                                                         |

| Note 1:        |                                              | en; steps 1-4 must occur in the cycle-accurate order<br>rrupted by an interrupt or a debugger Halt, the action |

| 2:             | Opcodes shown are illustrative; any instruct | tion that has the indicated effect may be used.                                                                |

### EXAMPLE 13-2: NVM UNLOCK SEQUENCE

### 15.0 DIRECT MEMORY ACCESS (DMA)

### 15.1 Introduction

The Direct Memory Access (DMA) module is designed to service data transfers between different memory regions directly without intervention from the CPU. By eliminating the need for CPU-intensive management of handling interrupts intended for data transfers, the CPU now can spend more time on other tasks.

PIC18(L)F25/26K83 family has two DMA modules which can be independently programmed to transfer data between different memory locations, move different data sizes, and use a wide range of hardware triggers to initiate transfers. The two DMA registers can even be programmed to work together, in order to carry out more complex data transfers without CPU overhead.

Key features of the DMA module include:

- Support access to the following memory regions:

- GPR and SFR space (R/W)

- Program Flash Memory (R only)

- Data EEPROM Memory (R only)

- Programmable priority between the DMA and CPU Operations. Refer to **Section 3.1 "System Arbitration"** for details.

- Programmable Source and Destination address modes

- Fixed address

- Post-increment address

- Post-decrement address

- Programmable Source and Destination sizes

- Source and destination pointer register, dynamically updated and reloadable

- Source and destination count register, dynamically updated and reloadable

- Programmable auto-stop based on Source or Destination counter

- · Software triggered transfers

- Multiple user selectable sources for hardware triggered transfers

- Multiple user selectable sources for aborting DMA transfers

### 15.2 DMA Registers

The operation of the DMA module has the following registers:

- Control registers (DMAxCON0, DMAxCON1)

- Data buffer register (DMAxBUF)

- Source Start Address Register (DMAxSSAU:H:L)

- Source Pointer Register (DMAxSPTRU:H:L)

- Source Message Size Register (DMAxSSZH:L)

- Source Count Register (DMAxSCNTH:L)

- Destination Start Address Register (DMAxDSAH:L)

- Destination Pointer Register (DMAxDPTRH:L)

- Destination Message Size Register (DMAxDSZH:L)

- Destination Count Register (DMAxDCNTH:L)

- Start Interrupt Request Source Register (DMAxSIRQ)

- Abort Interrupt Request Source Register (DMAxAIRQ)

These registers are detailed in Section 15.13 "Register definitions: DMA".

### 22.6 Timer2 Operation During Sleep

When PSYNC = 1, Timer2 cannot be operated while the processor is in Sleep mode. The contents of the T2TMR and T2PR registers will remain unchanged while processor is in Sleep mode.

When PSYNC = 0, Timer2 will operate in Sleep as long as the clock source selected is also still running. Selecting the LFINTOSC, MFINTOSC, or HFINTOSC oscillator as the timer clock source will keep the selected oscillator running during Sleep.

### 23.5 Register Definitions: CCP Control

Long bit name prefixes for the CCP peripherals are shown below. Refer to **Section 1.3.2.2 "Long Bit Names"** for more information.

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| CCP1       | CCP1            |

| CCP2       | CCP2            |

| CCP3       | CCP3            |

| CCP4       | CCP4            |

### **REGISTER 23-1: CCPxCON: CCPx CONTROL REGISTER**

| R/W-0/0 | U-0 | R-x | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|-----|-----|---------|---------|---------|---------|---------|

| EN      | —   | OUT | FMT     |         | MODE    | <3:0>   |         |

| bit 7   |     |     |         |         |         |         | bit 0   |

| Legend:           |                  |                                |                    |

|-------------------|------------------|--------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as | '0'                |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared           | x = Bit is unknown |

| bit 7 | EN: CCP Module Enable bit<br>1 = CCP is enabled<br>0 = CCP is disabled                                                                                                                                    |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | Unimplemented: Read as '0'                                                                                                                                                                                |

| bit 5 | OUT: CCPx Output Data bit (read-only)                                                                                                                                                                     |

| bit 4 | FMT: CCPW (pulse-width) Alignment bit<br><u>MODE = Capture mode:</u><br>Unused<br><u>MODE = Compare mode:</u><br>Unused<br><u>MODE = PWM mode:</u><br>1 = Left-aligned format<br>0 = Right-aligned format |

#### bit 3-0 MODE<3:0>: CCPx Mode Select bits

| MODE | Operating Mode | Operation                                | Set CCPxIF |

|------|----------------|------------------------------------------|------------|

| 11xx | PWM            | PWM operation                            | Yes        |

| 1011 |                | Pulse output; clear TMR1 <sup>(2)</sup>  | Yes        |

| 1010 | Compore        | Pulse output                             | Yes        |

| 1001 | Compare        | Clear output <sup>(1)</sup>              | Yes        |

| 1000 |                | Set output <sup>(1)</sup>                | Yes        |

| 0111 |                | Every 16th rising edge of CCPx input     | Yes        |

| 0110 |                | Every 4th rising edge of CCPx input      | Yes        |

| 0101 | Capture        | Every rising edge of CCPx input          | Yes        |

| 0100 |                | Every falling edge of CCPx input         | Yes        |

| 0011 |                | Every edge of CCPx input                 | Yes        |

| 0010 | Compore        | Toggle output                            | Yes        |

| 0001 | Compare        | Toggle output; clear TMR1 <sup>(2)</sup> | Yes        |

| 0000 | Disabled       |                                          | -          |

Note 1: The set and clear operations of the Compare mode are reset by setting MODE = 4 'b0000 or EN = 0.

2: When MODE = 0001 or 1011, then the timer associated with the CCP module is cleared. TMR1 is the default selection for the CCP module, so it is used for indication purpose only.

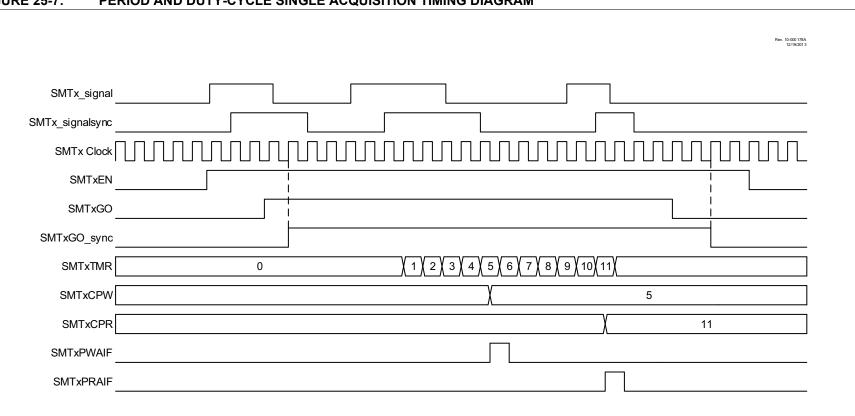

### FIGURE 25-7: PERIOD AND DUTY-CYCLE SINGLE ACQUISITION TIMING DIAGRAM

PIC18(L)F25/26K83

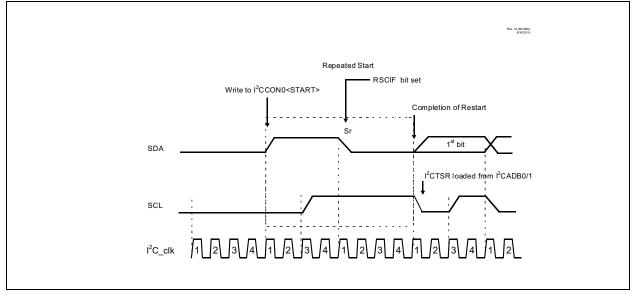

### 33.5.7 ACKNOWLEDGE SEQUENCE TIMING

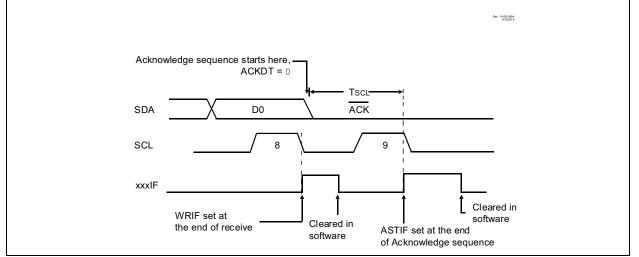

An Acknowledge sequence is enabled automatically following an address/data byte transmission. The SCL pin is pulled low and the contents of the Acknowledge Data bits (ACKDT/ACKCNT) are presented on the SDA pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The master then waits one clock period (TSCL) and the SCL pin is released high. When the SCL pin is sampled high (clock arbitration), the master counts another TSCL. The SCL pin is then pulled low. Figure 33-17 shows the timings for Acknowledge sequence.

### 33.5.8 STOP CONDITION TIMING

A Stop bit is asserted on the SDA pin at the end of receive/transmit when I2CxCNT = 0. After the last byte of a receive/transmit sequence, the SCL line is held low. The master asserts the SDA line low. The SCL pin is then released high TSCL/2 later and is detected high. The SDA pin is then released. When the SDA pin tran-

sitions high while SCL is high, the PCIF bit of the I2CxIF register is set. Figure 33-18 shows the timings for a Stop condition.

| REGISTER            | 33-7: I2CxS                             | TAT1: I <sup>2</sup> C ST          | ATUS REGI     | STER 1              |                   |                |                       |

|---------------------|-----------------------------------------|------------------------------------|---------------|---------------------|-------------------|----------------|-----------------------|

| R/W/HS-0            | U-0                                     | R-1                                | U-0           | R/W/HS-0            | R/S-0/0           | U-0            | R-0                   |

| TXWE <sup>(2)</sup> | _                                       | TXBE <sup>(1, 3)</sup>             | _             | RXRE <sup>(2)</sup> | CLRBF             | —              | RXBF <sup>(1,3)</sup> |

| bit 7               |                                         |                                    |               |                     |                   |                | bit 0                 |

| Laward              |                                         |                                    |               |                     |                   |                |                       |

| Legend:             |                                         |                                    | 1.11          |                     |                   |                |                       |

| R = Readable        |                                         | W = Writable                       |               |                     | mented bit, read  |                |                       |

| u = Bit is unc      | C C                                     | x = Bit is unkr                    |               |                     | at POR and BO     |                |                       |

| '1' = Bit is set    | t                                       | '0' = Bit is cle                   | ared          | HS = Hardwa         | are set HC =      | Hardware clea  | r                     |

| bit 7               |                                         |                                    |               | TXB when it w       | as full (Must be  | cleared by sof | tware)                |

| bit 6               | Unimplemen                              | ted: Read as '                     | 0'            |                     |                   |                |                       |

| bit 5               |                                         |                                    | •             | the I2CTXB re       | gister)           |                |                       |

| bit 4               | Unimplemen                              | ted: Read as '                     | 0'            |                     |                   |                |                       |

| bit 3               |                                         |                                    |               | B when it was e     | empty. (Must be   | cleared by sof | ftware)               |

| bit 2               | Setting this bi                         | t clears/emptie<br>t clears the RX | IF and TXIF i |                     | uffers, causing ı | reset of RXBF  | and TXBE.             |

| bit 1               | Unimplemen                              | ted: Read as '                     | 0'            |                     |                   |                |                       |

| bit 0               |                                         |                                    |               | red by reading      | the I2CRXB re     | gister)        |                       |

|                     | ne bits are held ir<br>ill cause NACK t |                                    |               | and master/sla      | ve data read by   | tes.           |                       |

**3:** Used as triggers for DMA operation.

## REGISTER 34-35: BnDLC: TX/RX BUFFER 'n' DATA LENGTH CODE REGISTERS IN TRANSMIT MODE $[0 \le n \le 5, TXnEN (BSEL \le n) = 1]^{(1)}$

| U-0          | R/W-x              | U-0                            | U-0         | R/W-x            | R/W-x            | R/W-x           | R/W-x |  |  |  |  |

|--------------|--------------------|--------------------------------|-------------|------------------|------------------|-----------------|-------|--|--|--|--|

| —            | TXRTR              |                                | —           | DLC3             | DLC2             | DLC1            | DLC0  |  |  |  |  |

| bit 7        |                    |                                |             |                  |                  |                 | bit 0 |  |  |  |  |

| Lonordi      |                    |                                |             |                  |                  |                 |       |  |  |  |  |

| Legend:      | bl- b:4            |                                | - :4        |                  |                  | H = = (0)       |       |  |  |  |  |

| R = Reada    |                    | W = Writable I                 | DIT         | -                | nented bit, read |                 |       |  |  |  |  |

| -n = Value   | at POR             | '1' = Bit is set               |             | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |  |  |  |  |

| h:4 <b>7</b> |                    |                                |             |                  |                  |                 |       |  |  |  |  |

| bit 7        | -                  | ited: Read as '0               |             |                  |                  |                 |       |  |  |  |  |

| bit 6        | TXRTR: Tran        | ismitter Remote                | Transmissio | n Request bit    |                  |                 |       |  |  |  |  |

|              |                    | ed message wi<br>ed message wi |             |                  |                  |                 |       |  |  |  |  |

| bit 5-4      | Unimplemen         | ited: Read as 'd               | )'          |                  |                  |                 |       |  |  |  |  |

| bit 3-0      | DLC<3:0>: D        | ata Length Coc                 | le bits     |                  |                  |                 |       |  |  |  |  |

|              | 1111-1001 =        | Reserved                       |             |                  |                  |                 |       |  |  |  |  |

|              | 1000 <b>= Data</b> | length = 8 bytes               | 5           |                  |                  |                 |       |  |  |  |  |

|              | 0111 <b>= Data</b> | length = 7 bytes               | 5           |                  |                  |                 |       |  |  |  |  |

|              |                    | length = 6 bytes               |             |                  |                  |                 |       |  |  |  |  |

|              |                    | 0101 = Data length = 5 bytes   |             |                  |                  |                 |       |  |  |  |  |

|              |                    | 0100 = Data length = 4 bytes   |             |                  |                  |                 |       |  |  |  |  |

|              |                    | length = 3 bytes               |             |                  |                  |                 |       |  |  |  |  |

|              |                    | length = 2 bytes               | 5           |                  |                  |                 |       |  |  |  |  |

|              |                    | length = 1 byte                |             |                  |                  |                 |       |  |  |  |  |

|              | 0000 <b>= Data</b> | length = 0 bytes               | 5           |                  |                  |                 |       |  |  |  |  |

**Note 1:** These registers are available in Mode 1 and 2 only.

### REGISTER 34-36: BSEL0: BUFFER SELECT REGISTER 0<sup>(1)</sup>

| R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | U-0   | U-0 |

|--------|--------|--------|--------|--------|--------|-------|-----|

| B5TXEN | B4TXEN | B3TXEN | B2TXEN | B1TXEN | B0TXEN | —     | —   |

| bit 7  |        |        |        |        |        | bit 0 |     |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-2 B<5:0>TXEN: Buffer 5 to Buffer 0 Transmit Enable bits

- 1 = Buffer is configured in Transmit mode

- 0 = Buffer is configured in Receive mode

- bit 1-0 Unimplemented: Read as '0'

Note 1: These registers are available in Mode 1 and 2 only.

## REGISTER 34-39: RXFnEIDH: RECEIVE ACCEPTANCE FILTER 'n' EXTENDED IDENTIFIER REGISTERS, HIGH BYTE [0 $\le$ n $\le$ 15]<sup>(1)</sup>

| R/W-x | R/W-x       | R/W-x                     | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |  |  |

|-------|-------------|---------------------------|-------|-------|-------|-------|-------|--|--|

| EID15 | EID14       | EID13 EID12 EID11 EID10 E |       | EID9  | EID8  |       |       |  |  |

| bit 7 | bit 7 bit 0 |                           |       |       |       |       |       |  |  |

|       |             |                           |       |       |       |       |       |  |  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-0 EID<15:8>: Extended Identifier Filter bits

**Note 1:** Registers, RXF6EIDH:RXF15EIDH, are available in Mode 1 and 2 only.

## REGISTER 34-40: RXFnEIDL: RECEIVE ACCEPTANCE FILTER 'n' EXTENDED IDENTIFIER REGISTERS, LOW BYTE [0 $\leq$ n $\leq$ 15]<sup>(1)</sup>

| R/W-x     | R/W-x |

|-------|-------|-------|-------|-------|-------|-----------|-------|

| EID7  | EID6  | EID5  | EID4  | EID3  | EID2  | EID2 EID1 |       |

| bit 7 |       |       |       |       |       |           | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 EID<7:0>: Extended Identifier Filter bits

**Note 1:** Registers, RXF6EIDL:RXF15EIDL, are available in Mode 1 and 2 only.

## REGISTER 34-41: RXMnSIDH: RECEIVE ACCEPTANCE MASK 'n' STANDARD IDENTIFIER MASK REGISTERS, HIGH BYTE [0 $\le$ n $\le$ 1]

| R/W-x          | R/W-x | R/W-x        | R/W-x | R/W-x        | R/W-x            | R/W-x  | R/W-x |

|----------------|-------|--------------|-------|--------------|------------------|--------|-------|

| SID10          | SID9  | SID8         | SID7  | SID6         | SID5             | SID4   | SID3  |

| bit 7          |       |              |       | ·            | •                |        | bit 0 |

|                |       |              |       |              |                  |        |       |

| Legend:        |       |              |       |              |                  |        |       |

| R = Readable I | bit   | W = Writable | bit   | U = Unimpler | mented bit, read | as '0' |       |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|-------------------|------------------|----------------------|--------------------|

|                   |                  |                      |                    |

bit 7-0 SID<10:3>: Standard Identifier Mask bits or Extended Identifier Mask bits (EID<28:21>)

| Mnem      | onic,              | Description                             | Qualas | 16-  | Bit Inst | ruction | Word | Status          | Notoo |

|-----------|--------------------|-----------------------------------------|--------|------|----------|---------|------|-----------------|-------|

| Opera     | ands               | Description                             | Cycles | MSb  |          |         | LSb  | Affected        | Notes |

| LITERAL I | NSTRUC             | TIONS                                   |        |      |          |         |      |                 |       |

| ADDLW     | k                  | Add literal and WREG                    | 1      | 0000 | 1111     | kkkk    | kkkk | C, DC, Z, OV, N |       |

| ANDLW     | k                  | AND literal with WREG                   | 1      | 0000 | 1011     | kkkk    | kkkk | Z, N            |       |

| IORLW     | k                  | Inclusive OR literal with WREG          | 1      | 0000 | 1001     | kkkk    | kkkk | Z, N            |       |

| LFSR      | f <sub>n</sub> , k | Load FSR(f <sub>n</sub> ) with a 14-bit | 2      | 1110 | 1110     | 00ff    | kkkk | None            |       |

|           |                    | literal (k)                             |        | 1111 | 00kk     | kkkk    | kkkk |                 |       |

| ADDFSR    | f <sub>n</sub> , k | Add FSR(f <sub>n</sub> ) with (k)       | 1      | 1110 | 1000     | ffkk    | kkkk | None            |       |

| SUBFSR    | f <sub>n</sub> , k | Subtract (k) from FSR(f <sub>n</sub> )  | 1      | 1110 | 1001     | ffkk    | kkkk | None            |       |

| MOVLB     | k                  | Move literal to BSR<5:0>                | 1      | 0000 | 0001     | 00kk    | kkkk | None            |       |

| MOVLW     | k                  | Move literal to WREG                    | 1      | 0000 | 1110     | kkkk    | kkkk | None            |       |

| MULLW     | k                  | Multiply literal with WREG              | 1      | 0000 | 1101     | kkkk    | kkkk | None            |       |

| RETLW     | k                  | Return with literal in WREG             | 2      | 0000 | 1100     | kkkk    | kkkk | None            |       |

| SUBLW     | k                  | Subtract WREG from literal              | 1      | 0000 | 1000     | kkkk    | kkkk | C, DC, Z, OV, N |       |

| XORLW     | k                  | Exclusive OR literal with WREG          | 1      | 0000 | 1010     | kkkk    | kkkk | Z, N            |       |

| DATA ME   | MORY – P           | ROGRAM MEMORY INSTRUCTIONS              |        |      |          |         |      |                 |       |

| TBLRD*    |                    | Table Read                              | 2 - 5  | 0000 | 0000     | 0000    | 1000 | None            |       |

| TBLRD*+   |                    | Table Read with post-increment          |        | 0000 | 0000     | 0000    | 1001 | None            |       |

| TBLRD*-   |                    | Table Read with post-decrement          |        | 0000 | 0000     | 0000    | 1010 | None            |       |

| TBLRD+*   |                    | Table Read with pre-increment           |        | 0000 | 0000     | 0000    | 1011 | None            |       |

| TBLWT*    |                    | Table Write                             | 2 - 5  | 0000 | 0000     | 0000    | 1100 | None            |       |

| TBLWT*+   |                    | Table Write with post-increment         |        | 0000 | 0000     | 0000    | 1101 | None            |       |

| TBLWT*-   |                    | Table Write with post-decrement         |        | 0000 | 0000     | 0000    | 1110 | None            |       |

| TBLWT+*   |                    | Table Write with pre-increment          |        | 0000 | 0000     | 0000    | 1111 | None            |       |

### TABLE 42-2: INSTRUCTION SET (CONTINUED)

Note 1: If Program Counter (PC) is modified or a conditional test is true, the instruction requires an additional cycle. The extra cycle is executed as a NOP.

2: Some instructions are multi word instructions. The second/third words of these instructions will be decoded as a NOP, unless the first word of the instruction retrieves the information embedded in these 16-bits. This ensures that all program memory locations have a valid instruction.

**3:** f<sub>s</sub> and f<sub>d</sub> do not cover the full memory range. 2 MSBs of bank selection are forced to 'b00 to limit the range of these instructions to lower 4k addressing space.

| BRA               | L L                                                   | Unconditional Branch                                                                                                                                                                                          |                                          |             |  |  |

|-------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-------------|--|--|

| Synta             | ax:                                                   | BRA n                                                                                                                                                                                                         |                                          |             |  |  |

| Oper              | ands:                                                 | $-1024 \le n \le 10$                                                                                                                                                                                          | )23                                      |             |  |  |

| Oper              | ation:                                                | (PC) + 2 + 2n                                                                                                                                                                                                 | $\rightarrow$ PC                         |             |  |  |

| Statu             | s Affected:                                           | None                                                                                                                                                                                                          |                                          |             |  |  |

| Enco              | ding:                                                 | 1101 (                                                                                                                                                                                                        | )nnn nnni                                | n nnnn      |  |  |

| Description:      |                                                       | Add the 2's complement number '2n' to<br>the PC. Since the PC will have incre-<br>mented to fetch the next instruction, the<br>new address will be PC + 2 + 2n. This<br>instruction is a 2-cycle instruction. |                                          |             |  |  |

| Word              | ls:                                                   | 1                                                                                                                                                                                                             |                                          |             |  |  |

| Cycle             | es:                                                   | 2                                                                                                                                                                                                             |                                          |             |  |  |

| Q Cycle Activity: |                                                       |                                                                                                                                                                                                               |                                          |             |  |  |

|                   | Q1                                                    | Q2                                                                                                                                                                                                            | Q3                                       | Q4          |  |  |

|                   | Decode                                                | Read literal<br>'n'                                                                                                                                                                                           | Process<br>Data                          | Write to PC |  |  |

|                   | No                                                    | No                                                                                                                                                                                                            | No                                       | No          |  |  |

|                   | operation                                             | operation                                                                                                                                                                                                     | operation                                | operation   |  |  |

|                   | nple:<br>Before Instru<br>PC<br>After Instructi<br>PC | = ad                                                                                                                                                                                                          | BRA Jump<br>dress (HERE)<br>dress (Jump) |             |  |  |

| BSF                                                                 | Bit Set f                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                            |      |                     |  |  |

|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------|--|--|

| Syntax:                                                             | BSF f, b                                                                                                                       | {,a}                                                                                                                                                                                                                                                                                                                                                                                                       |      |                     |  |  |

| Operands:                                                           | $\begin{array}{l} 0\leq f\leq 255\\ 0\leq b\leq 7\\ a\in [0,1] \end{array}$                                                    |                                                                                                                                                                                                                                                                                                                                                                                                            |      |                     |  |  |

| Operation:                                                          | $1 \rightarrow f \le b >$                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                            |      |                     |  |  |

| Status Affected:                                                    | None                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                            |      |                     |  |  |

| Encoding:                                                           | 1000                                                                                                                           | bbba                                                                                                                                                                                                                                                                                                                                                                                                       | ffff | ffff                |  |  |

| Description:                                                        | If 'a' is '0',<br>If 'a' is '1',<br>GPR bank<br>If 'a' is '0' a<br>set is enab<br>in Indexed<br>mode whe<br><b>tion 42.2.3</b> | Bit 'b' in register 'f' is set.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See Sec-<br>tion 42.2.3 "Byte-Oriented and Bit-<br>Oriented Instructions in Indexed Lit- |      |                     |  |  |

| Words:                                                              | 1                                                                                                                              | 1                                                                                                                                                                                                                                                                                                                                                                                                          |      |                     |  |  |

| Cycles:                                                             | 1                                                                                                                              | 1                                                                                                                                                                                                                                                                                                                                                                                                          |      |                     |  |  |

| Q Cycle Activity:                                                   |                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                            |      |                     |  |  |

| Q1                                                                  | Q2                                                                                                                             | Q3                                                                                                                                                                                                                                                                                                                                                                                                         | 5    | Q4                  |  |  |

| Decode                                                              | Read<br>register 'f'                                                                                                           | Proce<br>Dat                                                                                                                                                                                                                                                                                                                                                                                               |      | Write<br>gister 'f' |  |  |

| Example: BSF FLAG_REG, 7, 1<br>Before Instruction<br>FLAG_REG = 0Ah |                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                            |      |                     |  |  |

| After Instruction                                                   |                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                            |      |                     |  |  |

fter Instruction FLAG\_REG = 8Ah

| CALLW Subroutine Call Using WREG                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                             |                |                     |                 |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------------|-----------------|--|--|--|

| Syntax:                                                                                                                                                                                                                                                         | CALLW                                                                                                                                                                                                                                                                                                                                                                                                                       |                |                     |                 |  |  |  |

| Operands:                                                                                                                                                                                                                                                       | None                                                                                                                                                                                                                                                                                                                                                                                                                        |                |                     |                 |  |  |  |

| Operation:                                                                                                                                                                                                                                                      | $(PC + 2) \rightarrow TOS,$<br>$(W) \rightarrow PCL,$<br>$(PCLATH) \rightarrow PCH,$<br>$(PCLATU) \rightarrow PCU$                                                                                                                                                                                                                                                                                                          |                |                     |                 |  |  |  |

| Status Affected:                                                                                                                                                                                                                                                | None                                                                                                                                                                                                                                                                                                                                                                                                                        |                |                     |                 |  |  |  |

| Encoding:                                                                                                                                                                                                                                                       | 0000                                                                                                                                                                                                                                                                                                                                                                                                                        | 0000           | 0001                | 0100            |  |  |  |

| Description                                                                                                                                                                                                                                                     | First, the return address (PC + 2) is<br>pushed onto the return stack. Next, the<br>contents of W are written to PCL; the<br>existing value is discarded. Then, the<br>contents of PCLATH and PCLATU are<br>latched into PCH and PCU,<br>respectively. The second cycle is<br>executed as a NOP instruction while the<br>new next instruction is fetched.<br>Unlike CALL, there is no option to<br>update W, Status or BSR. |                |                     |                 |  |  |  |

| Words:                                                                                                                                                                                                                                                          | 1                                                                                                                                                                                                                                                                                                                                                                                                                           |                |                     |                 |  |  |  |

| Cycles:                                                                                                                                                                                                                                                         | 2                                                                                                                                                                                                                                                                                                                                                                                                                           |                |                     |                 |  |  |  |

| Q Cycle Activity:                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                             |                |                     |                 |  |  |  |

|                                                                                                                                                                                                                                                                 | Q1                                                                                                                                                                                                                                                                                                                                                                                                                          | Q2             | Q3                  | Q4              |  |  |  |

|                                                                                                                                                                                                                                                                 | Decode                                                                                                                                                                                                                                                                                                                                                                                                                      | Read<br>WREG   | PUSH PC<br>to stack | No<br>operation |  |  |  |

|                                                                                                                                                                                                                                                                 | No                                                                                                                                                                                                                                                                                                                                                                                                                          | No             | No                  | No              |  |  |  |

|                                                                                                                                                                                                                                                                 | operation                                                                                                                                                                                                                                                                                                                                                                                                                   | opera-<br>tion | operation           | operation       |  |  |  |

| Example: HERE CALLW                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                             |                |                     |                 |  |  |  |

| Before Instruction<br>$\begin{array}{rcl} PC &= & address (HERE) \\ PCLATH &= & 10h \\ PCLATU &= & 00h \\ W &= & 06h \\ \end{array}$ After Instruction<br>$\begin{array}{rcl} PC &= & 001006h \\ TOS &= & address (HERE + 2) \\ PCLATH &= & 10h \\ \end{array}$ |                                                                                                                                                                                                                                                                                                                                                                                                                             |                |                     |                 |  |  |  |

| CLRF                                                                  | Clear f                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |                       |  |

|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------|--|

| Syntax:                                                               | CLRF f {,a}                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                |                       |  |

| Operands:                                                             | $\begin{array}{l} 0 \leq f \leq 255 \\ a  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                                                                                                                                                              |                |                       |  |

| Operation:                                                            | $\begin{array}{l} 000h \rightarrow f \\ 1 \rightarrow Z \end{array}$                                                                                                                                                                                                                                                                                                                                                                                           |                |                       |  |

| Status Affected:                                                      | Z                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |                       |  |

| Encoding:                                                             | 0110 101                                                                                                                                                                                                                                                                                                                                                                                                                                                       | a fff          | f ffff                |  |

|                                                                       | Clears the contents of the specified<br>register.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See Sec-<br>tion 42.2.3 "Byte-Oriented and Bit-<br>Oriented Instructions in Indexed Lit-<br>eral Offset Mode" for details. |                |                       |  |

| Words:                                                                | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |                       |  |

| Cycles:                                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |                       |  |

| Q Cycle Activity:                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |                       |  |

| Q1                                                                    | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Q3             | Q4                    |  |

| Decode                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                | rocess<br>Data | Write<br>register 'f' |  |

| Example:<br>Before Instruct<br>FLAG_RI<br>After Instructio<br>FLAG_RI | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |                       |  |

| NEGF              | Negate f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:           | NEGF f {,a}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Operands:         | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| Operation:        | $(\overline{f}) + 1 \rightarrow f$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| Status Affected:  | N, OV, C, DC, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| Encoding:         | 0110 110a ffff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|                   | Location 'f' is negated using two's<br>complement. The result is placed in the<br>data memory location 'f'.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See Sec-<br>tion 42.2.3 "Byte-Oriented and Bit-<br>Oriented Instructions in Indexed Lit-<br>eral Offset Mode" for details. |  |  |  |  |

| Words:            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| Cycles:           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| O Cycle Activity: |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| NOF               | •      | No Operation    |                 |            |                 |              |  |

|-------------------|--------|-----------------|-----------------|------------|-----------------|--------------|--|

| Synta             | ax:    | NOP             | NOP             |            |                 |              |  |

| Operands:         |        | None            |                 |            |                 |              |  |

| Operation:        |        | No operati      | on              |            |                 |              |  |

| Status Affected:  |        | None            |                 |            |                 |              |  |

| Encoding:         |        | 0000<br>1111    | 0000<br>xxxx    | 000<br>xxx | ÷               | 0000<br>xxxx |  |