Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 64MHz                                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                   |

| Number of I/O              | 25                                                                           |

| Program Memory Size        | 64KB (32K x 16)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 1K x 8                                                                       |

| RAM Size                   | 4K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 28-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf26k83t-i-so |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Features                                                                                    | PIC18(L)F25K83                                                          | PIC18(L)F26K83                                                                      |

|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| Program Memory (Bytes)                                                                      | 32768                                                                   | 65536                                                                               |

| Program Memory (Instructions)                                                               | 16384                                                                   | 32768                                                                               |

| Data Memory (Bytes)                                                                         | 2048                                                                    | 4096                                                                                |

| Data EEPROM Memory (Bytes)                                                                  | 1024                                                                    | 1024                                                                                |

| Packages                                                                                    | 28-pin SPDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN<br>28-pin UQFN | 28-pin SPDIP<br>28-pin SOIC<br>28-pin SSOP<br>28-pin QFN<br>28-pin UQFN             |

| I/O Ports                                                                                   | A,B,C,E <sup>(1)</sup>                                                  | A,B,C,E <sup>(1)</sup>                                                              |

| 12-Bit Analog-to-Digital Conversion Module (ADC <sup>2</sup> ) with Computation Accelerator | 5 internal<br>24 external                                               | 5 internal<br>24 external                                                           |

| Capture/Compare/PWM Modules (CCP)                                                           |                                                                         | 4                                                                                   |

| 10-Bit Pulse-Width Modulator (PWM)                                                          |                                                                         | 4                                                                                   |

| Timers (16-/8-bit)                                                                          | 4                                                                       | /3                                                                                  |

| Serial Communications                                                                       | 2 UARTs with DMX/E                                                      | DALI/LIN, 2 I <sup>2</sup> C, 1 SPI                                                 |

| Complementary Waveform Generator (CWG)                                                      |                                                                         | 3                                                                                   |

| Zero-Cross Detect (ZCD)                                                                     |                                                                         | 1                                                                                   |

| Data Signal Modulator (DSM)                                                                 |                                                                         | 1                                                                                   |

| Signal Measurement Timer (SMT)                                                              |                                                                         | 2                                                                                   |

| 5-bit Digital to Analog Converter (DAC)                                                     |                                                                         | 1                                                                                   |

| Numerically Controlled Oscillator (NCO)                                                     |                                                                         | 1                                                                                   |

| Comparator Module                                                                           |                                                                         | 2                                                                                   |

| Direct Memory Access (DMA)                                                                  |                                                                         | 2                                                                                   |

| Configurable Logic Cell (CLC)                                                               |                                                                         | 4                                                                                   |

| Control Area Network (CAN)                                                                  | Y                                                                       | es                                                                                  |

| Peripheral Module Disable (PMD)                                                             | Y                                                                       | es                                                                                  |

| 16-bit CRC with Scanner                                                                     | Y                                                                       | es                                                                                  |

| Programmable High/Low-Voltage Detect (HLVD)                                                 | Y                                                                       | es                                                                                  |

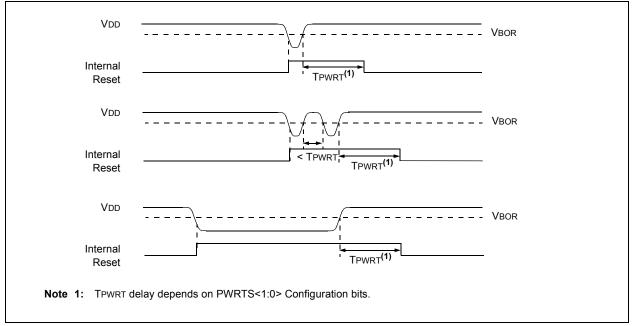

| Resets (and Delays)                                                                         | RESET Ir<br>Stack C<br>Stack U<br>(PWRT                                 | mmable BOR,<br>hstruction,<br>Dverflow,<br>nderflow<br>F, O <u>ST),</u><br>DT, MEMV |

| Instruction Set                                                                             |                                                                         | ructions;<br>struction Set enabled                                                  |

| Maximum Operating Frequency                                                                 | 64                                                                      | MHz                                                                                 |

**Note 1:** PORTE contains the single RE3 input-only pin.

| BOREN<1:0> | SBOREN | Device Mode | BOR Mode                       | Instruction Execution upon:             |                                         |  |  |

|------------|--------|-------------|--------------------------------|-----------------------------------------|-----------------------------------------|--|--|

| BURENS1:02 | SBUREN | Device Mode | BOR WOUL                       | Release of POR                          | Wake-up from Sleep                      |  |  |

| 11         | Х      | х           | Active                         | Wait for release of BOR<br>(BORRDY = 1) | Begins immediately                      |  |  |

| 10         | x      | Awake       | Active                         | Wait for release of BOR<br>(BORRDY = 1) | N/A                                     |  |  |

| 10         | A      | Sleep       | Hibernate                      | N/A                                     | Wait for release of BOR<br>(BORRDY = 1) |  |  |

| 01         | 1      | Х           | Active Wait for release of BOR |                                         | Begins immediately                      |  |  |

| 01         | 0      | Х           | Hibernate                      | (BORRDY = 1)                            | begins inifiediately                    |  |  |

| 00         | Х      | Х           | Disabled                       | Begins im                               | Begins immediately                      |  |  |

#### TABLE 6-1: BOR OPERATING MODES

## 11.1 Independent Clock Source

The WWDT can derive its time base from either the 31 kHz LFINTOSC or 31.25 kHz MFINTOSC internal oscillators, depending on the value of WDTE<1:0> Configuration bits.

If WDTE = 0b1x, then the clock source will be enabled depending on the WDTCCS<2:0> Configuration bits.

If WDTE = 0b01, the SEN bit should be set by software to enable WWDT, and the clock source is enabled by the CS bits in the WDTCON1 register.

Time intervals in this chapter are based on a minimum nominal interval of 1 ms. See **Section 45.0 "Electrical Specifications"** for LFINTOSC and MFINTOSC tolerances.

## 11.2 WWDT Operating Modes

The Windowed Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Words. See Table 11-1.

#### 11.2.1 WWDT IS ALWAYS ON

When the WDTE bits of Configuration Words are set to '11', the WWDT is always on.

WWDT protection is active during Sleep.

#### 11.2.2 WWDT IS OFF IN SLEEP

When the WDTE bits of Configuration Words are set to '10', the WWDT is on, except in Sleep.

WWDT protection is not active during Sleep.

#### 11.2.3 WWDT CONTROLLED BY SOFTWARE

When the WDTE bits of Configuration Words are set to '01', the WWDT is controlled by the SEN bit of the WDTCON0 register.

WWDT protection is unchanged by Sleep. See Table 11-1 for more details.

| WDTE<1:0> | SEN | Device<br>Mode | WWDT<br>Mode |

|-----------|-----|----------------|--------------|

| 11        | Х   | Х              | Active       |

| 10        | x   | Awake          | Active       |

| TO        | A   | Sleep          | Disabled     |

| 01        | 1   | Х              | Active       |

| 01        | 0   | Х              | Disabled     |

| 00        | Х   | Х              | Disabled     |

## TABLE 11-1: WWDT OPERATING MODES

## 11.3 Time-out Period

If the WDTCPS<4:0> Configuration bits default to 0b11111, then the PS bits of the WDTCON0 register set the time-out period from 1 ms to 256 seconds (nominal). If any value other than the default value is assigned to WDTCPS<4:0> Configuration bits, then the timer period will be based on the WDTCPS<4:0> bits in the CONFIG3L register. After a Reset, the default time-out period is 2s.

## 11.4 Watchdog Window

The Windowed Watchdog Timer has an optional Windowed mode that is controlled by the WDTCWS<2:0> Configuration bits and WINDOW<2:0> bits of the WDTCON1 register. In the Windowed mode, the CLRWDT instruction must occur within the allowed window of the WDT period. Any CLRWDT instruction that occurs outside of this window will trigger a window violation and will cause a WWDT Reset, similar to a WWDT time out. See Figure 11-2 for an example.

The window size is controlled by the WINDOW<2:0> Configuration bits, or the WINDOW<2:0> bits of WDTCON1, if WDTCWS<2:0> = 111.

The five Most Significant bits of the WDTTMR register are used to determine whether the window is open, as defined by the WINDOW<2:0> bits of the WDTCON1 register.

In the event of a window violation, a Reset will be generated and the WDTWV bit of the PCON0 register will be cleared. This bit is set by a POR or can be set in firmware.

## 11.5 Clearing the WWDT

The WWDT is cleared when any of the following conditions occur:

- Any Reset

- Valid CLRWDT instruction is executed

- Device enters Sleep

- Exit Sleep by Interrupt

- WWDT is disabled

- Oscillator Start-up Timer (OST) is running

- Any write to the WDTCON0 or WDTCON1

registers

#### 11.5.1 CLRWDT CONSIDERATIONS (WINDOWED MODE)

When in Windowed mode, the WWDT must be armed before a CLRWDT instruction will clear the timer. This is performed by reading the WDTCON0 register. Executing a CLRWDT instruction without performing such an arming action will trigger a window violation regardless of whether the window is open or not.

See Table 11-2 for more information.

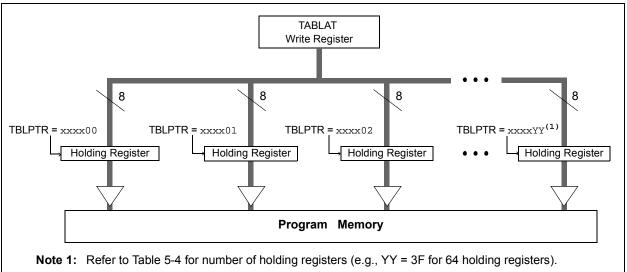

#### 13.1.6.1 Program Flash Memory Write Sequence

The sequence of events for programming an internal program memory location should be:

- 1. Read appropriate number of bytes into RAM. Refer to Table 13-2 for Write latch size.

- 2. Update data values in RAM as necessary.

- 3. Load Table Pointer register with address being erased.

- 4. Execute the block erase procedure.

- 5. Load Table Pointer register with address of first byte being written.

- Write the n-byte block into the holding registers with auto-increment. Refer to Table 13-2 for Write latch size.

- 7. Set REG<1:0> bits to point to program memory.

- 8. Clear FREE bit and set WREN bit in NVMCON1 register.

- 9. Disable interrupts.

- 10. Execute the unlock sequence (see Section 13.1.4 "NVM Unlock Sequence").

- 11. WR bit is set in NVMCON1 register.

- 12. The CPU will stall for the duration of the write (about 2 ms using internal timer).

- 13. Re-enable interrupts.

- 14. Verify the memory (table read).

This procedure will require about 6 ms to update each write block of memory. An example of the required code is given in Example 13-4.

**Note:** Before setting the WR bit, the Table Pointer address needs to be within the intended address range of the bytes in the holding registers.

## 13.3 Data EEPROM Memory

The data EEPROM is a nonvolatile memory array, separate from the data RAM and program memory, which is used for long-term storage of program data. It is not directly mapped in either the register file or program memory space but is indirectly addressed through the Special Function Registers (SFRs). The EEPROM is readable and writable during normal operation over the entire VDD range.

Four SFRs are used to read and write to the data EEPROM as well as the program memory. They are:

- NVMCON1

- NVMCON2

- NVMDAT

- NVMADRL

- NVMADRH

The data EEPROM allows byte read and write. When interfacing to the data memory block, NVMDAT holds the 8-bit data for read/write and the NVMADRH:NVMADRL register pair holds the address of the EEPROM location being accessed.

The EEPROM data memory is rated for high erase/write cycle endurance. A byte write automatically erases the location and writes the new data (erase-before-write). The write time is controlled by an internal programming timer; it will vary with voltage and temperature as well as from chip-to-chip. Refer to the Data EEPROM Memory parameters in Section 45.0 "Electrical Specifications" for limits.

#### 13.3.1 NVMADRL AND NVMADRH REGISTERS

The NVMADRH:NVMADRL registers are used to address the data EEPROM for read and write operations.

#### 13.3.2 NVMCON1 AND NVMCON2 REGISTERS

Access to the data EEPROM is controlled by two registers: NVMCON1 and NVMCON2. These are the same registers which control access to the program memory and are used in a similar manner for the data EEPROM.

The NVMCON1 register (Register 13-1) is the control register for data and program memory access. Control bits REG<1:0> determine if the access will be to program, Data EEPROM Memory or the User IDs, Configuration bits, Revision ID and Device ID.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear.

The WRERR bit is set by hardware when the WR bit is set and cleared when the internal programming timer expires and the write operation is complete.

The WR control bit initiates write operations. The bit can be set but not cleared by software. It is cleared only by hardware at the completion of the write operation.

The NVMIF Interrupt Flag bit of the PIR0 register is set when the write is complete. It must be cleared by software.

Control bits, RD and WR, start read and erase/write operations, respectively. These bits are set by firmware and cleared by hardware at the completion of the operation.

The RD bit cannot be set when accessing program memory (REG<1:0> = 0x10). Program memory is read using table read instructions. See **Section 13.1.1 "Table Reads and Table Writes"** regarding table reads.

| R/W-0/0      | R/W-0/0                                                                                                                             | R/W-0/0                          | R/W-0/0         | R/W-0/0           | R/W-0/0              | R/W-0/0            | R/W-0/0 |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------|-------------------|----------------------|--------------------|---------|

| DMC          | )DE<1:0>                                                                                                                            | DSTP                             | SMR             | <1:0>             | SMOD                 | E<1:0>             | SSTP    |

| bit 7        |                                                                                                                                     |                                  |                 |                   |                      |                    | bit C   |

| Legend:      |                                                                                                                                     |                                  |                 |                   |                      |                    |         |

| R = Reada    | ble bit                                                                                                                             | W = Writable bit                 |                 | U = Unimplemer    | nted bit, read as '0 | ,                  |         |

| u = Bit is u | nchanged                                                                                                                            | x = Bit is unknow                | vn              | -n/n = Value at F | OR and BOR/Val       | ue at all other Re | sets    |

|              |                                                                                                                                     | xDPTR<15:0> re                   |                 |                   |                      | n                  |         |

|              |                                                                                                                                     | xDPTR<15:0> is<br>xDPTR<15:0> re |                 |                   |                      | n                  |         |

| bit 5        | DSTP: Dest                                                                                                                          | ination Counter F                | Reload Stop bit |                   |                      |                    |         |

|              | - 0                                                                                                                                 | N bit is cleared w               |                 |                   |                      |                    |         |

| L:4 0        |                                                                                                                                     | N bit is not clear               |                 |                   | loads                |                    |         |

| bit 4-3      |                                                                                                                                     | Source Memory R                  | •               |                   |                      |                    |         |

|              | <ul> <li>1x = DMAxSSA&lt;21:0&gt; points to Data EEPROM</li> <li>01 = DMAxSSA&lt;21:0&gt; points to Program Flash Memory</li> </ul> |                                  |                 |                   |                      |                    |         |

|              |                                                                                                                                     | xSSA<21:0> poir                  |                 |                   |                      |                    |         |

| bit 2-1      | SMODE[1:0                                                                                                                           | ]: Source Addres                 | s Mode Selecti  | on bits           |                      |                    |         |

|              | 11 = Rese                                                                                                                           | erved, Do not use                |                 |                   |                      |                    |         |

|              | 10 = DMA                                                                                                                            | xSPTR < 21:0 > is                | decremented a   | fter each transfe | r completion         |                    |         |

- 10 = DMAxSPTR<21:0> is decremented after each transfer completion

- 01 = DMAxSPTR<21:0> is incremented after each transfer completion

- 00 = DMAxSPTR<21:0> remains unchanged after each transfer completion

- bit 0 **SSTP:** Source Counter Reload Stop bit

- 1 = SIRQEN bit is cleared when Source Counter reloads

- 0 = SIRQEN bit is not cleared when Source Counter reloads

# 24.2 Register Definitions: PWM Control

Long bit name prefixes for the PWM peripherals are shown below. Refer to **Section 1.3.2.2 "Long Bit Names"** for more information.

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| PWM3       | PWM3            |

| PWM4       | PWM4            |

## REGISTER 24-1: PWMxCON: PWM CONTROL REGISTER

| R/W-0/0 | U-0 | R-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | U-0   |

|---------|-----|-------|---------|-----|-----|-----|-------|

| EN      | —   | OUT   | POL     | —   |     |     | —     |

| bit 7   |     |       |         |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | EN: PWM Module Enable bit                     |

|---------|-----------------------------------------------|

|         | 1 = PWM module is enabled                     |

|         | 0 = PWM module is disabled                    |

| bit 6   | Unimplemented: Read as '0'                    |

| bit 5   | OUT: PWM Module Output Level When Bit is Read |

| bit 4   | POL: PWM Output Polarity Select bit           |

|         | 1 = PWM output is inverted                    |

|         | 0 = PWM output is normal                      |

| bit 3-0 | Unimplemented: Read as '0'                    |

| R/W-x/u          | R/W-x/u     | R/W-x/u                                      | R/W-x/u         | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u     |  |

|------------------|-------------|----------------------------------------------|-----------------|----------------|------------------|------------------|-------------|--|

| G1D4T            | G1D4N       | G1D3T                                        | G1D3N           | G1D2T          | G1D2N            | G1D1T            | G1D1N       |  |

| bit 7            |             |                                              |                 |                |                  |                  | bit         |  |

|                  |             |                                              |                 |                |                  |                  |             |  |

| Legend:          |             |                                              |                 |                |                  |                  |             |  |

| R = Readable     | e bit       | W = Writable                                 | bit             | U = Unimpler   | mented bit, read | l as '0'         |             |  |

| u = Bit is uncl  | nanged      | x = Bit is unki                              | nown            | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |  |

| '1' = Bit is set |             | '0' = Bit is cle                             | ared            |                |                  |                  |             |  |

|                  |             |                                              |                 |                |                  |                  |             |  |

| bit 7            |             | 0 Data 4 True                                | •               |                |                  |                  |             |  |

|                  |             | (true) is gated                              |                 |                |                  |                  |             |  |

| bit 6            |             | (true) is not ga                             |                 |                |                  |                  |             |  |

| DILO             |             | e 0 Data 4 Nega<br>(inverted) is ga          | · ·             |                |                  |                  |             |  |

|                  |             | (inverted) is ga                             |                 |                |                  |                  |             |  |

| bit 5            |             | 0 Data 3 True                                | •               |                |                  |                  |             |  |

|                  |             | (true) is gated                              | •               |                |                  |                  |             |  |

|                  | 0 = CLCIN2  | (true) is not ga                             | ted into CLCx   | Gate 0         |                  |                  |             |  |

| bit 4            | G1D3N: Gate | e 0 Data 3 Neg                               | ated (inverted) | ) bit          |                  |                  |             |  |

|                  |             | (inverted) is ga                             |                 |                |                  |                  |             |  |

|                  |             | (inverted) is no                             | •               |                |                  |                  |             |  |

| bit 3            |             | 0 Data 2 True                                |                 | ,              |                  |                  |             |  |

|                  |             | (true) is gated (<br>(true) is not ga        |                 |                |                  |                  |             |  |

| bit 2            |             | e 0 Data 2 Neg                               |                 |                |                  |                  |             |  |

|                  |             | (inverted) is ga                             |                 |                |                  |                  |             |  |

|                  |             | (inverted) is no                             |                 |                |                  |                  |             |  |

| bit 1            | G1D1T: Gate | G1D1T: Gate 0 Data 1 True (non-inverted) bit |                 |                |                  |                  |             |  |

|                  | 1 = CLCIN0  | (true) is gated                              | into CLCx Gat   | te 0           |                  |                  |             |  |

|                  |             | (true) is not ga                             |                 |                |                  |                  |             |  |

| bit 0            |             | e 0 Data 1 Neg                               | · ·             |                |                  |                  |             |  |

|                  |             | (inverted) is ga                             |                 |                |                  |                  |             |  |

|                  | 0 = CLCINO  | (inverted) is no                             | t gated into C  | LCx Gate 0     |                  |                  |             |  |

## REGISTER 27-7: CLCxGLS0: GATE 0 LOGIC SELECT REGISTER

| U-0            | U-0                                                                                       | U-0               | U-0  | U-0          | U-0              | U-0    | R/W-0/0 |

|----------------|-------------------------------------------------------------------------------------------|-------------------|------|--------------|------------------|--------|---------|

| _              | —                                                                                         | _                 | _    | _            | —                | —      | P3<8>   |

| bit 7          | t 7                                                                                       |                   |      |              |                  |        | bit 0   |

|                |                                                                                           |                   |      |              |                  |        |         |

| Legend:        |                                                                                           |                   |      |              |                  |        |         |

| R = Readal     | ble bit                                                                                   | W = Writable      | bit  | U = Unimpler | mented bit, read | as '0' |         |

| u = Bit is ur  | u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Re |                   |      |              | ther Resets      |        |         |

| '1' = Bit is s | set                                                                                       | '0' = Bit is clea | ared |              |                  |        |         |

| bit 7-6        | Unimplemen                                                                                | ted: Read as '    | n'   |              |                  |        |         |

|                | -                                                                                         |                   |      | 0            |                  |        |         |

| bit 0          |                                                                                           | Significant Bit   |      | 5            |                  |        |         |

|                | DMX mode:                                                                                 |                   |      |              |                  |        |         |

|                | Most Significant bit of last address of receive block                                     |                   |      |              |                  |        |         |

|                | Other modes                                                                               | :                 |      |              |                  |        |         |

|                | Not used                                                                                  |                   |      |              |                  |        |         |

|                |                                                                                           |                   |      |              |                  |        |         |

#### REGISTER 31-16: UxP3H: UART PARAMETER 3 HIGH REGISTER

#### REGISTER 31-17: UxP3L: UART PARAMETER 3 LOW REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| P3<7:0> |         |         |         |         |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

P3<7:0>: Least Significant Bits of Parameter 3

DMX mode:

Least Significant Byte of last address of receive block

LIN Slave mode:

Number of data bytes to receive

Asynchronous Address mode:

Receiver address mask. Received address is XOR'd with UxP2L then AND'd with UxP3L

Match occurs when result is zero

Other modes:

Not used

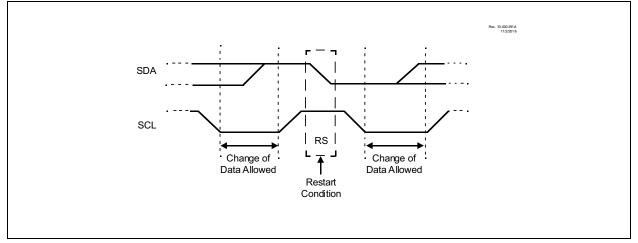

## 33.3.7 RESTART CONDITION

A Restart is valid any time that a Stop would be valid. A master can issue a Restart if it wishes to hold the bus after terminating the current transfer. A Restart has the same effect on the slave that a Start would, resetting all slave logic and preparing it to clock in an address. The master may want to address the same or another slave. Figure 33-4 shows the waveform for a Restart condition.

FIGURE 33-4: RESTART CONDITION

In 10-bit Addressing Slave mode a Restart is required for the master to clock data out of the addressed slave. Once a slave has been fully addressed, matching both high and low address bytes (SMA = 1), the master can issue a Restart and the high address byte with the R/W bit set. The slave logic will then hold the clock and prepare to clock out data.

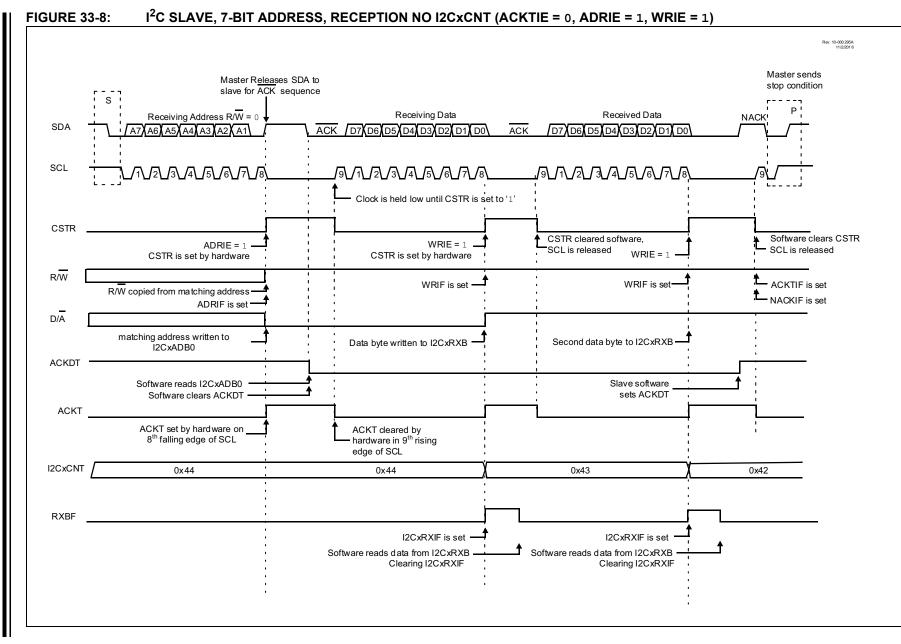

## 33.3.8 ACKNOWLEDGE SEQUENCE

The ninth SCL pulse for any transferred byte in  $I^2C$  is dedicated as an Acknowledge. It allows receiving devices to respond back to the transmitter by pulling the SDA line low. The transmitter must release control of the line during this time to shift in the response. The Acknowledge (ACK) is an active-low signal, pulling the SDA line low indicates to the transmitter that the device has received the transmitted data and is ready to receive more.

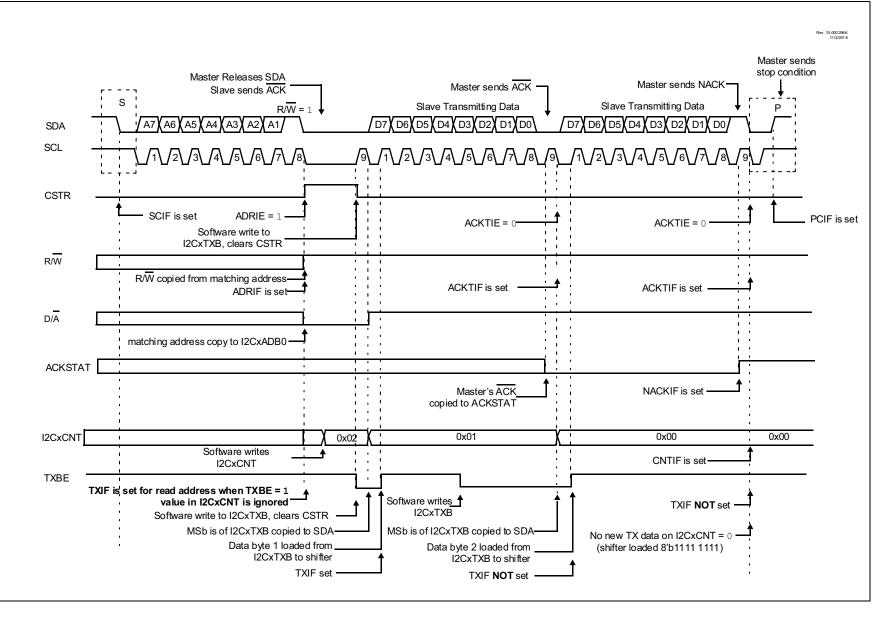

The result of an ACK is placed in the ACKSTAT bit of the I2CxCON1 register. The ACKSTAT bit is cleared when the receiving device sends an Acknowledge and is set when the receiving device does not Acknowledge. A slave sends an Acknowledge when it has recognized its address. When in a mode that is receiving data, the ACK data being sent to the transmitter depends on the value of I2CxCNT register. ACKDT is the value sent when I2CxCNT! = 0. When I2CxCNT = 0, the ACKCNT value is used instead.

In Slave mode, if the ADRIE or WRIE bits are set, clock stretching is initiated when there is an address match or when there is an attempt to write to slave. This allows the user to set the ACK value sent back to the transmitter. The ACKDT bit of the I2CxCON1 register is set/cleared to determine the response. Slave hardware will generate an ACK response if the ADRIE or WRIE bits are clear. Certain conditions will cause a not-ACK (NACK) to be sent automatically. If any of the RXRE, TXRE, RXO, or TXU bits is set, the hardware response is forced to NACK. All subsequent responses from the device for address matches or data will be a NACK response.

## 33.3.9 BUS TIME-OUT

The I2CxBTO register can be used to select the timeout source for the module. The I<sup>2</sup>C module is reset when the selected bus time out signal goes high. This feature is useful for SMBus and PMBus<sup>TM</sup> compatibility.

For example, Timer2 can be selected as the bus timeout source and configured to count when the SCL pin is low. If the timer runs over before the SCL pin transitioned high, the timer-out pulse will reset the module.

Note: The bus time-out source should produce a rising edge.

If the module is configured as a slave and a BTO event occurs when the slave is active (i.e., the SMA bit is set), the module is immediately reset. The SMA and CSTR bits are also cleared, and the BTOIF bit is set.

© 2017 Microchip Technology Inc

PIC18(L)F25/26K83

# FIGURE 33-9: I<sup>2</sup>C SLAVE, 7-BIT ADDRESS, TRANSMISSION

IC18(L)F25/26K83

# PIC18(L)F25/26K83

| R/W-0          | R/W-0                                                                            | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W-0                                                                             | R/W-0                                                                         | R/W-0                         | R/W-0                           | R/W-0                            |  |  |

|----------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------|---------------------------------|----------------------------------|--|--|

| ACNT           | GCEN                                                                             | FME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ADB                                                                               | SDAHT<                                                                        | :1:0>                         | BFRE                            | T<1:0>                           |  |  |

| bit 7          |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                   | -                                                                             |                               |                                 | bit (                            |  |  |

|                |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                   |                                                                               |                               |                                 |                                  |  |  |

| Legend:        |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                   |                                                                               |                               |                                 |                                  |  |  |

| R = Readal     | ble bit                                                                          | W = Writable b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                   | U = Unimpleme                                                                 | nted bit, read                | <b>d as</b> '0'                 |                                  |  |  |

| u = Bit is ur  | nchanged                                                                         | x = Bit is unkno                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | own                                                                               | -n/n = Value at F                                                             | POR and BC                    | R/Value at all c                | other Resets                     |  |  |

| '1' = Bit is s | set                                                                              | '0' = Bit is clea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | red                                                                               | HS = Hardware                                                                 | set HC =                      | Hardware clea                   | r                                |  |  |

| bit 7          | 1 = The firs<br>ister.<br>ACKD<br>receiv<br>updat                                | The I2CCNT regineration The I2CCNT regineration of the I2CCNT regineration | smitted byte al<br>ster is loaded a<br>ermine the ACI<br>is prevents a<br>gister. | ble bit<br>fter the address, is<br>at the same time a<br>I2CCNT <nack></nack> | s the value is<br>the address | s moved to/fron bytes and first | n the shifter.<br>data byte of a |  |  |

| bit 6          | 1 = Genera                                                                       | <b>GCEN:</b> General Call Address Enable bit (MODE<2:0> = 00x & 11x)<br>1 = General call address, 0x00, causes address match event<br>0 = General call address disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                   |                                                                               |                               |                                 |                                  |  |  |

| bit 5          | 1 = SCL is                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                   | driving SCL low. (<br>ing SCL low. (Fsci                                      |                               | (/4)                            |                                  |  |  |

| bit 4          | 1 = Receiv<br>Trans<br>0 = Receiv                                                | <ul> <li>0 = SCL is sampled high twice before driving SCL low. (FSCL = FCLK/5)</li> <li>ADB: Address Data Buffer Disable bit</li> <li>1 = Received address data is loaded into both the I2CADB and I2CRXB<br/>Transmitted address data is loaded from the I2CTXB</li> <li>0 = Received address data is loaded only into the I2CADB<br/>Transmitted address data is loaded from the I2CADB</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                   |                                                                               |                               |                                 |                                  |  |  |

| bit 3-2        | 11 = Reser<br>10 = Minim<br>01 = Minim                                           | <b>SDAHT&lt;1:0&gt;:</b> SDA Hold Time Selection bits<br>11 = Reserved<br>10 = Minimum of 30 ns hold time on SDA after the falling edge of SCL<br>01 = Minimum of 100 ns hold time on SDA after the falling edge of SCL<br>00 = Minimum of 300 ns hold time on SDA after the falling edge of SCL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                   |                                                                               |                               |                                 |                                  |  |  |

| bit 1-0        | 11 = 64 I <sup>2</sup> C<br>10 = 32 I <sup>2</sup> C<br>01 = 16 I <sup>2</sup> C | D>: Bus Free Tim<br>Clock pulses<br>Clock pulses<br>Clock pulses<br>Clock pulses<br>Clock pulses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | e Selection bit                                                                   | S                                                                             |                               |                                 |                                  |  |  |

messages: SDFLC

#### 34.3.3 MODE 2 – ENHANCED FIFO MODE

In Mode 2, two or more receive buffers are used to form the receive FIFO (first in, first out) buffer. There is no one-to-one relationship between the receive buffer and acceptance filter registers. Any filter that is enabled and linked to any FIFO receive buffer can generate acceptance and cause FIFO to be updated.

FIFO length is user-programmable, from 2-8 buffers deep. FIFO length is determined by the very first programmable buffer that is configured as a transmit buffer. For example, if Buffer 2 (B2) is programmed as a transmit buffer, FIFO consists of RXB0, RXB1, B0 and B1, creating a FIFO length of four. If all programmable buffers are configured as receive buffers, FIFO will have the maximum length of eight.

The following is the list of resources available in Mode 2:

- Three transmit buffers: TXB0, TXB1 and TXB2

- Two receive buffers: RXB0 and RXB1

- Six buffers programmable as TX or RX; receive buffers form FIFO: B0-B5

- Automatic RTR handling on B0-B5

- Sixteen acceptance filters: RXF0-RXF15

- Two dedicated acceptance mask registers; RXF15 programmable as third mask: RXM0-RXM1, RXF15

- Programmable data filter on standard identifier messages: SDFLC, useful for DeviceNet protocol

## 34.4 CAN Message Buffers

#### 34.4.1 DEDICATED TRANSMIT BUFFERS

The CAN module implements three dedicated transmit buffers – TXB0, TXB1 and TXB2. Each of these buffers occupies 14 bytes of SRAM and are mapped into the SFR memory map. These are the only transmit buffers available in Mode 0. Mode 1 and 2 may access these and other additional buffers.

Each transmit buffer contains one Control register (TXBnCON), four Identifier registers (TXBnSIDL, TXBnSIDH, TXBnEIDL, TXBnEIDH), one Data Length Count register (TXBnDLC) and eight Data Byte registers (TXBnDm).

## 34.4.2 DEDICATED RECEIVE BUFFERS

The CAN module implements two dedicated receive buffers: RXB0 and RXB1. Each of these buffers occupies 14 bytes of SRAM and are mapped into SFR memory map. These are the only receive buffers available in Mode 0. Mode 1 and 2 may access these and other additional buffers. Each receive buffer contains one Control register (RXBnCON), four Identifier registers (RXBnSIDL, RXBnSIDH, RXBnEIDL, RXBnEIDH), one Data Length Count register (RXBnDLC) and eight Data Byte registers (RXBnDm).

There is also a separate Message Assembly Buffer (MAB) which acts as an additional receive buffer. MAB is always committed to receiving the next message from the bus and is not directly accessible to user firmware. The MAB assembles all incoming messages one by one. A message is transferred to appropriate receive buffers only if the corresponding acceptance filter criteria is met.

#### 34.4.3 PROGRAMMABLE TRANSMIT/ RECEIVE BUFFERS

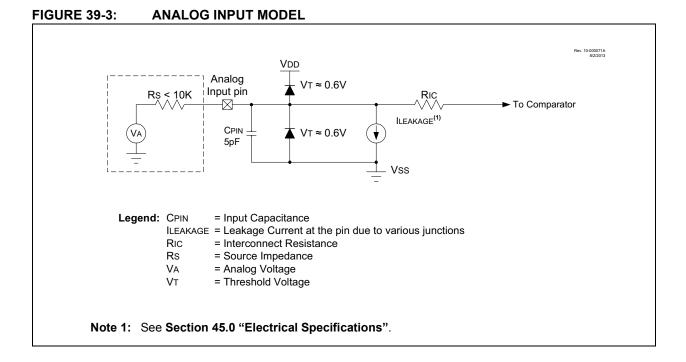

The CAN module implements six non-dedicated buffers: B0-B5. These buffers are individually programmable as either transmit or receive buffers. These buffers are available only in Mode 1 and 2. As with dedicated transmit and receive buffers, each of these programmable buffers occupies 14 bytes of SRAM and are mapped into SFR memory map.