Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 13                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128 × 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                |

| Data Converters            | A/D 4x8b                                                                 |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-VQFN Exposed Pad                                                      |

| Supplier Device Package    | 28-QFN (6x6)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f716-e-ml |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, KEELOQ logo, microID, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, PowerSmart, rfPIC, and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AmpLab, FilterLab, Linear Active Thermistor, Migratable Memory, MXDEV, MXLAB, PS logo, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, ECAN, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, PICkit, PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, rfPICDEM, Select Mode, Smart Serial, SmartTel, Total Endurance, UNI/O, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2007, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona, Gresham, Oregon and Mountain View, California. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

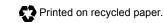

## **18-Pin Diagram**

## TABLE 1: 18-PIN PDIP, SOIC SUMMARY

| I/O | Pin | Analog   | ECCP     | Timer | Interrupts | Pull-ups | Basic       |

|-----|-----|----------|----------|-------|------------|----------|-------------|

| RA0 | 17  | AN0      |          |       | _          | -        | _           |

| RA1 | 18  | AN1      | _        | _     | —          |          | —           |

| RA2 | 1   | AN2      |          |       | —          | _        | —           |

| RA3 | 2   | AN3/VREF | _        | _     | _          | -        | —           |

| RA4 | 3   | —        | _        | TOCKI | _          | _        | —           |

| RB0 | 6   | —        | ECCPAS2  | _     | INT        | Y        | —           |

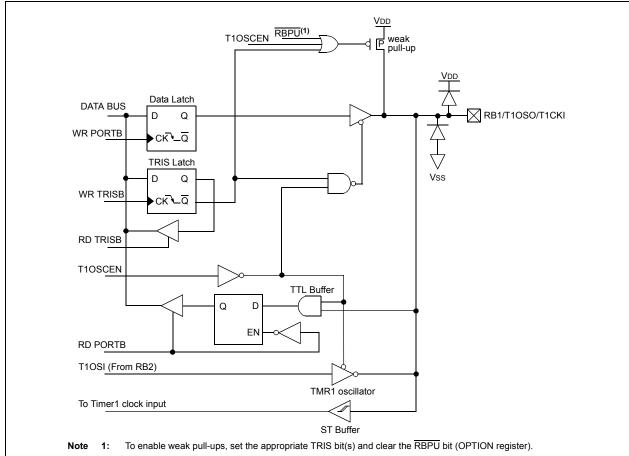

| RB1 | 7   | —        | _        | T1CKI | _          | Y        | —           |

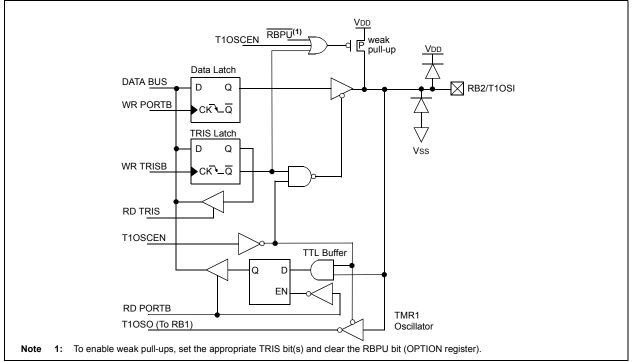

| RB2 | 8   | —        | _        | T10SI | —          | Y        | —           |

| RB3 | 9   | —        | CCP1/P1A |       | —          | Y        | —           |

| RB4 | 10  | —        | ECCPAS0  | —     | IOC        | Y        | —           |

| RB5 | 11  | —        | P1B      | _     | IOC        | Y        | —           |

| RB6 | 12  | —        | P1C      | -     | IOC        | Y        | ICSPCLK     |

| RB7 | 13  |          | P1D      |       | IOC        | Y        | ICSPDAT     |

| —   | 14  |          |          |       | —          |          | Vdd         |

| _   | 5   |          |          |       | —          |          | Vss         |

| _   | 4   | —        | _        | _     | _          | _        | MCLR/VPP    |

|     | 16  | _        | _        |       | _          | _        | OSC1/CLKIN  |

| _   | 15  |          | _        | _     | _          | _        | OSC2/CLKOUT |

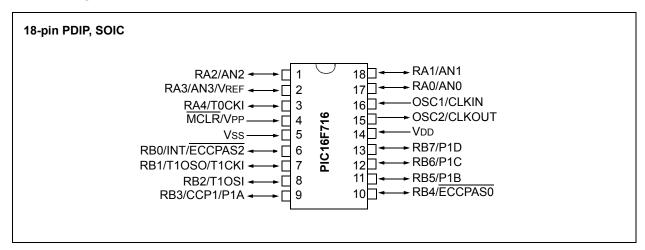

## 20-Pin Diagram

#### TABLE 2: 20-PIN SSOP SUMMARY

| I/O | Pin | Analog   | ECCP     | Timer | Interrupts | Pull-ups | Basic       |

|-----|-----|----------|----------|-------|------------|----------|-------------|

| RA0 | 19  | AN0      | —        | _     | —          | _        | —           |

| RA1 | 20  | AN1      | —        | _     | —          | _        | —           |

| RA2 | 1   | AN2      | —        | —     | —          |          | —           |

| RA3 | 2   | AN3/VREF | _        | _     | _          | _        | —           |

| RA4 | 3   | —        | —        | TOCKI | —          |          | —           |

| RB0 | 7   | —        | ECCPAS2  | _     | INT        | Y        | —           |

| RB1 | 8   | —        | —        | T1CKI | —          | Y        | —           |

| RB2 | 9   | —        | —        | T10SI | —          | Y        | —           |

| RB3 | 10  | —        | CCP1/P1A | _     | —          | Y        | —           |

| RB4 | 11  | —        | ECCPAS0  | _     | IOC        | Y        | —           |

| RB5 | 12  | —        | P1B      | —     | IOC        | Y        | —           |

| RB6 | 13  | —        | P1C      | _     | IOC        | Y        | ICSPCLK     |

| RB7 | 14  | —        | P1D      | —     | IOC        | Y        | ICSPDAT     |

| —   | 15  | —        | —        | _     | —          |          | Vdd         |

| —   | 16  | —        | _        |       | —          |          | Vdd         |

| —   | 5   | —        | —        |       | _          | -        | Vss         |

| —   | 6   | —        |          | —     | —          | —        | Vss         |

| —   | 4   |          |          |       | _          |          | MCLR/VPP    |

| —   | 18  | _        |          | —     | —          | _        | OSC1/CLKIN  |

|     | 17  |          | —        |       | _          |          | OSC2/CLKOUT |

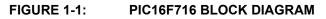

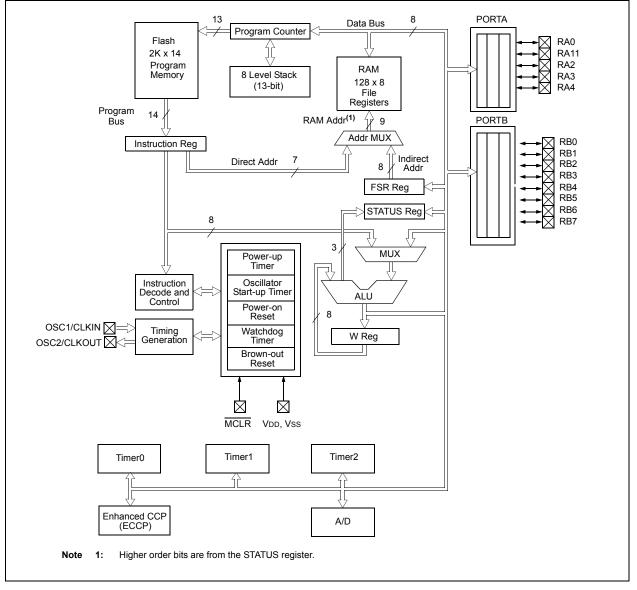

## 1.0 DEVICE OVERVIEW

This document contains device specific information for the PIC16F716. Figure 1-1 is the block diagram for the PIC16F716 device. The pinouts are listed in Table 1-1.

#### 5.8 ECCP Capture/Compare Time Base

The ECCP module uses the TMR1H:TMR1L register pair as the time base when operating in Capture or Compare mode.

In Capture mode, the value in the TMR1H:TMR1L register pair is copied into the CCPR1H:CCPR1L register pair on a configured event.

In Compare mode, an event is triggered when the value CCPR1H:CCPR1L register pair matches the value in the TMR1H:TMR1L register pair. This event can be a Special Event Trigger.

For more information, see Section 8.0 "Enhanced Capture/Compare/PWM Module".

## 5.9 ECCP Special Event Trigger

If a ECCP is configured to trigger a special event, the trigger will clear the TMR1H:TMR1L register pair. This special event does not cause a Timer1 interrupt. The ECCP module may still be configured to generate a ECCP interrupt.

In this mode of operation, the CCPR1H:CCPR1L register pair effectively becomes the period register for Timer1.

Timer1 should be synchronized to the FOSC to utilize the Special Event Trigger. Asynchronous operation of Timer1 can cause a Special Event Trigger to be missed.

In the event that a write to TMR1H or TMR1L coincides with a Special Event Trigger from the ECCP, the write will take precedence.

For more information, see Section 8.0 "Enhanced Capture/Compare/PWM Module".

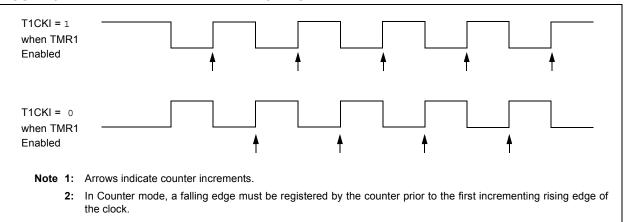

#### FIGURE 5-2: TIMER1 INCREMENTING EDGE

| Name   | Bit 7      | Bit 6    | Bit 5 | Bit 4  | Bit 3  | Bit 2   | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|------------|----------|-------|--------|--------|---------|--------|--------|----------------------|---------------------------------|

| ADCON0 | ADCS1      | ADCS0    | CHS2  | CHS1   | CHS0   | GO/DONE | _      | ADON   | 0000 0000            | 0000 0000                       |

| ADCON1 | _          | _        | _     | _      | _      | PCFG2   | PCFG1  | PCFG0  | 000                  | 000                             |

| ADRES  | A/D Result | Register |       |        |        |         |        |        | xxxx xxxx            | uuuu uuuu                       |

| INTCON | GIE        | PEIE     | T0IE  | INTE   | RBIE   | T0IF    | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| PIE1   | _          | ADIE     | _     | _      | _      | CCP1IE  | TMR2IE | TMR1IE | -0000                | -0000                           |

| PIR1   | _          | ADIF     | _     | _      | _      | CCP1IF  | TMR2IF | TMR1IF | -0000                | -0000                           |

| PORTA  | _          | _        | _     | RA4    | RA3    | RA2     | RA1    | RA0    | xx xxxx              | uu uuuu                         |

| TRISA  | _          | _        | _     | TRISA4 | TRISA3 | TRISA2  | TRISA1 | TRISA0 | 11 1111              | 11 1111                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for ADC module.

#### REGISTER 8-2: ECCPAS: ENHANCED CAPTURE/COMPARE/PWM AUTO-SHUTDOWN CONTROL REGISTER

| R/W-0           | R/W-0      | U-0                              | R/W-0         | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

|-----------------|------------|----------------------------------|---------------|------------------|------------------|-----------------|--------|

| ECCPASE         | ECCPAS2    |                                  | ECCPAS0       | PSSAC1           | PSSAC0           | PSSBD1          | PSSBD0 |

| bit 7           |            |                                  |               |                  |                  |                 | bit (  |

| Legend:         |            |                                  |               |                  |                  |                 |        |

| R = Readable    | bit        | W = Writable                     | bit           | U = Unimpler     | nented bit, read | 1 as '0'        |        |

| -n = Value at F | POR        | '1' = Bit is set                 |               | '0' = Bit is cle | ared             | x = Bit is unki | nown   |

|                 |            |                                  |               |                  |                  |                 |        |

| bit 7           | ECCPASE: E | CCP Auto-Shu                     | tdown Event S | Status bit       |                  |                 |        |

|                 |            |                                  |               | outputs are ir   | n shutdown stat  | е               |        |

|                 |            | tputs are opera                  | 0             |                  |                  |                 |        |

| bit 6           |            | CCP Auto-Shu                     |               |                  |                  |                 |        |

|                 |            | ) pin low level                  |               |                  |                  |                 |        |

|                 |            | NT) pin has no                   |               | Р                |                  |                 |        |

| bit 5           | •          | ted: Read as '                   |               |                  |                  |                 |        |

| bit 4           | ECCPAS0: E | CCP Auto-Shu                     | tdown bit '0' |                  |                  |                 |        |

|                 |            | low level ('0') c                |               | vn               |                  |                 |        |

|                 |            | has no effect o                  |               |                  |                  |                 |        |

| bit 3-2         |            | is P1A and P1                    |               | ate Control bits | S                |                 |        |

|                 |            | ns P1A and P1                    |               |                  |                  |                 |        |

|                 |            | ns P1A and P1<br>A and P1C tri-s |               |                  |                  |                 |        |

| bit 1-0         |            | s P1B and P1                     |               | ato Control hite | -                |                 |        |

|                 |            | is FIB and FI                    |               |                  | 5                |                 |        |

|                 |            | is PTB and PT                    |               |                  |                  |                 |        |

|                 | 51 D110 p1 |                                  |               |                  |                  |                 |        |

- 1x = Pins P1B and P1D tri-state

- Note 1: The auto-shutdown condition is a levelbased signal, not an edge-based signal. As long as the level is present, the autoshutdown will persist.

- 2: Writing to the ECCPASE bit is disabled while an auto-shutdown condition persists.

- **3:** Once the auto-shutdown condition has been removed and the PWM restarted (either through firmware or auto-restart), the PWM signal will always restart at the beginning of the next PWM period.

## 9.2 Oscillator Configurations

#### 9.2.1 OSCILLATOR TYPES

The PIC16F716 can be operated in four different oscillator modes. The user can program two Configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low-power Crystal

- · XT Crystal/Resonator

- HS High-speed Crystal/Resonator

- RC Resistor/Capacitor

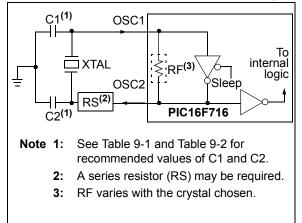

## 9.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

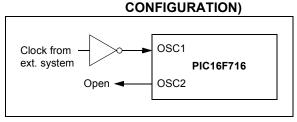

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 9-1). The PIC16F716 oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1/CLKIN pin (Figure 9-2).

| FIGURE 9-1: | CRYSTAL/CERAMIC            |

|-------------|----------------------------|

|             | <b>RESONATOR OPERATION</b> |

|             | (HS, XT OR LP              |

|             | OSC CONFIGURATION)         |

FIGURE 9-2: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC

## TABLE 9-1: CERAMIC RESONATORS

| Ranges Tested:                                                                  |                                |                                  |                                  |  |  |  |  |

|---------------------------------------------------------------------------------|--------------------------------|----------------------------------|----------------------------------|--|--|--|--|

| Mode                                                                            | Freq OSC1 (C1) OSC2 (C2)       |                                  |                                  |  |  |  |  |

| ХТ                                                                              | 455 kHz<br>2.0 MHz             | 68-100 pF<br>15-68 pF            | 68-100 pF<br>15-68 pF            |  |  |  |  |

| HS                                                                              | 4.0 MHz<br>8.0 MHz<br>16.0 MHz | 10-68 pF<br>15-68 pF<br>10-22 pF | 10-68 pF<br>15-68 pF<br>10-22 pF |  |  |  |  |

| Note 1: These values are for design guidance only. See notes at bottom of page. |                                |                                  |                                  |  |  |  |  |

## TABLE 9-2:CAPACITOR SELECTION FOR<br/>CRYSTAL OSCILLATOR

| Osc Type                                                                           | Crystal<br>Freq | Cap. Range<br>C1 | Cap. Range<br>C2 |  |  |

|------------------------------------------------------------------------------------|-----------------|------------------|------------------|--|--|

| LP                                                                                 | 32 kHz          | 15-33 pF         | 15-33 pF         |  |  |

|                                                                                    | 200 kHz         | 5-10 pF          | 5-10 pF          |  |  |

| XT                                                                                 | 200 kHz         | 47-68 pF         | 47-68 pF         |  |  |

|                                                                                    | 1 MHz           | 15-33 pF         | 15-33 pF         |  |  |

|                                                                                    | 4 MHz           | 15-33 pF         | 15-33 pF         |  |  |

| HS                                                                                 | 4 MHz           | 15-33 pF         | 15-33 pF         |  |  |

|                                                                                    | 8 MHz           | 15-33 pF         | 15-33 pF         |  |  |

|                                                                                    | 20 MHz          | 15-33 pF         | 15-33 pF         |  |  |

| Note 1: These values are for design guidance only.<br>See notes at bottom of page. |                 |                  |                  |  |  |

- **Note 1:** Higher capacitance increases the stability of the oscillator, but also increases the start-up time.

- 2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- **3:** RS may be required to avoid overdriving crystals with low drive level specification.

- 4: When using an external clock for the OSC1 input, loading of the OSC2 pin must be kept to a minimum by leaving the OSC2 pin unconnected.

### TABLE 9-5: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset (BOREN = 0)         | 000h                  | 0001 1xxx          | 0x               |

| Power-on Reset (BOREN = 1)         | 000h                  | 0001 1xxx          | 01               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during Sleep            | 000h                  | 0001 0uuu          | uu               |

| WDT Reset                          | 000h                  | 0000 luuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 0001 luuu          | u0               |

| Interrupt wake-up from Sleep       | PC + 1 <sup>(1)</sup> | uuul 0uuu          | uu               |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit read as '0'.

**Note 1:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

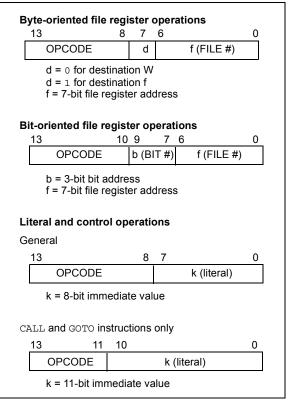

## 10.0 INSTRUCTION SET SUMMARY

The PIC16F716 instruction set is highly orthogonal and is comprised of three basic categories:

- Byte-oriented operations

- · Bit-oriented operations

- · Literal and control operations

Each PIC16 instruction is a 14-bit word divided into an **opcode**, which specifies the instruction type and one or more **operands**, which further specify the operation of the instruction. The formats for each of the categories is presented in Figure 10-1, while the various opcode fields are summarized in Table 10-1.

Table 10-2 lists the instructions recognized by the MPASM<sup>TM</sup> assembler.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator, which selects the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, 'k' represents an 8-bit or 11-bit constant, or literal value.

One instruction cycle consists of four oscillator periods; for an oscillator frequency of 4 MHz, this gives a nominal instruction execution time of 1  $\mu$ s. All instructions are executed within a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of an instruction. When this occurs, the execution takes two instruction cycles, with the second cycle executed as a NOP.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

## 10.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

For example, a CLRF PORTA instruction will read PORTA, clear all the data bits, then write the result back to PORTA. This example would have the unintended consequence of clearing the condition that set the RAIF flag.

#### TABLE 10-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                              |

| W     | Working register (accumulator)                                                                                                                                                    |

| b     | Bit address within an 8-bit file register                                                                                                                                         |

| k     | Literal field, constant data or label                                                                                                                                             |

| x     | Don't care location (= $0$ or 1).<br>The assembler will generate code with x = $0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1.                                                                     |

| PC    | Program Counter                                                                                                                                                                   |

| TO    | Time-out bit                                                                                                                                                                      |

| С     | Carry bit                                                                                                                                                                         |

| DC    | Digit carry bit                                                                                                                                                                   |

| Z     | Zero bit                                                                                                                                                                          |

| PD    | Power-down bit                                                                                                                                                                    |

#### FIGURE 10-1: GENERAL FORMAT FOR INSTRUCTIONS

NOTES:

## 12.5 AC (Timing) Characteristics

12.5.1 TIMING PARAMETER SYMBOLOGY

The timing parameter symbols have been created using one of the following formats:

| 1. | TppS2ppS |

|----|----------|

|----|----------|

| ×. |

|----|

| 2  |

|    |

|    | ippo      |                                    |   |      |                |

|----|-----------|------------------------------------|---|------|----------------|

| т  |           |                                    |   |      |                |

|    | F         | Frequency                          | Т | Time |                |

|    | Lowercase | e letters (pp) and their meanings: |   |      |                |

| рр |           |                                    |   |      |                |

|    | CC        | CCP1                               |   | OSC  | OSC1           |

|    | ck        | CLKOUT                             |   | rd   | RD             |

|    | cs        | CS                                 |   | rw   | RD or WR       |

|    | di        | SDI                                |   | SC   | SCK            |

|    | do        | SDO                                |   | SS   | SS             |

|    | dt        | Data in                            |   | t0   | ТОСКІ          |

|    | io        | I/O port                           |   | t1   | T1CKI          |

|    | mc        | MCLR                               |   | wr   | WR             |

|    | Uppercase | e letters and their meanings:      |   |      |                |

| S  |           |                                    |   |      |                |

|    | F         | Fall                               |   | Р    | Period         |

|    | Н         | High                               |   | R    | Rise           |

|    | I         | Invalid (High-impedance)           |   | V    | Valid          |

|    | L         | Low                                |   | Z    | High-impedance |

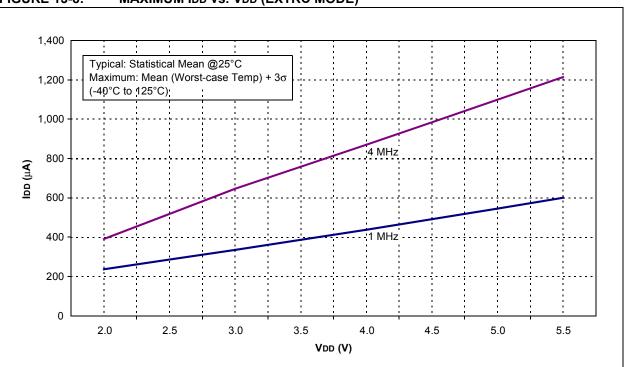

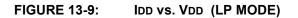

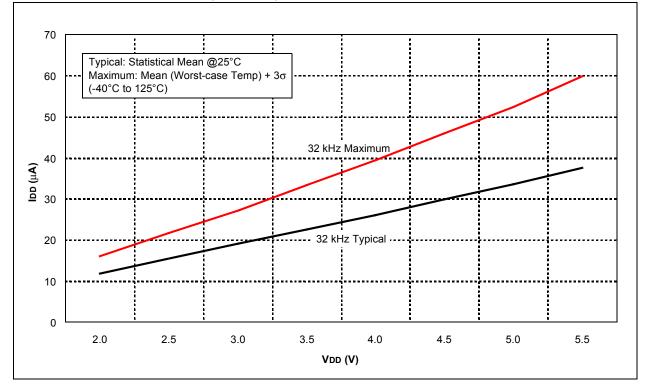

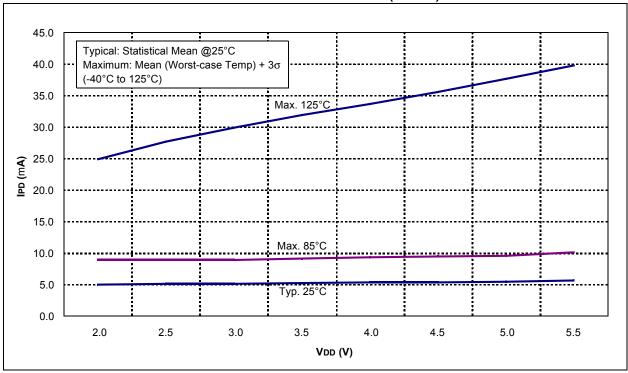

FIGURE 13-23: T1OSC IPD vs. VDD OVER TEMPERATURE (32 kHz)

### 14.2 Package Details

The following sections give the technical details of the packages.

### 18-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units         |      | INCHES   |      |

|----------------------------|---------------|------|----------|------|

| Dime                       | ension Limits | MIN  | NOM      | MAX  |

| Number of Pins             | Ν             |      | 18       |      |

| Pitch                      | е             |      | .100 BSC |      |

| Top to Seating Plane       | А             | -    | -        | .210 |

| Molded Package Thickness   | A2            | .115 | .130     | .195 |

| Base to Seating Plane      | A1            | .015 | -        | -    |

| Shoulder to Shoulder Width | E             | .300 | .310     | .325 |

| Molded Package Width       | E1            | .240 | .250     | .280 |

| Overall Length             | D             | .880 | .900     | .920 |

| Tip to Seating Plane       | L             | .115 | .130     | .150 |

| Lead Thickness             | С             | .008 | .010     | .014 |

| Upper Lead Width           | b1            | .045 | .060     | .070 |

| Lower Lead Width           | b             | .014 | .018     | .022 |

| Overall Row Spacing §      | eB            | -    | -        | .430 |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-007B

## APPENDIX A: REVISION HISTORY

#### Revision A (June 2003)

Original data sheet. However, the device described in this data sheet are upgrades to PIC16C716.

#### **Revision B (February 2007)**

Updated with current formats and added Characterization Data. Replaced Package Drawings.

## APPENDIX B: CONVERSION CONSIDERATIONS

This is a Flash program memory version of the PIC16C716 device. Refer to the migration document, DS40059, for more information about differences between the PIC16F716 and PIC16C716.

## APPENDIX C: MIGRATION FROM BASE-LINE TO MID-RANGE DEVICES

This section discusses how to migrate from a baseline device (i.e., PIC16C5X) to a mid-range device (i.e., PIC16F716).

The following are the list of modifications over the PIC16C5X microcontroller family:

- Instruction word length is increased to 14-bits. This allows larger page sizes both in program memory (2K now as opposed to 512 before) and register file (128 bytes now versus 32 bytes before).

- 2. A PC high latch register (PCLATH) is added to handle program memory paging. Bits PA2, PA1, PA0 are removed from STATUS register.

- 3. Data memory paging is redefined slightly. STATUS register is modified.

- Four new instructions have been added: RETURN, RETFIE, ADDLW, and SUBLW. Two instructions TRIS and OPTION are being phased out although they are kept for compatibility with PIC16C5X.

- 5. OPTION\_REG and TRIS registers are made addressable.

- 6. Interrupt capability is added. Interrupt vector is at 0004h.

- 7. Stack size is increased to 8 deep.

- 8. Reset vector is changed to 0000h.

- Reset of all registers is revisited. Five different Reset (and wake-up) types are recognized. Registers are reset differently.

- 10. Wake-up from Sleep through interrupt is added.

- 11. Two separate timers, Oscillator Start-up Timer (OST) and Power-up Timer (PWRT) are included for more reliable power-up. These timers are invoked selectively to avoid unnecessary delays on power-up and wake-up.

- 12. PORTB has weak pull-ups and interrupt-onchange feature.

- 13. T0CKI pin is also a port pin (RA4) now.

- 14. FSR is made a full eight-bit register.

- "In-circuit serial programming" is made possible. The user can program PIC16F716 devices using only five pins: VDD, Vss, MCLR/VPP, RB6 (clock) and RB7 (data in/out).

- PCON STATUS register is added with a Poweron Reset Status bit (POR).

- 17. Brown-out protection circuitry has been added. Controlled by Configuration Word bits BOREN and BORV. Brown-out Reset ensures the device is placed in a Reset condition if VDD dips below a fixed setpoint.

To convert code written for PIC16C5X to PIC16F716, the user should take the following steps:

- 1. Remove any program memory page select operations (PA2, PA1, PA0 bits) for CALL, GOTO.

- 2. Revisit any computed jump operations (write to PC or add to PC, etc.) to make sure page bits are set properly under the new scheme.

- 3. Eliminate any data memory page switching. Redefine data variables to reallocate them.

- 4. Verify all writes to STATUS, OPTION, and FSR registers since these have changed.

- 5. Change Reset vector to 0000h

- Note 1: This device has been designed to perform to the parameters of its data sheet. It has been tested to an electrical specification designed to determine its conformance with these parameters. Due to process differences in the manufacture of this device, this device may have different performance characteristics than its earlier version. These differences may cause this device to perform differently in your application than the earlier version of this device.

- 2: The user should verify that the device oscillator starts and performs as expected. Adjusting the loading capacitor values and/or the Oscillator mode may be required.

## **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| To:   | Technical Publications Manager         | Total Pages Sent                                       |

|-------|----------------------------------------|--------------------------------------------------------|

| RE:   | Reader Response                        |                                                        |

| From  | i: Name                                |                                                        |

|       |                                        |                                                        |

|       |                                        |                                                        |

|       | City / State / ZIP / Country           |                                                        |

|       | Telephone: ()                          | FAX: ()                                                |

| Appli | cation (optional):                     |                                                        |

| Woul  | ld you like a reply?YN                 |                                                        |

| Devi  | ce: PIC16F716                          | Literature Number: DS41206B                            |

| Ques  | stions:                                |                                                        |

| 1. V  | What are the best features of this do  | cument?                                                |

|       |                                        |                                                        |

| _     |                                        |                                                        |

| 2. ⊦  | low does this document meet your       | hardware and software development needs?               |

| _     |                                        |                                                        |

| _     |                                        |                                                        |

| 3. E  | Do you find the organization of this o | locument easy to follow? If not, why?                  |

| _     |                                        |                                                        |

| _     |                                        |                                                        |

| 4. V  | What additions to the document do y    | ou think would enhance the structure and subject?      |

| _     |                                        |                                                        |

| _     |                                        |                                                        |

| 5. V  | What deletions from the document c     | ould be made without affecting the overall usefulness? |

| _     |                                        |                                                        |

| _     |                                        |                                                        |

| 6. I  | s there any incorrect or misleading i  | nformation (what and where)?                           |

| -     |                                        |                                                        |

| _     |                                        |                                                        |

| 7. ⊦  | low would you improve this docume      | ent?                                                   |

| -     |                                        |                                                        |

|       |                                        |                                                        |

## Е

| ECCP. See Enhanced Capture/Compare/PWM             |               |

|----------------------------------------------------|---------------|

| ECCPAS Register                                    | 57            |

| Effects of Reset                                   |               |

| PWM mode                                           | 55            |

| Electrical Characteristics                         | 91            |

| Enhanced Capture/Compare/PWM                       |               |

| Enhanced Capture/Compare/PWM (ECCP)                |               |

| Enhanced PWM Mode                                  |               |

| Auto-Restart                                       | 58            |

| Auto-shutdown                                      |               |

| Half-Bridge Application Examples                   | 59            |

| Programmable Dead Band Delay                       | 59            |

| Shoot-through Current                              | 59            |

| Timer Resources                                    |               |

| Errata                                             | 4             |

| External Power-on Reset Circuit                    | 64            |

| Shoot-through Current<br>Timer Resources<br>Errata | 59<br>47<br>4 |

## F

| Firmware Instructions77       |

|-------------------------------|

| Fuses. See Configuration Bits |

## I

| I/O Ports                            |       | 19 |

|--------------------------------------|-------|----|

| ID Locations                         |       |    |

| In-Circuit Serial Programming (ICSP) | 61,   | 76 |

| Indirect Addressing                  |       | 18 |

| FSR Register                         | 8, 9, | 18 |

| INDF Register                        |       | 9  |

| Instruction Format                   |       | 77 |

| Instruction Set                      |       | 77 |

| ADDLW                                |       | 79 |

| ADDWF                                |       | 79 |

| ANDLW                                |       | 79 |

| ANDWF                                |       | 79 |

| BCF                                  |       | 79 |

| BSF                                  |       | 79 |

| BTFSC                                |       | 79 |

| BTFSS                                |       | 80 |

| CALL                                 |       | 80 |

| CLRF                                 |       | 80 |

| CLRW                                 |       | 80 |

| CLRWDT                               |       | 80 |

| COMF                                 |       | 80 |

| DECF                                 |       | 80 |

| DECFSZ                               |       | 81 |

| GOTO                                 |       | 81 |

| INCF                                 |       | 81 |

| INCFSZ                               |       | 81 |

| IORLW                                |       | 81 |

| IORWF                                |       | 81 |

| MOVF                                 |       | 82 |

| MOVLW                                |       | 82 |

| MOVWF                                |       | 82 |

| NOP                                  |       | 82 |

| RETFIE                               |       | 83 |

| RETLW                                |       | 83 |

| RETURN                               |       | 83 |

| RLF                                  |       | 84 |

| RRF                                  |       | 84 |

| SLEEP                                |       | 84 |

| SUBLW                                |       | 84 |

| SUBWF                                |       | 85 |

| SWAPF                                |       | 85 |

| XORLW                                |       | 85 |

|                                      |       |    |

| XORWF                                          | 85    |

|------------------------------------------------|-------|

| Summary Table                                  |       |

| INT Interrupt (RB0/INT). See Interrupt Sources |       |

| INTCON Register                                | 9, 13 |

| Internal Sampling Switch (RSS) IMPEDANCE       |       |

| Internet Address                               | 127   |

| Interrupt Sources                              |       |

| Interrupt-on-Change (RB)                       | 21    |

| RB0/INT Pin, External                          | 73    |

| TMR0 Overflow                                  | 73    |

| Interrupts                                     |       |

| ADC                                            | 40    |

| TMR1                                           | 30    |

| Interrupts, Context Saving During              | 73    |

| Interrupts, Enable Bits                        |       |

| Global Interrupt Enable (GIE Bit)              | 72    |

| Interrupt-on-Change (RB) Enable (RBIE Bit)     | 73    |

| Interrupts, Flag Bits                          |       |

| CCP1 Flag (CCP1IF Bit)                         | 15    |

| Interrupt-on-Change (RB) Flag (RBIF Bit)       | 73    |

| TMR0 Overflow Flag (T0IF Bit)                  | 73    |

## Μ

| Master Clear (MCLR)                            |            |

|------------------------------------------------|------------|

| MCLR Reset, Normal Operation                   | 64, 69, 70 |

| MCLR Reset, Sleep                              | 64, 69, 70 |

| Memory Organization                            |            |

| Data Memory                                    | 7          |

| Program Memory                                 | 7          |

| Microchip Internet Web Site                    | 127        |

| Migration from Base-Line to Mid-Range Devices  | 126        |

| MPLAB ASM30 Assembler, Linker, Librarian       | 88         |

| MPLAB ICD 2 In-Circuit Debugger                | 89         |

| MPLAB ICE 2000 High-Performance Universal      |            |

| In-Circuit Emulator                            | 89         |

| MPLAB Integrated Development Environment Softw | /are 87    |

| MPLAB PM3 Device Programmer                    | 89         |

| MPLAB REAL ICE In-Circuit Emulator System      |            |

| MPLINK Object Linker/MPLIB Object Librarian    | 88         |

## 0

| OPCODE Field Descriptions |            |

|---------------------------|------------|

| OPTION Register           |            |

| OPTION_REG Register       |            |

| Oscillator                |            |

| Associated registers      |            |

| Oscillator Configuration  | 61, 63     |

| HS                        | 63, 68     |

| LP                        | 63, 68     |

| RC                        | 63, 64, 68 |

| XT                        | 63, 68     |

| Oscillator, WDT           |            |

## Ρ

| Packaging                            | 121    |

|--------------------------------------|--------|

| PDIP Details                         |        |

| Paging, Program Memory               | 7, 17  |

| PCON Register                        | 16, 68 |

| PICSTART Plus Development Programmer | 90     |

| PIE1 Register                        | 10, 14 |

| PIR1 Register                        | 9, 15  |

| CCP1IF Bit                           | 15     |

| Pointer, FSR                         | 18     |

| POR. See Power-on Reset              |        |

| PORTA                                |        |

| Associated Registers                 | 20     |