Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

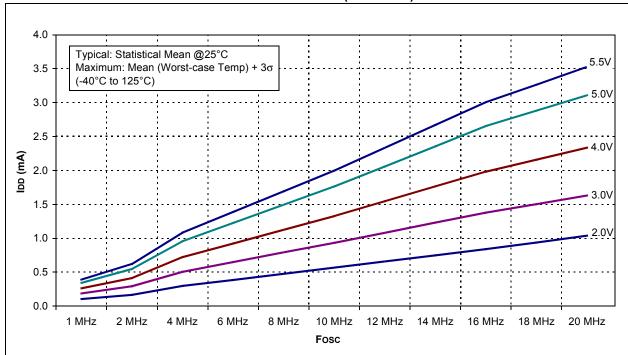

| Speed                      | 20MHz                                                                   |

| Connectivity               | -                                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 13                                                                      |

| Program Memory Size        | 3.5KB (2K x 14)                                                         |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 128 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                               |

| Data Converters            | A/D 4x8b                                                                |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                 |

| Supplier Device Package    | 18-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f716-i-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly or indirectly through the File Select Register FSR (Section 2.5 "Indirect Addressing, INDF and FSR Registers").

FIGURE 2-2:

#### **REGISTER FILE MAP**

| File                                 |                      |                      | File    |  |  |  |

|--------------------------------------|----------------------|----------------------|---------|--|--|--|

| Address                              |                      |                      | Address |  |  |  |

| 00h                                  | INDF <sup>(1)</sup>  | INDF <sup>(1)</sup>  | 80h     |  |  |  |

| 01h                                  | TMR0                 | OPTION_REG           | 81h     |  |  |  |

| 02h                                  | PCL                  | PCL                  | 82h     |  |  |  |

| 03h                                  | STATUS               | STATUS               | 83h     |  |  |  |

| 04h                                  | FSR                  | FSR                  | 84h     |  |  |  |

| 05h                                  | PORTA                | TRISA                | 85h     |  |  |  |

| 06h                                  | PORTB                | TRISB                | 86h     |  |  |  |

| 07h                                  |                      |                      | 87h     |  |  |  |

| 08h                                  |                      |                      | 88h     |  |  |  |

| 09h                                  |                      |                      | 89h     |  |  |  |

| 0Ah                                  | PCLATH               | PCLATH               | 8Ah     |  |  |  |

| 0Bh                                  | INTCON               | INTCON               | 8Bh     |  |  |  |

| 0Ch                                  | PIR1                 | PIE1                 | 8Ch     |  |  |  |

| 0Dh                                  | TMD4                 | DOON                 | 8Dh     |  |  |  |

| 0Eh                                  | TMR1L                | PCON                 | 8Eh     |  |  |  |

| 0Fh                                  | TMR1H                |                      | 8Fh     |  |  |  |

| 10h                                  | T1CON                |                      | 90h     |  |  |  |

| 11h                                  | TMR2                 |                      | 91h     |  |  |  |

| 12h                                  | T2CON                | PR2                  | 92h     |  |  |  |

| 13h                                  |                      |                      | 93h     |  |  |  |

| 14h                                  |                      |                      | 94h     |  |  |  |

| 15h                                  | CCPR1L               |                      | 95h     |  |  |  |

| 16h                                  | CCPR1H               |                      | 96h     |  |  |  |

| 17h                                  | CCP1CON              |                      | 97h     |  |  |  |

| 18h                                  | PWM1CON              |                      | 98h     |  |  |  |

| 19h                                  | ECCPAS               |                      | 99h     |  |  |  |

| 1Ah                                  |                      |                      | 9Ah     |  |  |  |

| 1Bh                                  |                      |                      | 9Bh     |  |  |  |

| 1Ch                                  |                      |                      | 9Ch     |  |  |  |

| 1Dh                                  |                      |                      | 9Dh     |  |  |  |

| 1Eh                                  | ADRES                |                      | 9Eh     |  |  |  |

| 1Fh                                  | ADCON0               | ADCON1               | 9Fh     |  |  |  |

| 20h                                  | General              | General              | A0h     |  |  |  |

|                                      | Purpose<br>Registers | Purpose<br>Registers |         |  |  |  |

|                                      | registers            | 32 Bytes             | BFh     |  |  |  |

|                                      | 80 Bytes             |                      | C0h     |  |  |  |

| 6Fh                                  |                      |                      | EFh     |  |  |  |

| 70h                                  | 16 Bytes             | Accesses             | F0h     |  |  |  |

| 7Fh                                  | -                    | 70-7Fh               | FFh     |  |  |  |

| I                                    | Bank 0               | Bank 1               |         |  |  |  |

| Unimplemented data memory locations, |                      |                      |         |  |  |  |

| read as '0'.                         |                      |                      |         |  |  |  |

| Note 1:                              | Not a physical       | register.            |         |  |  |  |

|                                      |                      |                      |         |  |  |  |

| Address | Name                    | Bit 7              | Bit 6                  | Bit 5       | Bit 4        | Bit 3          | Bit 2           | Bit 1        | Bit 0         | Value on<br>POR, BOR | Page |

|---------|-------------------------|--------------------|------------------------|-------------|--------------|----------------|-----------------|--------------|---------------|----------------------|------|

| 80h     | INDF <sup>(1)</sup>     | Addressin          | ng this location       | on uses con | tents of FSF | R to address   | data memory     | (not a physi | cal register) | 0000 0000            | 18   |

| 81h     | OPTION_REG              | RBPU               | INTEDG                 | TOCS        | TOSE         | PSA            | PS2             | PS1          | PS0           | 1111 1111            | 12   |

| 82h     | PCL <sup>(1)</sup>      | Program            | Counter's (P           | C) Least Si | gnificant By | e              |                 |              |               | 0000 0000            | 17   |

| 83h     | STATUS <sup>(1)</sup>   | IRP <sup>(4)</sup> | RP1 <sup>(4)</sup>     | RP0         | TO           | PD             | Z               | DC           | С             | 0001 1xxx            | 11   |

| 84h     | FSR <sup>(1)</sup>      | Indirect D         | ata Memory             | Address Po  | binter       |                |                 |              |               | xxxx xxxx            | 18   |

| 85h     | TRISA                   | _                  | _                      | (7)         | TRISA4       | TRISA3         | TRISA2          | TRISA1       | TRISA0        | 1 1111               | 19   |

| 86h     | TRISB                   | TRISB7             | TRISB6                 | TRISB5      | TRISB4       | TRISB3         | TRISB2          | TRISB1       | TRISB0        | 1111 1111            | 21   |

| 87h-89h | _                       | Unimplem           | nented                 |             |              |                |                 |              |               | —                    |      |

| 8Ah     | PCLATH <sup>(1,2)</sup> | _                  | _                      | _           | Write Buffe  | er for the upp | er 5 bits of th | e Program C  | Counter       | 0 0000               | 17   |

| 8Bh     | INTCON <sup>(1)</sup>   | GIE                | PEIE                   | T0IE        | INTE         | RBIE           | T0IF            | INTF         | RBIF          | x000 0000            | 13   |

| 8Ch     | PIE1                    | _                  | ADIE                   | _           | _            | _              | CCP1IE          | TMR2IE       | TMR1IE        | -0000                | 14   |

| 8Dh     |                         | Unimplem           | nented                 |             |              |                |                 |              |               | _                    |      |

| 8Eh     | PCON                    | —                  | _                      | -           | —            | -              | _               | POR          | BOR           | dd                   | 16   |

| 8Fh-91h | _                       | Unimplem           | Unimplemented          |             |              |                |                 |              | _             |                      |      |

| 92h     | PR2                     | Timer2 Pe          | Timer2 Period Register |             |              |                |                 |              | 1111 1111     | 35, 52               |      |

| 93h-9Eh |                         | Unimplem           | Jnimplemented          |             |              |                |                 |              |               | _                    |      |

| 9Fh     | ADCON1                  |                    | _                      | _           | _            | —              | PCFG2           | PCFG1        | PCFG0         | 000                  | 42   |

#### **TABLE 2-2: SPECIAL FUNCTION REGISTER SUMMARY BANK 1**

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', Shaded locations are unimplemented, Note

1:

read as '0'. These registers can be addressed from either bank. The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<12:8> whose contents are 2: transferred to the upper byte of the program counter. Other (non Power-up) Resets include: external Reset through MCLR and the Watchdog Timer Reset. The IRP and RP1 bits are reserved. Always maintain these bits clear.

3:

4:

On any device Reset, these pins are configured as inputs. This is the value that will be in the PORT output latch. 5:

6: 7: Reserved bits, do not use.

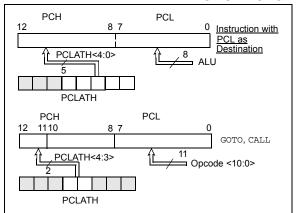

# 2.3 PCL and PCLATH

The Program Counter (PC) is 13 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<12:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 2-3 shows the two situations for the loading of the PC. The upper example in Figure 2-3 shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in Figure 2-3 shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### 2.3.1 MODIFYING PCL

Executing any instruction with the PCL register as the destination simultaneously causes the Program Counter PC<12:8> bits (PCH) to be replaced by the contents of the PCLATH register. This allows the entire contents of the program counter to be changed by writing the desired upper 5 bits to the PCLATH register. When the lower 8 bits are written to the PCL register, all 13 bits of the program counter will change to the values contained in the PCLATH register.

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). Care should be exercised when jumping into a look-up table or program branch table (computed GOTO) by modifying the PCL register. Assuming that PCLATH is set to the table start address, if the table length is greater than 255 instructions or if the lower 8 bits of the memory address rolls over from 0xFF to 0x00 in the middle of the table, then PCLATH must be incremented for each address rollover that occurs between the table beginning and the target location within the table.

For more information refer to Application Note AN556, *"Implementing a Table Read"* (DS00556).

#### 2.3.2 PROGRAM MEMORY PAGING

The CALL and GOTO instructions provide 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction, the upper bit of the address is provided by PCLATH<3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bit is programmed so that the desired program memory page is addressed. If a RETURN from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is pushed onto the stack. Therefore, manipulation of the PCLATH<3> bit is not required for the RETURN instructions (which POPs the address from the stack).

#### FIGURE 2-3: LOADING OF PC IN DIFFERENT SITUATIONS

# 2.4 Stack

The stack allows a combination of up to 8 program calls and interrupts to occur. The stack contains the return address from this branch in program execution.

Mid-range devices have an 8-level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space, and the Stack Pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not modified when the stack is PUSHed or POPed.

After the stack has been PUSHed 8 times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

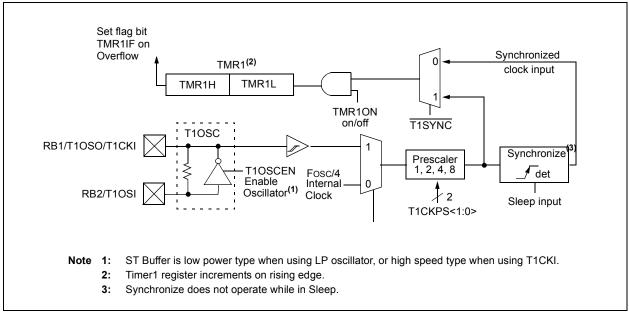

# 5.0 TIMER1 MODULE WITH GATE CONTROL

The Timer1 module is a 16-bit timer/counter with the following features:

- 16-bit timer/counter register pair (TMR1H:TMR1L)

- Programmable internal or external clock source

- 3-bit prescaler

- Optional LP oscillator

- Synchronous or asynchronous operation

- Interrupt on overflow

- Wake-up on overflow (external clock, Asynchronous mode only)

- Time base for the Capture/Compare function

- Special Event Trigger (with ECCP)

Figure 5-1 is a block diagram of the Timer1 module.

#### FIGURE 5-1: TIMER1 BLOCK DIAGRAM

#### 5.1 Timer1 Operation

The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer. When used with an external clock source, the module can be used as either a timer or counter.

# 5.2 Clock Source Selection

The TMR1CS bit of the T1CON register is used to select the clock source. When TMR1CS = 0, the clock source is FOSC/4. When TMR1CS = 1, the clock source is supplied externally.

#### 5.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected, the TMR1H:TMR1L register pair will increment on multiples of TcY as determined by the Timer1 prescaler.

#### 5.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter.

When counting, Timer1 is incremented on the rising edge of the external clock input T1CKI. In addition, the Counter mode clock can be synchronized to the microcontroller system clock or run asynchronously.

In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge after one or more of the following conditions:

- · Timer1 is enabled after POR or BOR Reset

- · A write to TMR1H or TMR1L

- T1CKI is high when Timer1 is disabled and when Timer1 is reenabled T1CKI is low. See Figure 5-2.

| Name   | Bit 7                                                                       | Bit 6          | Bit 5         | Bit 4          | Bit 3         | Bit 2       | Bit 1     | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-----------------------------------------------------------------------------|----------------|---------------|----------------|---------------|-------------|-----------|--------|----------------------|---------------------------------|

| INTCON | GIE                                                                         | PEIE           | T0IE          | INTE           | RBIE          | T0IF        | INTF      | RBIF   | 0000 000x            | 0000 000x                       |

| PIE1   | _                                                                           | ADIE           | _             | _              | _             | CCP1IE      | TMR2IE    | TMR1IE | -0000                | -0000                           |

| PIR1   | _                                                                           | ADIF           | _             | _              | _             | CCP1IF      | TMR2IF    | TMR1IF | -0000                | -0000                           |

| TMR1H  | Holding Reg                                                                 | gister for the | Most Signific | ant Byte of th | ne 16-bit TMF | R1 Register |           |        | xxxx xxxx            | uuuu uuuu                       |

| TMR1L  | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |                |               |                |               | xxxx xxxx   | uuuu uuuu |        |                      |                                 |

| T1CON  | _                                                                           | _              | T1CKPS1       | T1CKPS0        | T1OSCEN       | T1SYNC      | TMR1CS    | TMR10N | 00 0000              | uu uuuu                         |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

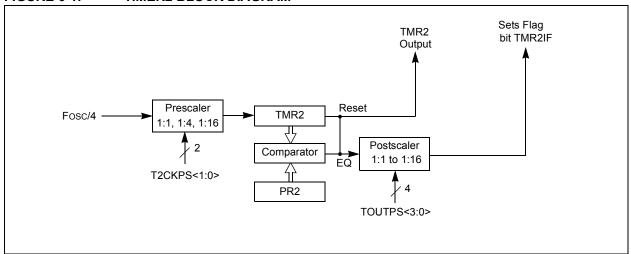

# 6.0 TIMER2 MODULE

The Timer2 module is an 8-bit timer with the following features:

- 8-bit timer register (TMR2)

- 8-bit period register (PR2)

- Interrupt on TMR2 match with PR2

- Software programmable prescaler (1:1, 1:4, 1:16)

- Software programmable postscaler (1:1 to 1:16)

See Figure 6-1 for a block diagram of Timer2.

#### 6.1 Timer2 Operation

The clock input to the Timer2 module is the system instruction clock (Fosc/4). The clock is fed into the Timer2 prescaler, which has prescale options of 1:1, 1:4 or 1:16. The output of the prescaler is then used to increment the TMR2 register.

The values of TMR2 and PR2 are constantly compared to determine when they match. TMR2 will increment from 00h until it matches the value in PR2. When a match occurs, two things happen:

- TMR2 is reset to 00h on the next increment cycle

- The Timer2 postscaler is incremented

The match output of the Timer2/PR2 comparator is then fed into the Timer2 postscaler. The postscaler has postscale options of 1:1 to 1:16 inclusive. The output of the Timer2 postscaler is used to set the TMR2IF interrupt flag bit in the PIR2 register.

#### FIGURE 6-1: TIMER2 BLOCK DIAGRAM

The TMR2 and PR2 registers are both fully readable and writable. On any Reset, the TMR2 register is set to 00h and the PR2 register is set to FFh.

Timer2 is turned on by setting the TMR2ON bit in the T2CON register to a '1'. Timer2 is turned off by clearing the TMR2ON bit to a '0'.

The Timer2 prescaler is controlled by the T2CKPS bits in the T2CON register. The Timer2 postscaler is controlled by the TOUTPS bits in the T2CON register. The prescaler and postscaler counters are cleared when:

- · A write to TMR2 occurs.

- A write to T2CON occurs.

- Any device Reset occurs (Power-on Reset, MCLR Reset, Watchdog Timer Reset, or Brown-out Reset).

Note: TMR2 is not cleared when T2CON is written.

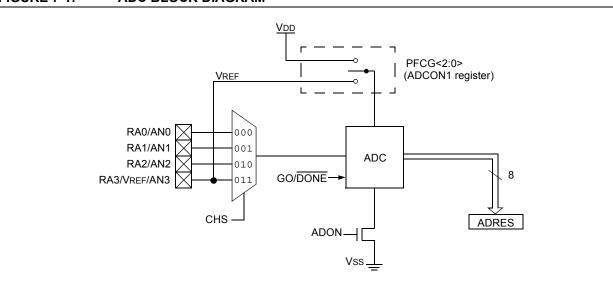

# 7.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

The Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 8-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 8-bit binary result via successive approximation and stores the conversion result into the ADC result register (ADRES).

The ADC voltage reference is software selectable to either VDD or a voltage applied to the external reference pins.

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake-up the device from Sleep.

Figure 7-1 shows the block diagram of the ADC.

### FIGURE 7-1: ADC BLOCK DIAGRAM

# 7.1 ADC Configuration

When configuring and using the ADC the following functions must be considered:

- · Port configuration

- · Channel selection

- · ADC voltage reference selection

- · ADC conversion clock source

- Interrupt control

#### 7.1.1 PORT CONFIGURATION

The ADC can be used to convert both analog and digital signals. When converting analog signals, the I/O pin should be configured for analog by setting the associated TRIS and ADCON1 bits. See the corresponding Port section for more information.

| Note: | Analog voltages on any pin that is defined |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|

|       | as a digital input may cause the input     |  |  |  |  |  |  |  |

|       | buffer to conduct excess current.          |  |  |  |  |  |  |  |

#### 7.1.2 CHANNEL SELECTION

The CHS bits of the ADCON0 register determine which channel is connected to the sample and hold circuit.

When changing channels, a delay is required before starting the next conversion. Refer to **Section 7.2 "ADC Operation"** for more information.

### 7.1.3 ADC VOLTAGE REFERENCE

The PCFG bits of the ADCON0 register provide independent control of the positive voltage reference. The positive voltage reference can be either VDD or an external voltage source.

#### 7.1.4 CONVERSION CLOCK

The source of the conversion clock is software selectable via the ADCS bits of the ADCON0 register. There are four possible clock options:

- Fosc/2

- Fosc/8

- Fosc/32

- FRC (dedicated internal oscillator)

The time to complete one bit conversion is defined as TAD. One full 8-bit conversion requires 9.5 TAD periods.

For correct conversion, the appropriate TAD specification must be met. See A/D conversion requirements in **Section 12.0 "Electrical Characteristics"** for more information. Table 7-1 gives examples of appropriate ADC clock selections.

Note: Unless using the FRC, any changes in the system clock frequency will change the ADC clock frequency, which may adversely affect the ADC result.

#### TABLE 7-1: TAD vs. DEVICE OPERATING FREQUENCIES

| AD Clock Source (TAD) |           | Device Frequency           |                            |                            |                       |  |  |

|-----------------------|-----------|----------------------------|----------------------------|----------------------------|-----------------------|--|--|

| Operation             | ADCS<1:0> | 20 MHz                     | 5 MHz                      | 1.25 MHz                   | 333.33 kHz            |  |  |

| 2 Tosc                | 0 0       | 100 ns <sup>(2)</sup>      | 400 ns <sup>(2)</sup>      | 1.6 μs                     | 6 µs                  |  |  |

| 8 Tosc                | 01        | 400 ns <sup>(2)</sup>      | 1.6 μs                     | 6.4 μs                     | 24 μs <sup>(3)</sup>  |  |  |

| 32 Tosc               | 10        | 1.6 μs                     | 6.4 μs                     | 25.6 μs <sup>(3)</sup>     | 96 μs <sup>(3)</sup>  |  |  |

| RC                    | 11        | 2-6 μs <sup>(1), (4)</sup> | 2-6 μs <sup>(1), (4)</sup> | 2-6 μs <sup>(1), (4)</sup> | 2-6 μs <sup>(1)</sup> |  |  |

Legend: Shaded cells are outside of recommended range.

Note 1: The RC source has a typical TAD time of 4  $\mu$ s.

2: These values violate the minimum required TAD time.

3: For faster conversion times, the selection of another clock source is recommended.

4: When device frequency is greater than 1 MHz, the RC A/D conversion clock source is recommended for Sleep operation only.

### 9.2 Oscillator Configurations

#### 9.2.1 OSCILLATOR TYPES

The PIC16F716 can be operated in four different oscillator modes. The user can program two Configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low-power Crystal

- · XT Crystal/Resonator

- HS High-speed Crystal/Resonator

- RC Resistor/Capacitor

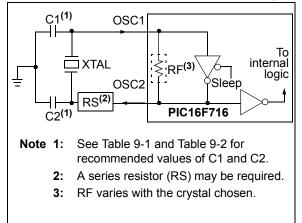

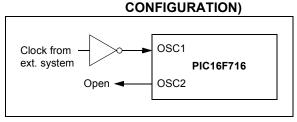

# 9.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 9-1). The PIC16F716 oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1/CLKIN pin (Figure 9-2).

| FIGURE 9-1: | CRYSTAL/CERAMIC            |

|-------------|----------------------------|

|             | <b>RESONATOR OPERATION</b> |

|             | (HS, XT OR LP              |

|             | OSC CONFIGURATION)         |

FIGURE 9-2: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC

### TABLE 9-1: CERAMIC RESONATORS

| Ranges Tested:                                                                  |                                |                                  |                                  |  |  |  |

|---------------------------------------------------------------------------------|--------------------------------|----------------------------------|----------------------------------|--|--|--|

| Mode                                                                            | Freq                           | OSC1 (C1)                        | OSC2 (C2)                        |  |  |  |

| ХТ                                                                              | 455 kHz<br>2.0 MHz             | 68-100 pF<br>15-68 pF            | 68-100 pF<br>15-68 pF            |  |  |  |

| HS                                                                              | 4.0 MHz<br>8.0 MHz<br>16.0 MHz | 10-68 pF<br>15-68 pF<br>10-22 pF | 10-68 pF<br>15-68 pF<br>10-22 pF |  |  |  |

| Note 1: These values are for design guidance only. See notes at bottom of page. |                                |                                  |                                  |  |  |  |

# TABLE 9-2:CAPACITOR SELECTION FOR<br/>CRYSTAL OSCILLATOR

| Osc Type                                                                           | Crystal<br>Freq | Cap. Range<br>C1 | Cap. Range<br>C2 |  |  |

|------------------------------------------------------------------------------------|-----------------|------------------|------------------|--|--|

| LP                                                                                 | 32 kHz          | 15-33 pF         | 15-33 pF         |  |  |

|                                                                                    | 200 kHz         | 5-10 pF          | 5-10 pF          |  |  |

| XT                                                                                 | 200 kHz         | 47-68 pF         | 47-68 pF         |  |  |

|                                                                                    | 1 MHz           | 15-33 pF         | 15-33 pF         |  |  |

|                                                                                    | 4 MHz           | 15-33 pF         | 15-33 pF         |  |  |

| HS                                                                                 | 4 MHz           | 15-33 pF         | 15-33 pF         |  |  |

|                                                                                    | 8 MHz           | 15-33 pF         | 15-33 pF         |  |  |

|                                                                                    | 20 MHz          | 15-33 pF         | 15-33 pF         |  |  |

| Note 1: These values are for design guidance only.<br>See notes at bottom of page. |                 |                  |                  |  |  |

- **Note 1:** Higher capacitance increases the stability of the oscillator, but also increases the start-up time.

- 2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- **3:** RS may be required to avoid overdriving crystals with low drive level specification.

- 4: When using an external clock for the OSC1 input, loading of the OSC2 pin must be kept to a minimum by leaving the OSC2 pin unconnected.

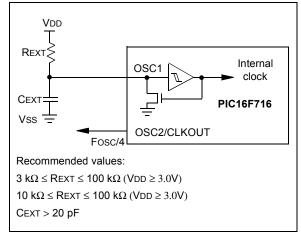

### 9.2.3 RC OSCILLATOR

For timing insensitive applications, the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values and the operating temperature. In addition to this, the oscillator frequency will vary from unit-to-unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 9-3 shows how the R/C combination is connected to the PIC16F716.

FIGURE 9-3: RC OSCILLATOR MODE

### 9.3 Reset

The PIC16F716 differentiates between various kinds of Reset:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during Sleep

- WDT Reset (during normal operation)

- WDT Wake-up (during Sleep)

- Brown-out Reset (BOR)

Some registers are not affected in any Reset condition; their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on Power-on Reset (POR), on the MCLR and WDT Reset, on MCLR Reset during Sleep and Brown-out Reset (BOR). They are not affected by a WDT Wake-up, which is viewed as the resumption of normal operation. The TO and PD bits are set or cleared differently in different Reset situations as indicated in Table 9-4. These bits are used in software to determine the nature of the Reset. See Table 9-6 for a full description of Reset states of all registers.

A simplified block diagram of the On-chip Reset circuit is shown in Figure 9-5.

The PIC<sup>®</sup> microcontrollers have an  $\overline{\text{MCLR}}$  noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive the  $\overline{\text{MCLR}}$  pin low.

# 9.4 Power-On Reset (POR)

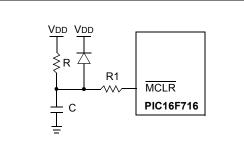

A Power-on Reset pulse is generated on-chip when VDD rise is detected. To take advantage of the POR, just tie the MCLR pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified (parameter D004). For a slow rise time, see Figure 9-4.

When the device starts normal operation (exits the Reset condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met. Brown-out Reset may be used to meet the start-up conditions.

#### EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: External Power-on Reset circuit is required only if VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- R < 40 kΩ is recommended to make sure that voltage drop across R does not violate the device's electrical specification.

- **3:** R1 =  $100\Omega$  to 1 k $\Omega$  will limit any current flowing into  $\overline{MCLR}$  from external capacitor C in the event of  $\overline{MCLR}/VPP$  pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

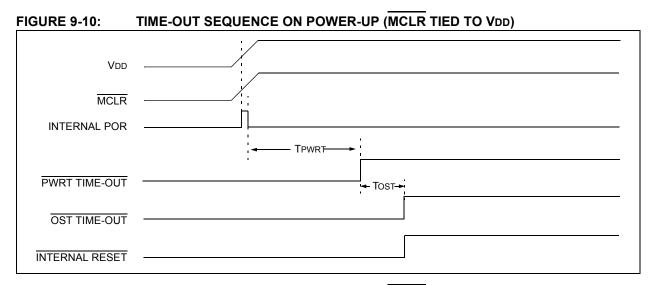

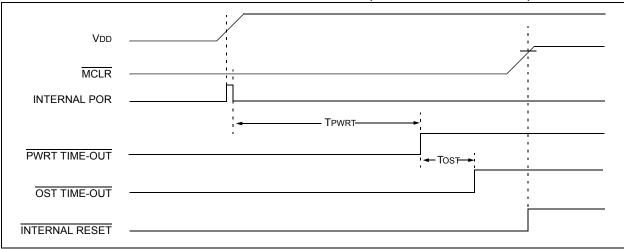

### 9.5 Power-up Timer (PWRT)

The Power-up Timer provides a fixed nominal time-out, on power-up only, from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in Reset as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. The power-up timer enable Configuration bit, PWRTE, is provided to enable/disable the PWRT.

The power-up time delay will vary from chip-to-chip due to VDD, temperature and process variation. See AC parameters for details.

### 9.6 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized. See AC parameters for details.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from Sleep.

# 9.7 Programmable Brown-Out Reset (PBOR)

The PIC16F716 has on-chip Brown-out Reset circuitry. A Configuration bit, BOREN, can disable (if clear/programmed) or enable (if set) the Brown-out Reset circuitry.

The BORV Configuration bit selects the programmable Brown-out Reset threshold voltage (VBOR). When BORV is 1, VBOR IS 4.0V. When BORV is 0, VBOR is 2.5V

A Brown-out Reset occurs when VDD falls below VBOR for a time greater than parameter TBOR (see Table 12-4). A Brown-out Reset is not guaranteed to occur if VDD falls below VBOR for less than parameter TBOR.

On any Reset (Power-on, Brown-out, Watchdog, etc.) the chip will remain in Reset until VDD rises above VBOR. The Power-up Timer will be invoked and will keep the chip in Reset an additional 72 ms only if the Power-up Timer enable bit in the Configuration register is set to 0 ( $\overline{PWRTE} = 0$ ).

If the Power-up Timer is enabled and VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above VBOR, the Power-up Timer will execute a 72 ms Reset. See Figure 9-6.

For operations where the desired brown-out voltage is other than 4.0V or 2.5V, an external brown-out circuit must be used. Figure 9-8, Figure 9-9 and Figure 9-10 show examples of external Brown-out Protection circuits.

| Register                       | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset | Wake-up via WDT or<br>Interrupt |

|--------------------------------|------------------------------------|--------------------------|---------------------------------|

| W                              | xxxx xxxx                          | uuuu uuuu                | սսսս սսսս                       |

| INDF                           | N/A                                | N/A                      | N/A                             |

| TMR0                           | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PCL                            | 0000h                              | 0000h                    | PC + 1 <sup>(2)</sup>           |

| STATUS                         | 0001 1xxx                          | 000q quuu <sup>(3)</sup> | uuuq quuu <sup>(3)</sup>        |

| FSR                            | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PORTA <sup>(4),</sup> (5), (6) | xx 0000                            | xx 0000                  | uu uuuu                         |

| PORTB <sup>(4), (5)</sup>      | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PCLATH                         | 0 0000                             | 0 0000                   | u uuuu                          |

| INTCON                         | 0000 -00x                          | 0000 -00u                | uuuu -uuu <sup>(1)</sup>        |

| PIR1                           | -0000                              | -0000                    | -uuuu <sup>(1)</sup>            |

| TMR1L                          | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| TMR1H                          | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| T1CON                          | 00 0000                            | uu uuuu                  | uu uuuu                         |

| TMR2                           | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| T2CON                          | -000 0000                          | -000 0000                | -uuu uuuu                       |

| CCPR1L                         | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| CCPR1H                         | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| CCP1CON                        | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| PWM1CON                        | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| ECCPAS                         | 00-0 0000                          | 00-0 0000                | u-uu uuuu                       |

| ADRES                          | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| ADCON0                         | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| OPTION_REG                     | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| TRISA                          | 11 1111                            | 11 1111                  | uu uuuu                         |

| TRISB                          | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| PIE1                           | -0000                              | -0000                    | -uuuu                           |

| PCON                           | dd                                 | uu                       | uu                              |

| PR2                            | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| ADCON1                         | 000                                | 000                      | uuu                             |

#### TABLE 9-6: INITIALIZATION CONDITIONS FOR ALL REGISTERS OF THE PIC16F716

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition

**Note 1:** One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

- **3:** See Table 9-5 for Reset value for specific condition.

- **4:** On any device Reset, these pins are configured as inputs.

- 5: This is the value that will be in the port output latch.

- 6: Output latches are unknown or unchanged. Analog inputs default to analog and read '0'.

FIGURE 9-11: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

FIGURE 9-12: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

# PIC16F716

NOTES:

# 11.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB® IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C18 and MPLAB C30 C Compilers

- MPLINK™ Object Linker/

- MPLIB™ Object Librarian

- MPLAB ASM30 Assembler/Linker/Library

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD 2

- Device Programmers

- PICSTART® Plus Development Programmer

- MPLAB PM3 Device Programmer

- PICkit™ 2 Development Programmer

- Low-Cost Demonstration and Development Boards and Evaluation Kits

### 11.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- · A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- High-level source code debugging

- Visual device initializer for easy register initialization

- · Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive on-line help

- Integration of select third party tools, such as HI-TECH Software C Compilers and IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either assembly or C)

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- · Debug using:

- Source files (assembly or C)

- Mixed assembly and C

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

### 11.11 PICSTART Plus Development Programmer

The PICSTART Plus Development Programmer is an easy-to-use, low-cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. The PICSTART Plus Development Programmer supports most PIC devices in DIP packages up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus Development Programmer is CE compliant.

### 11.12 PICkit 2 Development Programmer

The PICkit<sup>™</sup> 2 Development Programmer is a low-cost programmer and selected Flash device debugger with an easy-to-use interface for programming many of Microchip's baseline, mid-range and PIC18F families of Flash memory microcontrollers. The PICkit 2 Starter Kit includes a prototyping development board, twelve sequential lessons, software and HI-TECH's PICC<sup>™</sup> Lite C compiler, and is designed to help get up to speed quickly using PIC<sup>®</sup> microcontrollers. The kit provides everything needed to program, evaluate and develop applications using Microchip's powerful, mid-range Flash memory family of microcontrollers.

### 11.13 Demonstration, Development and Evaluation Boards

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart<sup>®</sup> battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Check the Microchip web page (www.microchip.com) and the latest *"Product Selector Guide"* (DS00148) for the complete list of demonstration, development and evaluation kits.

# PIC16F716

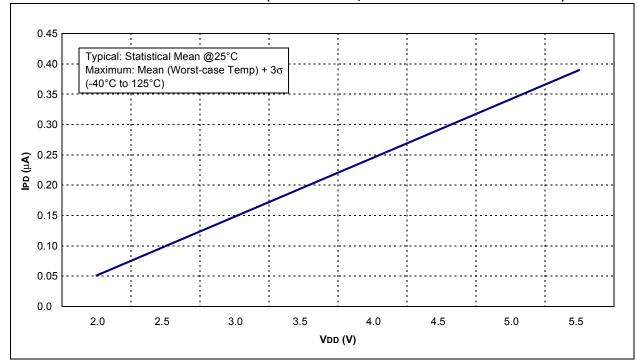

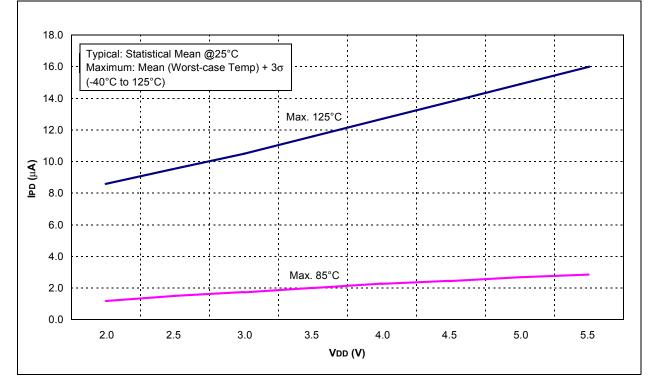

FIGURE 13-10: TYPICAL IPD vs. VDD (SLEEP MODE, ALL PERIPHERALS DISABLED)

# PIC16F716

| Timing Diagrams and Specifications |     |

|------------------------------------|-----|

| A/D Conversion                     | 105 |

| Brown-out Reset (BOR)              | 101 |

| Capture/Compare/PWM (CCP)          | 103 |

| CLKOUT and I/O                     | 100 |

| External Clock                     |     |

| Oscillator Start-up Timer (OST)    | 101 |

| Power-up Timer (PWRT)              | 101 |

| Reset                              | 101 |

| Timer0 and Timer1                  | 102 |

| Watchdog Timer (WDT)               | 101 |

# ۷

VREF. SEE ADC Reference Voltage

#### W

| W/Deviator                      | 70     |

|---------------------------------|--------|

| W Register                      |        |

| Wake-up from Sleep              | 61, 75 |

| Interrupts                      |        |

| MCLR Reset                      | 70     |

| Timing Diagram                  | 76     |

| WDT Reset                       | 70     |

| Watchdog Timer (WDT)            | 61, 74 |

| Enable (WDTE Bit)               | 74     |

| Postscaler. See Postscaler, WDT |        |

| Programming Considerations      | 74     |

| RC Oscillator                   |        |

| Time-out Period                 | 74     |

| Timing Diagram                  |        |

| WDT Reset, Normal Operation     |        |

| WDT Reset, Sleep                |        |

| WWW Address                     |        |

| WWW, On-Line Support            |        |

|                                 |        |

# WORLDWIDE SALES AND SERVICE

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://support.microchip.com Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

**Chicago** Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara, CA Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Habour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Fuzhou** Tel: 86-591-8750-3506 Fax: 86-591-8750-3521

**China - Hong Kong SAR** Tel: 852-2401-1200 Fax: 852-2401-3431

China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

**China - Shunde** Tel: 86-757-2839-5507 Fax: 86-757-2839-5571

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7250 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-4182-8400 Fax: 91-80-4182-8422

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Yokohama** Tel: 81-45-471- 6166 Fax: 81-45-471-6122

**Korea - Gumi** Tel: 82-54-473-4301 Fax: 82-54-473-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

**Malaysia - Penang** Tel: 60-4-646-8870 Fax: 60-4-646-5086

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-572-9526 Fax: 886-3-572-6459

**Taiwan - Kaohsiung** Tel: 886-7-536-4818 Fax: 886-7-536-4803

**Taiwan - Taipei** Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820