Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                 |

| Data Converters            | A/D 4x8b                                                                  |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 18-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f716t-e-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is give in Table 2-1.

The Special Function Registers can be classified into two sets; core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in that peripheral feature section.

| Address | Name                    | Bit 7              | Bit 6                                                                                         | Bit 5         | Bit 4          | Bit 3           | Bit 2          | Bit 1       | Bit 0   | Value on<br>POR, BOR | Page |

|---------|-------------------------|--------------------|-----------------------------------------------------------------------------------------------|---------------|----------------|-----------------|----------------|-------------|---------|----------------------|------|

| 00h     | INDF <sup>(1)</sup>     | Addressing         | ddressing this location uses contents of FSR to address data memory (not a physical register) |               |                |                 |                |             |         |                      | 18   |

| 01h     | TMR0                    | Timer0 mod         | ule's register                                                                                |               |                |                 |                |             |         | xxxx xxxx            | 27   |

| 02h     | PCL <sup>(1)</sup>      | Program Co         | ounter's (PC)                                                                                 | Least Signif  | icant Byte     |                 |                |             |         | 0000 0000            | 17   |

| 03h     | STATUS <sup>(1)</sup>   | IRP <sup>(4)</sup> | RP1 <sup>(4)</sup>                                                                            | RP0           | TO             | PD              | Z              | DC          | С       | 0001 1xxx            | 11   |

| 04h     | FSR <sup>(1)</sup>      | Indirect Data      | a Memory Ac                                                                                   | Idress Pointe | er             |                 |                |             |         | xxxx xxxx            | 18   |

| 05h     | PORTA <sup>(5,6)</sup>  | _                  | _                                                                                             | (7)           | RA4            | RA3             | RA2            | RA1         | RA0     | x 0000               | 19   |

| 06h     | PORTB <sup>(5,6)</sup>  | RB7                | RB6                                                                                           | RB5           | RB4            | RB3             | RB2            | RB1         | RB0     | xxxx xxxx            | 21   |

| 07h-09h | _                       | Unimpleme          | nted                                                                                          |               |                |                 |                |             |         | —                    |      |

| 0Ah     | PCLATH <sup>(1,2)</sup> | _                  | _                                                                                             | _             | Write Bu       | ffer for the up | oper 5 bits of | the Program | Counter | 0 0000               | 17   |

| 0Bh     | INTCON <sup>(1)</sup>   | GIE                | PEIE                                                                                          | T0IE          | INTE           | RBIE            | T0IF           | INTF        | RBIF    | 0000 000x            | 13   |

| 0Ch     | PIR1                    | _                  | ADIF                                                                                          | _             | _              | _               | CCP1IF         | TMR2IF      | TMR1IF  | -0000                | 15   |

| 0Dh     | _                       | Unimpleme          | nted                                                                                          |               |                |                 |                |             |         | —                    |      |

| 0Eh     | TMR1L                   | Holding Reg        | gister for the                                                                                | Least Signifi | cant Byte of   | the 16-bit TN   | IR1 Register   |             |         | xxxx xxxx            | 29   |

| 0Fh     | TMR1H                   | Holding Reg        | gister for the                                                                                | Most Signific | ant Byte of th | he 16-bit TM    | R1 Register    |             |         | xxxx xxxx            | 29   |

| 10h     | T1CON                   | _                  | _                                                                                             | T1CKPS1       | T1CKPS0        | T1OSCEN         | T1SYNC         | TMR1CS      | TMR10N  | 00 0000              | 32   |

| 11h     | TMR2                    |                    |                                                                                               |               | Timer2 Modu    | ile's Register  |                |             |         | 0000 0000            | 35   |

| 12h     | T2CON                   | _                  | TOUTPS3                                                                                       | TOUTPS2       | TOUTPS1        | TOUTPS0         | TMR2ON         | T2CKPS1     | T2CKPS0 | -000 0000            | 36   |

| 13h-14h | _                       | Unimpleme          | nted                                                                                          |               |                |                 |                |             |         | —                    |      |

| 15h     | CCPR1L                  | Capture/Co         | mpare/PWM                                                                                     | Register 1 (I | _SB)           |                 |                |             |         | xxxx xxxx            | 48   |

| 16h     | CCPR1H                  | Capture/Co         | mpare/PWM                                                                                     | Register 1 (I | MSB)           |                 |                |             |         | xxxx xxxx            | 48   |

| 17h     | CCP1CON                 | P1M1               | P1M0                                                                                          | DC1B1         | DC1B0          | CCP1M3          | CCP1M2         | CCP1M1      | CCP1M0  | 0000 0000            | 48   |

| 18h     | PWM1CON                 | PRSEN              | PDC6                                                                                          | PDC5          | PDC4           | PDC3            | PDC2           | PDC1        | PDC0    | 0000 0000            | 60   |

| 19h     | ECCPAS                  | ECCPASE            | ECCPAS2                                                                                       | (8)           | ECCPAS0        | PSSAC1          | PSSAC0         | PSSBD1      | PSSBD0  | 00-0 0000            | 57   |

| 1Ah-1Dh | _                       | Unimpleme          | nted                                                                                          |               |                |                 |                |             |         | _                    |      |

| 1Eh     | ADRES                   | A/D Result I       | Register                                                                                      |               |                |                 |                |             |         | xxxx xxxx            | 37   |

| 1Fh     | ADCON0                  | ADCS1              | ADCS0                                                                                         | CHS2          | CHS1           | CHS0            | GO/DONE        | (7)         | ADON    | 0000 0000            | 41   |

#### TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY BANK 0

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from either bank.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<12:8> whose contents are transferred to the upper byte of the program counter.

3: Other (non Power-up) Resets include: external Reset through MCLR and the Watchdog Timer Reset.

4: The IRP and RP1 bits are reserved. Always maintain these bits clear.

**5:** On any device Reset, these pins are configured as inputs.

6: This is the value that will be in the PORT output latch.

7: Reserved bits, do not use.

8: ECCPAS1 bit is not used on PIC16F716.

## 2.2.2.5 PIR1 Register

This register contains the individual flag bits for the peripheral interrupts.

Note: Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

## REGISTER 2-5: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

| U-0   | R/W-0    | R/W-0 | R/W-0 R/W-0 |  | U-0    | R/W-0  | R/W-0  |

|-------|----------|-------|-------------|--|--------|--------|--------|

| —     | — ADIF – |       |             |  | CCP1IF | TMR2IF | TMR1IF |

| bit 7 |          |       |             |  |        |        | bit 0  |

| Legend:           |                                                     |                      |                    |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |

| bit 7<br>bit 6 | Unimplemented: Read as '0'<br>ADIF: A/D Interrupt Flag bit<br>1 = A/D conversion complete<br>0 = A/D conversion has not completed or has not been started                                                                                                                                                                      |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5-3        | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                     |

| bit 2          | CCP1IF: CCP1 Interrupt Flag bit                                                                                                                                                                                                                                                                                                |

|                | <u>Capture Mode</u><br>1 = A TMR1 register capture occurred (must be cleared in software)<br>0 = No TMR1 register capture occurred<br><u>Compare Mode</u><br>1 = A TMR1 register compare match occurred (must be cleared in software)<br>0 = No TMR1 register compare match occurred<br><u>PWM Mode</u><br>Unused in this mode |

| bit 1          | TMR2IF: Timer2 to PR2 Match Interrupt Flag bit <ol> <li>= Timer2 to PR2 match occurred (must be cleared in software)</li> <li>= Timer2 to PR2 match has not occurred</li> </ol>                                                                                                                                                |

| bit 0          | TMR1IF: Timer1 Overflow Interrupt Flag bit <ol> <li>= Timer1 register overflowed (must be cleared in software)</li> <li>= Timer1 has not overflowed</li> </ol>                                                                                                                                                                 |

#### 2.2.2.6 **PCON Register**

The Power Control (PCON) register contains a flag bit to allow differentiation between a Power-on Reset (POR) to an external MCLR Reset or WDT Reset. These devices contain an additional bit to differentiate a Brown-out Reset condition from a Power-on Reset condition.

Note: If the BOREN Configuration bit is set, BOR is '1' on Power-on Reset and reset to '0' when a Brown-out condition occurs. BOR must then be set by the user and checked on subsequent Resets to see if it is clear, indicating that another Brown-out has occurred.

If the BOREN Configuration bit is clear, BOR is unknown on Power-on Reset.

| REGISTER 2-6: PCON: POWER CONTROL REGI | STER |

|----------------------------------------|------|

|----------------------------------------|------|

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-x |

|-------|-----|-----|-----|-----|-----|-------|-------|

| —     | _   | —   | —   | —   | _   | POR   | BOR   |

| bit 7 |     |     |     |     |     |       | bit 0 |

| Legend:           |                  |                                                 |                    |  |  |

|-------------------|------------------|-------------------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | Writable bit U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                            | x = Bit is unknown |  |  |

| bit 7-2 | Unimplemented: Read as '0'                                                                                                                           |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 1   | POR: Power-on Reset Status bit                                                                                                                       |

|         | 1 = No Power-on Reset occurred                                                                                                                       |

|         | 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)                                                                |

| bit 0   | BOR: Brown-out Reset Status bit                                                                                                                      |

|         | <ul> <li>1 = No Brown-out Reset occurred</li> <li>0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)</li> </ul> |

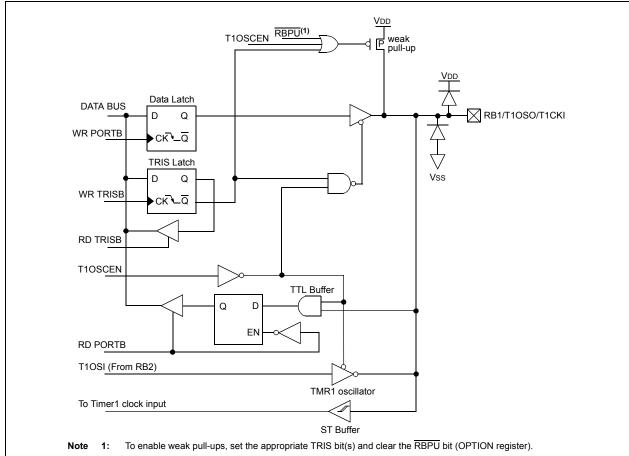

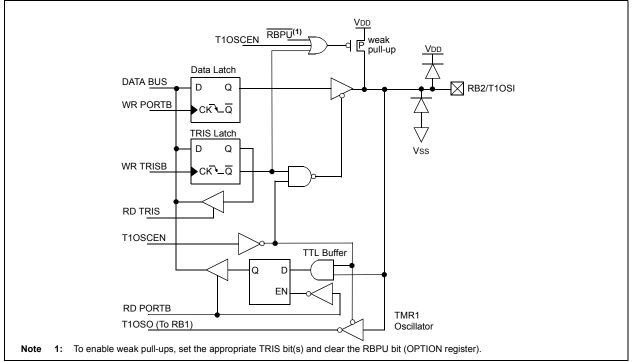

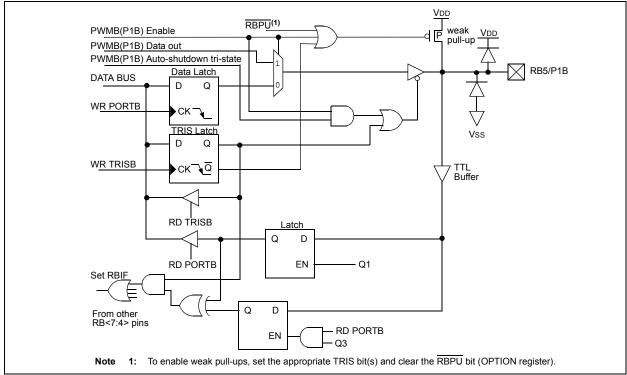

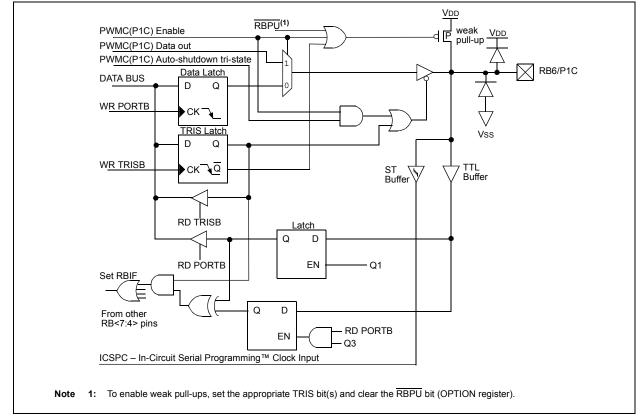

## 3.2 PORTB and the TRISB Register

PORTB is an 8-bit wide bidirectional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

EXAMPLE 3-2: INITIALIZING PORTB

| BCF   | STATUS, | RP0 | ;select Bank 0         |

|-------|---------|-----|------------------------|

| CLRF  | PORTB   |     | ;Initialize PORTB by   |

|       |         |     | ;clearing output       |

|       |         |     | ;data latches          |

| BSF   | STATUS, | RP0 | ;Select Bank 1         |

| MOVLW | 0xCF    |     | ;Value used to         |

|       |         |     | ;initialize data       |

|       |         |     | ;direction             |

| MOVWF | TRISB   |     | ;Set RB<3:0> as inputs |

|       |         |     | ;RB<5:4> as outputs    |

|       |         |     | ;RB<7:6> as inputs     |

|       |         |     |                        |

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU of the OPTION register. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

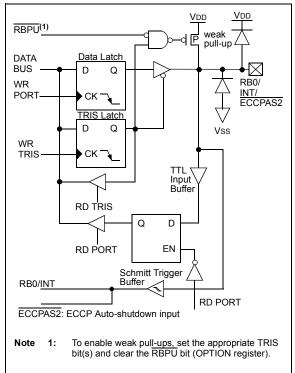

#### FIGURE 3-3: BLOCK DIAGRAM OF RB0/INT/ECCPAS2 PIN

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTB pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modifywrite instructions (such as BSF, BCF, XORWF) with TRISB as the destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

Four of PORTB's pins, RB<7:4>, have an interrupt-onchange feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB<7:4> pin configured as an output is excluded from the interrupton-change comparison). The input pins, RB<7:4>, are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB<7:4> are OR'ed together to generate the RB Port Change Interrupt with flag bit RBIF of the INTCON register.

This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- 1. Perform a read of PORTB to end the mismatch condition.

- 2. Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

NOTES:

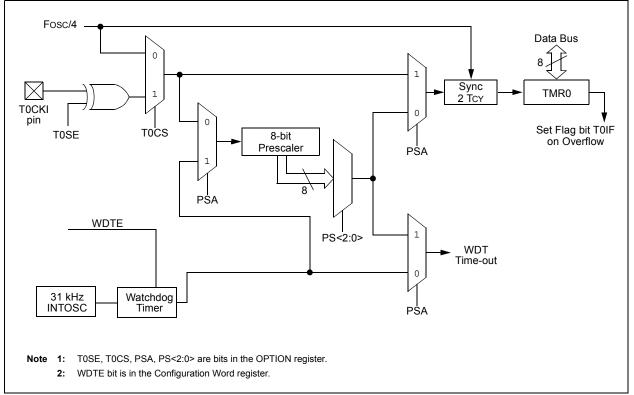

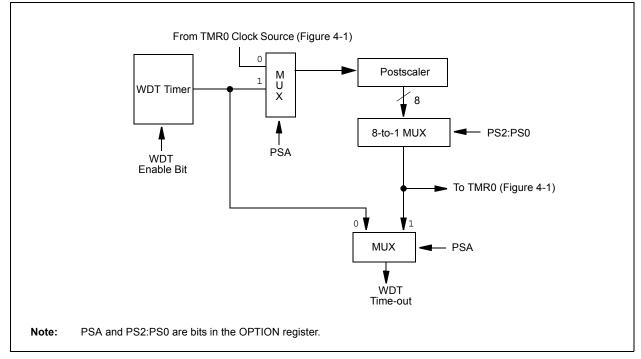

## 4.0 TIMER0 MODULE

The Timer0 module is an 8-bit timer/counter with the following features:

- 8-bit timer/counter register (TMR0)

- 8-bit prescaler (shared with Watchdog Timer)

- Programmable internal or external clock source

- · Programmable external clock edge selection

- · Interrupt on overflow

Figure 4-1 is a block diagram of the Timer0 module.

## 4.1 Timer0 Operation

When used as a timer, the Timer0 module can be used as either an 8-bit timer or an 8-bit counter.

## 4.1.1 8-BIT TIMER MODE

When used as a timer, the Timer0 module will increment every instruction cycle (without prescaler). Timer mode is selected by clearing the T0CS bit of the OPTION register to '0'.

When TMR0 is written, the increment is inhibited for two instruction cycles immediately following the write.

Note: The value written to the TMR0 register can be adjusted, in order to account for the two instruction cycle delay when TMR0 is written.

## 4.1.2 8-BIT COUNTER MODE

When used as a counter, the Timer0 module will increment on every rising or falling edge of the T0CKI pin. The incrementing edge is determined by the T0SE bit of the OPTION register. Counter mode is selected by setting the T0CS bit of the OPTION register to '1'.

## FIGURE 4-1: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

| U-0          | R/W-0                  | R/W-0                                            | R/W-0          | R/W-0             | R/W-0           | R/W-0           | R/W-0   |  |  |  |  |

|--------------|------------------------|--------------------------------------------------|----------------|-------------------|-----------------|-----------------|---------|--|--|--|--|

| _            | TOUTPS3                | TOUTPS2                                          | TOUTPS1        | TOUTPS0           | TMR2ON          | T2CKPS1         | T2CKPS0 |  |  |  |  |

| bit 7        | ·                      |                                                  |                |                   |                 |                 | bit     |  |  |  |  |

|              |                        |                                                  |                |                   |                 |                 |         |  |  |  |  |

| Legend:      |                        |                                                  |                |                   |                 |                 |         |  |  |  |  |

| R = Readab   | ole bit                | W = Writable                                     | bit            | U = Unimplem      | nented bit, rea | d as '0'        |         |  |  |  |  |

| -n = Value a | at POR                 | '1' = Bit is set                                 |                | '0' = Bit is clea | ared            | x = Bit is unkr | nown    |  |  |  |  |

|              |                        |                                                  |                |                   |                 |                 |         |  |  |  |  |

| bit 7        | Unimplemen             | ted: Read as '                                   | 0'             |                   |                 |                 |         |  |  |  |  |

| bit 6-3      | TOUTPS<3:0             | >: Timer2 Out                                    | out Postscaler | Select bits       |                 |                 |         |  |  |  |  |

|              | 0000 <b>= 1:1</b> P    | ostscaler                                        |                |                   |                 |                 |         |  |  |  |  |

|              | 0001 = 1:2 P           | ostscaler                                        |                |                   |                 |                 |         |  |  |  |  |

|              | 0010 = 1:3 P           | 0010 = 1:3 Postscaler                            |                |                   |                 |                 |         |  |  |  |  |

|              |                        | 0011 = 1:4 Postscaler                            |                |                   |                 |                 |         |  |  |  |  |

|              |                        | 0100 = 1:5 Postscaler                            |                |                   |                 |                 |         |  |  |  |  |

|              |                        | 0101 = 1:6 Postscaler                            |                |                   |                 |                 |         |  |  |  |  |

|              | 0110 = 1:7 Postscaler  |                                                  |                |                   |                 |                 |         |  |  |  |  |

|              |                        | 0111 = 1:8 Postscaler                            |                |                   |                 |                 |         |  |  |  |  |

|              |                        | 1000 = 1:9 Postscaler                            |                |                   |                 |                 |         |  |  |  |  |

|              |                        | 1001 = 1:10  Postscaler                          |                |                   |                 |                 |         |  |  |  |  |

|              |                        | 1010 = 1:11 Postscaler<br>1011 = 1:12 Postscaler |                |                   |                 |                 |         |  |  |  |  |

|              |                        | 1011 = 1.12 Postscaler                           |                |                   |                 |                 |         |  |  |  |  |

|              | 1101 = 1:14            |                                                  |                |                   |                 |                 |         |  |  |  |  |

|              |                        | 1110 = 1:15 Postscaler                           |                |                   |                 |                 |         |  |  |  |  |

|              | 1111 = 1:16 Postscaler |                                                  |                |                   |                 |                 |         |  |  |  |  |

| bit 2        | TMR2ON: Tir            | TMR20N: Timer2 On bit                            |                |                   |                 |                 |         |  |  |  |  |

|              | 1 = Timer2 is          | son                                              |                |                   |                 |                 |         |  |  |  |  |

|              | 0 = Timer2 is          | off                                              |                |                   |                 |                 |         |  |  |  |  |

| bit 1-0      |                        | T2CKPS<1:0>: Timer2 Clock Prescale Select bits   |                |                   |                 |                 |         |  |  |  |  |

|              | 00 = Prescale          | er is 1                                          |                |                   |                 |                 |         |  |  |  |  |

|              | 01 = Prescale          |                                                  |                |                   |                 |                 |         |  |  |  |  |

|              | 1x = Prescale          | orio 16                                          |                |                   |                 |                 |         |  |  |  |  |

## REGISTER 6-1: T2CON: TIMER 2 CONTROL REGISTER

## TABLE 6-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER2

| Name    | Bit 7                                           | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |  |

|---------|-------------------------------------------------|---------|---------|---------|---------|--------|---------|---------|----------------------|---------------------------------|--|

| INTCON  | GIE                                             | PEIE    | T0IE    | INTE    | RBIE    | T0IF   | INTF    | RBIF    | x000 0000x           | 0000 000x                       |  |

| PIE1    | —                                               | ADIE    | _       | _       | _       | CCP1IE | TMR2IE  | TMR1IE  | -0000                | -0000                           |  |

| PIR1    | —                                               | ADIF    | _       | _       | _       | CCP1IF | TMR2IF  | TMR1IF  | -0000                | -0000                           |  |

| PR2     | PR2 Timer2 Module Period Register               |         |         |         |         |        |         |         |                      | 1111 1111                       |  |

| TMR2    | R2 Holding Register for the 8-bit TMR2 Register |         |         |         |         |        |         |         | 0000 0000            | 0000 0000                       |  |

| T2CON   | —                                               | TOUTPS3 | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000            | -000 0000                       |  |

| Lananda |                                                 |         |         |         |         |        |         |         |                      |                                 |  |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for Timer2 module.

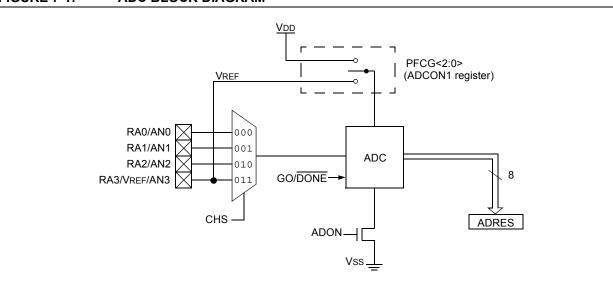

## 7.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

The Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 8-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 8-bit binary result via successive approximation and stores the conversion result into the ADC result register (ADRES).

The ADC voltage reference is software selectable to either VDD or a voltage applied to the external reference pins.

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake-up the device from Sleep.

Figure 7-1 shows the block diagram of the ADC.

## FIGURE 7-1: ADC BLOCK DIAGRAM

## 7.1 ADC Configuration

When configuring and using the ADC the following functions must be considered:

- · Port configuration

- · Channel selection

- · ADC voltage reference selection

- · ADC conversion clock source

- Interrupt control

## 7.1.1 PORT CONFIGURATION

The ADC can be used to convert both analog and digital signals. When converting analog signals, the I/O pin should be configured for analog by setting the associated TRIS and ADCON1 bits. See the corresponding Port section for more information.

| Note: | Analog voltages on any pin that is defined |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|

|       | as a digital input may cause the input     |  |  |  |  |  |  |  |

|       | buffer to conduct excess current.          |  |  |  |  |  |  |  |

## 7.1.2 CHANNEL SELECTION

The CHS bits of the ADCON0 register determine which channel is connected to the sample and hold circuit.

When changing channels, a delay is required before starting the next conversion. Refer to **Section 7.2 "ADC Operation"** for more information.

## 7.1.3 ADC VOLTAGE REFERENCE

The PCFG bits of the ADCON0 register provide independent control of the positive voltage reference. The positive voltage reference can be either VDD or an external voltage source.

## 7.1.4 CONVERSION CLOCK

The source of the conversion clock is software selectable via the ADCS bits of the ADCON0 register. There are four possible clock options:

- Fosc/2

- Fosc/8

- Fosc/32

- FRC (dedicated internal oscillator)

The time to complete one bit conversion is defined as TAD. One full 8-bit conversion requires 9.5 TAD periods.

For correct conversion, the appropriate TAD specification must be met. See A/D conversion requirements in **Section 12.0 "Electrical Characteristics"** for more information. Table 7-1 gives examples of appropriate ADC clock selections.

Note: Unless using the FRC, any changes in the system clock frequency will change the ADC clock frequency, which may adversely affect the ADC result.

## TABLE 7-1: TAD vs. DEVICE OPERATING FREQUENCIES

| AD Clock  | Source (TAD) | Device Frequency           |                            |                            |                       |  |  |  |  |

|-----------|--------------|----------------------------|----------------------------|----------------------------|-----------------------|--|--|--|--|

| Operation | ADCS<1:0>    | 20 MHz                     | 5 MHz                      | 1.25 MHz                   | 333.33 kHz            |  |  |  |  |

| 2 Tosc    | 0 0          | 100 ns <sup>(2)</sup>      | 400 ns <sup>(2)</sup>      | 1.6 μs                     | 6 µs                  |  |  |  |  |

| 8 Tosc    | 01           | 400 ns <sup>(2)</sup>      | 1.6 μs                     | 6.4 μs                     | 24 μs <sup>(3)</sup>  |  |  |  |  |

| 32 Tosc   | 10           | 1.6 μs                     | 6.4 μs                     | 25.6 μs <sup>(3)</sup>     | 96 μs <sup>(3)</sup>  |  |  |  |  |

| RC        | 11           | 2-6 μs <sup>(1), (4)</sup> | 2-6 μs <sup>(1), (4)</sup> | 2-6 μs <sup>(1), (4)</sup> | 2-6 μs <sup>(1)</sup> |  |  |  |  |

Legend: Shaded cells are outside of recommended range.

Note 1: The RC source has a typical TAD time of 4  $\mu$ s.

2: These values violate the minimum required TAD time.

3: For faster conversion times, the selection of another clock source is recommended.

4: When device frequency is greater than 1 MHz, the RC A/D conversion clock source is recommended for Sleep operation only.

## 7.2.7 ADC REGISTER DEFINITIONS

The following registers are used to control the operation of the ADC.

#### REGISTER 7-1: ADCON0: A/D CONTROL REGISTER 0

| R/W-0         | R/W-0                                                                                                                                                                                                                                                                                                 | R/W-0                                                                                       | R/W-0 | R/W-0            | R/W-0            | U-0            | R/W-0 |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------|------------------|------------------|----------------|-------|--|

| ADCS1         | ADCS0                                                                                                                                                                                                                                                                                                 | CHS2                                                                                        | CHS1  | CHS0             | GO/DONE          | _              | ADON  |  |

| bit 7         | 1.2000                                                                                                                                                                                                                                                                                                | 0.102                                                                                       | 0.101 | 0                | 00/20/12         |                | bit C |  |

|               |                                                                                                                                                                                                                                                                                                       |                                                                                             |       |                  |                  |                |       |  |

| Legend:       |                                                                                                                                                                                                                                                                                                       |                                                                                             |       |                  |                  |                |       |  |

| R = Readable  | e bit                                                                                                                                                                                                                                                                                                 | W = Writable                                                                                | bit   | U = Unimple      | mented bit, read | d as '0'       |       |  |

| -n = Value at | POR                                                                                                                                                                                                                                                                                                   | '1' = Bit is set                                                                            |       | '0' = Bit is cle | eared            | x = Bit is unk | nown  |  |

| bit 7-6       | 00 = Fosc/2<br>01 = Fosc/8<br>10 = Fosc/32                                                                                                                                                                                                                                                            | A/D Conversion                                                                              |       |                  | ator)            |                |       |  |

| bit 5-3       | 000 = AN0<br>001 = AN1<br>010 = AN2<br>011 = AN3<br>100 = Reser<br>101 = Reser<br>110 = Reser                                                                                                                                                                                                         | ved, do not use<br>ved, do not use<br>ved, do not use<br>ved, do not use<br>ved, do not use |       |                  |                  |                |       |  |

| bit 2         | <ul> <li>GO/DONE: A/D Conversion Status bit</li> <li>1 = A/D conversion cycle in progress. Setting this bit starts an A/D conversion cycle.<br/>This bit is automatically cleared by hardware when the A/D conversion has completed.</li> <li>0 = A/D conversion completed/not in progress</li> </ul> |                                                                                             |       |                  |                  |                |       |  |

| bit 1         | Unimplemer                                                                                                                                                                                                                                                                                            | ted: Read as '                                                                              | 0'    |                  |                  |                |       |  |

| bit 0         | ADON: ADC Enable bit<br>1 = ADC is enabled<br>0 = ADC is disabled and consumes no operating current                                                                                                                                                                                                   |                                                                                             |       |                  |                  |                |       |  |

| Name    | Bit 7                                                                          | Bit 6          | Bit 5          | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|--------------------------------------------------------------------------------|----------------|----------------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| CCPR1L  | Capture/Cor                                                                    | mpare/PWM F    | Register 1 (LS | iB)    |        |        |        |        | XXXX XXXX            | xxxx xxxx                       |

| CCPR1H  | CPR1H Capture/Compare/PWM Register 1 (MSB)                                     |                |                |        |        |        |        |        | XXXX XXXX            | xxxx xxxx                       |

| CCP1CON | P1M1                                                                           | P1M0           | DC1B1          | DC1B0  | CCP1M3 | CCP1M2 | CCP1M1 | CCP1M0 | 0000 0000            | 0000 0000                       |

| INTCON  | GIE                                                                            | PEIE           | T0IE           | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| PIE1    | _                                                                              | ADIE           | _              | _      | _      | CCP1IE | TMR2IE | TMR1IE | -0000                | -0000                           |

| PIR1    | _                                                                              | ADIF           | _              | _      | _      | CCP1IF | TMR2IF | TMR1IF | -0000                | -0000                           |

| PR2     | PR2 Timer2 Period Register                                                     |                |                |        |        |        |        |        |                      | 1111 1111                       |

| TMR1L   | 1L Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |                |                |        |        |        |        |        | xxxx xxxx            | xxxx xxxx                       |

| TMR1H   | H Holding Register for the Most Significant Byte of the 16-bit TMR1 Register   |                |                |        |        |        |        |        | xxxx xxxx            | xxxx xxxx                       |

| TMR2    | Timer2 mod                                                                     | ule's register |                |        |        |        |        |        | 0000 0000            | 0000 0000                       |

| TRISB   | TRISB7                                                                         | TRISB6         | TRISB5         | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 1111 1111            | 1111 1111                       |

TABLE 8-2: REGISTERS ASSOCIATED WITH CAPTURE

Legend: -= Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the Capture.

## 9.12 Watchdog Timer (WDT)

The Watchdog Timer is a free running, on-chip, RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run, even if the clock on the OSC1/CLKIN and OSC2/CLKOUT pins of the device have been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT time-out generates a device Reset (Watchdog Timer Reset). If the device is in Sleep mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The TO bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

The WDT can be permanently disabled by clearing Configuration bit WDTE (Section 9.1 "Configuration Bits").

WDT time-out period values may be found in the Electrical Specifications section under TWDT (parameter #31). Values for the WDT prescaler (actually a postscaler, but shared with the Timer0 prescaler) may be assigned using the OPTION register.

**Note:** The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device Reset condition.

**Note:** When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared, but the prescaler assignment is not changed.

## FIGURE 9-14: WATCHDOG TIMER BLOCK DIAGRAM

## TABLE 9-7: SUMMARY OF REGISTERS ASSOCIATED WITH WATCHDOG TIMER

| Name                   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|------------------------|-------|--------|-------|-------|-------|-------|-------|-------|----------------------|---------------------------------|

| CONFIG1 <sup>(1)</sup> | BORV  | BOREN  |       | _     | PWRTE | WDTE  | FOSC1 | FOSC0 | _                    | _                               |

| OPTION_REG             | RBPU  | INTEDG | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111            | 1111 1111                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used the Watchdog Timer.

**Note 1:** See Configuration Word Register (Register 9-1) for operation of all register bits.

## 9.13 Power-down Mode (Sleep)

Power-Down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the  $\overline{PD}$  bit of the STATUS register is cleared, the  $\overline{TO}$  of the STATUS register bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before the SLEEP instruction was executed (driving high, low or high-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD or Vss, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D and the disable external clocks. Pull all I/O pins that are high-impedance inputs, high or low externally, to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or Vss for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The  $\overline{\text{MCLR}}$  pin must be at a logic high level (parameter D042).

#### 9.13.1 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on  $\overline{\text{MCLR}}$  pin.

- 2. Watchdog Timer Wake-up (if WDT was enabled).

- 3. Interrupt from INT pin, RB port change or some peripheral interrupts.

External MCLR Reset will cause a device Reset. All other events are considered a continuation of program execution and cause a "wake-up". The TO and PD bits in the STATUS register can be used to determine the cause of device Reset. The PD bit, which is set on power-up, is cleared when Sleep is invoked. The TO bit is cleared if a WDT time-out occurred (and caused wake-up).

The following peripheral interrupts can wake the device from Sleep:

- 1. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 2. ECCP capture mode interrupt.

- 3. ADC running in ADRC mode.

Other peripherals cannot generate interrupts, since during Sleep, no on-chip clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

## 9.13.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs before the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs **during or after** the execution of a SLEEP instruction, the device will immediately wake-up from Sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

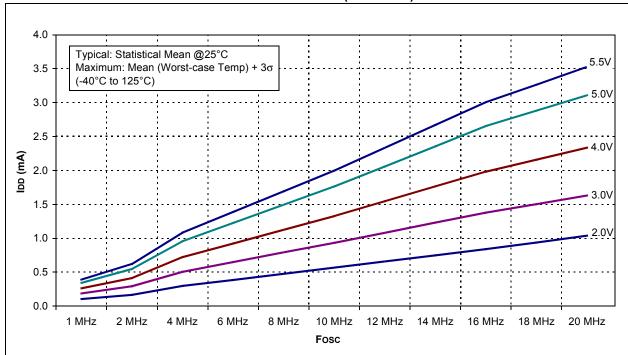

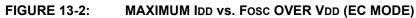

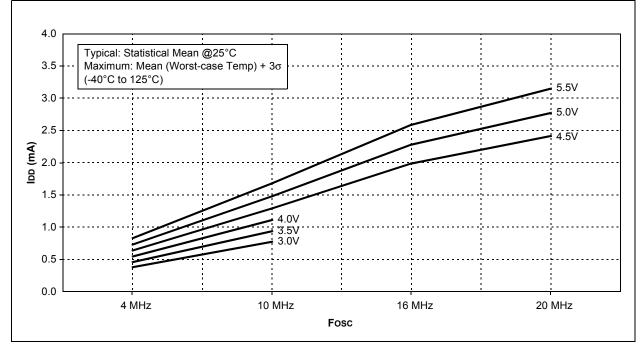

| DC CHARACTERISTICS |     |                           | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |      |       |     |                              |  |

|--------------------|-----|---------------------------|-----------------------------------------------------------------------------------------------------------------------|------|------|-------|-----|------------------------------|--|

| Param<br>No.       | Sym | Characteristic            | Min                                                                                                                   | Тур† | Max  | Units | Vdd | Conditions                   |  |

|                    | Vdd | Supply Voltage            |                                                                                                                       |      |      |       |     |                              |  |

| D001               |     |                           | 3.0                                                                                                                   | —    | 5.5  | V     | —   |                              |  |

|                    | Idd | Supply Current            | •                                                                                                                     | •    | •    |       |     |                              |  |

| D010E              |     |                           |                                                                                                                       | 21   | 28   | μΑ    | 3.0 | Fosc = 32 kHz                |  |

| DUIUE              |     |                           |                                                                                                                       | 38   | 63.7 | μΑ    | 5.0 | LP Oscillator mode           |  |

|                    |     |                           | —                                                                                                                     | 182  | 250  | μΑ    | 3.0 | Fosc = 1 MHz                 |  |

| D011E              |     |                           | _                                                                                                                     | 293  | 370  | μΑ    | 5.0 | XT Oscillator mode           |  |

|                    |     |                           | —                                                                                                                     | 371  | 470  | μΑ    | 3.0 | Fosc = 4 MHz                 |  |

| D012E              |     |                           | _                                                                                                                     | 668  | 780  | μΑ    | 5.0 | XT Oscillator mode           |  |

|                    |     |                           | _                                                                                                                     | 2.6  | 2.9  | mA    | 4.5 | Fosc = 20 MHz                |  |

| D013E              |     |                           | _                                                                                                                     | 3    | 3.3  | mA    | 5.0 | HS Oscillator mode           |  |

|                    | IPD | Power-down Base Current   |                                                                                                                       | L    |      |       |     | •                            |  |

| D020E              |     |                           |                                                                                                                       | 0.1  | 11   | μΑ    | 3.0 | WDT, BOR and T1OSC: disabled |  |

| DUZUE              |     |                           | _                                                                                                                     | 0.2  | 15   | μA    | 5.0 |                              |  |

|                    |     | Peripheral Module Current | 1)                                                                                                                    | •    |      |       |     | •                            |  |

| D021E              |     |                           | —                                                                                                                     | 2    | 19   | μΑ    | 3.0 | WDT Current                  |  |

| DUZIE              |     |                           | _                                                                                                                     | 9    | 22   | μΑ    | 5.0 |                              |  |

|                    |     |                           | —                                                                                                                     | 37   | 60   | μA    | 3.0 |                              |  |

| D022E              |     |                           |                                                                                                                       | 40   | 71   | μΑ    | 4.5 | BOR Current                  |  |

|                    |     |                           |                                                                                                                       | 45   | 76   | μA    | 5.0 | 1                            |  |

|                    |     |                           |                                                                                                                       | 2.6  | 20   | μA    | 3.0 | T1osc Current                |  |

| D025E              |     |                           | —                                                                                                                     | 3.0  | 25   | μA    | 5.0 | 1                            |  |

## 12.3 DC Characteristics: PIC16F716 (Extended)

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral "Δ" current can be determined by subtracting the base IDD or IPD current from this limit.

| Param<br>No. | Sym   | Characteristic                            | Min | Тур† | Мах    | Units | Conditions          |

|--------------|-------|-------------------------------------------|-----|------|--------|-------|---------------------|

| 1A           | Fosc  | Ext. Clock Input Frequency <sup>(1)</sup> | DC  |      | 4      | MHz   | RC and XT Osc modes |

|              |       |                                           | DC  | —    | 20     | MHz   | HS Osc mode         |

|              |       |                                           | DC  | —    | 200    | kHz   | LP Osc mode         |

|              |       | Oscillator Frequency <sup>(1)</sup>       | DC  |      | 4      | MHz   | RC Osc mode         |

|              |       |                                           | 0.1 | —    | 4      | MHz   | XT Osc mode         |

|              |       |                                           | 4   | —    | 20     | MHz   | HS Osc mode         |

|              |       |                                           | 5   |      | 200    | kHz   | LP Osc mode         |

| 1            | Tosc  | External CLKIN Period <sup>(1)</sup>      | 250 |      | _      | ns    | RC and XT Osc modes |

|              |       |                                           | 50  | —    | —      | ns    | HS Osc mode         |

|              |       |                                           | 5   |      | _      | μs    | LP Osc mode         |

|              |       | Oscillator Period <sup>(1)</sup>          | 250 |      | _      | ns    | RC Osc mode         |

|              |       |                                           | 250 | —    | 10,000 | ns    | XT Osc mode         |

|              |       |                                           | 50  | —    | 250    | ns    | HS Osc mode         |

|              |       |                                           | 5   | _    | _      | μs    | LP Osc mode         |

| 2            | Тсу   | Instruction Cycle Time <sup>(1)</sup>     | 200 | _    | DC     | ns    | Tcy = 4/Fosc        |

| 3*           | TosL, | External Clock in (OSC1) High or          | 100 | —    | —      | ns    | XT oscillator       |

|              | TosH  | Low Time                                  | 2.5 | —    | —      | μs    | LP oscillator       |

|              |       |                                           | 15  | —    | _      | ns    | HS oscillator       |

| 4*           | TosR, | External Clock in (OSC1) Rise or          | —   | —    | 25     | ns    | XT oscillator       |

|              | TosF  | Fall Time                                 | —   | —    | 50     | ns    | LP oscillator       |

|              |       |                                           | _   | _    | 15     | ns    | HS oscillator       |

|  | <b>TABLE 12-2</b> : | EXTERNAL CLOCK TIMING REQUIREMENTS |

|--|---------------------|------------------------------------|

|--|---------------------|------------------------------------|

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Instruction cycle period (TcY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to the OSC1/CLKIN pin.

When an external clock input is used, the "Max" cycle time limit is "DC" (no clock) for all devices.

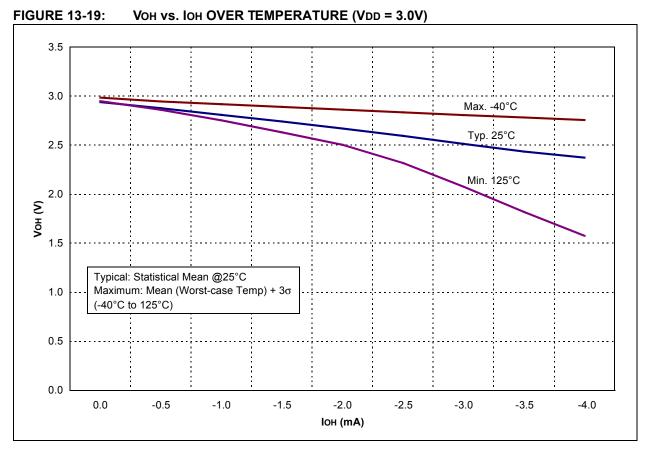

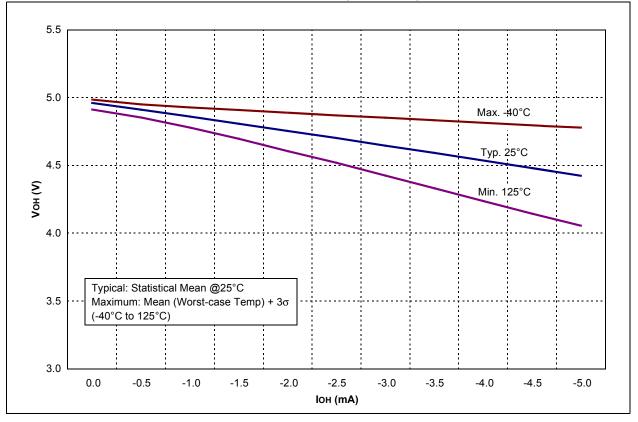

FIGURE 13-20: VOH vs. IOH OVER TEMPERATURE (VDD = 5.0V)

© 2007 Microchip Technology Inc.

## 14.2 Package Details

The following sections give the technical details of the packages.

## 18-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units         |      | INCHES   |      |

|----------------------------|---------------|------|----------|------|

| Dime                       | ension Limits | MIN  | NOM      | MAX  |

| Number of Pins             | Ν             |      | 18       |      |

| Pitch                      | е             |      | .100 BSC |      |

| Top to Seating Plane       | А             | -    | -        | .210 |

| Molded Package Thickness   | A2            | .115 | .130     | .195 |

| Base to Seating Plane      | A1            | .015 | -        | -    |

| Shoulder to Shoulder Width | E             | .300 | .310     | .325 |

| Molded Package Width       | E1            | .240 | .250     | .280 |

| Overall Length             | D             | .880 | .900     | .920 |

| Tip to Seating Plane       | L             | .115 | .130     | .150 |

| Lead Thickness             | С             | .008 | .010     | .014 |

| Upper Lead Width           | b1            | .045 | .060     | .070 |

| Lower Lead Width           | b             | .014 | .018     | .022 |

| Overall Row Spacing §      | eB            | -    | -        | .430 |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-007B