Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                               |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | 56800E                                                               |

| Core Size                  | 16-Bit                                                               |

| Speed                      | 60MHz                                                                |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI                           |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 54                                                                   |

| Program Memory Size        | 48KB (24K x 16)                                                      |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 4K x 16                                                              |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                            |

| Data Converters            | A/D 16x12b; D/A 1x12b                                                |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                        |

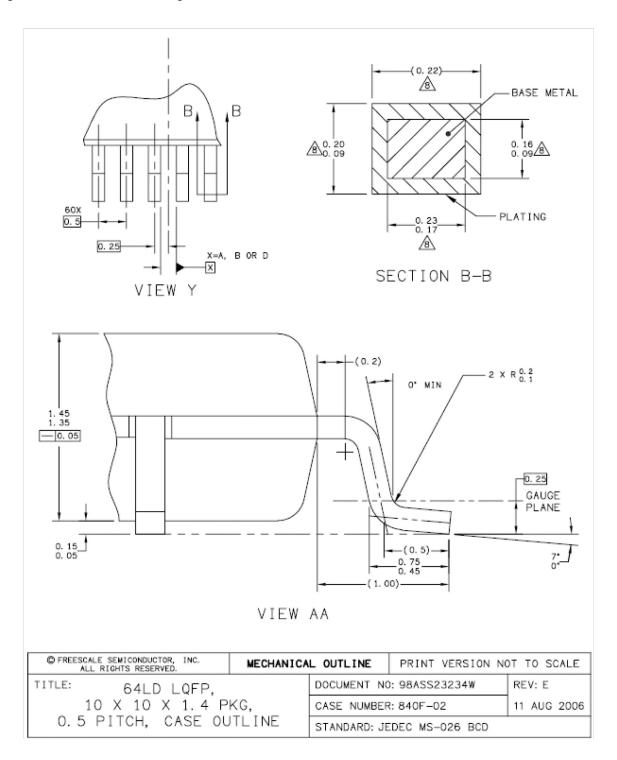

| Package / Case             | 64-LQFP                                                              |

| Supplier Device Package    | 64-LQFP (10x10)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc56f8247vlh |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.4 Product Documentation

The documents listed in Table 2 are required for a complete description and proper design with the MC56F825x/MC56F824x. Documentation is available from local Freescale distributors, Freescale Semiconductor sales offices, Freescale Literature Distribution Centers, or online at http://www.freescale.com.

| Торіс                                        | Description                                                                                                                      | Order Number |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------|

| DSP56800E Reference Manual                   | Detailed description of the 56800E family architecture, 16-bit digital signal controller core processor, and the instruction set | DSP56800ERM  |

| MC56F825x Reference Manual                   | Detailed description of peripherals of the MC56F825x/MC56F824x devices                                                           | MC56F825XRM  |

| MC56F824x/5x Serial Bootloader<br>User Guide | Detailed description of the Serial Bootloader in the 56F800x family of devices                                                   | TBD          |

| MC56F825x Technical Data Sheet               | Electrical and timing specifications, pin descriptions, and package descriptions (this document)                                 | MC56F825X    |

| MC56F825x Errata                             | Detailed description of any chip issues that might be present                                                                    | MC56F825XE   |

### Table 2. MC56F825x/MC56F824x Device Documentation

# 3 Signal/Connection Descriptions

# 3.1 Introduction

The input and output signals of the MC56F825x/MC56F824x are organized into functional groups, as detailed in Table 3.

| Functional Group                                                                                  | Number of Pins<br>in 44 LQFP | Number of Pins<br>in 48 LQFP | Number of Pins<br>in 64 LQFP |

|---------------------------------------------------------------------------------------------------|------------------------------|------------------------------|------------------------------|

| Power inputs (V <sub>DD</sub> , V <sub>DDA</sub> , V <sub>CAP</sub> )                             | 5                            | 5                            | 6                            |

| Ground (V <sub>SS</sub> , V <sub>SSA</sub> )                                                      | 4                            | 4                            | 4                            |

| Reset <sup>1</sup>                                                                                | 1                            | 1                            | 1                            |

| Enhanced Flex Pulse Width Modulator (eFlexPWM) ports <sup>1</sup>                                 | 6                            | 6                            | 9                            |

| Queued Serial Peripheral Interface (SPI) ports <sup>1</sup>                                       | 4                            | 4                            | 4                            |

| Queued Serial Communications Interface 0&1 (QSCI0 & QSCI1) ports <sup>1</sup>                     | 6                            | 6                            | 9                            |

| Inter-Integrated Circuit Interface 0&1 (I <sup>2</sup> C0 & I <sup>2</sup> C0) ports <sup>1</sup> | 4                            | 4                            | 6                            |

| Analog-to-Digital Converter (ADC) inputs <sup>1</sup>                                             | 8                            | 10                           | 16                           |

| High Speed Analog Comparator inputs/outputs <sup>1</sup>                                          | 11                           | 12                           | 15                           |

| 12-bit Digital-to-Analog Converter (DAC_12B) output                                               | 1                            | 1                            | 1                            |

| Quad Timer Module (TMRA & TMRB) ports <sup>1</sup>                                                | 5                            | 5                            | 8                            |

| Freescale's Scalable Controller-Area-Network (MSCAN) <sup>1, 2</sup>                              | 2                            | 2                            | 2                            |

| Inter-Module Cross Bar package inputs/outputs1                                                    | 10                           | 12                           | 17                           |

| Clock <sup>1</sup>                                                                                | 3                            | 4                            | 4                            |

| JTAG/Enhanced On-Chip Emulation (EOnCE) <sup>1</sup>                                              | 4                            | 4                            | 4                            |

### Table 3. Functional Group Pin Allocations

| Pin Number |            | ber        |                                | Peripherals |                  |      |               |                        |                 |           |         |               |              |                  |      |       |

|------------|------------|------------|--------------------------------|-------------|------------------|------|---------------|------------------------|-----------------|-----------|---------|---------------|--------------|------------------|------|-------|

| 44<br>LQFP | 48<br>LQFP | 64<br>LQFP | Pin Name                       | GPIO        | l <sup>2</sup> C | SCI  | SPI           | MS<br>CAN <sup>1</sup> | ADC             | Cross Bar | СОМР    | Quad<br>Timer | eFlex<br>PWM | Power            | JTAG | Misc. |

| 19         | 21         | 28         | GPIOB3/<br>ANB3&VREFLB&CMPC_M0 | GPIOB3      |                  |      |               |                        | ANB3&<br>VREFLB |           | CMPC_M0 |               |              |                  |      |       |

|            |            | 29         | V <sub>DD</sub>                |             |                  |      |               |                        |                 |           |         |               |              | V <sub>DD</sub>  |      |       |

| 20         | 22         | 30         | V <sub>SS</sub>                |             |                  |      |               |                        |                 |           |         |               |              | V <sub>SS</sub>  |      |       |

| 21         | 23         | 31         | GPIOC6/TA2/XB_IN3/<br>CMP_REF  | GPIOC6      |                  |      |               |                        |                 | XB_IN3    | CMP_REF | TA2           |              |                  |      |       |

| 22         | 24         | 32         | GPIOC7/SS/TXD0                 | GPIOC7      |                  | TXD0 | SS            |                        |                 |           |         |               |              |                  |      |       |

| 23         | 25         | 33         | GPIOC8/MISO/RXD0               | GPIOC8      |                  | RXD0 | MISO          |                        |                 |           |         |               |              |                  |      |       |

| 24         | 26         | 34         | GPIOC9/SCLK/XB_IN4             | GPIOC9      |                  |      | SCLK          |                        |                 | XB_IN4    |         |               |              |                  |      |       |

| 25         | 27         | 35         | GPIOC10/MOSI/XB_IN5/MISO       | GPIOC10     |                  |      | MOSI/<br>MISO |                        |                 | XB_IN5    |         |               |              |                  |      |       |

|            | 28         | 36         | GPIOF0/XB_IN6                  | GPIOF0      |                  |      |               |                        |                 | XB_IN6    |         |               |              |                  |      |       |

| 26         | 29         | 37         | GPIOC11/CANTX/SCL1/TXD1        | GPIOC11     | SCL1             | TXD1 |               | CANTX                  |                 |           |         |               |              |                  |      |       |

| 27         | 30         | 38         | GPIOC12/CANRX/SDA1/RXD1        | GPIOC12     | SDA1             | RXD1 |               | CANRX                  |                 |           |         |               |              |                  |      |       |

|            |            | 39         | GPIOF2/SCL1/XB_OUT2            | GPIOF2      | SCL1             |      |               |                        |                 | XB_OUT2   |         |               |              |                  |      |       |

|            |            | 40         | GPIOF3/SDA1/XB_OUT3            | GPIOF3      | SDA1             |      |               |                        |                 | XB_OUT3   |         |               |              |                  |      |       |

|            |            | 41         | GPIOF4/TXD1/XB_OUT4            | GPIOF4      |                  | TXD1 |               |                        |                 | XB_OUT4   |         |               |              |                  |      |       |

|            |            | 42         | GPIOF5/RXD1/XB_OUT5            | GPIOF5      |                  | RXD1 |               |                        |                 | XB_OUT5   |         |               |              |                  |      |       |

| 28         | 31         | 43         | V <sub>SS</sub>                |             |                  |      |               |                        |                 |           |         |               |              | V <sub>SS</sub>  |      |       |

| 29         | 32         | 44         | V <sub>DD</sub>                |             |                  |      |               |                        |                 |           |         |               |              | V <sub>DD</sub>  |      |       |

| 30         | 33         | 45         | GPIOE0/PWM0B                   | GPIOE0      |                  |      |               |                        |                 |           |         |               | PWM0B        |                  |      |       |

| 31         | 34         | 46         | GPIOE1/PWM0A                   | GPIOE1      |                  |      |               |                        |                 |           |         |               | PWM0A        |                  |      |       |

| 32         | 35         | 47         | GPIOE2/PWM1B                   | GPIOE2      |                  |      |               |                        |                 |           |         |               | PWM1B        |                  |      |       |

| 33         | 36         | 48         | GPIOE3/PWM1A                   | GPIOE3      |                  |      |               |                        |                 |           |         |               | PWM1A        |                  |      |       |

| 34         | 37         | 49         | GPIOC13/TA3/XB_IN6             | GPIOC13     |                  |      |               |                        |                 | XB_IN6    |         | TA3           |              |                  |      |       |

|            | 38         | 50         | GPIOF1/CLKO/XB_IN7             | GPIOF1      |                  |      |               |                        |                 | XB_IN7    |         |               |              |                  |      | CLKO  |

| 35         | 39         | 51         | GPIOE4/PWM2B/XB_IN2            | GPIOE4      |                  |      |               |                        |                 | XB_IN2    |         |               | PWM2B        |                  |      |       |

| 36         | 40         | 52         | GPIOE5/PWM2A/XB_IN3            | GPIOE5      |                  |      |               |                        |                 | XB_IN3    |         |               | PWM2A        |                  |      |       |

|            |            | 53         | GPIOE6/PWM3B/XB_IN4            | GPIOE6      |                  |      |               |                        |                 | XB_IN4    |         |               | PWM3B        |                  |      |       |

|            |            | 54         | GPIOE7/PWM3A/XB_IN5            | GPIOE7      |                  |      |               |                        |                 | XB_IN5    |         |               | <i>РWM3A</i> |                  |      |       |

| 37         | 41         | 55         | GPIOC14/SDA0/XB_OUT0           | GPIOC14     | SDA0             |      |               |                        |                 | XB_OUT0   |         |               |              |                  |      |       |

| 38         | 42         | 56         | GPIOC15/SCL0/XB_OUT1           | GPIOC15     | SCL0             |      |               |                        |                 | XB_OUT1   |         |               |              |                  |      |       |

| 39         | 43         | 57         | V <sub>CAP</sub>               |             |                  |      |               |                        |                 |           |         |               |              | V <sub>CAP</sub> |      |       |

|            |            | 58         | GPIOF6/TB2/PWM3X               | GPIOF6      |                  |      |               |                        |                 |           |         | TB2           | РWM3X        |                  |      |       |

|            |            | 59         | GPIOF7/TB3                     | GPIOF7      |                  |      |               |                        |                 |           |         | ТВ3           |              |                  |      |       |

| 40         | 44         | 60         | V <sub>DD</sub>                |             |                  |      |               |                        |                 |           |         |               |              | V <sub>DD</sub>  |      |       |

### Table 4. MC56F825x/MC56F824x Pins (continued)

Signal/Connection Descriptions

## 3.3 MC56F825x/MC56F824x Signal Pins

After reset, each pin is configured for its primary function (listed first). Any alternative functionality, shown in parentheses and as *italic*, must be programmed via the GPIO module's peripheral enable registers (GPIO\_x\_PER) and the SIM module's GPIO peripheral select (GPSx) registers.

| Signal<br>Name   | 44<br>LQFP | 48<br>LQFP | 64<br>LQFP | Туре             | State<br>During<br>Reset                | Signal Description                                                                                                                                                                                                                             |

|------------------|------------|------------|------------|------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub>  |            |            | 29         | Supply           | Supply                                  | I/O Power — This pin supplies 3.3 V power to the chip I/O interface.                                                                                                                                                                           |

| V <sub>DD</sub>  | 29         | 32         | 44         |                  |                                         |                                                                                                                                                                                                                                                |

| V <sub>DD</sub>  | 40         | 44         | 60         |                  |                                         |                                                                                                                                                                                                                                                |

| V <sub>SS</sub>  | 20         | 22         | 30         | Supply           | Supply                                  | I/O Ground — These pins provide ground for chip I/O interface.                                                                                                                                                                                 |

| V <sub>SS</sub>  | 28         | 31         | 43         |                  |                                         |                                                                                                                                                                                                                                                |

| V <sub>SS</sub>  | 41         | 45         | 61         |                  |                                         |                                                                                                                                                                                                                                                |

| V <sub>DDA</sub> | 13         | 15         | 22         | Supply           | Supply                                  | Analog Power — This pin supplies 3.3 V power to the analog modules. It must be connected to a clean analog power supply.                                                                                                                       |

| V <sub>SSA</sub> | 14         | 16         | 23         | Supply           | Supply                                  | Analog Ground — This pin supplies an analog ground to the analog modules. It must be connected to a clean power supply.                                                                                                                        |

| V <sub>CAP</sub> | 17         | 19         | 26         | Supply           | Supply                                  | $V_{CAP}$ — Connect a bypass capacitor of 2.2 $\mu$ F or greater between                                                                                                                                                                       |

| V <sub>CAP</sub> | 39         | 43         | 57         |                  |                                         | this pin and $V_{SS}$ to stabilize the core voltage regulator output required for proper device operation. See Section 8.2, "Electrical Design Considerations," on page 73.                                                                    |

| TDI              | 44         | 48         | 64         | Input            | Input,<br>internal<br>pullup<br>enabled | Test Data Input — This input pin provides a serial input data stream to the JTAG/EOnCE port. It is sampled on the rising edge of TCK and has an on-chip pullup resistor.                                                                       |

| (GPIOD0)         |            |            |            | Input/<br>Output |                                         | Port D GPIO — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                                          |

|                  |            |            |            |                  |                                         | After reset, the default state is TDI.                                                                                                                                                                                                         |

| TDO              | 42         | 46         | 62         | Output           | Output                                  | Test Data Output — This tri-stateable output pin provides a serial output data stream from the JTAG/EOnCE port. It is driven in the shift-IR and shift-DR controller states, and changes on the falling edge of TCK.                           |

| (GPIOD1)         |            |            |            | Input/<br>Output |                                         | Port D GPIO — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                                          |

|                  |            |            |            |                  |                                         | After reset, the default state is TDO.                                                                                                                                                                                                         |

| ТСК              | 1          | 1          | 1          | Input            | Input,<br>internal<br>pullup<br>enabled | Test Clock Input — This input pin provides a gated clock to synchronize the test logic and shift serial data to the JTAG/EOnCE port. The pin is connected internally to a pullup resistor. A Schmitt-trigger input is used for noise immunity. |

| (GPIOD2)         |            |            |            | Input/<br>Output |                                         | Port D GPIO — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                                          |

|                  |            |            |            |                  |                                         | After reset, the default state is TCK                                                                                                                                                                                                          |

Table 5. MC56F825x/MC56F824x Signal and Package Information

### Signal/Connection Descriptions

### Table 5. MC56F825x/MC56F824x Signal and Package Information (continued)

| Signal<br>Name | 44<br>LQFP | 48<br>LQFP | 64<br>LQFP | Туре             | State<br>During<br>Reset     | Signal Description                                                                                                                                                    |

|----------------|------------|------------|------------|------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIOC2         | 5          | 5          | 5          | Input/<br>Output | Input,<br>internal<br>pullup | Port C GPIO — This GPIO pin can be individually programmed as an input or output pin.                                                                                 |

| (TXD0)         |            |            |            | Output           | enabled                      | TXD0 — The SCI0 transmit data output or transmit/receive in single wire operation.                                                                                    |

| <i>(TB0)</i>   |            |            |            | Input/<br>Output |                              | TB0 — Quad timer module B channel 0 input/output.                                                                                                                     |

| (XB_IN2)       |            |            |            | Input            |                              | XB_IN2 — Crossbar module input 2                                                                                                                                      |

| (CLKO)         |            |            |            | Output           |                              | CLKO — This is a buffered clock output; the clock source is selected<br>by clockout select (CLKOSEL) bits in the clock output select register<br>(CLKOUT) of the SIM. |

|                |            |            |            |                  |                              | After reset, the default state is GPIOC2.                                                                                                                             |

| GPIOC3         | 6          | 6          | 7          | Input/<br>Output | Input,<br>internal<br>pullup | Port C GPIO — This GPIO pin can be individually programmed as an input or output pin.                                                                                 |

| (TA0)          |            |            |            | Input/<br>Output | enabled                      | TA0 — Quad timer module A channel 0 input/output.                                                                                                                     |

| (CMPA_O)       |            |            |            | Output           |                              | CMPA_O— Analog comparator A output                                                                                                                                    |

| (RXD0)         |            |            |            | Input            |                              | RXD0 — The SCI0 receive data input.                                                                                                                                   |

|                |            |            |            |                  |                              | After reset, the default state is GPIOC3.                                                                                                                             |

| GPIOC4         | 7          | 7          | 8          | Input/<br>Output | Input,<br>internal<br>pullup | Port C GPIO — This GPIO pin can be individually programmed as an input or output pin.                                                                                 |

| (TA1)          |            |            |            | Input/<br>Output | enabled                      | TA1 — Quad timer module A channel 1input/output                                                                                                                       |

| (CMPB_O)       |            |            |            | Output           |                              | CMPB_O — Analog comparator B output                                                                                                                                   |

|                |            |            |            |                  |                              | After reset, the default state is GPIOC4.                                                                                                                             |

| GPIOC5         | 12         | 13         | 18         | Input/<br>Output | Input,<br>internal<br>pullup | Port C GPIO — This GPIO pin can be individually programmed as an input or output pin.                                                                                 |

| (DACO)         |            |            |            | Analog<br>Output | enabled                      | DACO — 12-bit Digital-to-Analog Controller output                                                                                                                     |

| (XB_IN7)       |            |            |            | Input            |                              | XB_IN7 — Crossbar module input 7                                                                                                                                      |

|                |            |            |            |                  |                              | After reset, the default state is GPIOC5.                                                                                                                             |

### Signal/Connection Descriptions

### Table 5. MC56F825x/MC56F824x Signal and Package Information (continued)

| Signal<br>Name | 44<br>LQFP | 48<br>LQFP | 64<br>LQFP | Туре                           | State<br>During<br>Reset     | Signal Description                                                                    |

|----------------|------------|------------|------------|--------------------------------|------------------------------|---------------------------------------------------------------------------------------|

| GPIOC14        | 37         | 41         | 55         | Input/<br>Output               | Input,<br>internal<br>pullup | Port C GPIO — This GPIO pin can be individually programmed as an input or output pin. |

| (SDA0)         |            |            |            | Input/<br>Open-drain<br>Output | enabled                      | SDA0 — I <sup>2</sup> C0 serial data line                                             |

| (XB_OUT0)      |            |            |            | Input                          |                              | XB_OUT0 — Crossbar module output 0                                                    |

|                |            |            |            |                                |                              | After reset, the default state is GPIOC14.                                            |

| GPIOC15        | 38         | 42         | 56         | Input/<br>Output               | Input,<br>internal           | Port C GPIO — This GPIO pin can be individually programmed as an input or output pin. |

| (SCL0)         |            |            |            | Input/<br>Open-drain<br>Output | pullup<br>enabled            | SCL0 — I <sup>2</sup> C0 serial clock                                                 |

| (XB_OUT1)      |            |            |            | Input                          |                              | XB_OUT1 — Crossbar module output 1                                                    |

|                |            |            |            |                                |                              | After reset, the default state is GPIOC15.                                            |

| GPIOE0         | 30         | 33         | 45         | Input/<br>Output               | Input,<br>internal           | Port E GPIO — This GPIO pin can be individually programmed as an input or output pin. |

| PWM0B          |            |            |            | Input                          | pullup<br>enabled            | PWM0B — NanoEdge PWM submodule 0 output B                                             |

|                |            |            |            |                                |                              | After reset, the default state is GPIOE0.                                             |

| GPIOE1         | 31         | 34         | 46         | Input/<br>Output               | Input,<br>internal           | Port E GPIO — This GPIO pin can be individually programmed as an input or output pin. |

| (PWM0A)        |            |            |            | Output                         | pullup<br>enabled            | PWM0A — NanoEdge PWM submodule 0 output B                                             |

|                |            |            |            |                                |                              | After reset, the default state is GPIOE1.                                             |

| GPIOE2         | 32         | 35         | 47         | Input/<br>Output               | Input,<br>internal           | Port E GPIO — This GPIO pin can be individually programmed as an input or output pin. |

| (PWM1B)        |            |            |            | Output                         | pullup<br>enabled            | PWM1B — NanoEdge PWM submodule 1 output A                                             |

|                |            |            |            |                                |                              | After reset, the default state is GPIOE2.                                             |

| GPIOE3         | 33         | 36         | 48         | Input/<br>Output               | Input,<br>internal           | Port E GPIO — This GPIO pin can be individually programmed as an input or output pin. |

| (PWM1A)        |            |            |            | Output                         | pullup<br>enabled            | PWM1A — NanoEdge PWM submodule 1 output A                                             |

|                |            |            |            |                                |                              | After reset, the default state is GPIOE3.                                             |

#### **Memory Maps**

### Table 5. MC56F825x/MC56F824x Signal and Package Information (continued)

| Signal<br>Name | 44<br>LQFP | 48<br>LQFP | 64<br>LQFP | Туре             | State<br>During<br>Reset     | Signal Description                                                                    |

|----------------|------------|------------|------------|------------------|------------------------------|---------------------------------------------------------------------------------------|

| GPIOF6         |            |            | 58         | Input/<br>Output | Input,<br>internal<br>pullup | Port F GPIO — This GPIO pin can be individually programmed as an input or output pin. |

| (TB2)          |            |            |            | Input/<br>Output | enabled                      | TB2 — Quad timer module B channel 2 input/output.                                     |

| (PWM3X)        |            |            |            | Input/<br>Output |                              | PWM3X — Enhanced PWM submodule 3 output X or input capture X                          |

|                |            |            |            |                  |                              | After reset, the default state is GPIOF6.                                             |

| GPIOF7         |            |            | 59         | Input/<br>Output | Input,<br>internal<br>pullup | Port F GPIO — This GPIO pin can be individually programmed as an input or output pin. |

| (TB3)          |            |            |            | Input/<br>Output | enabled                      | TB3 — Quad timer module B channel 3 input/output.                                     |

|                |            |            |            |                  |                              | After reset, the default state is GPIOF7.                                             |

| GPIOF8         |            |            | 6          | Input/<br>Output | Input,<br>internal<br>pullup | Port F GPIO — This GPIO pin can be individually programmed as an input or output pin. |

| (RXD0)         |            |            |            | Input            | enabled                      | RXD0 — The SCI0 receive data input.                                                   |

| (TB1)          |            |            |            | Input/<br>Output |                              | TB1 — Quad timer module B channel 1 input/output.                                     |

|                |            |            |            |                  |                              | After reset, the default state is GPIOF8.                                             |

If CLKIN is selected as the device's external clock input, both the GPS\_C0 bit in GPS1 and the EXT\_SEL bit in the OCCS oscillator control register (OSCTL) must be set. In this case, it is also recommended to power down the crystal oscillator.

# 4 Memory Maps

### 4.1 Introduction

The MC56F825x/MC56F824x device is based on the 56800E core. It uses a dual Harvard-style architecture with two independent memory spaces for data and program. On-chip RAM is shared by both data and program spaces; flash memory is used only in program space.

This section provides memory maps for:

- Program address space, including the interrupt vector table

- Data address space, including the EOnCE memory and peripheral memory maps

On-chip memory sizes for the device are summarized in Table 6. Flash memories' restrictions are identified in the "Use Restrictions" column of Table 6.

| On-Chip Memory            | 56F8245<br>56F8246      | 56F8247                 | 56F8255<br>56F8256<br>56F8357 | Use Restrictions                                               |

|---------------------------|-------------------------|-------------------------|-------------------------------|----------------------------------------------------------------|

| Program Flash<br>(PFLASH) | 24K x 16<br>or<br>48 KB | 24K x 16<br>or<br>48 KB | 32K x 16<br>or<br>64 KB       | Erase/program via flash interface unit and word writes to CDBW |

| Unified RAM<br>(RAM)      | 3K x 16<br>or<br>6 KB   | 4K x 16<br>or<br>8 KB   | 4K x 16<br>or<br>8 KB         | Usable by the program and data memory spaces                   |

**Table 6. Chip Memory Configurations**

## 4.2 Program Map

The MC56F825x/MC56F824x series provide up to 64 KB on-chip flash memory. It primarily accesses through the program memory buses (PAB; PDB). PAB is used to select program memory addresses; instruction fetches are performed over PDB. Data can be read from and written to the program memory space through the primary data memory buses: CDBW for data write and CDBR for data read. Access time for accessing the program memory space over the data memory buses is longer than for accessing data memory space. The special MOVE instructions are provided to support these accesses. The benefit is that non-time-critical constants or tables can be stored and accessed in program memory.

The program memory map appears in Table 7, Table 8, and Table 9, depending on the device.

| Begin/End Address            | Memory Allocation                                                                                                                                                                               |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P: 0x1F FFFF<br>P: 0x00 8800 | RESERVED                                                                                                                                                                                        |

| P: 0x00 8FFF<br>P: 0x00 8000 | On-chip RAM <sup>2</sup> : 8 KB                                                                                                                                                                 |

| P: 0x00 7FFF<br>P: 0x00 0000 | <ul> <li>Internal program flash: 64 KB</li> <li>Interrupt vector table locates from 0x00 0000 to 0x00 0085</li> <li>COP reset address = 0x00 0002</li> <li>Boot location = 0x00 0000</li> </ul> |

Table 7. Program Memory Map<sup>1</sup> for 56F8255/56/57 at Reset

<sup>1</sup> All addresses are 16-bit word addresses.

<sup>2</sup> This RAM is shared with data space starting at address X: 0x00 0000. See Figure 6.

| Begin/End Address            | Memory Allocation                                                                                                                                                                               |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P: 0x1F FFFF<br>P: 0x00 8800 | RESERVED                                                                                                                                                                                        |

| P: 0x00 8FFF<br>P: 0x00 8000 | On-chip RAM <sup>2</sup> : 8 KB                                                                                                                                                                 |

| P: 0x00 7FFF<br>P: 0x00 2000 | <ul> <li>Internal program flash: 48 KB</li> <li>Interrupt vector table locates from 0x00 2000 to 0x00 2085</li> <li>COP reset address = 0x00 2002</li> <li>Boot location = 0x00 2000</li> </ul> |

| P: 0x00 2000<br>P: 0x00 0000 | RESERVED                                                                                                                                                                                        |

• Software reset (SWR)

Each of these sources has an associated bit in the reset status register (RSTAT) in the system integration module (SIM).

The external pin reset function is shared with a GPIO port A7 on the RESET/GPIOA7 pin. The reset function is enabled following any reset of the device. Bit 7 of the GPIOA\_PER register must be cleared to use this pin as a GPIO port pin. When the pin is enabled as the RESET pin, an internal pullup device is automatically enabled.

# 5.4 On-chip Clock Synthesis

The on-chip clock synthesis (OCCS) module allows designers using an internal relaxation oscillator, an external crystal, or an external clock to run 56F8000 family devices at user-selectable frequencies up to 60 MHz.

The features of OCCS module include:

- Ability to power down the internal relaxation oscillator or crystal oscillator

- Ability to put the internal relaxation oscillator into standby mode

- Ability to power down the PLL

- Provides a 2x system clock that operates at two times the system clock to the timer and SCI modules

- Safety shutdown feature if the PLL reference clock is lost

- Ability to be driven from an external clock source

The clock generation module provides the programming interface for the PLL, internal relaxation oscillator, and crystal oscillator. It also provides a postscaler to divide clock frequency down by 1, 2, 4, 8, 16, 32, 64, 128, or 256 before feeding it to the SIM. The SIM is responsible for further dividing these frequencies by 2, which ensures a 50% duty cycle in the system clock output. For details, refer to the OCCS section of the device's reference manual.

### 5.4.1 Internal Clock Source

When an external frequency source or crystal is not used, an internal relaxation oscillator can supply the reference frequency. It is optimized for accuracy and programmability while providing several power-saving configurations that accommodate different operating conditions. The internal relaxation oscillator has little temperature and voltage variability. To optimize power, the internal relaxation oscillator supports a run state (8 MHz), standby state (400 kHz), and a power-down state.

During a boot or reset sequence, the relaxation oscillator is enabled by default (the PRECS bit in the PLLCR word is set to 0). Application code can then also switch to the external clock source and power down the internal oscillator, if desired. If a changeover between internal and external clock sources is required at power-on, ensure that the clock source is not switched until the desired external clock source is enabled and stable.

To compensate for variances in the device manufacturing process, the accuracy of the relaxation oscillator can be incrementally adjusted to within + 0.078% of 8 MHz by trimming an internal capacitor. Bits 0–9 of the oscillator control (OSCTL) register allow you to set an additional offset (trim) to this preset value to increase or decrease capacitance. Each unit added or subtracted changes the output frequency by about 0.078% of 8 MHz, allowing incremental adjustment until the desired frequency accuracy is achieved.

The center frequency of the internal oscillator is calibrated at the factory to 8 MHz, and the TRIM value is stored in the flash information block and loaded to the HFM IFR option register 0 at reset. When using the relaxation oscillator, the boot code should read the HFM IFR option register 0 and set this value as OSCTL TRIM. For further information, refer to the device's reference manual.

### 5.4.2 Crystal Oscillator/Ceramic Resonator

The internal crystal oscillator circuit is designed to interface with a parallel-resonant crystal resonator in the frequency range, specified for the external crystal, of 4 MHz to 16 MHz. A ceramic resonator can be substituted for the 4 MHz to 16 MHz range. When used to supply a source to the internal PLL, the recommended crystal/resonator is in the 8 MHz to 16 MHz range to optimize PLL performance. Oscillator circuits appear in Figure 9 and Figure 10. Follow the crystal supplier's recommendations

#### **General System Control Information**

| EXT_SEL & CLK_MODE = 1 | MC56F825x/MC56F824x |  |  |  |

|------------------------|---------------------|--|--|--|

| GPIOC_PER0 = 0         | CLKIN               |  |  |  |

| GPS_C0 = 1             |                     |  |  |  |

External Clock (≤ 120 MHz)

### Figure 11. Connecting an External Clock Signal Using GPIO

### 5.5 Interrupt Controller

The MC56F825x/MC56F824x interrupt controller (INTC) module arbitrates the various interrupt requests (IRQs). When an interrupt of sufficient priority exists, the INTC signals to the 56800E core and provides the address to which to jump to service the interrupt.

The interrupt controller contains registers that allow each of the 66 interrupt sources to be set to one of three priority levels (excluding certain interrupt sources that have fixed priority) or to be disabled. Next, all interrupt requests of a given level are priority encoded to determine the lowest numeric value of the active interrupt requests for that level. Within a given priority level, the lowest vector number is the highest priority, and the highest vector number is the lowest priority.

Any two interrupt sources can be assigned to faster interrupts. Fast interrupts are described in the DSP56800E Reference Manual. The interrupt controller recognizes fast interrupts before the core does.

A fast interrupt is defined by:

- 1. Setting the priority of the interrupt as level 2 with the appropriate field in the Interrupt Priority Register (IPR) registers

- 2. Setting the Fast Interrupt Match (FIM*n*) register to the appropriate vector number

- 3. Setting the Fast Interrupt Vector Address Low (FIVAL*n*) and Fast Interrupt Vector Address High (FIVAH*n*) registers with the address of the code for the fast interrupt

When an interrupt occurs, its vector number is compared with the FIM0 and FIM1 register values. If a match occurs, and it is a level 2 interrupt, the INTC handles it as a Fast Interrupt. The INTC takes the vector address from the appropriate FIVAL*n* and FIVAH*n* registers, instead of generating an address that is an offset from the VBA.

The core then fetches the instruction from the indicated vector address instead of jumping to the vector table. If the instruction is not a JSR, the core starts its fast interrupt handling. Refer to section 9.3.3.3 of *DSP56800E 16-Bit Core Reference Manual* for details.

Table 48 on page 85 provides the MC56F825x/MC56F824x's interrupt table contents and interrupt priority structure.

### 5.6 System Integration Module (SIM)

The SIM module consists of the glue logic that ties together the system-on-a-chip. It controls distribution of resets and clocks and provides a number of control features, including pin muxing control, inter-module connection control (such as connecting comparator output to eFlexPWM fault input), individual peripheral enabling/disabling, clock rate control for quad timers and SCIs, enabling peripheral operation in stop mode, and port configuration overwrite protection. For more information, refer to the device's reference manual.

The SIM is responsible for the following functions:

- Chip reset sequencing

- Core and peripheral clock control and distribution

- Stop/wait mode control

- System status control

- Registers containing the JTAG ID of the chip

- Controls for programmable peripheral and GPIO connections

# 7.3 ESD Protection and Latch-up Immunity

Although damage from electrostatic discharge (ESD) is much less common on these devices than on early CMOS circuits, use normal handling precautions to avoid exposure to static discharge. Qualification tests are performed to ensure that these devices can withstand exposure to reasonable levels of static without suffering any permanent damage.

All ESD testing conforms with AEC-Q100 Stress Test Qualification. During device qualification, ESD stresses are performed for the human body model (HBM), the machine model (MM), and the charge device model (CDM).

All latch-up testing conforms with AEC-Q100 Stress Test Qualification.

A device is defined as a failure if, after exposure to ESD pulses, the device no longer meets the device specification. Comprehensive DC parametric and functional testing is performed according to the applicable device specification at room temperature and then at hot temperature, unless specified otherwise in the device specification.

| Characteristic <sup>1</sup>                            | Min   | Тур | Max | Unit |

|--------------------------------------------------------|-------|-----|-----|------|

| ESD for Human Body Model (HBM)                         | 2000  | _   | _   | V    |

| ESD for Machine Model (MM)                             | 200   | _   | _   | V    |

| ESD for Charge Device Model (CDM)                      | 750   | _   | _   | V    |

| Latch-up current at $T_A = 85  {}^{\circ}C  (I_{LAT})$ | ± 100 |     |     | mA   |

Table 18. MC56F825x/MC56F824x ESD/Latch-up Protection

Parameter is achieved by design characterization on a small sample size from typical devices under typical conditions, unless otherwise noted

### 7.4 Thermal Characteristics

This section provides information about operating temperature range, power dissipation, and package thermal resistance. Power dissipation on I/O pins is usually small compared to power dissipation in on-chip logic and voltage regulator circuits, and it is user-determined rather than being controlled by the device design. To account for  $P_{I/O}$  in power calculations, determine the difference between actual pin voltage and  $V_{SS}$  or  $V_{DD}$  and multiply by the pin current for each I/O pin. Except in cases of unusually high pin current (heavy loads), the difference between pin voltage and  $V_{SS}$  or  $V_{DD}$  is very small.

| Characteristic                            | Comments                   | Symbol                 | Value<br>(LQFP) | Unit |

|-------------------------------------------|----------------------------|------------------------|-----------------|------|

| Junction to ambient<br>Natural convection | Single layer board<br>(1s) | $R_{	extsf{	heta}JA}$  | 70              | °C/W |

| Junction to ambient<br>Natural convection | Four layer board<br>(2s2p) | $R_{	extsf{	heta}JMA}$ | 48              | °C/W |

| Junction to ambient<br>(@200 ft/min)      | Single layer board<br>(1s) | $R_{	extsf{	heta}JMA}$ | 57              | °C/W |

| Junction to ambient<br>(@200 ft/min)      | Four layer board<br>(2s2p) | $R_{	extsf{	heta}JMA}$ | 42              | °C/W |

| Junction to board                         |                            | $R_{\theta JB}$        | 30              | °C/W |

| Junction to case                          |                            | $R_{	extsf{	heta}JC}$  | 13              | °C/W |

| Junction to package top                   | Natural convection         | $\Psi_{JT}$            | 2               | °C/W |

Table 19. 44LQFP Package Thermal Characteristics

Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

See Section 8.1, "Thermal Design Considerations," for more detail on thermal design considerations.

### 7.5 Recommended Operating Conditions

This section contains information about recommended operating conditions.

| Table 22. Recommended Operating Conditions | $(V_{REFLx} = 0 V, V_{SSA} = 0 V, V_{SS} = 0 V)$ |

|--------------------------------------------|--------------------------------------------------|

|--------------------------------------------|--------------------------------------------------|

| Characteristic                                                                                                                                        | Symbol                               | Notes                              | Min        | Тур | Max                   | Unit   |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------------------------------|------------|-----|-----------------------|--------|--|--|

| Supply voltage                                                                                                                                        | V <sub>DD,</sub><br>V <sub>DDA</sub> |                                    | 3          | 3.3 | 3.6                   | V      |  |  |

| ADC Reference Voltage High                                                                                                                            | V <sub>REFHx</sub>                   |                                    | 3.0        |     | V <sub>DDA</sub>      | V      |  |  |

| Voltage difference $\rm V_{DD}$ to $\rm V_{DDA}$                                                                                                      | $\Delta V_{DD}$                      |                                    | -0.1       | 0   | 0.1                   | V      |  |  |

| Voltage difference $\rm V_{SS}$ to $\rm V_{SSA}$                                                                                                      | $\Delta V_{SS}$                      |                                    | -0.1       | 0   | 0.1                   | V      |  |  |

| Device Clock Frequency<br>Using relaxation oscillator<br>Using external clock source                                                                  | FSYSCLK                              |                                    | 0.001<br>0 |     | 60<br>60              | MHz    |  |  |

| Input Voltage High (digital inputs)                                                                                                                   | V <sub>IH</sub>                      | Pin Groups 1, 2                    | 2.0        |     | 5.5                   | V      |  |  |

| Input Voltage Low (digital inputs)                                                                                                                    | V <sub>IL</sub>                      | Pin Groups 1, 2                    | -0.3       |     | 0.8                   | V      |  |  |

| Oscillator Input Voltage High<br>XTAL driven by an external clock source                                                                              | V <sub>IHOSC</sub>                   | Pin Group 4                        | 2.0        |     | V <sub>DD</sub> + 0.3 | V      |  |  |

| Oscillator Input Voltage Low                                                                                                                          | V <sub>ILOSC</sub>                   | Pin Group 4                        | -0.3       |     | 0.8                   | V      |  |  |

| DAC Output Load Resistance                                                                                                                            | R <sub>LD</sub>                      | Pin Group 5                        | ЗK         |     |                       | Ω      |  |  |

| DAC Output Load Capacitance                                                                                                                           | C <sub>LD</sub>                      | Pin Group 5                        |            |     | 400                   | pf     |  |  |

| Output Source Current High at V <sub>OH</sub> min.) <sup>1</sup><br>When programmed for low drive strength<br>When programmed for high drive strength | I <sub>OH</sub>                      | Pin Group 1<br>Pin Group 1         | _          |     | -4<br>-8              | mA     |  |  |

| Output Source Current Low (at V <sub>OL</sub> max.) <sup>1</sup><br>When programmed for low drive strength<br>When programmed for high drive strength | I <sub>OL</sub>                      | Pin Groups 1, 2<br>Pin Groups 1, 2 |            |     | 4<br>8                | mA     |  |  |

| Ambient Operating Temperature (Extended Industrial)                                                                                                   | T <sub>A</sub>                       |                                    | -40        |     | 105                   | °C     |  |  |

| Flash Endurance<br>(Program Erase Cycles)                                                                                                             | N <sub>F</sub>                       | T <sub>A</sub> = -40°C to<br>125°C | 10,000     |     | —                     | cycles |  |  |

| Flash Data Retention                                                                                                                                  | T <sub>R</sub>                       | T <sub>J</sub> <= 85°C avg         | 15         |     | —                     | years  |  |  |

| Flash Data Retention with <100<br>Program/Erase Cycles                                                                                                | t <sub>FLRET</sub>                   | T <sub>J</sub> <= 85°C avg         | 20         | —   | _                     | years  |  |  |

### 7.8 Power-On Reset, Low Voltage Detection Specification

| Characteristic                                      | Symbol             | Min | Тур  | Max | Unit |

|-----------------------------------------------------|--------------------|-----|------|-----|------|

| Low-Voltage Interrupt for 3.3 V supply <sup>1</sup> | V <sub>LVI27</sub> | 2.6 | 2.7  | 2.8 | V    |

| Low-Voltage Interrupt for 2.5 V supply <sup>2</sup> | V <sub>LVI21</sub> | —   | 2.18 | _   | V    |

| Low-Voltage Interrupt Recovery Hysteresis           | V <sub>EIH</sub>   | _   | 50   | _   | mV   |

| Power-On Reset Threshold <sup>3</sup>               | POR                | 2.6 | 2.7  | 2.8 | V    |

| Brown-Out Reset Threshold <sup>4</sup>              | BOR                | —   | 1.8  | 1.9 | V    |

Table 25. Power-On Reset and Low-Voltage Detection Parameters

<sup>1</sup> When V<sub>DD</sub> drops below LVI27, an interrupt is generated.

<sup>2</sup> When V<sub>DD</sub> drops below LVI21, an interrupt is generated.

<sup>3</sup> While power is ramping up, this signal remains active for as long as the internal 2.5 V is below 2.18 V or the 3.3 V V<sub>DD</sub> voltage is below 2.7 V, no matter how long the ramp-up rate is. The internally regulated voltage is typically 100 mV less than V<sub>DD</sub> during ramp-up until 2.5 V is reached, at which time it self-regulates.

<sup>4</sup> Brown-Out Reset occurs whenever the internally regulated 2.5 V digital supply drops below 1.8 V.

# 7.9 Voltage Regulator Specifications

The MC56F825x/MC56F824x has two on-chip regulators. One supplies the PLL, crystal oscillator, NanoEdge placement PWM, and relaxation oscillator. It has no external pins and therefore has no external characteristics that must be guaranteed (other than proper operation of the device). The second regulator supplies approximately 2.5 V to the

MC56F825x/MC56F824x's core logic. For proper operation, this regulator requires an external capacitor of 2.2  $\mu$ F or greater. Ceramic and tantalum capacitors tend to provide better performance tolerances. The output voltage can be measured directly on the V<sub>CAP</sub> pin. The specifications for this regulator appear in Table 26.

Table 26. Regulator Parameters

| Characteristic                                                  | Symbol           | Min | Typical | Max  | Unit    |

|-----------------------------------------------------------------|------------------|-----|---------|------|---------|

| Short Circuit Current                                           | I <sub>SS</sub>  | _   | 900     | 1300 | mA      |

| Short Circuit Tolerance<br>(V <sub>CAP</sub> shorted to ground) | T <sub>RSC</sub> | _   | _       | 30   | minutes |

### 7.10 AC Electrical Characteristics

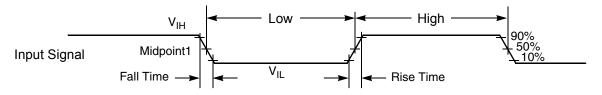

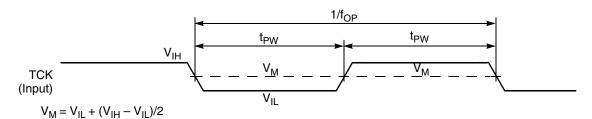

Tests are conducted using the input levels specified in Table 23. Unless otherwise specified, propagation delays are measured from the 50% to the 50% point, and rise and fall times are measured between the 10% and 90% points, as shown in Figure 15.

The midpoint is  $V_{IL} + (V_{IH} - V_{IL})/2$ .

Figure 15. Input Signal Measurement References

| Characteristic                                    | Symbol            | Min                 | Тур | Max                | Unit |

|---------------------------------------------------|-------------------|---------------------|-----|--------------------|------|

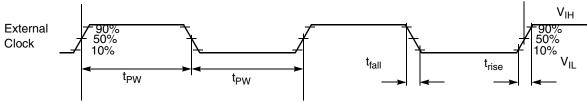

| External clock input rise time <sup>4</sup>       | t <sub>rise</sub> | _                   | _   | 3                  | ns   |

| External clock input fall time <sup>5</sup>       | t <sub>fall</sub> | _                   |     | 3                  | ns   |

| Input high voltage overdrive by an external clock | V <sub>ih</sub>   | 0.85V <sub>DD</sub> | _   | _                  | V    |

| Input high voltage overdrive by an external clock | V <sub>il</sub>   | —                   | _   | 0.3V <sub>DD</sub> | V    |

Table 29. External Clock Operation Timing Requirements<sup>1</sup> (continued)

<sup>1</sup> Parameters listed are guaranteed by design.

<sup>2</sup> See Figure 17 for details on using the recommended connection of an external clock driver.

<sup>3</sup> The chip may not function if the high or low pulse width is smaller than 6.25 ns.

<sup>4</sup> External clock input rise time is measured from 10% to 90%.

<sup>5</sup> External clock input fall time is measured from 90% to 10%.

Note: The midpoint is  $V_{IL} + (V_{IH} - V_{IL})/2$ .

Figure 17. External Clock Timing

## 7.14 Phase Locked Loop Timing

### Table 30. Phase Locked Loop Timing

| Characteristic                                                                    | Symbol                 | Min | Тур | Мах | Unit |

|-----------------------------------------------------------------------------------|------------------------|-----|-----|-----|------|

| PLL input reference frequency <sup>1</sup>                                        | f <sub>ref</sub>       | 4   | 8   | 8   | MHz  |

| PLL output frequency <sup>2</sup>                                                 | f <sub>op</sub>        | 120 |     | 240 | MHz  |

| PLL lock time <sup>3 4</sup>                                                      | t <sub>plls</sub>      | _   | 40  | 100 | μs   |

| Accumulated jitter using an 8 MHz external crystal as the PLL source <sup>5</sup> | J <sub>A</sub>         | _   |     | TBD | %    |

| Cycle-to-cycle jitter                                                             | t <sub>jitterpll</sub> | _   | 350 | _   | ps   |

<sup>1</sup> An externally supplied reference clock should be as free as possible from any phase jitter for the PLL to work correctly. The PLL is optimized for 8 MHz input.

<sup>2</sup> The core system clock operates at 1/6 of the PLL output frequency.

<sup>3</sup> This is the time required after the PLL is enabled to ensure reliable operation.

<sup>4</sup> From powerdown to powerup state at 60 MHz system clock state.

<sup>5</sup> This is measured on the CLKO signal (programmed as system clock) over 264 system clocks at 60 MHz system clock frequency and using an 8 MHz oscillator frequency.

# 7.22 JTAG Timing

Table 38. JTAG Timing

| Characteristic                          | Symbol          | Min | Max       | Unit | See Figure |

|-----------------------------------------|-----------------|-----|-----------|------|------------|

| TCK frequency of operation <sup>1</sup> | f <sub>OP</sub> | DC  | SYS_CLK/8 | MHz  | Figure 28  |

| TCK clock pulse width                   | t <sub>PW</sub> | 50  | —         | ns   | Figure 28  |

| TMS, TDI data set-up time               | t <sub>DS</sub> | 5   | —         | ns   | Figure 29  |

| TMS, TDI data hold time                 | t <sub>DH</sub> | 5   | —         | ns   | Figure 29  |

| TCK low to TDO data valid               | t <sub>DV</sub> | _   | 30        | ns   | Figure 29  |

| TCK low to TDO tri-state                | t <sub>TS</sub> |     | 30        | ns   | Figure 29  |

<sup>1</sup> TCK frequency of operation must be less than 1/8 the processor rate.

Figure 28. Test Clock Input Timing Diagram

# 7.24 COP Specifications

Table 40. COP Specifications

| Parameter                                                 | Symbol | Min | Тур  | Max  | Unit |

|-----------------------------------------------------------|--------|-----|------|------|------|

| Oscillator output frequency                               | LPFosc | 500 | 1000 | 1500 | Hz   |

| Oscillator current consumption in partial power down mode | IDD    |     | TBD  |      | nA   |

# 7.25 Analog-to-Digital Converter (ADC) Parameters

Table 41. ADC Parameters<sup>1</sup>

| Parameter                                                                                                                                                                                               | Symbol                      | Min               | Тур                       | Max                  | Unit                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------------|---------------------------|----------------------|--------------------------------------|

| DC Specifications                                                                                                                                                                                       |                             |                   |                           | -                    | ·                                    |

| Resolution                                                                                                                                                                                              | R <sub>ES</sub>             | 12                | —                         | 12                   | Bits                                 |

| ADC internal clock                                                                                                                                                                                      | f <sub>ADIC</sub>           | 0.1               | —                         | 15                   | MHz                                  |

| Conversion range                                                                                                                                                                                        | R <sub>AD</sub>             | V <sub>REFL</sub> | —                         | V <sub>REFH</sub>    | V                                    |

| ADC and VREF power-up time <sup>2</sup> (from power down mode)                                                                                                                                          | t <sub>ADPU</sub>           | —                 | 13                        |                      | t <sub>AIC</sub> cycles <sup>3</sup> |

| VREF power-up time (from low power mode)                                                                                                                                                                | t <sub>REFPU</sub>          | —                 | 6                         | _                    | t <sub>AIC</sub> cycles <sup>3</sup> |

| ADC RUN current (Speed Control setting)<br>at 100 kHz ADC clock (Standby Mode)<br>at ADC clock $\leq$ 5 MHz (00)<br>at 5 MHz < ADC clock $\leq$ 12 MHz (01)<br>at 12 MHz < ADC clock $\leq$ 15 MHz (10) | I <sub>ADRUN</sub>          | _<br>_<br>_<br>_  | 0.6<br>10<br>17<br>27     | <br>                 | mA                                   |

| Conversion time                                                                                                                                                                                         | t <sub>ADC</sub>            | _                 | 6                         | —                    | t <sub>AIC</sub> cycles <sup>3</sup> |

| Sample time                                                                                                                                                                                             | t <sub>ADS</sub>            | _                 | 1                         | —                    | t <sub>AIC</sub> cycles <sup>3</sup> |

| Accuracy (DC or absolute) (gain of 1x, 2x                                                                                                                                                               | , 4x and f <sub>ADC</sub> : | ≤ 10 MHz)         | (all data in single-ended | d mode) <sup>4</sup> | L                                    |

| Integral non-linearity <sup>5</sup><br>(Full input signal range)                                                                                                                                        | INL                         | —                 | +/- 3                     | +/- 6                | LSB <sup>6</sup>                     |

| Differential non-linearity <sup>5</sup>                                                                                                                                                                 | DNL                         | _                 | +/- 0.6                   | +/- 1                | LSB <sup>5</sup>                     |

| Monotonicity                                                                                                                                                                                            |                             | 1                 | GUARANTEED                |                      |                                      |

| Offset Voltage Internal Ref                                                                                                                                                                             | V <sub>OFFSET</sub>         | —                 | +/- 8                     | +/- 15               | mV                                   |

| Offset Voltage External Ref                                                                                                                                                                             | V <sub>OFFSET</sub>         | —                 | +/- 8                     | +/- 15               | mV                                   |

| Gain Error (transfer gain)                                                                                                                                                                              | E <sub>GAIN</sub>           | —                 | 0.995 to 1.005            | 1.01 to 0.99         | —                                    |

| ADC Inputs <sup>7</sup> (Pin Group 3)                                                                                                                                                                   |                             |                   |                           | •                    |                                      |

| Input voltage (external reference)                                                                                                                                                                      | V <sub>ADIN</sub>           | V <sub>REFL</sub> | _                         | V <sub>REFH</sub>    | V                                    |

| Input voltage (internal reference)                                                                                                                                                                      | V <sub>ADIN</sub>           | V <sub>SSA</sub>  | —                         | V <sub>DDA</sub>     | V                                    |

| Input leakage                                                                                                                                                                                           | I <sub>IA</sub>             | —                 | 0                         | +/- 2                | μA                                   |

| V <sub>REFH</sub> current                                                                                                                                                                               | I <sub>VREFH</sub>          | —                 | 0.001                     | —                    | μA                                   |

| Input injection current <sup>8</sup> , per pin                                                                                                                                                          | I <sub>ADI</sub>            | —                 | —                         | 3                    | mA                                   |

| Input capacitance                                                                                                                                                                                       | C <sub>ADI</sub>            |                   | See Figure 31             | _                    | pF                                   |

### **Ordering Information**

Use the following list of considerations to assure correct operation of the MC56F825x/MC56F824x: