### NXP USA Inc. - MC56F8257MLH Datasheet

#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                               |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | 56800E                                                               |

| Core Size                  | 16-Bit                                                               |

| Speed                      | 60MHz                                                                |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI                           |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 54                                                                   |

| Program Memory Size        | 64KB (32K x 16)                                                      |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                |                                                                      |

| RAM Size                   | 4K x 16                                                              |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                            |

| Data Converters            | A/D 16x12b; D/A 1x12b                                                |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 64-LQFP                                                              |

| Supplier Device Package    | 64-LQFP (10x10)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc56f8257mlh |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Overview

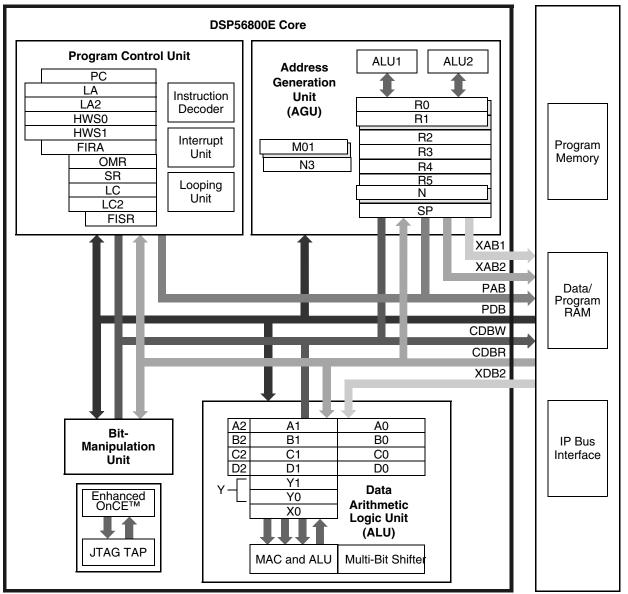

Figure 1. 56800E Core Block Diagram

Figure 2 shows the peripherals and control blocks connected to the IP bus bridge. Refer to the system integration module (SIM) section in the device's reference manual for information about which signals are multiplexed with those of other peripherals.

### Signal/Connection Descriptions

| Pi         | Pin Number |            |                 | Peripherals |                  |     |     |                        |     |           |      |               |              |                 |      |       |

|------------|------------|------------|-----------------|-------------|------------------|-----|-----|------------------------|-----|-----------|------|---------------|--------------|-----------------|------|-------|

| 44<br>LQFP | 48<br>LQFP | 64<br>LQFP | Pin Name        | GPIO        | l <sup>2</sup> C | SCI | SPI | MS<br>CAN <sup>1</sup> | ADC | Cross Bar | COMP | Quad<br>Timer | eFlex<br>PWM | Power           | JTAG | Misc. |

| 41         | 45         | 61         | V <sub>SS</sub> |             |                  |     |     |                        |     |           |      |               |              | V <sub>SS</sub> |      |       |

| 42         | 46         | 62         | TDO/GPIOD1      | GPIOD1      |                  |     |     |                        |     |           |      |               |              |                 | TDO  |       |

| 43         | 47         | 63         | TMS/GPIOD3      | GIPOD3      |                  |     |     |                        |     |           |      |               |              |                 | TMS  |       |

| 44         | 48         | 64         | TDI/GPIOD0      | GPIOD0      |                  |     |     |                        |     |           |      |               |              |                 | TDI  |       |

### Table 4. MC56F825x/MC56F824x Pins (continued)

<sup>1</sup> The MSCAN module is not available on the MC56F824x devices.

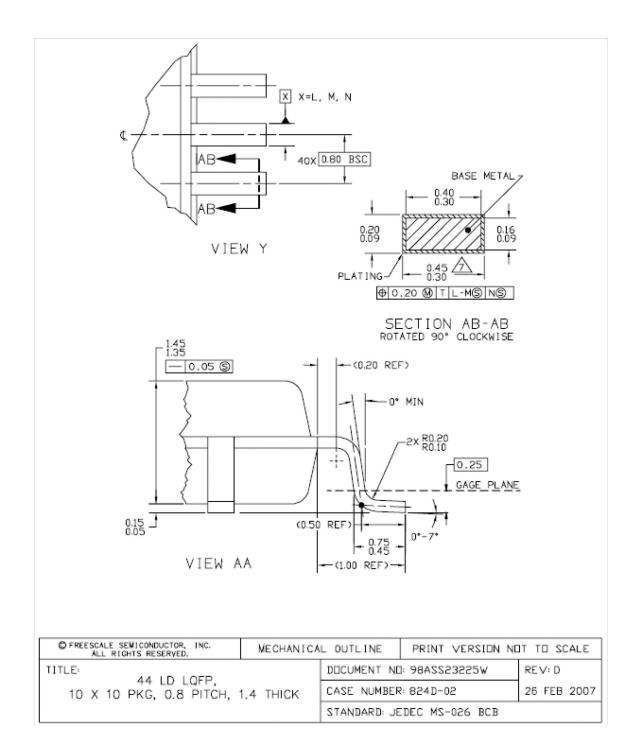

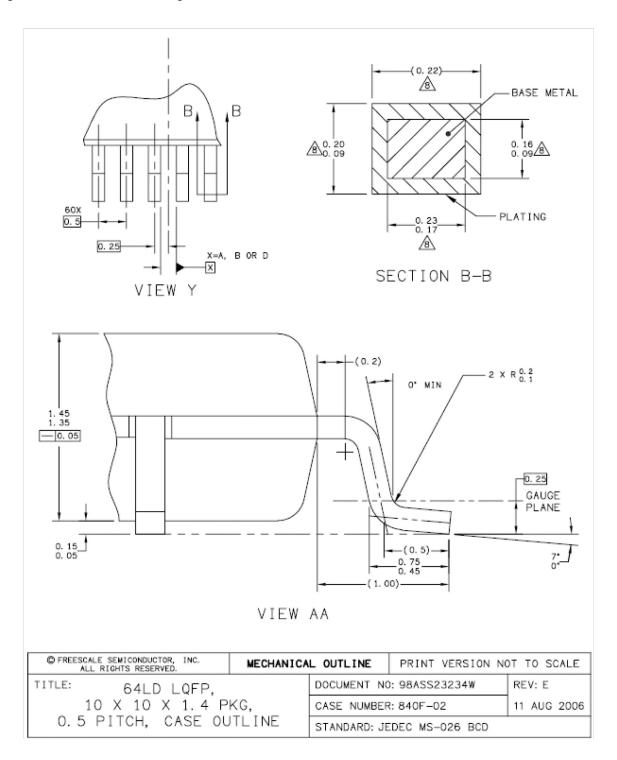

## 3.2 Pin Assignment

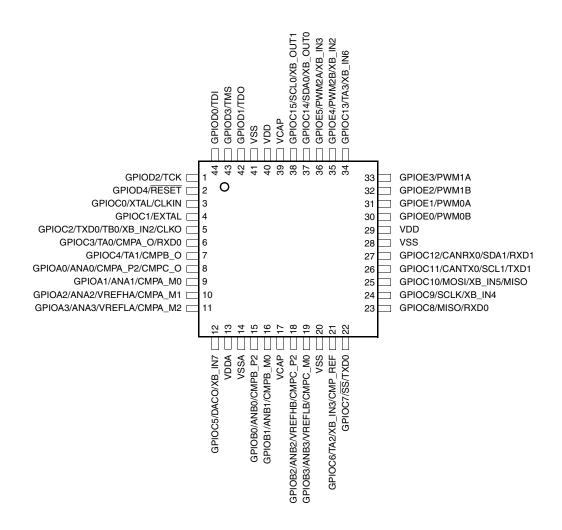

Figure 3 shows the pin assignments of the 56F8245 and 56F8255's 44-pin low-profile quad flat pack (44LQFP). Figure 4 shows the pin assignments of the 56F8246 and 56F8256's 48-pin low-profile quad flat pack (48LQFP). Figure 5 shows the pin assignments of the 56F8247 and 56F8257's 64-pin low-profile quad flat pack (64LQFP).

### NOTE

The CANRX and CANTX signals of the MSCAN module are not available on the MC56F824x devices.

Figure 3. Top View: 56F8245 and 56F8255 44-Pin LQFP Package

### Signal/Connection Descriptions

### Table 5. MC56F825x/MC56F824x Signal and Package Information (continued)

| Signal<br>Name | 44<br>LQFP | 48<br>LQFP | 64<br>LQFP | Туре             | State<br>During<br>Reset     | Signal Description                                                                                                                                                    |

|----------------|------------|------------|------------|------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIOC2         | 5          | 5          | 5          | Input/<br>Output | Input,<br>internal<br>pullup | Port C GPIO — This GPIO pin can be individually programmed as an input or output pin.                                                                                 |

| (TXD0)         |            |            |            | Output           | enabled                      | TXD0 — The SCI0 transmit data output or transmit/receive in single wire operation.                                                                                    |

| <i>(TB0)</i>   |            |            |            | Input/<br>Output |                              | TB0 — Quad timer module B channel 0 input/output.                                                                                                                     |

| (XB_IN2)       |            |            |            | Input            |                              | XB_IN2 — Crossbar module input 2                                                                                                                                      |

| (CLKO)         |            |            |            | Output           |                              | CLKO — This is a buffered clock output; the clock source is selected<br>by clockout select (CLKOSEL) bits in the clock output select register<br>(CLKOUT) of the SIM. |

|                |            |            |            |                  |                              | After reset, the default state is GPIOC2.                                                                                                                             |

| GPIOC3         | 6          | 6          | 7          | Input/<br>Output | Input,<br>internal<br>pullup | Port C GPIO — This GPIO pin can be individually programmed as an input or output pin.                                                                                 |

| (TA0)          |            |            |            | Input/<br>Output | enabled                      | TA0 — Quad timer module A channel 0 input/output.                                                                                                                     |

| (CMPA_O)       |            |            |            | Output           |                              | CMPA_O— Analog comparator A output                                                                                                                                    |

| (RXD0)         |            |            |            | Input            |                              | RXD0 — The SCI0 receive data input.                                                                                                                                   |

|                |            |            |            |                  |                              | After reset, the default state is GPIOC3.                                                                                                                             |

| GPIOC4         | 7          | 7          | 8          | Input/<br>Output | Input,<br>internal<br>pullup | Port C GPIO — This GPIO pin can be individually programmed as an input or output pin.                                                                                 |

| (TA1)          |            |            |            | Input/<br>Output | enabled                      | TA1 — Quad timer module A channel 1input/output                                                                                                                       |

| (CMPB_O)       |            |            |            | Output           |                              | CMPB_O — Analog comparator B output                                                                                                                                   |

|                |            |            |            |                  |                              | After reset, the default state is GPIOC4.                                                                                                                             |

| GPIOC5         | 12         | 13         | 18         | Input/<br>Output | Input,<br>internal<br>pullup | Port C GPIO — This GPIO pin can be individually programmed as an input or output pin.                                                                                 |

| (DACO)         |            |            |            | Analog<br>Output | enabled                      | DACO — 12-bit Digital-to-Analog Controller output                                                                                                                     |

| (XB_IN7)       |            |            |            | Input            |                              | XB_IN7 — Crossbar module input 7                                                                                                                                      |

|                |            |            |            |                  |                              | After reset, the default state is GPIOC5.                                                                                                                             |

### Signal/Connection Descriptions

### Table 5. MC56F825x/MC56F824x Signal and Package Information (continued)

| Signal<br>Name | 44<br>LQFP | 48<br>LQFP | 64<br>LQFP | Туре                           | State<br>During<br>Reset     | Signal Description                                                                                                                                                                                                                           |

|----------------|------------|------------|------------|--------------------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIOC10        | 25         | 27         | 35         | Input/<br>Output               | Input,<br>internal<br>pullup | Port C GPIO — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                                        |

| (MOSI)         |            |            |            | Input/<br>Output               | enabled                      | MOSI — Master out/slave in. In master mode, this pin serves as the data output. In slave mode, this pin serves as the data input.                                                                                                            |

| (XB_IN5)       |            |            |            | Input                          |                              | XB_IN5 — Crossbar module input 5                                                                                                                                                                                                             |

| (MISO)         |            |            |            | Input/<br>Output               |                              | MISO — Master in/slave out. In master mode, this pin serves as the data input. In slave mode, this pin serves as the data output. The MISO line of a slave device is placed in the high-impedance state if the slave device is not selected. |

|                |            |            |            |                                |                              | After reset, the default state is GPIOC10.                                                                                                                                                                                                   |

| GPIOC11        | 26         | 29         | 37         | Input/<br>Output               | Input,<br>internal<br>pullup | Port C GPIO — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                                        |

| (CANTX)        |            |            |            | Open-drain<br>Output           | enabled                      | CANTX — CAN transmit data output (not available on 56F8245/46/47)                                                                                                                                                                            |

| (SCL1)         |            |            |            | Input/<br>Open-drain<br>Output |                              | SCL1 — I <sup>2</sup> C1 serial clock                                                                                                                                                                                                        |

| (TXD1)         |            |            |            | Output                         |                              | TXD1 — SCI1 transmit data output or transmit/receive in single wire operation                                                                                                                                                                |

|                |            |            |            |                                |                              | After reset, the default state is GPIOC11.                                                                                                                                                                                                   |

| GPIOC12        | 27         | 30         | 38         | Input/<br>Output               | Input,<br>internal<br>pullup | Port C GPIO — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                                        |

| (CANRX)        |            |            |            | Input                          | enabled                      | CANRX — CAN receive data input (not available on 56F8245/46/47)                                                                                                                                                                              |

| (SDA1)         |            |            |            | Input/<br>Open-drain<br>Output |                              | SDA1 — I <sup>2</sup> C1 serial data line                                                                                                                                                                                                    |

| (RXD1)         |            |            |            | Input                          |                              | RXD1 — SCI1 receive data input                                                                                                                                                                                                               |

|                |            |            |            |                                |                              | After reset, the default state is GPIOC12.                                                                                                                                                                                                   |

| GPIOC13        | 34         | 37         | 49         | Input/<br>Output               | Input,<br>internal<br>pullup | Port C GPIO — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                                        |

| (TA3)          |            |            |            | Input/<br>Output               | enabled                      | TA3 — Quad timer module A channel 3input/output.                                                                                                                                                                                             |

| (XB_IN6)       |            |            |            | Input                          |                              | XB_IN6 — Crossbar module input 6                                                                                                                                                                                                             |

|                |            |            |            |                                |                              | After reset, the default state is GPIOC13.                                                                                                                                                                                                   |

### **Memory Maps**

### Table 5. MC56F825x/MC56F824x Signal and Package Information (continued)

| Signal<br>Name | 44<br>LQFP | 48<br>LQFP | 64<br>LQFP | Туре             | State<br>During<br>Reset     | Signal Description                                                                    |

|----------------|------------|------------|------------|------------------|------------------------------|---------------------------------------------------------------------------------------|

| GPIOF6         |            |            | 58         | Input/<br>Output | Input,<br>internal<br>pullup | Port F GPIO — This GPIO pin can be individually programmed as an input or output pin. |

| (TB2)          |            |            |            | Input/<br>Output | enabled                      | TB2 — Quad timer module B channel 2 input/output.                                     |

| (PWM3X)        |            |            |            | Input/<br>Output |                              | PWM3X — Enhanced PWM submodule 3 output X or input capture X                          |

|                |            |            |            |                  |                              | After reset, the default state is GPIOF6.                                             |

| GPIOF7         |            |            | 59         | Input/<br>Output | Input,<br>internal<br>pullup | Port F GPIO — This GPIO pin can be individually programmed as an input or output pin. |

| (TB3)          |            |            |            | Input/<br>Output | enabled                      | TB3 — Quad timer module B channel 3 input/output.                                     |

|                |            |            |            |                  |                              | After reset, the default state is GPIOF7.                                             |

| GPIOF8         |            |            | 6          | Input/<br>Output | Input,<br>internal<br>pullup | Port F GPIO — This GPIO pin can be individually programmed as an input or output pin. |

| (RXD0)         |            |            |            | Input            | enabled                      | RXD0 — The SCI0 receive data input.                                                   |

| (TB1)          |            |            |            | Input/<br>Output |                              | TB1 — Quad timer module B channel 1 input/output.                                     |

|                |            |            |            |                  |                              | After reset, the default state is GPIOF8.                                             |

If CLKIN is selected as the device's external clock input, both the GPS\_C0 bit in GPS1 and the EXT\_SEL bit in the OCCS oscillator control register (OSCTL) must be set. In this case, it is also recommended to power down the crystal oscillator.

# 4 Memory Maps

## 4.1 Introduction

The MC56F825x/MC56F824x device is based on the 56800E core. It uses a dual Harvard-style architecture with two independent memory spaces for data and program. On-chip RAM is shared by both data and program spaces; flash memory is used only in program space.

This section provides memory maps for:

- Program address space, including the interrupt vector table

- Data address space, including the EOnCE memory and peripheral memory maps

On-chip memory sizes for the device are summarized in Table 6. Flash memories' restrictions are identified in the "Use Restrictions" column of Table 6.

| On-Chip Memory            | 56F8245<br>56F8246      | 56F8247                 | 56F8255<br>56F8256<br>56F8357 | Use Restrictions                                               |

|---------------------------|-------------------------|-------------------------|-------------------------------|----------------------------------------------------------------|

| Program Flash<br>(PFLASH) | 24K x 16<br>or<br>48 KB | 24K x 16<br>or<br>48 KB | 32K x 16<br>or<br>64 KB       | Erase/program via flash interface unit and word writes to CDBW |

| Unified RAM<br>(RAM)      | 3K x 16<br>or<br>6 KB   | 4K x 16<br>or<br>8 KB   | 4K x 16<br>or<br>8 KB         | Usable by the program and data memory spaces                   |

**Table 6. Chip Memory Configurations**

## 4.2 Program Map

The MC56F825x/MC56F824x series provide up to 64 KB on-chip flash memory. It primarily accesses through the program memory buses (PAB; PDB). PAB is used to select program memory addresses; instruction fetches are performed over PDB. Data can be read from and written to the program memory space through the primary data memory buses: CDBW for data write and CDBR for data read. Access time for accessing the program memory space over the data memory buses is longer than for accessing data memory space. The special MOVE instructions are provided to support these accesses. The benefit is that non-time-critical constants or tables can be stored and accessed in program memory.

The program memory map appears in Table 7, Table 8, and Table 9, depending on the device.

| Begin/End Address            | Memory Allocation                                                                                                                                                                               |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P: 0x1F FFFF<br>P: 0x00 8800 | RESERVED                                                                                                                                                                                        |

| P: 0x00 8FFF<br>P: 0x00 8000 | On-chip RAM <sup>2</sup> : 8 KB                                                                                                                                                                 |

| P: 0x00 7FFF<br>P: 0x00 0000 | <ul> <li>Internal program flash: 64 KB</li> <li>Interrupt vector table locates from 0x00 0000 to 0x00 0085</li> <li>COP reset address = 0x00 0002</li> <li>Boot location = 0x00 0000</li> </ul> |

Table 7. Program Memory Map<sup>1</sup> for 56F8255/56/57 at Reset

<sup>1</sup> All addresses are 16-bit word addresses.

<sup>2</sup> This RAM is shared with data space starting at address X: 0x00 0000. See Figure 6.

| Begin/End Address            | Memory Allocation                                                                                                                                                                               |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P: 0x1F FFFF<br>P: 0x00 8800 | RESERVED                                                                                                                                                                                        |

| P: 0x00 8FFF<br>P: 0x00 8000 | On-chip RAM <sup>2</sup> : 8 KB                                                                                                                                                                 |

| P: 0x00 7FFF<br>P: 0x00 2000 | <ul> <li>Internal program flash: 48 KB</li> <li>Interrupt vector table locates from 0x00 2000 to 0x00 2085</li> <li>COP reset address = 0x00 2002</li> <li>Boot location = 0x00 2000</li> </ul> |

| P: 0x00 2000<br>P: 0x00 0000 | RESERVED                                                                                                                                                                                        |

### **General System Control Information**

| EXT_SEL & CLK_MODE = 1 | MC56F825x/MC56F824x |  |  |

|------------------------|---------------------|--|--|

| GPIOC_PER0 = 0         | CLKIN               |  |  |

| GPS_C0 = 1             |                     |  |  |

External Clock (≤ 120 MHz)

### Figure 11. Connecting an External Clock Signal Using GPIO

## 5.5 Interrupt Controller

The MC56F825x/MC56F824x interrupt controller (INTC) module arbitrates the various interrupt requests (IRQs). When an interrupt of sufficient priority exists, the INTC signals to the 56800E core and provides the address to which to jump to service the interrupt.

The interrupt controller contains registers that allow each of the 66 interrupt sources to be set to one of three priority levels (excluding certain interrupt sources that have fixed priority) or to be disabled. Next, all interrupt requests of a given level are priority encoded to determine the lowest numeric value of the active interrupt requests for that level. Within a given priority level, the lowest vector number is the highest priority, and the highest vector number is the lowest priority.

Any two interrupt sources can be assigned to faster interrupts. Fast interrupts are described in the DSP56800E Reference Manual. The interrupt controller recognizes fast interrupts before the core does.

A fast interrupt is defined by:

- 1. Setting the priority of the interrupt as level 2 with the appropriate field in the Interrupt Priority Register (IPR) registers

- 2. Setting the Fast Interrupt Match (FIM*n*) register to the appropriate vector number

- 3. Setting the Fast Interrupt Vector Address Low (FIVAL*n*) and Fast Interrupt Vector Address High (FIVAH*n*) registers with the address of the code for the fast interrupt

When an interrupt occurs, its vector number is compared with the FIM0 and FIM1 register values. If a match occurs, and it is a level 2 interrupt, the INTC handles it as a Fast Interrupt. The INTC takes the vector address from the appropriate FIVAL*n* and FIVAH*n* registers, instead of generating an address that is an offset from the VBA.

The core then fetches the instruction from the indicated vector address instead of jumping to the vector table. If the instruction is not a JSR, the core starts its fast interrupt handling. Refer to section 9.3.3.3 of *DSP56800E 16-Bit Core Reference Manual* for details.

Table 48 on page 85 provides the MC56F825x/MC56F824x's interrupt table contents and interrupt priority structure.

## 5.6 System Integration Module (SIM)

The SIM module consists of the glue logic that ties together the system-on-a-chip. It controls distribution of resets and clocks and provides a number of control features, including pin muxing control, inter-module connection control (such as connecting comparator output to eFlexPWM fault input), individual peripheral enabling/disabling, clock rate control for quad timers and SCIs, enabling peripheral operation in stop mode, and port configuration overwrite protection. For more information, refer to the device's reference manual.

The SIM is responsible for the following functions:

- Chip reset sequencing

- Core and peripheral clock control and distribution

- Stop/wait mode control

- System status control

- Registers containing the JTAG ID of the chip

- Controls for programmable peripheral and GPIO connections

### **General System Control Information**

- Peripheral clocks for Quad Timers and SCIs with a high-speed (2x) option

- Power-saving clock gating for peripherals

- Controls for enabling/disabling functions of large regulator standby mode with write protection capability

- Allowing selected peripherals to run in stop mode to generate stop recovery interrupts

- Controls for programmable peripheral and GPIO connections

- Software chip reset

- I/O short address base location control

- Peripheral protection control to provide runaway code protection for safety-critical applications

- Controls for output of internal clock sources to CLKO pin

- · Four general-purpose software control registers that are reset only at power-on

- Peripheral stop mode clocking control

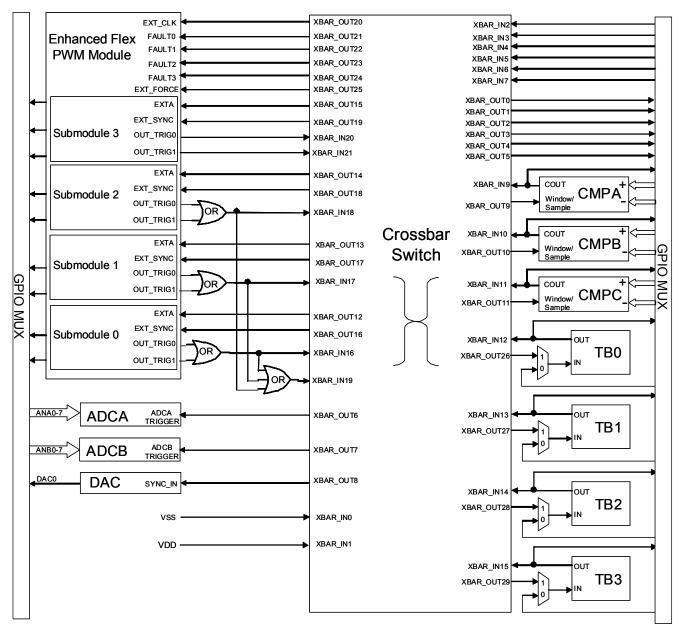

## 5.7 Inter-Module Connections

The operations between on-chip peripherals can be synchronized or cascaded through internal module connections to support particular applications. Examples include synchronization between ADC sampling and PWM waveform generation for a power conversion application, and synchronization between timer pulse outputs and DAC waveform generation for a printer application. The user can program the internal Crossbar Switch or Comparator input multiplexes to connect one on-chip peripheral's outputs to other peripherals' inputs.

## 5.7.1 Comparator Connections

The MC56F825x/MC56F824x includes three high-speed comparators. Each comparator input has a 4-to-1 input mux, allowing it to sample a variety of analog sources. Some of these inputs share package pins with the on-chip ADCs; see Table 5 on page 18.

Each comparator is paired with a dedicated, programmable, 5-bit on-chip voltage reference DAC (VREF\_DAC). Optionally, an on-chip 12-bit DAC can be internally fed to each comparator's positive input 1 (CMPn\_P1) or negative input 3 (CMPn\_M3). In addition, all three comparators' positive input 3 (CMPn\_P3) can be connected together to package pin CMP\_REF. Other inputs can be routed to package pins when the corresponding pin is configured for peripheral mode in the GPIO module.

### **General System Control Information**

## 5.7.2.1 Crossbar Switch Inputs

Table 15 lists the signal assignments of Crossbar Switch inputs.

### Specifications

### Specifications

| Parameter                                                                              | Symbol          | Min Typ |               | Мах | Unit |  |  |  |  |

|----------------------------------------------------------------------------------------|-----------------|---------|---------------|-----|------|--|--|--|--|

| Input impedance                                                                        | X <sub>IN</sub> | —       | See Figure 31 | _   | Ohms |  |  |  |  |

| AC Specifications <sup>9</sup> (gain of 1x, 2x, 4x and $f_{ADC} \le 10 \text{ MHz})^4$ |                 |         |               |     |      |  |  |  |  |

| Signal-to-noise ratio                                                                  | SNR             | _       | 59            |     | dB   |  |  |  |  |

| Total Harmonic Distortion                                                              | THD             | _       | 64            |     | dB   |  |  |  |  |

| Spurious Free Dynamic Range                                                            | SFDR            | _       | 65            |     | dB   |  |  |  |  |

| Signal-to-noise plus distortion                                                        | SINAD           | _       | 59            |     | dB   |  |  |  |  |

| Effective Number Of Bits                                                               | ENOB            | —       | 9.5           |     | Bits |  |  |  |  |

### Table 41. ADC Parameters<sup>1</sup> (continued)

1 All measurements were made at V\_{DD} = 3.3V, V\_{REFH} = 3.3V, and V\_{REFL} = ground Includes power-up of ADC and V\_{REF}

2

3 ADC clock cycles

4 Speed register setting must be 00 for ADC clock ≤ 5 MHz, 01 for 5 MHz < ADC clock ≤ 12 MHz, and 10 for ADC clock > 12 MHz

INL and DNL measured from  $V_{\text{IN}}$  =  $V_{\text{REFL}}$  to  $V_{\text{IN}}$  =  $V_{\text{REFH}}$ 5

6 LSB = Least Significant Bit = 0.806 mV at x1 gain

7 Pin groups are detailed following Table 17.

8 The current that can be injected or sourced from an unselected ADC signal input without affecting the performance of the ADC

9 ADC PGA gain is x1

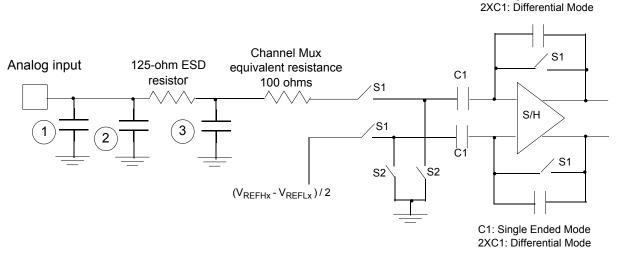

#### **Equivalent Circuit for ADC Inputs** 7.25.1

Figure 31 illustrates the ADC input circuit during sample and hold. S1 and S2 are always opened/closed at non-overlapping phases and operate at the ADC clock frequency. Equivalent input impedance, when the input is selected, is as follows:

### (2 x k / ADCClockRate x C<sub>gain</sub>) + 100 ohms + 125 ohms

where k =

- 1 for first sample .

- 6 for subsequent samples

and C<sub>gain</sub> is as described in note 4 below.

1. Parasitic capacitance due to package, pin-to-pin, and pin-to-package base coupling: 1.8 pF

### MC56F825x/MC56F824x Digital Signal Controller, Rev. 3

Eqn. 1

C1: Single Ended Mode

### **Ordering Information**

| Device    | Supply<br>Voltage | Package Type                         | Pin<br>Count | Frequency<br>(MHz) | Ambient<br>Temperature<br>Range      | Order Number <sup>1</sup>    |

|-----------|-------------------|--------------------------------------|--------------|--------------------|--------------------------------------|------------------------------|

| MC56F8245 | 3.0–3.6 V         | Low-Profile Quad Flat Pack<br>(LQFP) | 44           | 60                 | -40° to + 105° C<br>-40° to + 125° C | MC56F8245VLD<br>MC56F8245MLD |

| MC56F8246 | 3.0–3.6 V         | Low-Profile Quad Flat Pack<br>(LQFP) | 48           | 60                 | -40° to + 105° C<br>-40° to + 125° C | MC56F8246VLF<br>MC56F8246MLF |

| MC56F8247 | 3.0–3.6 V         | Low-Profile Quad Flat Pack<br>(LQFP) | 64           | 60                 | -40° to + 105° C<br>-40° to + 125° C | MC56F8247VLH<br>MC56F8247MLH |

| MC56F8255 | 3.0–3.6 V         | Low-Profile Quad Flat Pack<br>(LQFP) | 44           | 60                 | -40° to + 105° C<br>-40° to + 125° C | MC56F8255VLD<br>MC56F8255MLD |

| MC56F8256 | 3.0–3.6 V         | Low-Profile Quad Flat Pack<br>(LQFP) | 48           | 60                 | -40° to + 105° C<br>-40° to + 125° C | MC56F8256VLF<br>MC56F8256MLF |

| MC56F8257 | 3.0–3.6 V         | Low-Profile Quad Flat Pack<br>(LQFP) | 64           | 60                 | -40° to + 105° C<br>-40° to + 125° C | MC56F8257VLH<br>MC56F8257MLH |

### Table 46. MC56F825x/MC56F824x Ordering Information

<sup>1</sup> All of the packages are RoHS compliant.

| NOTES:                                                                                                                                                                |                                                                                                                                                            |              |                            |             |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------------------|-------------|--|

| 1. DIMENSIONS AND TO                                                                                                                                                  | DIMENSIONS AND TOLERANCING PER ASME Y14.5M-1994.                                                                                                           |              |                            |             |  |

| 2. CONTROLLING DIMENS                                                                                                                                                 | CONTROLLING DIMENSION: MILLIMETER.                                                                                                                         |              |                            |             |  |

| WITH THE LEAD WHE                                                                                                                                                     | DATUM PLANE AB IS LOCATED AT BOTTOM OF LEAD AND IS COINCIDENT<br>WITH THE LEAD WHERE THE LEAD EXITS THE PLASTIC BODY AT THE BOTTOM<br>OF THE PARTING LINE. |              |                            |             |  |

| 4. DATUMS T, U, AND                                                                                                                                                   | Z TO BE DETERN                                                                                                                                             | INED AT DAT  | UM PLANE AB.               |             |  |

| $\Delta$ dimensions to be (                                                                                                                                           | DETERMINED AT                                                                                                                                              | SEATING PLAN | NE AC.                     |             |  |

| 6. DIMENSIONS DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE<br>PROTRUSION IS 0.250 PER SIDE. DIMENSIONS DO INCLUDE<br>MOLD MISMATCH AND ARE DETERMINED AT DATUM PLANE AB. |                                                                                                                                                            |              |                            |             |  |

| A THIS DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED 0.350.                                                |                                                                                                                                                            |              |                            |             |  |

| 8. MINIMUM SOLDER PLATE THICKNESS SHALL BE 0.0076.                                                                                                                    |                                                                                                                                                            |              |                            |             |  |

| 9. EXACT SHAPE OF EA                                                                                                                                                  | ACH CORNER IS                                                                                                                                              | OPTIONAL.    |                            |             |  |

|                                                                                                                                                                       |                                                                                                                                                            |              |                            |             |  |

| FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED.                                                                                                                 | MECHANICA                                                                                                                                                  | LOUTLINE     | PRINT VERSION NO           | DT TO SCALE |  |

| TITLE:                                                                                                                                                                | 0 50 01704                                                                                                                                                 | DOCUMENT NO  | : 98ASH00962A              | REV: G      |  |

| LQFP, 48 LEAD,<br>(7.0 X 7.0                                                                                                                                          |                                                                                                                                                            | CASE NUMBER  |                            | 14 APR 2005 |  |

|                                                                                                                                                                       | /                                                                                                                                                          | STANDARD: JE | STANDARD: JEDEC MS-026-BBC |             |  |

Figure 33. 56F8246 and 56F8256 48-Pin LQFP Mechanical Information

Package Mechanical Outline Drawings

**Revision History**

# 11 Revision History

Table 47 summarizes changes to the document since the release of the previous version.

Table 47. Revision History

| Revision | Date       | Description                                                                                                                                                                                                                                                                                  |

|----------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |            | Table 46 on page 75: Added "M" orderable part numbers                                                                                                                                                                                                                                        |

| Rev. 3   | 2011-04-22 | Table 24 on page 55: Updated data for run, wait, and stop modes, and added data for standby and<br>powerdown modesTable 23 on page 54: Added minimum and maximum values for Internal Pull-Up Resistance<br>Renumbered sections: Section 9 (was 8.3), Section 10 (was 9), Section 11 (was 10) |

### Interrupt Vector Table

| Peripheral        | Vector<br>Number | Priority<br>Level | Vector Base<br>Address + | Interrupt Function                        |

|-------------------|------------------|-------------------|--------------------------|-------------------------------------------|

| CAN               | 25               | 0 - 2             | P:0x32                   | CAN Error Interrupt                       |

| CAN               | 26               | 0 - 2             | P:0x34                   | CAN Wake-Up Interrupt                     |

| QSCI1             | 27               | 0 - 2             | P:0x36                   | QSCI1 Receiver Overrun/Errors             |

| QSCI1             | 28               | 0 - 2             | P:0x38                   | QSCI1 Receiver Full                       |

| QSCI1             | 29               | 0 - 2             | P:0x3A                   | QSCI1 Transmitter Idle                    |

| QSCI1             | 30               | 0 - 2             | P:0x3C                   | QSCI1 Transmitter Empty                   |

| QSCI0             | 31               | 0 - 2             | P:0x3E                   | QSCI0 Receiver Overrun/Errors             |

| QSCI0             | 32               | 0 - 2             | P:0x40                   | QSCI0 Receiver Full                       |

| QSCI0             | 33               | 0 - 2             | P:0x42                   | QSCI0 Transmitter Idle                    |

| QSCI0             | 34               | 0 - 2             | P:0x44                   | QSCI0 Transmitter Empty                   |

| QSPI              | 35               | 0 - 2             | P:0x46                   | SPI Transmitter Empty                     |

| QSPI              | 36               | 0 - 2             | P:0x48                   | SPI Receiver Full                         |

| l <sup>2</sup> C1 | 37               | 0 - 2             | P:0x4A                   | I <sup>2</sup> C1 Interrupt               |

| l <sup>2</sup> C0 | 38               | 0 -2              | P:0x4C                   | I <sup>2</sup> C0 Interrupt               |

| TMRA3             | 39               | 0 -2              | P:0x4E                   | Quad Timer A, Channel 3 Interrupt         |

| TMRA2             | 40               | 0 -2              | P:0x50                   | Quad Timer A, Channel 2 Interrupt         |

| TMRA1             | 41               | 0 -2              | P:0x52                   | Quad Timer A, Channel 1 Interrupt         |

| TMRA0             | 42               | 0 -2              | P:0x54                   | Quad Timer A, Channel 0 Interrupt         |

| eFlexPWM          | 43               | 0 -2              | P:0x56                   | PWM Fault                                 |

| eFlexPWM          | 44               | 0 -2              | P:0x58                   | PWM Reload Error                          |

| eFlexPWM          | 45               | 0 -2              | P:0x5A                   | PWM Sub-Module 3 Reload                   |

| eFlexPWM          | 46               | 0 -2              | P:0x5C                   | PWM Sub-Module 3 input capture            |

| eFlexPWM          | 47               | 0 -2              | P:0x5E                   | PWM Sub-Module 3 Compare                  |

| eFlexPWM          | 48               | 0 -2              | P:0x60                   | PWM Sub-Module 2 Reload                   |

| eFlexPWM          | 49               | 0 -2              | P:0x62                   | PWM Sub-Module 2 Compare                  |

| eFlexPWM          | 50               | 0 -2              | P:0x64                   | PWM Sub-Module 1 Reload                   |

| eFlexPWM          | 51               | 0 -2              | P:0x66                   | PWM Sub-Module 1 Compare                  |

| eFlexPWM          | 52               | 0 -2              | P:0x68                   | PWM Sub-Module 0 Reload                   |

| eFlexPWM          | 53               | 0 -2              | P:0x6A                   | PWM Sub-Module 0Compare                   |

| FM                | 54               | 0 -2              | P:0x6C                   | Flash Memory Access Error                 |

| FM                | 55               | 0 -2              | P:0x6E                   | Flash Memory Programming Command Complete |

| FM                | 56               | 0 -2              | P:0x70                   | Flash Memory Buffer Empty Request         |

| CMPC              | 57               | 0 - 2             | P:0x72                   | Comparator C Rising/Falling Flag          |

| CMPB              | 58               | 0 - 2             | P:0x74                   | Comparator B Rising/Falling Flag          |

| Table 48. Interrupt Vector Table Contents <sup>1</sup> ( | (continued) |

|----------------------------------------------------------|-------------|

|----------------------------------------------------------|-------------|

### **Interrupt Vector Table**

| Peripheral | Vector<br>Number | Priority<br>Level | Vector Base<br>Address + | Interrupt Function               |

|------------|------------------|-------------------|--------------------------|----------------------------------|

| CMPA       | 59               | 0 - 2             | P:0x76                   | Comparator A Rising/Falling Flag |

| GPIOF      | 60               | 0 - 2             | P:0x78                   | GPIOF Interrupt                  |

| GPIOE      | 61               | 0 - 2             | P:0x7A                   | GPIOE Interrupt                  |

| GPIOD      | 62               | 0 - 2             | P:0x7C                   | GPIOD Interrupt                  |

| GPIOC      | 63               | 0 - 2             | P:0x7E                   | GPIOC Interrupt                  |

| GPIOB      | 64               | 0 - 2             | P:0x80                   | GPIOB Interrupt                  |

| GPIOA      | 65               | 0 - 2             | P:0x82                   | GPIOA Interrupt                  |

| SWILP      | 66               | -1                | P:0x84                   | SW Interrupt Low Priority        |

### Table 48. Interrupt Vector Table Contents<sup>1</sup> (continued)

<sup>1</sup> Two words are allocated for each entry in the vector table. This does not allow the full address range to be referenced from the vector table, providing only 19 bits of address.

<sup>2</sup> If the VBA is set to the reset value, the first two locations of the vector table overlay the chip reset addresses because the reset address would match the base of this vector table.

#### How to Reach Us:

Home Page: www.freescale.com

#### Web Support:

http://www.freescale.com/support

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 +1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

For Literature Requests Only: Freescale Semiconductor Literature Distribution Center 1-800-441-2447 or +1-303-675-2140 Fax: +1-303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

Document Number: MC56F825X Rev. 3 04/2011 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics as their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Freescale, the Freescale logo, and CodeWarrior are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. Processor Expert is a trademark of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2009-2011. All rights reserved.