Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                     |

|----------------------------|------------------------------------------------------------|

| Core Processor             | CPU32                                                      |

| Core Size                  | 32-Bit Single-Core                                         |

| Speed                      | 20MHz                                                      |

| Connectivity               | EBI/EMI, UART/USART                                        |

| Peripherals                | -                                                          |

| Number of I/O              | 47                                                         |

| Program Memory Size        | -                                                          |

| Program Memory Type        | ROMIess                                                    |

| EEPROM Size                | -                                                          |

| RAM Size                   | 1K x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                  |

| Data Converters            | A/D 8x8/10b                                                |

| Oscillator Type            | External                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                          |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 132-BQFP Bumpered                                          |

| Supplier Device Package    | 132-PQFP (24.13x24.13)                                     |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc68334gceh20 |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

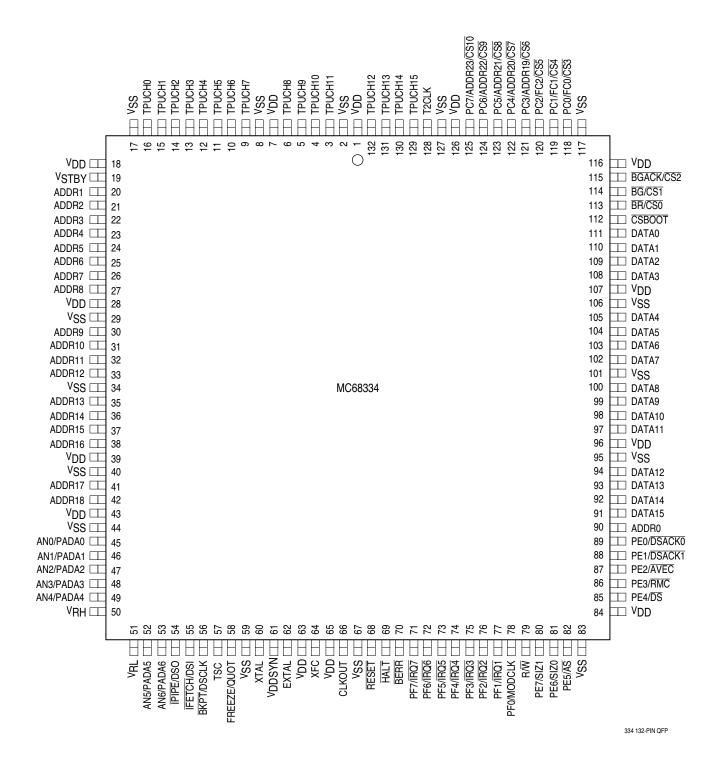

## **1.3 Pin Assignments**

Figure 2 MC68334 132-Pin QFP Pin Assignments

# **2 Signal Descriptions**

## 2.1 Pin Characteristics

The following table shows MCU pins and their characteristics. All inputs detect CMOS logic levels. All inputs can be put in a high-impedance state, but the method of doing this differs depending upon pin function. Refer to the table MCU Driver Types for a description of output drivers. An entry in the discrete I/O column of the MCU Pin Characteristics table indicates that a pin has an alternate I/O function. The port designation is given when it applies. Refer to the MCU Block Diagram for information about port organization.

| Pin<br>Mnemonic              | Output<br>Driver | Input<br>Synchronized | Input<br>Hysteresis | Discrete<br>I/O | Port<br>Designation |

|------------------------------|------------------|-----------------------|---------------------|-----------------|---------------------|

| ADDR23/CS10/ECLK             | А                | Y                     | N                   |                 | _                   |

| ADDR[22:19]/CS[9:6]          | А                | Y                     | N                   | 0               | PC[6:3]             |

| ADDR[18:0]                   | А                | Y                     | N                   |                 | —                   |

| AN[6:0]                      |                  | Y1                    | Y                   | I               | PADA[6:0]           |

| ĀS                           | В                | Y                     | N                   | I/O             | PE5                 |

| AVEC                         | В                | Y                     | N                   | I/O             | PE2                 |

| BERR <sup>2</sup>            | В                | Y                     | N                   | —               | —                   |

| BG/CS1                       | В                | _                     | _                   |                 | _                   |

| BGACK/CS2                    | В                | Y                     | N                   |                 | _                   |

| BKPT/DSCLK                   | _                | Y                     | Y                   | _               | _                   |

| BR/CS0                       | В                | Y                     | N                   | _               | _                   |

| CLKOUT                       | А                | _                     | —                   | _               | —                   |

| CSBOOT                       | В                | —                     | —                   |                 | —                   |

| DATA[15:0] <sup>1</sup>      | Aw               | Y                     | N                   | —               | —                   |

| DS                           | В                | Y                     | N                   | I/O             | PE4                 |

| DSACK1                       | В                | Y                     | N                   | I/O             | PE1                 |

| DSACK0                       | В                | Y                     | N                   | I/O             | PE0                 |

| DSI/IFETCH                   | А                | Y                     | Y                   | _               | —                   |

| DSO/IPIPE                    | А                | _                     | —                   | —               | —                   |

| EXTAL <sup>3</sup>           | —                | —                     | —                   | —               | —                   |

| FC[2:0]/CS[5:3]              | А                | Y                     | —                   | 0               | PC[2:0]             |

| FREEZE/QUOT                  | А                | _                     | —                   | _               | —                   |

| HALT <sup>2</sup>            | Во               | Y                     | N                   | —               | —                   |

| IRQ[7:1]                     | В                | Y                     | Y                   | I/O             | PF[7:1]             |

| MODCLK <sup>1</sup>          | В                | Y                     | N                   | I/O             | PF0                 |

| R/W                          | Α                | Y                     | N                   |                 | _                   |

| RESET                        | Во               | Y                     | Y                   |                 | _                   |

| RMC                          | В                | Y                     | N                   | I/O             | PE3                 |

| SIZ[1:0]                     | В                | Y                     | N                   | I/O             | PE[7:6]             |

| TPUCH[15:0]                  | А                | Y                     | Y                   | —               | —                   |

| TSC                          |                  | Y                     | Y                   | _               | _                   |

| T2CLK                        | А                | Y                     | Y                   |                 |                     |

| V <sub>RH</sub> <sup>4</sup> | _                |                       | _                   | _               | —                   |

| V <sub>RL</sub> 4            |                  | -                     | —                   |                 | _                   |

| XFC <sup>3</sup>             | _                |                       | —                   |                 | —                   |

| XTAL <sup>3</sup>            |                  | —                     | —                   | —               | —                   |

| R/W                          | А                | Y                     | N                   |                 |                     |

## Table 7 SIM Address Map

| Access | Address  | 15 8 7 0                       |

|--------|----------|--------------------------------|

| S      | \$YFFA5E | CHIP-SELECT OPTION 4 (CSOR4)   |

| S      | \$YFFA60 | CHIP-SELECT BASE 5 (CSBAR5)    |

| S      | \$YFFA62 | CHIP-SELECT OPTION 5 (CSOR5)   |

| S      | \$YFFA64 | CHIP-SELECT BASE 6 (CSBAR6)    |

| S      | \$YFFA66 | CHIP-SELECT OPTION 6 (CSOR6)   |

| S      | \$YFFA68 | CHIP-SELECT BASE 7 (CSBAR7)    |

| S      | \$YFFA6A | CHIP-SELECT OPTION 7 (CSOR7)   |

| S      | \$YFFA6C | CHIP-SELECT BASE 8 (CSBAR8)    |

| S      | \$YFFA6E | CHIP-SELECT OPTION 8 (CSOR8)   |

| S      | \$YFFA70 | CHIP-SELECT BASE 9 (CSBAR9)    |

| S      | \$YFFA72 | CHIP-SELECT OPTION 9 (CSOR9)   |

| S      | \$YFFA74 | CHIP-SELECT BASE 10 (CSBAR10)  |

| S      | \$YFFA76 | CHIP-SELECT OPTION 10 (CSOR10) |

Y = M111, where M is the logic state of the module mapping (MM) bit in the SIMCR.

## 3.2 System Configuration and Protection Block

This functional block provides configuration control for the entire MCU. It also performs interrupt arbitration, bus monitoring, and system test functions. MCU system protection includes a bus monitor, a HALT monitor, a spurious interrupt monitor, and a software watchdog timer. These functions have been made integral to the microcontroller to reduce the number of external components in a complete control system.

## 3.2.2 System Protection Control Register

The system protection control register controls system monitor functions, software watchdog clock prescaling, and bus monitor timing. This register can be written only once following power-on or reset, but can be read at any time.

| 5 | SYPCR | — Sys | stem P | rotectio | on Cor | trol Re | gister |   |     |        |    |    |     | :   | \$YFF | A21 |

|---|-------|-------|--------|----------|--------|---------|--------|---|-----|--------|----|----|-----|-----|-------|-----|

|   | 15    | 14    | 13     | 12       | 11     | 10      | 9      | 8 | 7   | 6      | 5  | 4  | 3   | 2   | 1     | 0   |

| Γ |       |       |        | NOT U    | SED    |         |        |   | SWE | SWP    | SV | VT | HME | BME | BN    | ΛT  |

|   | RESE  | ET:   |        |          |        |         |        |   |     |        |    |    |     |     |       |     |

|   |       |       |        |          |        |         |        |   | 1   | MODCLK | 0  | 0  | 0   | 0   | 0     | 0   |

SWE — Software Watchdog Enable

0 = Software watchdog disabled

1 = Software watchdog enabled

## SWP — Software Watchdog Prescale

This bit controls the value of the software watchdog prescaler.

- 0 = Software watchdog clock not prescaled

- 1 = Software watchdog clock prescaled by 512

## SWT[1:0] — Software Watchdog Timing

This field selects the divide ratio used to establish software watchdog time-out period. The following table gives the ratio for each combination of SWP and SWT bits.

| SWP | SWT | Ratio |  |  |

|-----|-----|-------|--|--|

| 0   | 00  | 29    |  |  |

| 0   | 01  | 211   |  |  |

| 0   | 10  | 213   |  |  |

| 0   | 11  | 215   |  |  |

| 1   | 00  | 218   |  |  |

| 1   | 01  | 220   |  |  |

| 1   | 10  | 222   |  |  |

| 1   | 11  | 224   |  |  |

#### HME — Halt Monitor Enable

0 = Disable halt monitor function

1 = Enable halt monitor function

BME — Bus Monitor External Enable

- 0 = Disable bus monitor function for an internal to external bus cycle.

- 1 = Enable bus monitor function for an internal to external bus cycle.

#### BMT[1:0] — Bus Monitor Timing

This field selects a bus monitor time-out period as shown in the following table.

| BMT | Bus Monitor Time-out Period |

|-----|-----------------------------|

| 00  | 64 System Clocks            |

| 01  | 32 System Clocks            |

| 10  | 16 System Clocks            |

| 11  | 8 System Clocks             |

#### 3.2.3 Bus Monitor

The internal bus monitor checks for excessively long DSACK response times during normal bus cycles and for excessively long DSACK or AVEC response times during interrupt acknowledge cycles. The monitor asserts BERR if response time is excessive.

DSACK and AVEC response times are measured in clock cycles. The maximum allowable response time can be selected by setting the BMT field.

The monitor does not check DSACK response on the external bus unless the CPU initiates the bus cycle. The BME bit in the SYPCR enables the internal bus monitor for internal to external bus cycles. If a system contains external bus masters, an external bus monitor must be implemented and the internal to external bus monitor option must be disabled.

#### 3.2.4 Halt Monitor

The halt monitor responds to an assertion of  $\overline{HALT}$  on the internal bus. A flag in the reset status register (RSR) indicates that the last reset was caused by the halt monitor. The halt monitor reset can be inhibited by the HME bit in the SYPCR.

#### 3.2.5 Spurious Interrupt Monitor

The spurious interrupt monitor issues BERR if no interrupt arbitration occurs during an interrupt-acknowledge cycle.

#### 3.2.6 Software Watchdog

The software watchdog is controlled by SWE in the SYPCR. Once enabled, the watchdog requires that a service sequence be written to SWSR on a periodic basis. If servicing does not take place, the watchdog times out and issues a reset. This register can be written at any time, but returns zeros when read.

| Ş | SWSR — Software Service Register |     |    |       |     |    |   |   |   |   | \$YF | FA27 |   |   |   |   |

|---|----------------------------------|-----|----|-------|-----|----|---|---|---|---|------|------|---|---|---|---|

|   | 15                               | 14  | 13 | 12    | 11  | 10 | 9 | 8 | 7 | 6 | 5    | 4    | 3 | 2 | 1 | 0 |

| Γ |                                  |     |    | NOT U | SED |    |   |   | 0 | 0 | 0    | 0    | 0 | 0 | 0 | 0 |

| - | RES                              | ET: |    |       |     |    |   |   |   |   |      |      |   |   |   |   |

|   |                                  |     |    |       |     |    |   |   | 0 | 0 | 0    | 0    | 0 | 0 | 0 | 0 |

Register shown with read value

Perform a software watchdog service sequence as follows:

- Write \$55 to SWSR.

- Write \$AA to SWSR.

Both writes must occur before time-out in the order listed, but any number of instructions can be executed between the two writes.

The watchdog clock rate is affected by SWP and SWT in SYPCR. When SWT[1:0] are modified, a watchdog service sequence must be performed before the new time-out period takes effect.

The reset value of SWP is affected by the state of the MODCLK pin on the rising edge of reset, as shown in the following table.

| MODCLK | SWP |  |  |  |  |

|--------|-----|--|--|--|--|

| 0      | 1   |  |  |  |  |

| 1      | 0   |  |  |  |  |

mum limp frequency does not exceed one half maximum system clock when X = 0, or maximum system clock frequency when X = 1.

When RSTEN is set, the SIM resets the MCU.

The limp status bit (SLIMP) in SYNCR indicates whether the synthesizer has a reference signal. It is set when a reference failure is detected.

#### 3.3.6 Clock Control

The clock control circuits determine system clock frequency and clock operation under special circumstances, such as following loss of synthesizer reference or during low-power operation. Clock source is determined by the logic state of the MODCLK pin during reset.

| SYNCR | — Clo | ock S | ynthe | sizer ( | Control | Regis | ter |      |   |   |       |       |       | \$YF  | FFA04 |

|-------|-------|-------|-------|---------|---------|-------|-----|------|---|---|-------|-------|-------|-------|-------|

| 15    | 14    | 13    | 12    | 11      | 10      | 9     | 8   | 7    | 6 | 5 | 4     | 3     | 2     | 1     | 0     |

| W     | Х     |       |       |         | Y       |       |     | EDIV | 0 | 0 | SLIMP | SLOCK | RSTEN | STSIM | STEXT |

| RESE  | T:    | •     |       |         |         |       |     |      |   |   |       |       |       | •     |       |

| 0     | 0     | 1     | 1     | 1       | 1       | 1     | 1   | 0    | 0 | 0 | U     | U     | 0     | 0     | 0     |

When the on-chip clock synthesizer is used, system clock frequency is controlled by the bits in the upper byte of SYNCR. Bits in the lower byte show status of or control operation of internal and external clocks. The SYNCR can be read or written only when the CPU is operating at the supervisor privilege level.

#### W — Frequency Control (VCO)

This bit controls a prescaler tap in the synthesizer feedback loop. Setting the bit increases the VCO speed by a factor of four. VCO relock delay is required.

#### X — Frequency Control Bit (Prescale)

This bit controls a divide by two prescaler that is not in the synthesizer feedback loop. Setting the bit doubles clock speed without changing the VCO speed. There is no VCO relock delay.

#### Y[5:0] — Frequency Control (Counter)

The Y field controls the modulus down counter in the synthesizer feedback loop, causing it to divide by a value of Y + 1. Values range from 0 to 63. VCO relock delay is required.

#### EDIV — E Clock Divide Rate

0 = ECLK frequency is system clock divided by 8.

1 = ECLK frequency is system clock divided by 16.

ECLK is an external M6800 bus clock available on pin ADDR23. Refer to **3.5 Chip Selects** for more information.

#### SLIMP — Limp Mode Flag

0 = External crystal is VCO reference.

1 = Loss of crystal reference.

When the on-chip synthesizer is used, loss of reference frequency causes SLIMP to be set. The VCO continues to run using the base control voltage. Maximum limp frequency is maximum specified system clock frequency. X-bit state affects limp frequency.

## SLOCK — Synthesizer Lock Flag

0 = VCO is enabled, but has not locked.

1 = VCO has locked on the desired frequency (or system clock is external).

The MCU maintains reset state until the synthesizer locks, but SLOCK does not indicate synthesizer lock status until after the user writes to SYNCR.

## RSTEN — Reset Enable

- 0 = Loss of crystal causes the MCU to operate in limp mode.

- 1 = Loss of crystal causes system reset.

- STSIM Stop Mode SIM Clock

- 0 = When LPSTOP is executed, the SIM clock is driven from the crystal oscillator and the VCO is turned off to conserve power.

- 1 = When LPSTOP is executed, the SIM clock is driven from the VCO.

### STEXT — Stop Mode External Clock

- 0 = When LPSTOP is executed, the CLKOUT signal is held negated to conserve power.

- 1 = When LPSTOP is executed, the CLKOUT signal is driven from the SIM clock, as determined by the state of the STSIM bit.

## 3.4 External Bus Interface

The external bus interface (EBI) transfers information between the internal MCU bus and external devices. The external bus has 24 address lines and 16 data lines.

The EBI provides dynamic sizing between 8-bit and 16-bit data accesses. It supports byte, word, and long-word transfers. Ports are accessed through the use of asynchronous cycles controlled by the data transfer (SIZ1 and SIZ0) and data size acknowledge pins (DSACK1 and DSACK0). Multiple bus cycles may be required for a transfer to or from an 8-bit port.

Port width is the maximum number of bits accepted or provided during a bus transfer. External devices must follow the handshake protocol described below. Control signals indicate the beginning of the cycle, the address space, the size of the transfer, and the type of cycle. The selected device controls the length of the cycle. Strobe signals, one for the address bus and another for the data bus, indicate the validity of an address and provide timing information for data. The EBI operates in an asynchronous mode for any port width.

To add flexibility and minimize the necessity for external logic, MCU chip-select logic can be synchronized with EBI transfers. Chip-select logic can also provide internally-generated bus control signals for these accesses. Refer to **3.5 Chip Selects** for more information.

## 3.4.1 Bus Control Signals

The CPU initiates a bus cycle by driving the address, size, function code, and read/write outputs. At the beginning of the cycle, size signals SIZ0 and SIZ1 are driven along with the function code signals. The size signals indicate the number of bytes remaining to be transferred during an operand cycle. They are valid while the address strobe ( $\overline{AS}$ ) is asserted. The following table shows SIZ0 and SIZ1 encoding. The read/write ( $R/\overline{W}$ ) signal determines the direction of the transfer during a bus cycle. This signal changes state, when required, at the beginning of a bus cycle, and is valid while  $\overline{AS}$  is asserted.  $R/\overline{W}$  only changes state when a write cycle is preceded by a read cycle or vice versa. The signal can remain low for two consecutive write cycles.

| SIZ1 | SIZ0 | Transfer Size |

|------|------|---------------|

| 0    | 1    | Byte          |

| 1    | 0    | Word          |

| 1    | 1    | 3 Byte        |

| 0    | 0    | Long Word     |

## **Table 9 Size Signal Encoding**

## 3.4.2 Function Codes

The CPU32 automatically generates function code signals FC[2:0]. The function codes can be considered address extensions that automatically select one of eight address spaces to which an address applies. These spaces are designated as either user or supervisor, and program or data spaces. Address space seven is designated CPU space. CPU space is used for control information not normally associated with read or write bus cycles. Function codes are valid while  $\overline{AS}$  is asserted.

| FC2 | FC1 | FC0 | Address Space            |

|-----|-----|-----|--------------------------|

| 0   | 0   | 0   | Reserved                 |

| 0   | 0   | 1   | User Data Space          |

| 0   | 1   | 0   | User Program Space       |

| 0   | 1   | 1   | Reserved                 |

| 1   | 0   | 0   | Reserved                 |

| 1   | 0   | 1   | Supervisor Data Space    |

| 1   | 1   | 0   | Supervisor Program Space |

| 1   | 1   | 1   | CPU Space                |

#### Table 10 CPU32 Address Space Encoding

#### 3.4.3 Address Bus

Address bus signals ADDR[23:0] define the address of the most significant byte to be transferred during a bus cycle. The MCU places the address on the bus at the beginning of a bus cycle. The address is valid while  $\overline{\text{AS}}$  is asserted.

#### 3.4.4 Address Strobe

AS is a timing signal that indicates the validity of an address on the address bus and the validity of many control signals. It is asserted one-half clock after the beginning of a bus cycle.

#### 3.4.5 Data Bus

Data bus signals DATA[15:0] make up a bidirectional, nonmultiplexed parallel bus that transfers data to or from the MCU. A read or write operation can transfer 8 or 16 bits of data in one bus cycle. During a read cycle, the data is latched by the MCU on the last falling edge of the clock for that bus cycle. For a write cycle, all 16 bits of the data bus are driven, regardless of the port width or operand size. The MCU places the data on the data bus one-half clock cycle after  $\overline{AS}$  is asserted in a write cycle.

#### 3.4.6 Data Strobe

Data strobe ( $\overline{DS}$ ) is a timing signal. For a read cycle, the MCU asserts  $\overline{DS}$  to signal an external device to place data on the bus.  $\overline{DS}$  is asserted at the same time as  $\overline{AS}$  during a read cycle. For a write cycle,  $\overline{DS}$  signals an external device that data on the bus is valid. The MCU asserts  $\overline{DS}$  one full clock cycle after the assertion of  $\overline{AS}$  during a write cycle.

#### 3.4.7 Bus Cycle Termination Signals

During bus cycles, external devices assert the data transfer and size acknowledge signals (DSACK1 and DSACK0). During a read cycle, the signals tell the MCU to terminate the bus cycle and to latch data. During a write cycle, the signals indicate that an external device has successfully stored data and that the cycle can end. These signals also indicate to the MCU the size of the port for the bus cycle just completed. (Refer to **3.4.9 Dynamic Bus Sizing**).

The bus error (BERR) signal is also a bus cycle termination indicator and can be used in the absence of DSACK1 and DSACK0 to indicate a bus error condition. It can also be asserted in conjunction with these signals, provided it meets the appropriate timing requirements. The internal bus monitor can be used to generate the BERR signal for internal and internal-to-external transfers. When BERR and HALT are asserted simultaneously, the CPU takes a bus error exception.

## 3.4.10 Operand Alignment

The data multiplexer establishes the necessary connections for different combinations of address and data sizes. The multiplexer takes the two bytes of the 16-bit bus and routes them to their required positions. Positioning of bytes is determined by the size and address outputs. SIZ1 and SIZ0 indicate the remaining number of bytes to be transferred during the current bus cycle. The number of bytes transferred is equal to or less than the size indicated by SIZ1 and SIZ0, depending on port width.

ADDR0 also affects the operation of the data multiplexer. During an operand transfer, ADDR[23:1] indicate the word base address of the portion of the operand to be accessed, and ADDR0 indicates the byte offset from the base.

## 3.4.11 Misaligned Operands

CPU32 processor architecture uses a basic operand size of 16 bits. An operand is misaligned when it overlaps a word boundary. This is determined by the value of ADDR0. When ADDR0 = 0 (an even address), the address is on a word and byte boundary. When ADDR0 = 1 (an odd address), the address is on a byte boundary only. A byte operand is aligned at any address; a word or long-word operand is misaligned at an odd address. The MCU does not support misaligned operand transfers.

The largest amount of data that can be transferred by a single bus cycle is an aligned word. If the MCU transfers a long-word operand via a 16-bit port, the most significant operand word is transferred on the first bus cycle and the least significant operand word on a following bus cycle.

### 3.4.12 Operand Transfer Cases

The following table summarizes how operands are aligned for various types of transfers. OPn entries are portions of a requested operand that are read or written during a bus cycle and are defined by SIZ1, SIZ0, and ADDR0 for that bus cycle.

| Transfer Case                                      | SIZ1 | SIZ0 | ADDR0 | DSACK1 | DSACK0 | DATA<br>[15:8] | DATA<br>[7:0]      |

|----------------------------------------------------|------|------|-------|--------|--------|----------------|--------------------|

| Byte to 8-Bit Port (Even/Odd)                      | 0    | 1    | Х     | 1      | 0      | OP0            | (OP0) <sup>1</sup> |

| Byte to 16-Bit Port (Even)                         | 0    | 1    | 0     | 0      | Х      | OP0            | (OP0)              |

| Byte to 16-Bit Port (Odd)                          | 0    | 1    | 1     | 0      | Х      | (OP0)          | OP0                |

| Word to 8-Bit Port (Aligned)                       | 1    | 0    | 0     | 1      | 0      | OP0            | (OP1)              |

| Word to 8-Bit Port (Misaligned) <sup>2</sup>       | 1    | 0    | 1     | 1      | 0      | OP0            | (OP0)              |

| Word to 16-Bit Port (Aligned)                      | 1    | 0    | 0     | 0      | Х      | OP0            | OP1                |

| Word to 16-Bit Port (Misaligned) <sup>2</sup>      | 1    | 0    | 1     | 0      | Х      | (OP0)          | OP0                |

| 3 Byte to 8-Bit Port (Aligned) <sup>3</sup>        |      | 1    | 0     | 1      | 0      | OP0            | (OP1)              |

| 3 Byte to 8-Bit Port (Misaligned) <sup>2, 3</sup>  |      | 1    | 1     | 1      | 0      | OP0            | (OP0)              |

| 3 Byte to 16-Bit Port (Aligned) <sup>3</sup>       | 1    | 1    | 0     | 0      | Х      | OP0            | OP1                |

| 3 Byte to 16-Bit Port (Misaligned) <sup>2, 3</sup> | 1    | 1    | 1     | 0      | Х      | (OP0)          | OP0                |

| Long Word to 8-Bit Port (Aligned)                  |      | 0    | 0     | 1      | 0      | OP0            | (OP1)              |

| Long Word to 8-Bit Port (Misaligned) <sup>2</sup>  |      | 0    | 1     | 1      | 0      | OP0            | (OP0)              |

| Long Word to 16-Bit Port (Aligned)                 |      | 0    | 0     | 0      | Х      | OP0            | OP1                |

| Long Word to 16-Bit Port (Misaligned) <sup>2</sup> | 1    | 0    | 1     | 0      | Х      | (OP0)          | OP0                |

## Table 12 Operand Alignment

1. Operands in parentheses are ignored by the CPU32 during read cycles.

2. The CPU32 does not support misaligned word or long-word transfers.

3. Three-byte transfer cases occur only as a result of a long word to byte transfer.

CSORBT, the option register for CSBOOT, contains special reset values that support bootstrap operations from peripheral memory devices.

The following bit descriptions apply to both CSORBT and CSOR[10:0] option registers.

#### MODE — Asynchronous/Synchronous Mode

- 0 = Asynchronous mode selected (chip-select assertion determined by internal or external bus control signals)

- 1 = Synchronous mode selected (chip-select assertion synchronized with ECLK signal) In asynchronous mode, the chip select is asserted synchronized with  $\overline{AS}$  or  $\overline{DS}$ .

The DSACK field is not used in synchronous mode because a bus cycle is only performed as a synchronous operation. When a match condition occurs on a chip select programmed for synchronous operation, the chip select signals the EBI that an ECLK cycle is pending.

#### BYTE — Upper/Lower Byte Option

This field is used only when the chip-select 16-bit port option is selected in the pin assignment register. The following table lists upper/lower byte options.

| Byte | Description |

|------|-------------|

| 00   | Disable     |

| 01   | Lower Byte  |

| 10   | Upper Byte  |

| 11   | Both Bytes  |

#### $R/\overline{W}$ — Read/Write

This field causes a chip select to be asserted only for a read, only for a write, or for both read and write. Refer to the following table for options available.

| R/W | Description |

|-----|-------------|

| 00  | Reserved    |

| 01  | Read Only   |

| 10  | Write Only  |

| 11  | Read/Write  |

STRB — Address Strobe/Data Strobe

0 = Address strobe

1 = Data strobe

This bit controls the timing for assertion of a chip select in asynchronous mode. Selecting address strobe causes chip select to be asserted synchronized with address strobe. Selecting data strobe causes chip select to be asserted synchronized with data strobe.

#### DSACK — Data and Size Acknowledge

This field specifies the source of DSACK in asynchronous mode. It also allows the user to adjust bus timing with internal DSACK generation by controlling the number of wait states that are inserted to optimize bus speed in a particular application. The following table shows the DSACK field encoding. The fast termination encoding (1110) is used for two-cycle access to external memory.

| DSACK | Description      |

|-------|------------------|

| 0000  | No Wait States   |

| 0001  | 1 Wait State     |

| 0010  | 2 Wait States    |

| 0011  | 3 Wait States    |

| 0100  | 4 Wait States    |

| 0101  | 5 Wait States    |

| 0110  | 6 Wait States    |

| 0111  | 7 Wait States    |

| 1000  | 8 Wait States    |

| 1001  | 9 Wait States    |

| 1010  | 10 Wait States   |

| 1011  | 11 Wait States   |

| 1100  | 12 Wait States   |

| 1101  | 13 Wait States   |

| 1110  | Fast Termination |

| 1111  | External DSACK   |

## SPACE — Address Space

Use this option field to select an address space for the chip-select logic. The CPU32 normally operates in supervisor or user space, but interrupt acknowledge cycles must take place in CPU space.

| Space | Address Space         |

|-------|-----------------------|

| 00    | CPU Space             |

| 01    | User Space            |

| 10    | Supervisor Space      |

| 11    | Supervisor/User Space |

## IPL — Interrupt Priority Level

If the space field is set for CPU space (00), chip-select logic can be used for interrupt acknowledge. During an interrupt acknowledge cycle, the priority level on address lines ADDR[3:1] is compared to the value in the IPL field. If the values are the same, a chip select is asserted, provided that other option register conditions are met. The following table shows IPL field encoding.

| IPL | Description |

|-----|-------------|

| 000 | Any Level   |

| 001 | IPL1        |

| 010 | IPL2        |

| 011 | IPL3        |

| 100 | IPL4        |

| 101 | IPL5        |

| 110 | IPL6        |

| 111 | IPL7        |

This field only affects the response of chip selects and does not affect interrupt recognition by the CPU. Any level means that chip select is asserted regardless of the level of the interrupt acknowledge cycle.

#### AVEC — Autovector Enable

0 = External interrupt vector enabled

1 = Autovector enabled

This field selects one of two methods of acquiring an interrupt vector number during an external interrupt acknowledge cycle.

## 3.8 Interrupts

Interrupt recognition and servicing involve complex interaction between the central processing unit, the system integration module, and a device or module requesting interrupt service.

The CPU32 provides eight levels of interrupt priority. All interrupts with priorities less than seven can be masked by the interrupt priority (IP) field in status register.

There are seven interrupt request signals ( $\overline{IRQ[7:1]}$ ). These signals are used internally on the IMB, and there are corresponding pins for external interrupt service requests. The CPU treats all interrupt requests as though they come from internal modules — external interrupt requests are treated as interrupt service requests from the SIM. Each of the interrupt request signals corresponds to an interrupt priority level. IRQ1 has the lowest priority and IRQ7 the highest.

Interrupt recognition is determined by interrupt priority level and interrupt priority mask value. The interrupt priority mask consists of three bits in the CPU32 status register. Binary values %000 to %111 provide eight priority masks. Masks prevent an interrupt request of a priority less than or equal to the mask value from being recognized and processed. IRQ7, however, is always recognized, even if the mask value is %111.

IRQ[7:1] are active-low level-sensitive inputs. The low on the pin must remain asserted until an interrupt acknowledge cycle corresponding to that level is detected.

$\overline{IRQ7}$  is transition-sensitive as well as level-sensitive: a level-7 interrupt is not detected unless a falling edge transition is detected on the  $\overline{IRQ7}$  line. This prevents redundant servicing and stack overflow. A nonmaskable interrupt is generated each time  $\overline{IRQ7}$  is asserted as well as each time the priority mask changes from%111 to a lower number while  $\overline{IRQ7}$  is asserted.

Interrupt requests are sampled on consecutive falling edges of the system clock. Interrupt request input circuitry has hysteresis: to be valid, a request signal must be asserted for at least two consecutive clock periods. Valid requests do not cause immediate exception processing, but are left pending. Pending requests are processed at instruction boundaries or when exception processing of higher-priority exceptions is complete.

The CPU32 does not latch the priority of a pending interrupt request. If an interrupt source of higher priority makes a service request while a lower priority request is pending, the higher priority request is serviced. If an interrupt request with a priority equal to or lower than the current IP mask value is made, the CPU32 does not recognize the occurrence of the request. If simultaneous interrupt requests of different priorities are made, and both have a priority greater than the mask value, the CPU32 recognizes the higher-level request.

## 3.8.1 Interrupt Acknowledge and Arbitration

When the CPU32 detects one or more interrupt requests of a priority higher than the interrupt priority mask value, it places the interrupt request level on the address bus and initiates a CPU space read cycle. The request level serves two purposes: it is decoded by modules or external devices that have requested interrupt service, to determine whether the current interrupt acknowledge cycle pertains to them, and it is latched into the interrupt priority mask field in the CPU32 status register, to preclude further interrupts of lower priority during interrupt service.

Modules or external devices that have requested interrupt service must decode the interrupt priority mask value placed on the address bus during the interrupt acknowledge cycle and respond if the priority of the service request corresponds to the mask value. However, before modules or external devices respond, interrupt arbitration takes place.

Arbitration is performed by means of serial contention between values stored in individual module interrupt arbitration (IARB) fields. Each module that can make an interrupt service request, including the SIM, has an IARB field in its configuration register. IARB fields can be assigned values from %0000 to

%1111. In order to implement an arbitration scheme, each module that can initiate an interrupt service request must be assigned a unique, non-zero IARB field value during system initialization. Arbitration priorities range from %0001 (lowest) to %1111 (highest) — if the CPU recognizes an interrupt service request from a source that has an IARB field value of %0000, a spurious interrupt exception is processed.

## WARNING

Do not assign the same arbitration priority to more than one module. When two or more IARB fields have the same nonzero value, the CPU32 interprets multiple vector numbers at the same time, with unpredictable consequences.

Because the EBI manages external interrupt requests, the SIM IARB value is used for arbitration between internal and external interrupt requests. The reset value of IARB for the SIM is %1111, and the reset IARB value for all other modules is %0000.

Although arbitration is intended to deal with simultaneous requests of the same priority, it always takes place, even when a single source is requesting service. This is important for two reasons: the EBI does not transfer the interrupt acknowledge read cycle to the external bus unless the SIM wins contention, and failure to contend causes the interrupt acknowledge bus cycle to be terminated early, by a bus error.

When arbitration is complete, the module with the highest arbitration priority must terminate the bus cycle. Internal modules place an interrupt vector number on the data bus and generate appropriate internal cycle termination signals. In the case of an external interrupt request, after the interrupt acknowledge cycle is transferred to the external bus, the appropriate external device must decode the mask value and respond with a vector number, then generate data and size acknowledge ( $\overline{DSACK}$ ) termination signals, or it must assert the autovector ( $\overline{AVEC}$ ) request signal. If the device does not respond in time, the EBI bus monitor asserts the bus error signal  $\overline{BERR}$ , and a spurious interrupt exception is taken.

Chip-select logic can also be used to generate internal AVEC or DSACK signals in response to interrupt requests from external devices. Chip-select address match logic functions only after the EBI transfers an interrupt acknowledge cycle to the external bus following IARB contention. If a module makes an interrupt request of a certain priority, and the appropriate chip-select registers are programmed to generate AVEC or DSACK signals in response to an interrupt acknowledge cycle for that priority level, chip-select logic does not respond to the interrupt acknowledge cycle, and the internal module supplies a vector number and generates internal cycle termination signals.

For periodic timer interrupts, the PIRQ field in the periodic interrupt control register (PICR) determines PIT priority level. A PIRQ value of %000 means that PIT interrupts are inactive. By hardware convention, when the CPU32 receives simultaneous interrupt requests of the same level from more than one SIM source (including external devices), the periodic interrupt timer is given the highest priority, followed by the IRQ pins. Refer to **3.2.7 Periodic Interrupt Timer** for more information.

#### 3.8.2 Interrupt Processing Summary

A summary of the interrupt processing sequence follows. When the sequence begins, a valid interrupt service request has been detected and is pending.

- A. The CPU finishes higher priority exception processing or reaches an instruction boundary.

- B. The processor state is stacked. The S bit in the status register is set, establishing supervisor access level, and bits T1 and T0 are cleared, disabling tracing.

- C. The interrupt acknowledge cycle begins:

- 1. FC[2:0] are driven to %111 (CPU space) encoding.

- The address bus is driven as follows: ADDR[23:20] = %1111; ADDR[19:16] = %1111, which indicates that the cycle is an interrupt acknowledge CPU space cycle; ADDR[15:4] = %111111111111; ADDR[3:1] = the priority of the interrupt request being acknowledged; and ADDR0 = %1.

- 3. The request level is latched from the address bus into the interrupt priority mask field in the status or condition code register.

- D. Modules that have requested interrupt service decode the priority value in ADDR[3:1]. If request priority is the same as acknowledged priority, arbitration by IARB contention takes place.

- E. After arbitration, the interrupt acknowledge cycle is completed in one of the following ways:

- 1. When there is no contention (IARB = %0000), the spurious interrupt monitor asserts BERR, and the CPU generates the spurious interrupt vector number.

- 2. The dominant interrupt source supplies a vector number and DSACK signals appropriate to the access. The CPU acquires the vector number.

- 3. The AVEC signal is asserted (the signal can be asserted by the dominant interrupt source or the pin can be tied low), and the CPU generates an autovector number corresponding to interrupt priority.

- 4. The bus monitor asserts BERR and the CPU32 generates the spurious interrupt vector number.

- F. The vector number is converted to a vector address.

- G. The content of the vector address is loaded into the PC, and the processor transfers control to the exception handler routine.

## 3.9 Factory Test Block

The test submodule supports scan-based testing of the various MCU modules. It is integrated into the SIM to support production testing.

Test submodule registers are intended for Freescale use. Register names and addresses are provided to indicate that these addresses are occupied.

| SIMTR — System Integration Test Register            | \$YFFA02 |

|-----------------------------------------------------|----------|

| SIMTRE — System Integration Test Register (E Clock) | \$YFFA08 |

| TSTMSRA — Master Shift Register A                   | \$YFFA30 |

| TSTMSRB — Master Shift Register B                   | \$YFFA32 |

| TSTSC — Test Module Shift Count                     | \$YFFA34 |

| TSTRC — Test Module Repetition Count                | \$YFFA36 |

| CREG — Test Module Control Register                 | \$YFFA38 |

| DREG — Test Module Distributed Register             | \$YFFA3A |

# 4.6 Instruction Set Summary

| Instruction             | Syntax                        | Operand Size                 | Operation                                                                                                                                                                                       |

|-------------------------|-------------------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ABCD                    | Dn, Dn<br>– (An), – (An)      | 8<br>8                       | Source <sub>10</sub> + Destination <sub>10</sub> + X $\Rightarrow$ Destination                                                                                                                  |

| ADD                     | Dn, ⟨ea⟩<br>⟨ea⟩, Dn          | 8, 16, 32<br>8, 16, 32       | Source + Destination $\Rightarrow$ Destination                                                                                                                                                  |

| ADDA                    | ⟨ea⟩, An                      | 16, 32                       | Source + Destination $\Rightarrow$ Destination                                                                                                                                                  |

| ADDI                    | #⟨data⟩, ⟨ea⟩                 | 8, 16, 32                    | Immediate data + Destination $\Rightarrow$ Destination                                                                                                                                          |

| ADDQ                    | #⟨data⟩, ⟨ea⟩                 | 8, 16, 32                    | Immediate data + Destination $\Rightarrow$ Destination                                                                                                                                          |

| ADDX                    | Dn, Dn<br>– (An), – (An)      | 8, 16, 32<br>8, 16, 32       | Source + Destination + $X \Rightarrow$ Destination                                                                                                                                              |

| AND                     | ⟨ea⟩, Dn<br>Dn, ⟨ea⟩          | 8, 16, 32<br>8, 16, 32       | Source $*$ Destination $\Rightarrow$ Destination                                                                                                                                                |

| ANDI                    | #⟨data⟩, ⟨ea⟩                 | 8, 16, 32                    | Data $*$ Destination $\Rightarrow$ Destination                                                                                                                                                  |

| ANDI to CCR             | #⟨data⟩, CCR                  | 8                            | Source $*$ CCR $\Rightarrow$ CCR                                                                                                                                                                |

| ANDI to SR <sup>1</sup> | #⟨data⟩, SR                   | 16                           | Source $*$ SR $\Rightarrow$ SR                                                                                                                                                                  |

| ASL                     | Dn, Dn<br>#⟨data⟩, Dn<br>⟨ea⟩ | 8, 16, 32<br>8, 16, 32<br>16 | X/C                                                                                                                                                                                             |

| ASR                     | Dn, Dn<br>#⟨data⟩, Dn<br>⟨ea⟩ | 8, 16, 32<br>8, 16, 32<br>16 |                                                                                                                                                                                                 |

| Bcc                     | <pre> (label)</pre>           | 8, 16, 32                    | If condition true, then PC + d $\Rightarrow$ PC                                                                                                                                                 |

| BCHG                    | Dn, ⟨ea⟩<br>#⟨data⟩, ⟨ea⟩     | 8, 32<br>8, 32               | ((bit number) of destination) $\Rightarrow$ Z $\Rightarrow$ bit of destination                                                                                                                  |

| BCLR                    | Dn, ⟨ea⟩<br>#⟨data⟩, ⟨ea⟩     | 8, 32<br>8, 32               | $\begin{array}{l} (\langle \text{bit number} \rangle \text{ of destination}) \Rightarrow Z; \\ 0 \Rightarrow \text{bit of destination} \end{array}$                                             |

| BGND                    | none                          | none                         | If background mode enabled, then enter<br>background mode, else format/vector offset $\Rightarrow$<br>- (SSP);<br>PC $\Rightarrow$ - (SSP); SR $\Rightarrow$ - (SSP); (vector) $\Rightarrow$ PC |

| ВКРТ                    | #⟨data⟩                       | none                         | If breakpoint cycle acknowledged, then execute returned operation word, else trap as illegal instruction.                                                                                       |

| BRA                     | (label)                       | 8, 16, 32                    | $PC + d \Rightarrow PC$                                                                                                                                                                         |

| BSET                    | Dn, ⟨ea⟩<br>#⟨data⟩, ⟨ea⟩     | 8, 32<br>8, 32               | ((bit number) of destination) $\Rightarrow$ Z;<br>1 $\Rightarrow$ bit of destination                                                                                                            |

| BSR                     | (label)                       | 8, 16, 32                    | $SP - 4 \Rightarrow SP; PC \Rightarrow (SP); PC + d \Rightarrow PC$                                                                                                                             |

| BTST                    | Dn, ⟨ea⟩<br>#⟨data⟩, ⟨ea⟩     | 8, 32<br>8, 32               | ((bit number) of destination) $\Rightarrow$ Z                                                                                                                                                   |

| СНК                     | ⟨ea⟩, Dn                      | 16, 32                       | If Dn < 0 or Dn < (ea), then CHK exception                                                                                                                                                      |

| CHK2                    | ⟨ea⟩, Rn                      | 8, 16, 32                    | If Rn < lower bound or Rn > upper bound, then<br>CHK exception                                                                                                                                  |

| CLR                     | 〈ea〉                          | 8, 16, 32                    | $0 \Rightarrow \text{Destination}$                                                                                                                                                              |

| CMP                     | ⟨ea⟩, Dn                      | 8, 16, 32                    | (Destination – Source), CCR shows results                                                                                                                                                       |

| CMPA                    | ⟨ea⟩, An                      | 16, 32                       | (Destination – Source), CCR shows results                                                                                                                                                       |

| CMPI                    | #(data), (ea)                 | 8, 16, 32                    | (Destination – Data), CCR shows results                                                                                                                                                         |

| CMPM                    | (An) +, (An) +                | 8, 16, 32                    | (Destination – Source), CCR shows results                                                                                                                                                       |

| CMP2                    | ⟨ea⟩, Rn                      | 8, 16, 32                    | Lower bound $\leq$ Rn $\leq$ Upper bound, CCR shows result                                                                                                                                      |

## Table 23 Instruction Set Summary

## Table 23 Instruction Set Summary

| Instruction               | Syntax                                 | Operand Size              | Operation                                                                                                                                                   |

|---------------------------|----------------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DBcc                      | Dn, (label)                            | 16                        | If condition false, then $Dn - 1 \Rightarrow PC$ ;                                                                                                          |

|                           |                                        |                           | if $Dn \neq (-1)$ , then PC + d $\Rightarrow$ PC                                                                                                            |

| DIVS/DIVU                 | ⟨ea⟩, Dn                               | 32/16 ⇒ 16: 16            | Destination / Source $\Rightarrow$ Destination (signed or unsigned)                                                                                         |

| DIVSL/DIVUL               | ⟨ea⟩, Dr: Dq                           | $64/32 \Rightarrow 32:32$ |                                                                                                                                                             |

|                           | ⟨ea⟩, Dq                               | $32/32 \Rightarrow 32$    | (signed or unsigned)                                                                                                                                        |

|                           | ⟨ea⟩, Dr : Dq                          | 32/32 ⇒ 32 : 32           |                                                                                                                                                             |

| EOR                       | Dn, ⟨ea⟩                               | 8, 16, 32                 | Source $\oplus$ Destination $\Rightarrow$ Destination                                                                                                       |

| EORI                      | #⟨data⟩, ⟨ea⟩                          | 8, 16, 32                 | Data $\oplus$ Destination $\Rightarrow$ Destination                                                                                                         |

| EORI to CCR               | #⟨data⟩, CCR                           | 8                         | Source $\oplus$ CCR $\Rightarrow$ CCR                                                                                                                       |

| EORI to SR <sup>1</sup>   | #⟨data⟩, SR                            | 16                        | Source $\oplus$ SR $\Rightarrow$ SR                                                                                                                         |

| EXG                       | Rn, Rn                                 | 32                        | $Rn \Rightarrow Rn$                                                                                                                                         |

| EXT                       | Dn                                     | 8 ⇒ 16                    | Sign extended Destination $\Rightarrow$ Destination                                                                                                         |

|                           | Dn                                     | $16 \Rightarrow 32$       |                                                                                                                                                             |

| EXTB                      | Dn                                     | 8 ⇒ 32                    | Sign extended Destination $\Rightarrow$ Destination                                                                                                         |

| ILLEGAL                   | none                                   | none                      | SSP – 2 $\Rightarrow$ SSP; vector offset $\Rightarrow$ (SSP);                                                                                               |

|                           |                                        |                           | $SSP - 4 \Rightarrow SSP; PC \Rightarrow (SSP);$                                                                                                            |

|                           |                                        |                           | SSP – 2 $\Rightarrow$ SSP; SR $\Rightarrow$ (SSP);<br>illegal instruction vector address $\Rightarrow$ PC                                                   |

| JMP                       | 〈ea〉                                   | none                      | Destination $\Rightarrow$ PC                                                                                                                                |

| JSR                       | (ea)                                   |                           | $SP - 4 \Rightarrow SP; PC \Rightarrow (SP); destination \Rightarrow PC$                                                                                    |

| LEA                       |                                        | none<br>32                |                                                                                                                                                             |

|                           | (ea), An                               |                           | $\langle ea \rangle \Rightarrow An$                                                                                                                         |

| LINK                      | An, #〈d〉                               | 16, 32                    | $SP - 4 \Rightarrow SP$ , $An \Rightarrow (SP)$ ; $SP \Rightarrow An$ , $SP + d \Rightarrow SP$                                                             |

| LPSTOP <sup>1</sup>       | #⟨data⟩                                | none                      | Data $\Rightarrow$ SR; interrupt mask $\Rightarrow$ EBI; STOP                                                                                               |

| LSL                       | Dn, Dn                                 | 8, 16, 32                 |                                                                                                                                                             |

|                           | #⟨data⟩, Dn                            | 8, 16, 32<br>16           |                                                                                                                                                             |

|                           | ⟨ea⟩                                   | 10                        |                                                                                                                                                             |

| LSR                       | Dn, Dn                                 | 8, 16, 32                 |                                                                                                                                                             |

|                           | #⟨data⟩, Dn                            | 8, 16, 32                 |                                                                                                                                                             |

|                           | 〈ea〉                                   | 16                        |                                                                                                                                                             |

|                           |                                        |                           |                                                                                                                                                             |

| MOVE                      | ⟨ea⟩, ⟨ea⟩                             | 8, 16, 32                 | Source ⇒ Destination                                                                                                                                        |

| MOVEA                     | ⟨ea⟩, An                               | 16, 32 ⇒ 32               | Source ⇒ Destination                                                                                                                                        |

| MOVEA <sup>1</sup>        | USP, An                                | 32                        | $USP \Rightarrow An$                                                                                                                                        |

|                           | An, USP                                | 32                        | An ⇒ USP                                                                                                                                                    |

| MOVE from<br>CCR          | $CCR,\langleea angle$                  | 16                        | $CCR \Rightarrow Destination$                                                                                                                               |

| MOVE to CCR               | ⟨ea⟩, CCR                              | 16                        | Source $\Rightarrow$ CCR                                                                                                                                    |

| MOVE from SR <sup>1</sup> | SR, $\langle ea \rangle$               | 16                        | $SR \Rightarrow Destination$                                                                                                                                |

| MOVE to SR <sup>1</sup>   | $\langle \epsilon \alpha \rangle$ , SR | 16                        | Source $\Rightarrow$ SR                                                                                                                                     |

| MOVE USP1                 | USP, An                                | 32                        | $USP \Rightarrow An$                                                                                                                                        |

|                           | An, USP                                | 32                        | $An \Rightarrow USP$                                                                                                                                        |

| MOVEC <sup>1</sup>        | Rc, Rn                                 | 32                        | $Rc \Rightarrow Rn$                                                                                                                                         |

|                           | Rn, Rc                                 | 32                        | $Rn \Rightarrow Rc$                                                                                                                                         |

| MOVEM                     | list, ⟨ea⟩                             | 16, 32                    | Listed registers $\Rightarrow$ Destination                                                                                                                  |

|                           | ⟨ea⟩, list                             | 16, 32 ⇒ 32               | Source $\Rightarrow$ Listed registers                                                                                                                       |

| MOVEP                     | Dn, (d <sub>16</sub> , An)             | 16, 32                    | $Dn [31:24] \Rightarrow (An + d); Dn [23:16] \Rightarrow (An + d + 2);$                                                                                     |

|                           |                                        |                           | $Dn [15:8] \Rightarrow (An + d + 4); Dn [7:0] \Rightarrow (An + d + 6)$                                                                                     |

|                           |                                        |                           | $(An + d) \Rightarrow Dn [31:24]; (An + d + 2) \Rightarrow Dn [23:16]$                                                                                      |

|                           | (d <sub>16</sub> , An), Dn             |                           | $(An + d + 4) \Rightarrow Dn [15:8]; (An + d + 6) \Rightarrow Dn [7:0]$                                                                                     |

| MOVEP                     |                                        |                           | Dn [31:24] ⇒ (An + d); Dn [23:16] ⇒ (An + d + 2);<br>Dn [15:8] ⇒ (An + d + 4); Dn [7:0] ⇒ (An + d + 6)<br>(An + d) ⇒ Dn [31:24]; (An + d + 2) ⇒ Dn [23:16]; |

## 5.6.2 Input Capture/Transition Counter (ITC)

Any channel of the TPU can capture the value of a specified TCR or any specified location in parameter RAM upon the occurrence of each transition or specified number of transitions, and then generate an interrupt request to notify the bus master. The times of the most recent two transitions are maintained in parameter RAM. A channel can perform input captures continually, or a channel can detect a single transition or specified number of transitions, the channel activity until reinitialization. After each transition or specified number of transitions, the channel can generate a link to other channels.

## 5.6.3 Queued Output Match (QOM)

QOM can generate single or multiple output match events from a table of offsets in parameter RAM. Loop modes allow complex pulse trains to be generated once, a specified number of times, or continuously. The function can be triggered by a link from another TPU channel. In addition, the reference time for the sequence of matches can be obtained from another channel. QOM can generate pulse-width modulated waveforms, including waveforms with high times of 0% or 100%. QOM also allows a TPU channel to be used as a discrete output pin.

## 5.6.4 Programmable Time Accumulator (PTA)

PTA accumulates a 32-bit sum of the total high time, low time, or period of an input signal over a programmable number of periods or pulses. The accumulation can start on a rising or falling edge. After the specified number of periods or pulses, the PTA generates an interrupt request and optionally generates links to other channels.

From 1 to 255 period measurements can be made and summed with the previous measurement(s) before the TPU interrupts the CPU, providing instantaneous or average frequency measurement capability, and the latest complete accumulation (over the programmed number of periods).

## 5.6.5 Multichannel Pulse-Width Modulation (MCPWM)

MCPWM generates pulse-width modulated outputs with full 0% to 100% duty cycle range independent of other TPU activity. This capability requires two TPU channels plus an external gate for one PWM channel. (A simple one-channel PWM capability is supported by the QOM function.)

Multiple PWMs generated by MCPWM have two types of high time alignment: edge aligned and center aligned. Edge aligned mode uses n + 1 TPU channels for n PWMs; center aligned mode uses 2n + 1 channels. Center aligned mode allows a user defined 'dead time' to be specified so that two PWMs can be used to drive an H-bridge without destructive current spikes. This feature is important for motor control applications.

#### 5.6.6 Fast Quadrature Decode (FQD)

FQD is a position feedback function for motor control. It decodes the two signals from a slotted encoder to provide the CPU with a 16-bit free running position counter. FQD incorporates a "speed switch" which disables one of the channels at high speed, allowing faster signals to be decoded. A time stamp is provided on every counter update to allow position interpolation and better velocity determination at low speed or when low resolution encoders are used. The third index channel provided by some encoders is handled by the ITC function.

## 5.6.7 Universal Asynchronous Receiver/Transmitter (UART)

The UART function uses one or two TPU channels to provide asynchronous communications. Data word length is programmable from 1 to 14 bits. The function supports detection or generation of even, odd, and no parity. Baud rate is freely programmable and can be higher than 100 Kbaud. Eight bidirectional UART channels running in excess of 9600 baud could be implemented on the TPU.

| ADCTL1 — A/D Control Register 1 |          |     |    |    |    |    |   |      |      | \$YF | F70C |    |    |    |   |   |  |

|---------------------------------|----------|-----|----|----|----|----|---|------|------|------|------|----|----|----|---|---|--|

|                                 | 15       | 14  | 13 | 12 | 11 | 10 | 9 | 8    | 7    | 6    | 5    | 4  | 3  | 2  | 1 | 0 |  |

|                                 | NOT USED |     |    |    |    |    |   | SCAN | MULT | S8CM | CD   | CC | СВ | CA |   |   |  |

|                                 | RESI     | ET: |    |    |    |    |   |      |      | •    | •    |    |    | •  |   |   |  |

|                                 |          |     |    |    |    |    |   |      |      | 0    | 0    | 0  | 0  | 0  | 0 | 0 |  |

ADCTL1 is used to initiate an A/D conversion and to select conversion modes and a conversion channel. It can be written or read at any time. A write to ADCTL1 initiates a conversion sequence. If a conversion sequence is already in progress, a write to ADCTL1 aborts it and resets the SCF and CCF flags in the ADC status register.

## SCAN — Scan Mode Selection Bit

0 = Single conversion sequence

1 = Continuous conversion

Length of conversion sequence(s) is determined by S8CM.

- MULT Multichannel Conversion Bit

- 0 = Conversion sequence(s) run on single channel (channel selected via [CD:CA])

1 = Sequential conversion of a block of four or eight channels (block selected via [CD:CA])

Length of conversion sequence(s) is determined by S8CM.

## S8CM — Select Eight-Conversion Sequence Mode

- 0 = Four-conversion sequence

- 1 = Eight-conversion sequence

This bit determines the number of conversions in a conversion sequence.

## CD:CA — Channel Selection Field

The bits in this field are used to select an input or block of inputs for A/D conversion.

The following table summarizes the operation of S8CM and CD:CA when MULT is cleared (single channel mode). Number of conversions per channel is determined by SCAN.

- Test mode functions in conjunction with the SIM test functions. Test mode is used during factory test of the MCU.

- Writing the STOP bit of TRAMMCR causes the TPURAM module to enter stop mode. The TPURAM array is disabled (which allows external logic to decode TPURAM addresses, if necessary), but all data is retained. If V<sub>DD</sub> falls below V<sub>STBY</sub> during stop mode, internal circuitry switches to V<sub>STBY</sub>, as in standby mode. Stop mode is exited by clearing the STOP bit.

- The TPURAM array may be used to emulate the microcode ROM in the TPU module. This provides a means of developing custom TPU code. The TPU selects TPU emulation mode. While in TPU emulation mode, the access timing of the TPURAM module matches the timing of the TPU microinstruction ROM to ensure accurate emulation. Normal accesses via the IMB are inhibited and the control registers have no effect, allowing external RAM to emulate the TPURAM at the same addresses.

## 8 Summary of Changes

This is a partial revision. Most of the publication remains the same, but the following changes were made to improve it. Typographical errors that do not affect content are not annotated.

- Page 2 Ordering Information revised to reflect new quantities, TPU mask options.

- Page 7 Address map revised to reflect TPURAM array mapping.

- Pages 11-42 Expanded and revised SIM section. Added new information to **3.3 System Clock**, **3.5 Chip Selects**, **3.7 Resets**, and **3.8 Interrupts**.

- Page 72-74 Revised Standby RAM with TPU Emulation section to include details of array mapping to upper half of 2-Kbyte address block.