Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2014                       |                                                                  |

|----------------------------|------------------------------------------------------------------|

| Product Status             | Obsolete                                                         |

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 25MHz                                                            |

| Connectivity               | EBI/EMI, SIO, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR                                      |

| Number of I/O              | 32                                                               |

| Program Memory Size        | -                                                                |

| Program Memory Type        | ROMIess                                                          |

| EEPROM Size                | -                                                                |

| RAM Size                   | 256 x 8                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                      |

| Data Converters            | -                                                                |

| Oscillator Type            | External                                                         |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                  |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 44-LCC (J-Lead)                                                  |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/ds80c310-qcg |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **ORDERING INFORMATION**

| PART          | TEMP RANGE                       | MAX CLOCK<br>SPEED (MHz) | PIN-PACKAGE    |

|---------------|----------------------------------|--------------------------|----------------|

| DS80C310-MCG  | $0^{\circ}$ C to $+70^{\circ}$ C | 25                       | 40 Plastic DIP |

| DS80C310-MCG+ | $0^{\circ}$ C to $+70^{\circ}$ C | 25                       | 40 Plastic DIP |

| DS80C310-QCG  | $0^{\circ}$ C to $+70^{\circ}$ C | 25                       | 44 PLCC        |

| DS80C310-QCG+ | $0^{\circ}$ C to $+70^{\circ}$ C | 25                       | 44 PLCC        |

| DS80C310-QNG  | -40°C to +85°C                   | 25                       | 44 PLCC        |

| DS80C310-QNG+ | -40°C to +85°C                   | 25                       | 44 PLCC        |

| DS80C310-ECG  | $0^{\circ}$ C to $+70^{\circ}$ C | 25                       | 44 TQFP        |

| DS80C310-ECG+ | $0^{\circ}$ C to $+70^{\circ}$ C | 25                       | 44 TQFP        |

+ Denotes a lead(Pb)-free/RoHS-compliant device.

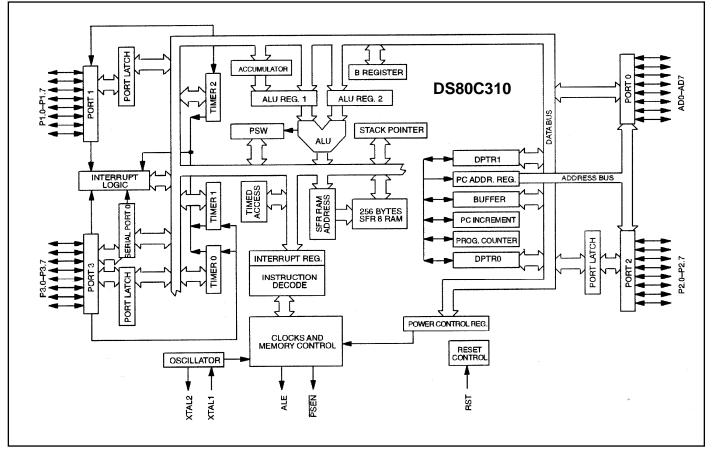

#### Figure 1. Block Diagram

# **PIN DESCRIPTION**

| PIN  |      |                   |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |      |      |           |                                                   |   |    |      |      |                                              |   |      |      |

|------|------|-------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-----------|---------------------------------------------------|---|----|------|------|----------------------------------------------|---|------|------|

| PDIP | PLCC | TQFP              | NAME      | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |      |      |           |                                                   |   |    |      |      |                                              |   |      |      |

|      |      |                   |           | Port 1 (I/O). Port 1 functions as both an 8-bit bidirectional I/O port<br>and an alternate functional interface for Timer 2 I/O and new<br>external interrupts. The reset condition of Port 1 is with all bits at<br>logic 1. In this state, a weak pullup holds the port high. This<br>condition also serves as an input mode, since any external circuit<br>that writes to the port overcomes the weak pullup. When software<br>writes a 0 to any port pin, the DS80C310 activates a strong pulldown<br>that remains on until either a 1 is written or a reset occurs. Writing a<br>1 after the port has been at 0 causes a strong transition driver to turn<br>on, followed by a weaker sustaining pullup. Once the momentary<br>strong driver turns off, the port once again becomes the output high<br>(and input) state. The alternate modes of Port 1 are outlined as<br>follows: |      |      |      |           |                                                   |   |    |      |      |                                              |   |      |      |

|      |      |                   |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | PIN  |      | PORT | ALTERNATE | FUNCTION                                          |   |    |      |      |                                              |   |      |      |

|      |      |                   |           | PDIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PLCC | TQFP | _    |           |                                                   |   |    |      |      |                                              |   |      |      |

| 1–8  | 2–9  | 40–44,<br>1, 2, 3 | P1.0–P1.7 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2    | 40   | P1.0 | T2        | External I/O for<br>Timer/Counter 2               |   |    |      |      |                                              |   |      |      |

|      |      |                   |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |      |      |           | 2                                                 | 3 | 41 | P1.1 | T2EX | Timer/Counter 2<br>Capture/Reload<br>Trigger |   |      |      |

|      |      |                   |           | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4    | 42   | P1.2 |           | DS80C320 has a serial port RXD                    |   |    |      |      |                                              |   |      |      |

|      |      |                   |           | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5    | 43   | P1.3 | _         | DS80C320 has a serial port TXD                    |   |    |      |      |                                              |   |      |      |

|      |      |                   |           | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6    | 44   | P1.4 | INT2      | External Interrupt 2<br>(Positive Edge Detect)    |   |    |      |      |                                              |   |      |      |

|      |      |                   |           | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7    | 1    | P1.5 | P1.5 INT3 | External Interrupt 3<br>(Negative Edge<br>Detect) |   |    |      |      |                                              |   |      |      |

|      |      |                   |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |      |      |           |                                                   |   |    |      | 7    | 8                                            | 2 | P1.6 | INT4 |

|      |      |                   |           | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9    | 3    | P1.7 | INT5      | External Interrupt 5<br>(Negative Edge<br>Detect) |   |    |      |      |                                              |   |      |      |

| 9    | 10   | 4                 | RST       | Reset (Input). The RST input pin contains a Schmitt voltage input to recognize external active-high reset inputs. The pin also employs an internal pulldown resistor to allow for a combination of wired-OR external reset sources.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |      |      |           |                                                   |   |    |      |      |                                              |   |      |      |

| PIN    |              |               | NAME            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                           |           | FUNC       | CTION              |                                         |                                   |

|--------|--------------|---------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------|--------------------|-----------------------------------------|-----------------------------------|

| PDIP   | PLCC         | TQFP          | INAME           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                           |           |            |                    |                                         |                                   |

|        |              |               |                 | Port 3 (I/O). Port 3 functions as both an 8-bit bidirectional I/O port<br>and an alternate functional interface for external Interrupts, Serial<br>Port 0, Timer 0 and 1 Inputs, RD and WR strobes. The reset<br>condition of Port 3 is with all bits at logic 1. In this state, a weak<br>pullup holds the port high. This condition also serves as an input<br>mode, since any external circuit that writes to the port will overcome<br>the weak pullup. When software writes a 0 to any port pin, the<br>DS80C310 will activate a strong pulldown that remains on until<br>either a 1 is written or a reset occurs. Writing a 1 after the port has<br>been at 0 will cause a strong transition driver to turn on, followed by<br>a weaker sustaining pullup. Once the momentary strong driver turns<br>off, the port once again becomes both the output high and input<br>state. The alternate modes of Port 3 are as follows: |                                                                                                                                           |           |            |                    |                                         |                                   |

|        |              |               |                 | DDID                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | PIN                                                                                                                                       | TOPP      | PORT       | ALTERNATE          | FUNCTION                                |                                   |

| 10–17  | 11,          | 5, 7–13       | P3.0–P3.7       | <b>PDIP</b> 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>PLCC</b> 11                                                                                                                            | TQFP<br>5 | P3.0       | RXD0               | Serial Port 0                           |                                   |

|        | 13–19        |               |                 | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 13                                                                                                                                        | 7         | P3.1       | TXD0               | Input<br>Serial Port 0                  |                                   |

|        |              |               |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 12                                                                                                                                        | 14        | 8          | P3.2               | ĪNT0                                    | Output<br>External Interrupt<br>0 |

|        |              |               |                 | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15                                                                                                                                        | 9         | P3.3       | INT1               | External Interrupt                      |                                   |

|        |              |               |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                           | 14        | 16         | 10                 | P3.4                                    | ТО                                |

|        |              |               |                 | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 17                                                                                                                                        | 11        | P3.5       | T1                 | Timer 1 External<br>Input               |                                   |

|        |              |               |                 | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 18                                                                                                                                        | 12        | P3.6       | WR                 | External Data<br>Memory Write<br>Strobe |                                   |

|        |              |               |                 | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 19                                                                                                                                        | 13        | P3.7       | RD                 | External Data<br>Memory Read<br>Strobe  |                                   |

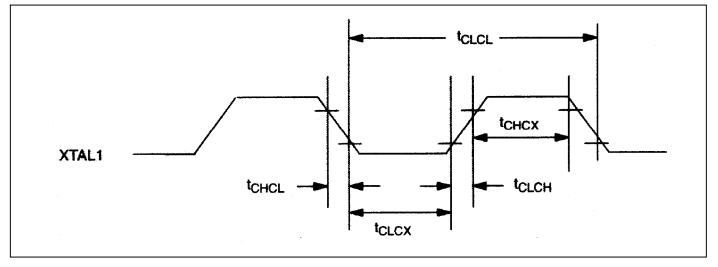

| 18, 19 | 20, 21       | 14, 15        | XTAL2,<br>XTAL1 | Crystal Oscillator Pins. XTAL1 and XTAL2 provide support for<br>parallel resonant, AT-cut crystals. XTAL1 also acts as an input in<br>the event that an external clock source is used in place of a crystal.<br>XTAL2 serves as the output of the crystal amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                           |           |            |                    |                                         |                                   |

| 20     | 1, 22,<br>23 | 16, 17,<br>39 | GND             | Digital                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Circuit C                                                                                                                                 | Ground    | -          | <u> </u>           |                                         |                                   |

| 21     | 24           | 18            | A8(P2.0)        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                           |           |            | . Port 2 serves as |                                         |                                   |

| 22     | 25           | 19            | A9(P2.1)        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                           | •         |            | nd P2.0 is A8. T   |                                         |                                   |

| 23     | 26           | 20            | A10(P2.2)       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                           |           |            |                    | for external ROM                        |                                   |

| 24     | 27           | 21            | A11 (P2.3)      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | and RAM access. Although Port 2 can be accessed like an ordinary I/O port, the value stored on the Port 2 latch is never seen on the pins |           |            |                    |                                         |                                   |

| 25     | 28           | 22            | A12(P2.4)       | · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (due to memory access). Therefore, writing to Port 2 in software is                                                                       |           |            |                    |                                         |                                   |

| 26     | 29           | 23            | A13 (P2.5)      | only us                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | only useful for the instructions MOVX A, @ Ri or MOVX @ Ri, A.                                                                            |           |            |                    |                                         |                                   |

| 27     | 30           | 24            | A14(P2.6)       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | These instructions use the Port 2 internal latch to supply the external address MSB; the Port 2 latch value is supplied as the address    |           |            |                    |                                         |                                   |

| 28     | 31           | 25            | A15(P2.7)       | addres                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                           | ie Port 2 | latch valu | ie is supplied as  | une address                             |                                   |

|      | PIN    |       | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                     |  |  |  |

|------|--------|-------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PDIP | PLCC   | TQFP  | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                     |  |  |  |

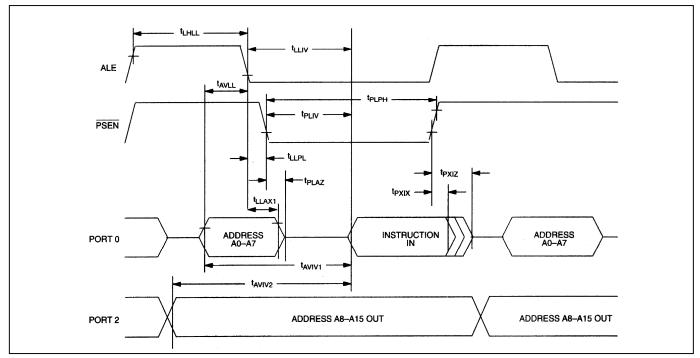

| 29   | 32     | 26    | PSEN            | Active-Low Program Store Enable (Output). This signal is<br>commonly connected to external ROM memory as a chip enable.<br><u>PSEN</u> is driven high when data memory (RAM) is being accessed<br>through the bus and during a reset condition.                                                                              |  |  |  |

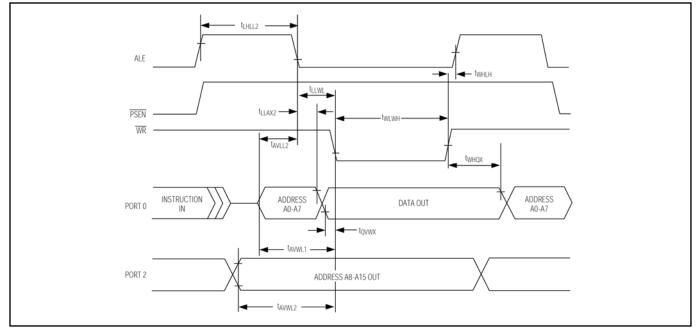

| 30   | 33     | 27    | ALE             | Address Latch Enable (Output). The output functions as clock to<br>latch the external address LSB from the multiplexed address/data<br>bus on Port 0. This signal is commonly connected to the latch enable<br>of an external 373 family transparent latch. ALE is forced high when<br>the DS80C310 is in a reset condition. |  |  |  |

| 31   | 35     | 29    | ĒĀ              | Active-Low External Access (Input). This pin must be connected to ground for proper operation.                                                                                                                                                                                                                               |  |  |  |

| 32   | 36     | 30    | AD7 (P0.7)      |                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 33   | 37     | 31    | AD6(P0.6)       | Address/Data Bus 0–7 (Port 0) (I/O). Port 0 is the multiplexed                                                                                                                                                                                                                                                               |  |  |  |

| 34   | 38     | 32    | AD5 (P0.5)      | address/data bus. During the time when ALE is high, the LSB of a                                                                                                                                                                                                                                                             |  |  |  |

| 35   | 39     | 33    | AD4 (P0.4)      | memory address is presented. When ALE falls to logic 0, the port<br>transitions to a bidirectional data bus. This bus is used to read                                                                                                                                                                                        |  |  |  |

| 36   | 40     | 34    | AD3 (P0.3)      | external ROM and read/write external RAM memory or peripherals.                                                                                                                                                                                                                                                              |  |  |  |

| 37   | 41     | 35    | AD2(P0.2)       | Port 0 has no true port latch and cannot be written directly by                                                                                                                                                                                                                                                              |  |  |  |

| 38   | 42     | 36    | AD1 (P0.1)      | software. The reset condition of Port 0 is high.                                                                                                                                                                                                                                                                             |  |  |  |

| 39   | 43     | 37    | AD0(P0.0)       |                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 40   | 44     | 38    | V <sub>CC</sub> | +5V Power Supply                                                                                                                                                                                                                                                                                                             |  |  |  |

| _    | 12, 34 | 6, 28 | N.C.            | No Connection (Reserved). These pins should not be connected.<br>They are reserved for use with future devices in this family.                                                                                                                                                                                               |  |  |  |

# COMPATIBILITY

The DS80C310 is a fully static, CMOS, 8051-compatible microcontroller designed for high performance. In most cases the DS80C310 can drop into an existing socket for the 80C31 or 80C32 to significantly improve the operation. In general, software written for existing 8051-based systems works without modification on the DS80C310. The exception is critical timing because the high-speed microcontroller performs its instructions much faster than the original for any given crystal selection. The DS80C310 runs the standard 8051 family instruction set and is pin compatible with DIP, PLCC, or TQFP packages. The DS80C310 is a streamlined version of the DS80C320. It maintains upward compatibility but has fewer peripherals.

The DS80C310 provides three 16-bit timer/counters, a full-duplex serial port, and 256 bytes of direct RAM. I/O ports have the same operation as a standard 8051 product. Timers default to a 12 clock-percycle operation to keep their timing compatible with original 8051 family systems. However, timers are individually programmable to run at the new 4 clocks per cycle if desired.

The DS80C310 provides several new hardware functions that are controlled by Special Function Registers (SFRs). Table 1 summarizes the SFRs.

### PERFORMANCE OVERVIEW

The DS80C310 features a high-speed 8051-compatible core. Higher speed comes not just from increasing the clock frequency but from a newer, more efficient design.

This updated core does not have the dummy memory cycles that exist in a standard 8051. A conventional 8051 generates machine cycles using the clock frequency divided by 12. In the DS80C310, the same

machine cycle takes 4 clocks. Thus the fastest instruction, 1 machine cycle, executes three times faster for the same crystal frequency. Note that these are identical instructions. The majority of instructions on the DS80C310 will see the full 3-to-1 speed improvement. Some instructions will get between 1.5 and 2.4 to 1 improvement. All instructions are faster than the original 8051.

The numerical average of all op codes gives approximately a 2.5-to-1 speed improvement. Improvement of individual programs depends on the actual instructions used. Speed-sensitive applications would make the most use of instructions that are three times faster. However, the sheer number of 3-to-1 improved op codes makes dramatic speed improvements likely for any code. These architecture improvements and 0.8µm CMOS produce a peak instruction cycle in 160ns (6.25MIPS). The dual data pointer feature also allows the user to eliminate wasted instructions when moving blocks of memory.

## **INSTRUCTION SET SUMMARY**

All instructions in the DS80C310 perform the same functions as their 8051 counterparts. Their effect on bits, flags, and other status functions is identical. However, the timing of each instruction is different. This applies both in absolute and relative number of clocks.

For absolute timing of real-time events, the timing of software loops can be calculated using a table in the *High-Speed Microcontroller User's Guide*. However, counter/timers default to run at the older 12 clocks per increment. In this way, timer-based events occur at the standard intervals with software executing at higher speed. Timers optionally can run at 4 clocks per increment to take advantage of faster processor operation.

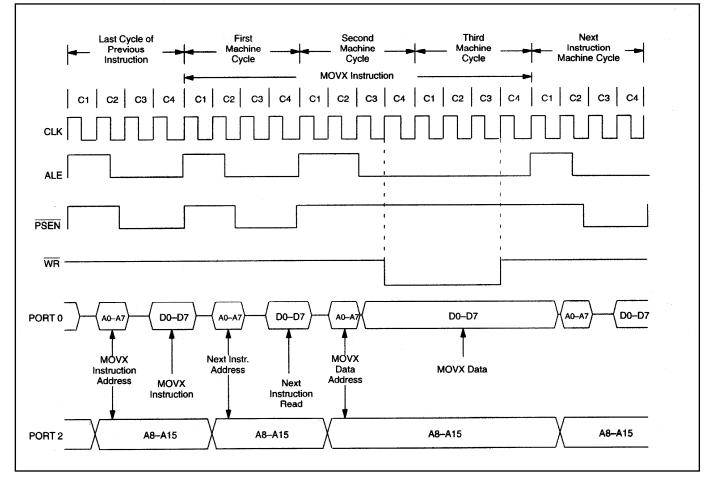

The relative time of two instructions might be different in the new architecture than it was previously. For example, in the original architecture the "MOVX A, @ DPTR" instruction and the "MOV direct, direct" instruction used 2 machine cycles or 24 oscillator cycles. Therefore, they required the same amount of time. In the DS80C310, the MOVX instruction takes as little as 2 machine cycles or 8 oscillator cycles but the "MOV direct, direct" uses 3 machine cycles or 12 oscillator cycles. While both are faster than their original counterparts, they now have different execution times. This is because the DS80C310 usually uses 1 instruction cycle for each instruction byte. The user concerned with precise program timing should examine the timing of each instruction for familiarity with the changes. Note that a machine cycle now requires just 4 clocks, and provides one ALE pulse per cycle. Many instructions require only 1 cycle, but some require 5. In the original architecture, all were 1 or 2 cycles except for MUL and DIV. Refer to the *High-Speed Microcontroller User's Guide* for details and individual instruction timing.

# SPECIAL FUNCTION REGISTERS (SFRs)

Special Function Registers control most special features of the DS80C310. The *High-Speed Microcontroller User's Guide* contains descriptions of all the SFRs. Functions that are not part of the standard 80C32 are in bold.

| REGISTER | BIT 7  | BIT 6            | BIT 5 | BIT 4 | BIT 3 | BIT 2            | BIT 1             | BIT 0               | ADDRESS |

|----------|--------|------------------|-------|-------|-------|------------------|-------------------|---------------------|---------|

| SP       |        | _                |       |       |       |                  |                   |                     | 81h     |

| DPL      |        |                  |       |       |       |                  |                   |                     | 82h     |

| DPH      |        |                  |       |       |       | _                |                   |                     | 83h     |

| DPL1     |        |                  |       |       |       |                  |                   |                     | 84h     |

| DPH1     |        |                  |       |       |       |                  |                   |                     | 85h     |

| DPS      | 0      | 0                | 0     | 0     | 0     | 0                | 0                 | SEL                 | 86h     |

| PCON     | SMOD   | SM0D0            |       |       | GF1   | GF0              | STOP              | IDLE                | 87h     |

| TCON     | TF1    | TR1              | TF0   | TR0   | IE1   | IT1              | IE0               | IT0                 | 88h     |

| TMOD     | GATE   | $C/\overline{T}$ | M1    | M0    | GATE  | $C/\overline{T}$ | M1                | M0                  | 89h     |

| TL0      |        |                  |       |       |       |                  |                   |                     | 8Ah     |

| TL1      |        |                  |       |       |       |                  |                   |                     | 8Bh     |

| TH0      |        |                  |       |       |       |                  |                   |                     | 8Ch     |

| TH1      |        |                  |       |       |       |                  |                   |                     | 8Dh     |

| CKCON    |        |                  | T2M   | T1M   | TOM   | MD2              | MD1               | MD0                 | 8Eh     |

| P1       | P1.7   | P1.6             | P1.5  | P1.4  | P1.3  | P1.2             | P1.1              | P1.0                | 90h     |

| EXIF     | IE5    | IE4              | IE3   | IE2   |       |                  |                   |                     | 91h     |

| SCON     | SMO/FE | SM1              | SM2   | REN   | TB8   | RB8              | TI                | RI                  | 98h     |

| SBUF     |        |                  |       |       |       |                  |                   |                     | 99h     |

| P2       | P2.7   | P2.6             | P2.5  | P2.4  | P2.3  | P2.2             | P2.1              | P2.0                | A0h     |

| IE       | EA     |                  | ET2   | ES0   | ET1   | EX1              | ET0               | EX0                 | A8h     |

| SADDR0   |        |                  |       |       |       |                  | —                 |                     | A9h     |

| P3       | P3.7   | P3.6             | P3.5  | P3.4  | P3.3  | P3.2             | P3.1              | P3.0                | B0h     |

| IP       |        |                  | PT2   | PSO   | PT1   | PX1              | PT0               | PX0                 | B8h     |

| SADEN0   |        |                  |       |       |       |                  |                   |                     | B9h     |

| STATUS   | 0      | HIP              | LIP   | 1     | 1     | 1                | 1                 | 1                   | C5h     |

| T2CON    | TF2    | EXF2             | RCLK  | TCLK  | EXEN2 | TR2              | $C/\overline{T2}$ | $CP/\overline{RL2}$ | C8h     |

| T2MOD    |        |                  |       |       |       |                  | T2OE              | DCEN                | C9h     |

| RCAP2L   |        |                  |       |       |       | _                |                   |                     | CAh     |

| RCAP2H   |        |                  |       |       |       |                  |                   |                     | CBh     |

| TL2      |        |                  |       |       |       |                  |                   |                     | CCh     |

| TH2      |        |                  |       |       |       |                  |                   |                     | CDh     |

| PSW      | CY     | AC               | F0    | RS1   | RS0   | OV               | FL                | Р                   | D0h     |

| WDCON    | —      | POR              |       |       |       |                  |                   |                     | D8h     |

| ACC      |        |                  |       |       |       |                  |                   |                     | E0h     |

| EIE      | —      |                  |       | —     | EX5   | EX4              | EX3               | EX2                 | E8h     |

| В        | —      |                  |       |       |       |                  |                   |                     | F0h     |

| EIP      |        |                  |       |       | PX5   | PX4              | PX3               | PX2                 | F8h     |

#### **Table 1. Special Function Registers**

# MEMORY ACCESS

The DS80C310 has 256 bytes of scratchpad RAM, but contains no on-chip ROM. Off-chip memory is accessed using the multiplexed address/data bus on P0 and the MSB address on P2. Timing diagrams are provided in the *Absolute Maximum Ratings* section. Program memory (ROM) is accessed at a fixed rate determined by the crystal frequency and the actual instructions. As mentioned above, an instruction cycle requires 4 clocks. Data memory (RAM) is accessed according to a variable speed MOVX instruction as described below.

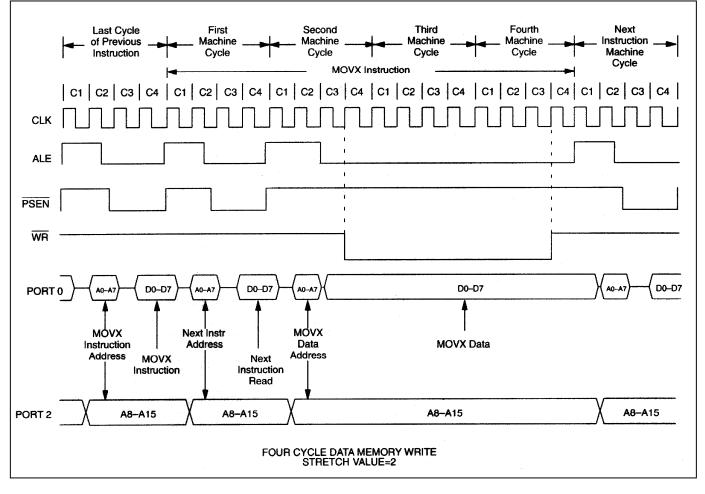

# STRETCH MEMORY CYCLE

The DS80C310 allows the application software to adjust the speed of data memory access. The microcontroller can perform the MOVX in as few as 2 instruction cycles. However, this value can be stretched as needed so that both fast memory and slow memory or peripherals can be accessed with no glue logic. Even in high-speed systems, it may not be necessary or desirable to perform data memory access at full speed. In addition, there are a variety of memory-mapped peripherals such as LCD displays or UARTs that are not fast.

The stretch MOVX is controlled by the Clock Control Register at SFR location 8Eh as described below. This allows the user to select a stretch value between 0 and 7. A stretch of 0 results in a 2-machine-cycle MOVX. A stretch of 7 results in a MOVX of 9 machine cycles. Software can dynamically change this value depending on the particular memory or peripheral.

On reset, the stretch value defaults to 1, resulting in a 3-cycle MOVX. Therefore, RAM access is not performed at full speed. This is a convenience to existing designs that may not have fast RAM in place. When maximum speed is desired, the software should select a stretch value of 0. When using very slow RAM or peripherals, a larger stretch value can be selected. Note that this affects data memory only and the only way to slow program memory (ROM) access is to use a slower crystal.

Using a stretch value between 1 and 7 causes the microcontroller to stretch the read/write strobe and all related timing. This results in a wider read/write strobe allowing more time for memory/peripherals to respond. The timing of the variable speed MOVX is shown in the *Absolute Maximum Ratings* section. Note that full speed access is not the reset default case. Table 2 shows the resulting strobe widths for each stretch value. The memory stretch is implemented using the Clock Control Special Function Register at SFR location 8Eh. The stretch value is selected using bits CKCON.2–CKCON.0. In the table, these bits are referred to as M2 through M0. The first stretch (default) allows the use of common 120ns or 150ns RAMs without dramatically lengthening the memory access.

| CKCON.2-CKCON.0 |    | MEMORY<br>CYCLES | RD OR WR STROBE<br>WIDTH IN CLOCKS | 25MHz STROBE WIDTH |      |  |

|-----------------|----|------------------|------------------------------------|--------------------|------|--|

| M2              | M1 | <b>M0</b>        | CICLES                             | WIDTH IN CLOCKS    | (ns) |  |

| 0               | 0  | 0                | 2                                  | 2                  | 80   |  |

| 0               | 0  | 1                | 3 (default)                        | 4                  | 160  |  |

| 0               | 1  | 0                | 4                                  | 8                  | 320  |  |

| 0               | 1  | 1                | 5                                  | 12                 | 480  |  |

| 1               | 0  | 0                | 6                                  | 16                 | 640  |  |

| 1               | 0  | 1                | 7                                  | 20                 | 800  |  |

| 1               | 1  | 0                | 8                                  | 24                 | 960  |  |

| 1               | 1  | 1                | 9                                  | 28                 | 1120 |  |

Table 2. Data Memory Cycle Stretch Values

# **DUAL DATA POINTER (DPTR)**

Data memory block moves can be accelerated using the DS80C310 dual data pointer (DPTR). The standard 8032 DPTR is a 16-bit value that is used to address off-chip data RAM or peripherals. In the DS80C310, the standard data pointer is called DPTR and is located at SFR addresses 82h and 83h. These are the standard locations. No modification of standard code is needed to use DPTR. The new DPTR is located at SFR 84h and 85h and is called DPTR1. The DPTR select bit (DPS) chooses the active pointer and is located at the LSB of the SFR location 86h. No other bits in register 86h have any effect and are set to 0. The user switches between data pointers by toggling the LSB of register 86h. The increment (INC) instruction is the fastest way to accomplish this. All DPTR-related instructions use the currently selected DPTR for any activity. Therefore, only one instruction is required to switch from a source to a destination address. Using the DPTR saves code from needing to save source and destination addresses when doing a block move. Once loaded, the software simply switches between DPTR0 and 1. The relevant register locations are as follows.

| DPL  | 82h | Low byte original DPTR  |

|------|-----|-------------------------|

| DPH  | 83h | High byte original DPTR |

| DPL1 | 84h | Low byte new DPTR       |

| DPH1 | 85h | High byte new DPTR      |

| DPS  | 86h | DPTR Select (lsb)       |

|      |     |                         |

### **STOP MODE ENHANCEMENTS**

Setting bit 1 of the Power Control Register (PCON; 87h) invokes the stop mode. Stop mode is the lowest power state because it turns off all internal clocking. The  $I_{CC}$  of a standard stop mode is approximately 1µA (but is specified in the *Absolute Maximum Ratings* section). The CPU exits stop mode from an external interrupt or a reset condition. Internally generated interrupts are not useful since they require clocking activity.

The DS80C310 allows a resume from stop using INT2–INT5, which are edge-triggered interrupts. An internal crystal counter manages the startup timing. A delay of 65,536 clocks occurs to allow the crystal time to stabilize. Software must also insert a delay of 100 machine cycles following the exit from stop mode. This ensures stabilization of internal timing prior to time-critical software tasks such as serial port operations or bus access to memory-mapped I/O devices.

# PERIPHERAL OVERVIEW

The DS80C310 provides the same peripheral functions as the standard 80C32. The device is compatible with the DS80C320, but it does not offer all the peripherals.

# TIMER RATE CONTROL

There is one important difference between the DS80C310 and 8051 regarding timers. The original 8051 used 12 clocks per cycle for timers and machine cycles. The DS80C310 architecture normally uses 4 clocks per machine cycle. However, in the area of timers and serial ports, the DS80C310 defaults to 12 clocks per cycle on reset. This allows existing code with real-time dependencies such as baud rates to operate properly.

If an application needs higher speed timers or serial baud rates, the user can select individual timers to run at the 4-clock rate. The Clock Control Register (CKCON; 8Eh) determines these timer speeds. When the relevant CKCON bit is logic 1, the DS80C310 uses 4 clocks per cycle to generate timer speeds. When the bit is 0, the DS80C310 uses 12 clocks for timer speeds. The reset condition is 0. CKCON.5 selects the speed of Timer 2. CKCON.4 selects Timer 1 and CKCON.3 selects Timer 0. Note that unless a user desires very fast timing, it is unnecessary to alter these bits. Also note that the timer controls are independent.

# **POWER-ON RESET**

The DS80C310 holds itself in reset during a power-up until 65,536 clock cycles have elapsed. The poweron reset used by the DS80C310 differs somewhat from other members of the high-speed microcontroller family. The crystal oscillator can start anywhere between 1.0V and 4.5V, but is not specified. This eliminates the need for an RC reset circuit. For voltage-specific precision-brownout detection, an external component is needed. When the device goes through a power-on reset, the POR flag is set in the WDCON (D8h) register at bit 6.

## **INTERRUPTS**

The DS80C310 provides 10 interrupt sources with two priority levels. Software can assign high or low priority to all sources. All interrupts that are new to the 8051 have a lower natural priority than the originals.

| NAME        | DESCRIPTION                   | VECTOR | NATURAL<br>PRIORITY |

|-------------|-------------------------------|--------|---------------------|

| <b>INTO</b> | External Interrupt 0          | 03h    | 1                   |

| TF0         | Timer 0                       | 0Bh    | 2                   |

| INT1        | External Interrupt 1          | 13h    | 3                   |

| TF1         | Timer 1                       | 1Bh    | 4                   |

| SCON        | T1 or R1 from the serial port | 23h    | 5                   |

| TF2         | Timer 2                       | 2Bh    | 6                   |

| INT2        | External Interrupt 2          | 43h    | 7                   |

| INT3        | External Interrupt 3          | 4Bh    | 8                   |

| INT4        | External Interrupt 4          | 53h    | 9                   |

| INT5        | External Interrupt 5          | 5Bh    | 10                  |

#### **Table 3. Interrupt Sources and Priorities**

# **ABSOLUTE MAXIMUM RATINGS**

| Voltage Range on Any Pin Relative to Ground         | 0.3V to (V <sub>CC</sub> + $0.5V$ )   |

|-----------------------------------------------------|---------------------------------------|

| Voltage Range on V <sub>CC</sub> Relative to Ground | -0.3V to +6.0V                        |

| Operating Temperature Range                         | 40°C to +85°C                         |

| Storage Temperature Range                           | 55°C to +125°C                        |

| Soldering Temperature                               | See IPC/JEDEC J-STD-020 Specification |

This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect device reliability.

# DC ELECTRICAL CHARACTERISTICS

|                                                                                                                          | $V_{CC} = 4.5V$ to 5.5V, $T_A = -40^{\circ}C$ to $+85^{\circ}C$ .) (Note 1) |      |      |                       |       |       |  |

|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|------|------|-----------------------|-------|-------|--|

| PARAMETER                                                                                                                | SYMBOL                                                                      | MIN  | TYP  | MAX                   | UNITS | NOTES |  |

| Supply Voltage                                                                                                           | V <sub>CC</sub>                                                             | 4.0  | 5.0  | 5.5                   | V     | 2     |  |

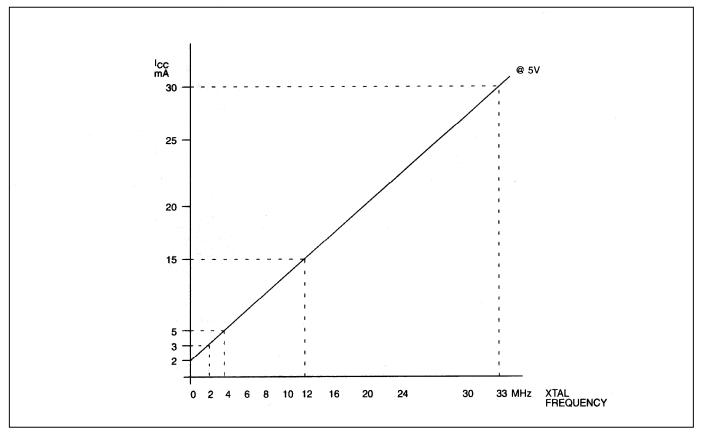

| Supply Current Active Mode<br>at 25MHz                                                                                   | I <sub>CC</sub>                                                             |      | 30   |                       | mA    | 3     |  |

| Supply Current Idle Mode<br>at 25MHz                                                                                     | I <sub>IDLE</sub>                                                           |      | 15   |                       | mA    | 4     |  |

| Supply Current Stop Mode                                                                                                 | I <sub>STOP</sub>                                                           |      | 1    |                       | μA    | 5     |  |

| Input Low Level                                                                                                          | V <sub>IL</sub>                                                             | -0.3 |      | +0.8                  | V     | 2     |  |

| Input High Level (Except XTAL1 and RST)                                                                                  | V <sub>IH</sub>                                                             | 2.0  |      | V <sub>CC</sub> + 0.3 | V     | 2     |  |

| Input High Level XTAL1 and RST                                                                                           | V <sub>IH2</sub>                                                            | 3.5  |      | V <sub>CC</sub> + 0.3 | V     | 2     |  |

| Output Low Voltage Ports 1, 3<br>at $I_{OL} = 1.6 \text{mA}$                                                             | V <sub>OL1</sub>                                                            |      | 0.15 | 0.45                  | V     | 2     |  |

| Output Low Voltage Port 0, 2, ALE,<br>$\overrightarrow{PSEN}$ at $I_{OL} = 3.2mA$                                        | V <sub>OL2</sub>                                                            |      | 0.15 | 0.45                  | V     | 2, 6  |  |

| $\frac{\text{Output High Voltage Port 1, 3, ALE,}}{\overline{\text{PSEN}}} \text{ at } I_{\text{OH}} = -50 \mu \text{A}$ | V <sub>OH1</sub>                                                            | 2.4  |      |                       | V     | 2, 7  |  |

| Output High Voltage Ports 1, 3<br>at $I_{OH} = -1.5$ mA                                                                  | V <sub>OH2</sub>                                                            | 2.4  |      |                       | V     | 2, 8  |  |