Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                    |

|----------------------------|------------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                           |

| Core Processor             | ARM® Cortex®-M0                                                                    |

| Core Size                  | 32-Bit Single-Core                                                                 |

| Speed                      | 32MHz                                                                              |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, I <sup>2</sup> S, POR, PWM, WDT                            |

| Number of I/O              | 26                                                                                 |

| Program Memory Size        | 200KB (200K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 16K × 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                        |

| Data Converters            | A/D 16x12b                                                                         |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 38-TFSOP (0.173", 4.40mm Width)                                                    |

| Supplier Device Package    | PG-TSSOP-38                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xmc1302t038x0200aaxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Summary of Features

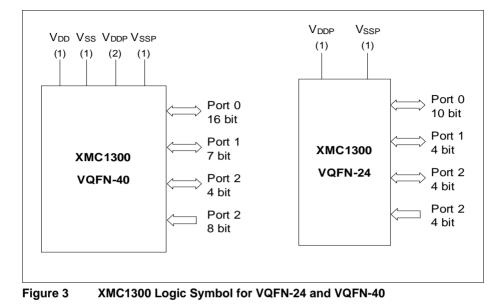

| Derivative   | ADC channel | ACMP | BCCU | MATH |  |

|--------------|-------------|------|------|------|--|

| XMC1301-T016 | 11          | 2    | -    | -    |  |

| XMC1302-T016 | 11          | 2    | 1    | 1    |  |

| XMC1301-T038 | 16          | 3    | -    | -    |  |

| XMC1302-T038 | 16          | 3    | 1    | 1    |  |

| XMC1301-Q024 | 13          | 3    | -    | -    |  |

| XMC1302-Q024 | 13          | 3    | 1    | 1    |  |

| XMC1301-Q040 | 16          | 3    |      |      |  |

| XMC1302-Q040 | 16          | 3    | 1    | 1    |  |

#### Table 2 Features of XMC1300 Device Types<sup>1)</sup>

1) Features that are not included in this table are available in all the derivatives

## Table 3ADC Channels 1)

| Package     | VADC0 G0 | VADC0 G1     |

|-------------|----------|--------------|

| PG-TSSOP-16 | CH0CH5   | CH0CH4       |

| PG-TSSOP-28 | CH0CH7   | CH0 CH4, CH7 |

| PG-TSSOP-38 | CH0CH7   | CH0CH7       |

| PG-VQFN-24  | CH0CH7   | CH0CH4       |

| PG-VQFN-40  | CH0CH7   | CH1, CH5 CH7 |

Some pins in a package may be connected to more than one channel. For the detailed mapping see the Port I/O Function table.

## 1.4 Chip Identification Number

The Chip Identification Number allows software to identify the marking. It is a 8 words value with the most significant 7 words stored in Flash configuration sector 0 (CS0) at address location :  $1000 0F00_{\rm H}$  (MSB) -  $1000 0F1B_{\rm H}$  (LSB). The least significant word and most significant word of the Chip Identification Number are the value of registers DBGROMID and IDCHIP, respectively.

#### **General Device Information**

#### **General Device Information**

| Function | VQFN<br>40 | TSSOP<br>38 | VQFN<br>24 | TSSOP<br>16 | Pad Type     | Notes                                                                                                                            |

|----------|------------|-------------|------------|-------------|--------------|----------------------------------------------------------------------------------------------------------------------------------|

| P0.13    | 38         | 32          | 24         | -           | STD_INOUT    |                                                                                                                                  |

| P0.14    | 39         | 33          | 23         | 13          | STD_INOUT    |                                                                                                                                  |

| P0.15    | 40         | 34          | 24         | 14          | STD_INOUT    |                                                                                                                                  |

| P1.0     | 22         | 16          | 14         | -           | High Current |                                                                                                                                  |

| P1.1     | 21         | 15          | 13         | -           | High Current |                                                                                                                                  |

| P1.2     | 20         | 14          | 12         | -           | High Current |                                                                                                                                  |

| P1.3     | 19         | 13          | 11         | -           | High Current |                                                                                                                                  |

| P1.4     | 18         | 12          | -          | -           | High Current |                                                                                                                                  |

| P1.5     | 17         | 11          | -          | -           | High Current |                                                                                                                                  |

| P1.6     | 16         | -           | -          | -           | STD_INOUT    |                                                                                                                                  |

| P2.0     | 1          | 35          | 1          | 15          | STD_INOUT/AN |                                                                                                                                  |

| P2.1     | 2          | 36          | 2          | -           | STD_INOUT/AN |                                                                                                                                  |

| P2.2     | 3          | 37          | 3          | -           | STD_IN/AN    |                                                                                                                                  |

| P2.3     | 4          | 38          | -          | -           | STD_IN/AN    |                                                                                                                                  |

| P2.4     | 5          | 1           | -          | -           | STD_IN/AN    |                                                                                                                                  |

| P2.5     | 6          | 2           | -          | -           | STD_IN/AN    |                                                                                                                                  |

| P2.6     | 7          | 3           | 4          | 16          | STD_IN/AN    |                                                                                                                                  |

| P2.7     | 8          | 4           | 5          | 1           | STD_IN/AN    |                                                                                                                                  |

| P2.8     | 9          | 5           | 5          | 1           | STD_IN/AN    |                                                                                                                                  |

| P2.9     | 10         | 6           | 6          | 2           | STD_IN/AN    |                                                                                                                                  |

| P2.10    | 11         | 7           | 7          | 3           | STD_INOUT/AN |                                                                                                                                  |

| P2.11    | 12         | 8           | 8          | 4           | STD_INOUT/AN |                                                                                                                                  |

| VSS      | 13         | 9           | 9          | 5           | Power        | Supply GND, ADC reference GND                                                                                                    |

| VDD      | 14         | 10          | 10         | 6           | Power        | Supply VDD, ADC<br>reference voltage/<br>ORC reference<br>voltage. VDD has to<br>be supplied with the<br>same voltage as<br>VDDP |

#### **General Device Information**

## 2.2.2 Port I/O Functions

The following general building block is used to describe each PORT pin:

| Table 7 | Port I/O | Function | Description |

|---------|----------|----------|-------------|

|         |          |          |             |

| Function |          | Outputs  |          | Inputs   |          |          |  |

|----------|----------|----------|----------|----------|----------|----------|--|

|          | ALT1     | ALTn     | HWO0     | HWI0     | Input    | Input    |  |

| P0.0     |          | MODA.OUT | MODB.OUT | MODB.INA | MODC.INA |          |  |

| Pn.y     | MODA.OUT |          |          |          | MODA.INA | MODC.INB |  |

Pn.y is the port pin name, defining the control and data bits/registers associated with it. As GPIO, the port is under software control. Its input value is read via Pn\_IN.y, Pn\_OUT defines the output value.

Up to seven alternate output functions (ALT1/2/3/4/5/6/7) can be mapped to a single port pin, selected by Pn\_IOCR.PC. The output value is directly driven by the respective module, with the pin characteristics controlled by the port registers (within the limits of the connected pad).

The port pin input can be connected to multiple peripherals. Most peripherals have an input multiplexer to select between different possible input sources.

The input path is also active while the pin is configured as output. This allows to feedback an output to on-chip resources without wasting an additional external pin.

By Pn\_HWSEL, it is possible to select between different hardware "masters" (HWO0/HWI0, HWO1/HWI1). The selected peripheral can take control of the pin(s). Hardware control overrules settings in the respective port pin registers.

#### Table 8 Port I/O Functions

| Function | Outputs                  |                       |                |                       |                 | Inputs                |                          |      |                     |      |                     |                   |                |                 |                |                    |                    |                    |                |                |                    |

|----------|--------------------------|-----------------------|----------------|-----------------------|-----------------|-----------------------|--------------------------|------|---------------------|------|---------------------|-------------------|----------------|-----------------|----------------|--------------------|--------------------|--------------------|----------------|----------------|--------------------|

|          | ALT1                     | ALT2                  | ALT3           | ALT4                  | ALT5            | ALT6                  | ALT7                     | HWO0 | HWO1                | HWIO | HWI1                | Input             | Input          | Input           | Input          | Input              | Input              | Input              | Input          | Input          | Input              |

| P0.0     | ERU0.<br>PDOUT0          |                       | ERU0.<br>GOUT0 | CCU40.<br>OUT0        | CCU80.<br>OUT00 | USIC0_CH0<br>.SELO0   | USIC0_CH1<br>.SELO0      |      |                     |      |                     | BCCU0.<br>TRAPINB | CCU40.<br>INOC |                 |                | USIC0_CH0<br>.DX2A | USIC0_CH1<br>.DX2A |                    |                |                |                    |

| P0.1     | ERU0.<br>PDOUT1          |                       | ERU0.<br>GOUT1 | CCU40.<br>OUT1        | CCU80.<br>OUT01 | BCCU0.<br>OUT8        | SCU.<br>VDROP            |      |                     |      |                     |                   | CCU40.<br>IN1C |                 |                |                    |                    |                    |                |                |                    |

| P0.2     | ERU0.<br>PDOUT2          |                       | ERU0.<br>GOUT2 | CCU40.<br>OUT2        | CCU80.<br>OUT02 | VADC0.<br>EMUX02      | CCU80.<br>OUT10          |      |                     |      |                     |                   | CCU40.<br>IN2C |                 |                |                    |                    |                    |                |                |                    |

| P0.3     | ERU0.<br>PDOUT3          |                       | ERU0.<br>GOUT3 | CCU40.<br>OUT3        | CCU80.<br>OUT03 | VADC0.<br>EMUX01      | CCU80.<br>OUT11          |      |                     |      |                     |                   | CCU40.<br>IN3C |                 |                |                    |                    |                    |                |                |                    |

| P0.4     | BCCU0.<br>OUT0           |                       |                | CCU40.<br>OUT1        | CCU80.<br>OUT13 | VADC0.<br>EMUX00      | WWDT.<br>SERVICE_<br>OUT |      |                     |      |                     |                   | CCU80.<br>INOB |                 |                |                    |                    |                    |                |                |                    |

| P0.5     | BCCU0.<br>OUT1           |                       |                | CCU40.<br>OUT0        | CCU80.<br>OUT12 | ACMP2.<br>OUT         | CCU80.<br>OUT01          |      |                     |      |                     |                   | CCU80.<br>IN1B |                 |                |                    |                    |                    |                |                |                    |

| P0.6     | BCCU0.<br>OUT2           |                       |                | CCU40.<br>OUT0        | CCU80.<br>OUT11 | USIC0_CH1<br>.MCLKOUT | USIC0_CH1<br>.DOUT0      |      |                     |      |                     |                   | CCU40.<br>INOB |                 |                | USIC0_CH1<br>.DX0C |                    |                    |                |                |                    |

| P0.7     | BCCU0.<br>OUT3           |                       |                | CCU40.<br>OUT1        | CCU80.<br>OUT10 | USIC0_CH0<br>.SCLKOUT | USIC0_CH1<br>.DOUT0      |      |                     |      |                     |                   | CCU40.<br>IN1B |                 |                | USIC0_CH0<br>.DX1C | USIC0_CH1<br>.DX0D | USIC0_CH1<br>.DX1C |                |                |                    |

| P0.8     | BCCU0.<br>OUT4           |                       |                | CCU40.<br>OUT2        | CCU80.<br>OUT20 | USIC0_CH0<br>.SCLKOUT | USIC0_CH1<br>.SCLKOUT    |      |                     |      |                     |                   | CCU40.<br>IN2B |                 |                | USIC0_CH0<br>.DX1B | USIC0_CH1<br>.DX1B |                    |                |                |                    |

| P0.9     | BCCU0.<br>OUT5           |                       |                | CCU40.<br>OUT3        | CCU80.<br>OUT21 | USIC0_CH0<br>.SELO0   | USIC0_CH1<br>.SELO0      |      |                     |      |                     |                   | CCU40.<br>IN3B |                 |                | USIC0_CH0<br>.DX2B | USIC0_CH1<br>.DX2B |                    |                |                |                    |

| P0.10    | BCCU0.<br>OUT6           |                       |                | ACMP0.<br>OUT         | CCU80.<br>OUT22 | USIC0_CH0<br>.SELO1   | USIC0_CH1<br>.SELO1      |      |                     |      |                     |                   | CCU80.<br>IN2B |                 |                | USIC0_CH0<br>.DX2C | USIC0_CH1<br>.DX2C |                    |                |                |                    |

| P0.11    | BCCU0.<br>OUT7           |                       |                | USIC0_CH0<br>.MCLKOUT | CCU80.<br>OUT23 | USIC0_CH0<br>.SELO2   | USIC0_CH1<br>.SELO2      |      |                     |      |                     |                   |                |                 |                | USIC0_CH0<br>.DX2D | USIC0_CH1<br>.DX2D |                    |                |                |                    |

| P0.12    | BCCU0.<br>OUT6           |                       |                |                       | CCU80.<br>OUT33 | USIC0_CH0<br>.SELO3   | CCU80.<br>OUT20          |      |                     |      |                     | BCCU0.<br>TRAPINA | CCU40.<br>IN0A | CCU40.<br>IN1A  | CCU40.<br>IN2A | CCU40.<br>IN3A     | CCU80.<br>IN0A     | CCU80.<br>IN1A     | CCU80.<br>IN2A | CCU80.<br>IN3A | USIC0_CH0<br>.DX2E |

| P0.13    | WWDT.<br>SERVICE_<br>OUT |                       |                |                       | CCU80.<br>OUT32 | USIC0_CH0<br>.SELO4   | CCU80.<br>OUT21          |      |                     |      |                     |                   | CCU80.<br>IN3B | POSIF0.<br>IN0B |                | USIC0_CH0<br>.DX2F |                    |                    |                |                |                    |

| P0.14    | BCCU0.<br>OUT7           |                       |                |                       | CCU80.<br>OUT31 | USIC0_CH0<br>.DOUT0   | USIC0_CH0<br>.SCLKOUT    |      |                     |      |                     |                   |                | POSIF0.<br>IN1B |                | USIC0_CH0<br>.DX0A | USIC0_CH0<br>.DX1A |                    |                |                |                    |

| P0.15    | BCCU0.<br>OUT8           |                       |                |                       | CCU80.<br>OUT30 | USIC0_CH0<br>.DOUT0   | USIC0_CH1<br>.MCLKOUT    |      |                     |      |                     |                   |                | POSIF0.<br>IN2B |                | USIC0_CH0<br>.DX0B |                    |                    |                |                |                    |

| P1.0     | BCCU0.<br>OUT0           | CCU40.<br>OUT0        |                |                       | CCU80.<br>OUT00 | ACMP1.<br>OUT         | USIC0_CH0<br>.DOUT0      |      | USIC0_CH0<br>.DOUT0 |      | USIC0_CH0<br>.HWIN0 |                   |                | POSIF0.<br>IN2A |                | USIC0_CH0<br>.DX0C |                    |                    |                |                |                    |

| P1.1     | VADC0.<br>EMUX00         | CCU40.<br>OUT1        |                |                       | CCU80.<br>OUT01 | USIC0_CH0<br>.DOUT0   | USIC0_CH1<br>.SELO0      |      | USIC0_CH0<br>.DOUT1 |      | USIC0_CH0<br>.HWIN1 |                   |                | POSIF0.<br>IN1A |                | USIC0_CH0<br>.DX0D | USIC0_CH0<br>.DX1D | USIC0_CH1<br>.DX2E |                |                |                    |

| P1.2     | VADC0.<br>EMUX01         | CCU40.<br>OUT2        |                |                       | CCU80.<br>OUT10 | ACMP2.<br>OUT         | USIC0_CH1<br>.DOUT0      |      | USIC0_CH0<br>.DOUT2 |      | USIC0_CH0<br>.HWIN2 |                   |                | POSIF0.<br>IN0A |                | USIC0_CH1<br>.DX0B |                    |                    |                |                |                    |

| P1.3     | VADC0.<br>EMUX02         | CCU40.<br>OUT3        |                |                       | CCU80.<br>OUT11 | USIC0_CH1<br>.SCLKOUT | USIC0_CH1<br>.DOUT0      |      | USIC0_CH0<br>.DOUT3 |      | USIC0_CH0<br>.HWIN3 |                   |                |                 |                | USIC0_CH1<br>.DX0A | USIC0_CH1<br>.DX1A |                    |                |                |                    |

| P1.4     | VADC0.<br>EMUX10         | USIC0_CH1<br>.SCLKOUT |                |                       | CCU80.<br>OUT20 | USIC0_CH0<br>.SELO0   | USIC0_CH1<br>.SELO1      |      |                     |      |                     |                   |                |                 |                | USIC0_CH0<br>.DX5E | USIC0_CH1<br>.DX5E |                    |                |                |                    |

| P1.5     | VADC0.<br>EMUX11         | USIC0_CH0<br>.DOUT0   |                | BCCU0.<br>OUT1        | CCU80.<br>OUT21 | USIC0_CH0<br>.SELO1   | USIC0_CH1<br>.SELO2      |      |                     |      |                     |                   |                |                 |                | USIC0_CH1<br>.DX5F |                    |                    |                |                |                    |

#### Table 11 Input/Output Characteristics (Operating Conditions apply) (cont'd)

| Parameter                                                                                                   | Symbo              | bl | Limit | Values | Unit | Test Conditions |

|-------------------------------------------------------------------------------------------------------------|--------------------|----|-------|--------|------|-----------------|

|                                                                                                             |                    |    | Min.  | Max.   | _    |                 |

| Maximum current into $V_{\text{DDP}}$ (TSSOP16, VQFN24)                                                     | I <sub>MVDD1</sub> | SR | -     | 130    | mA   | 3)              |

| Maximum current into $V_{\text{DDP}}$ (TSSOP38, VQFN40)                                                     | I <sub>MVDD2</sub> | SR | -     | 260    | mA   | 3)              |

| $\begin{tabular}{l} \hline \hline Maximum current out of \\ $V_{\rm SS}$ (TSSOP16, $VQFN24$) \end{tabular}$ | I <sub>MVSS1</sub> | SR | -     | 130    | mA   | 3)              |

| $\begin{tabular}{l} \hline $W$ aximum current out of $V_{SS}$ (TSSOP38, $VQFN40$) \end{tabular}$            | I <sub>MVSS2</sub> | SR | -     | 260    | mA   | 3)              |

Not subject to production test, verified by design/characterization. Hysteresis is implemented to avoid meta stable states and switching due to internal ground bounce. It cannot be guaranteed that it suppresses switching due to external system noise.

2) An additional error current ( $I_{INJ}$ ) will flow if an overload current flows through an adjacent pin.

3) Not subject to production test, verified by design/characterization.

4) Not subject to production test, verified by design/characterization. However, for applications with strict low power-down current requirements, it is mandatory that no active voltage source is supplied at any GPIO pin when V<sub>DDP</sub> is powered off.

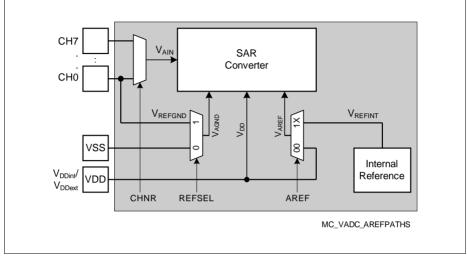

## 3.2.2 Analog to Digital Converters (ADC)

Table 12 shows the Analog to Digital Converter (ADC) characteristics.

| Table 12 | ADC Characteristics | (Operating Conditions apply) |

|----------|---------------------|------------------------------|

|          | ADO Onalacterístics | (operating conditions apply) |

| Parameter                                                  | Symbol                              |                            | Value | S                          | Unit           | Note /                                          |  |

|------------------------------------------------------------|-------------------------------------|----------------------------|-------|----------------------------|----------------|-------------------------------------------------|--|

|                                                            |                                     | Min. Typ. Max.             |       |                            | Test Condition |                                                 |  |

| Supply voltage range (internal reference)                  | $V_{\rm DD\_int}{\rm SR}$           | 1.8                        | -     | 3.0                        | V              | SHSCFG.AREF = 11 <sub>B</sub>                   |  |

|                                                            |                                     | 3.0                        | -     | 5.5                        | V              | SHSCFG.AREF = 10 <sub>B</sub>                   |  |

| Supply voltage range (external reference)                  | $V_{\rm DD\_ext}{\rm SR}$           | 3.0                        | -     | 5.5                        | V              | SHSCFG.AREF = 00 <sub>B</sub>                   |  |

| Analog input voltage range                                 | $V_{\rm AIN}{ m SR}$                | V <sub>SSP</sub><br>- 0.05 | -     | V <sub>DDP</sub><br>+ 0.05 | V              |                                                 |  |

| Auxiliary analog<br>reference ground<br>(SH0-CH0, SH1-CH0) | $V_{REFGND}SR$                      | V <sub>SSP</sub><br>- 0.05 | -     | V <sub>DDP</sub><br>+ 0.05 | V              |                                                 |  |

| Internal reference                                         | $V_{REFINT}CC$                      | 4.82                       | 5     | 5.18                       | V              | -40°C - 105°C                                   |  |

| voltage (full scale<br>value)                              |                                     | 4.9                        | 5     | 5.1                        | V              | 0°C - 85°C <sup>1)</sup>                        |  |

| Switched capacitance of an analog input <sup>1)</sup>      | $C_{\text{AINS}}$ CC                | -                          | 1.2   | 2                          | pF             | GNCTRxz.GAINy<br>= 00 <sub>B</sub> (unity gain) |  |

|                                                            |                                     | -                          | 1.2   | 2                          | pF             | GNCTRxz.GAINy<br>= 01 <sub>B</sub> (gain g1)    |  |

|                                                            |                                     | -                          | 4.5   | 6                          | pF             | GNCTRxz.GAINy<br>= 10 <sub>B</sub> (gain g2)    |  |

|                                                            |                                     | -                          | 4.5   | 6                          | pF             | GNCTRxz.GAINy<br>= 11 <sub>B</sub> (gain g3)    |  |

| Total capacitance of an analog input                       | $C_{\text{AINT}} \operatorname{CC}$ | -                          | -     | 10                         | pF             | 1)                                              |  |

| Total capacitance of the reference input                   | $C_{AREFT}CC$                       | -                          | -     | 10                         | pF             | 1)                                              |  |

## 3.2.4 Analog Comparator Characteristics

Table 14 below shows the Analog Comparator characteristics.

## Table 14 Analog Comparator Characteristics (Operating Conditions apply)

| Parameter                            | Symbol              |    | Li    | mit Val | ues                     | Unit | Notes/<br>Test Conditions                                          |  |

|--------------------------------------|---------------------|----|-------|---------|-------------------------|------|--------------------------------------------------------------------|--|

|                                      |                     |    | Min.  | Тур.    | Max.                    |      |                                                                    |  |

| Input Voltage                        | V <sub>CMP</sub>    | SR | -0.05 | -       | V <sub>DDP</sub> + 0.05 | V    |                                                                    |  |

| Input Offset                         | V <sub>CMPOFF</sub> | CC | -     | +/-3    | -                       | mV   | High power mode $\Delta V_{\rm CMP}$ < 200 mV                      |  |

|                                      |                     |    | -     | +/-20   | -                       | mV   | Low power mode <sup>2)</sup> $\Delta V_{\rm CMP}$ < 200 mV         |  |

| Propagation<br>Delay <sup>1)2)</sup> | t <sub>PDELAY</sub> | CC | -     | 25      | -                       | ns   | High power mode, $\Delta V_{\rm CMP}$ = 100 mV                     |  |

|                                      |                     |    | -     | 80      | -                       | ns   | High power mode,<br>$\Delta V_{\rm CMP}$ = 25 mV                   |  |

|                                      |                     |    | -     | 250     | -                       | ns   | Low power mode,<br>$\Delta V_{\rm CMP}$ = 100 mV                   |  |

|                                      |                     |    | -     | 700     | -                       | ns   | Low power mode,<br>$\Delta V_{\rm CMP}$ = 25 mV                    |  |

| Current<br>Consumption <sup>2)</sup> | I <sub>ACMP</sub>   | CC | -     | 100     | -                       | μA   | First active ACMP in high power mode, $\Delta V_{\rm CMP}$ > 30 mV |  |

|                                      |                     |    | -     | 66      | -                       | μA   | Each additional ACMP in high power mode, $\Delta V_{CMP}$ > 30 mV  |  |

|                                      |                     |    | -     | 10      | -                       | μΑ   | First active ACMP in<br>low power mode                             |  |

|                                      |                     |    | _     | 6       | -                       | μA   | Each additional<br>ACMP in low power<br>mode                       |  |

| Input Hysteresis <sup>2)</sup>       | $V_{\rm HYS}$       | СС | -     | 15      | -                       | mV   |                                                                    |  |

| Filter Delay <sup>1)2)</sup>         | t <sub>FDELAY</sub> | СС | -     | 5       | -                       | ns   |                                                                    |  |

37

1) Total Analog Comparator Delay is the sum of Propagation Delay and Filter Delay.

2) Not subject to production test, verified by design.

**Table 17** provides the active current consumption of some modules operating at 5 V power supply at 25 °C. The typical values shown are used as a reference guide on the current consumption when these modules are enabled.

| Active Current<br>Consumption | Symbol                | Limit<br>Values | Unit | Test Condition                                                    |

|-------------------------------|-----------------------|-----------------|------|-------------------------------------------------------------------|

|                               |                       | Тур.            |      |                                                                   |

| Baseload current              | I <sub>CPUDDC</sub>   | 5.04            | mA   | Modules including Core, SCU, PORT, memories, ANATOP <sup>2)</sup> |

| VADC and SHS                  | I <sub>ADCDDC</sub>   | 3.4             | mA   | Set CGATCLR0.VADC to 1 <sup>3)</sup>                              |

| USIC0                         | I <sub>USICODDC</sub> | 0.87            | mA   | Set CGATCLR0.USIC0 to 14)                                         |

| CCU40                         | I <sub>CCU40DDC</sub> | 0.94            | mA   | Set CGATCLR0.CCU40 to 1 <sup>5)</sup>                             |

| CCU80                         | I <sub>CCU80DDC</sub> | 0.42            | mA   | Set CGATCLR0.CCU80 to 16)                                         |

| POSIF0                        | I <sub>PIF0DDC</sub>  | 0.26            | mA   | Set CGATCLR0.POSIF0 to 17)                                        |

| BCCU0                         | I <sub>BCCU0DDC</sub> | 0.24            | mA   | Set CGATCLR0.BCCU0 to 18)                                         |

| MATH                          | I <sub>MATHDDC</sub>  | 0.35            | mA   | Set CGATCLR0.MATH to 19)                                          |

| WDT                           | I <sub>WDTDDC</sub>   | 0.03            | mA   | Set CGATCLR0.WDT to 1 <sup>10)</sup>                              |

| RTC                           | I <sub>RTCDDC</sub>   | 0.01            | mA   | Set CGATCLR0.RTC to 1 <sup>11)</sup>                              |

Table 17 Typical Active Current Consumption<sup>1)</sup>

1) Not subject to production test, verified by design/characterisation.

2) Baseload current is measured with device running in user mode, MCLK=PCLK=32 MHz, with an endless loop in the flash memory. The clock to the modules stated in CGATSTAT0 are gated.

3) Active current is measured with: module enabled, MCLK=32 MHz, running in auto-scan conversion mode

4) Active current is measured with: module enabled, alternating messages sent to PC at 57.6kbaud every 200ms

- Active current is measured with: module enabled, MCLK=PCLK=32 MHz, 1 CCU4 slice for PWM switching from 1500Hz and 1000Hz at regular intervals, 1 CCU4 slice in capture mode for reading period and duty cycle

- 6) Active current is measured with: module enabled, MCLK=PCLK=32 MHz, 1 CCU8 slice with PWM frequency at 1500Hz and a period match interrupt used to toggle duty cycle between 10% and 90%

- 7) Active current is measured with: module enabled, MCLK=32 MHz, PCLK=64MHz, hall sensor mode

- Active current is measured with: module enabled, MCLK=32 MHz, PCLK=64MHz, FCLK=0.8MHz, Normal mode (BCCU Clk = FCLK/4), 3 BCCU Channels and 1 Dimming Engine, change color or dim every 1s

- Active current is measured with: module enabled, MCLK=32 MHz, PCLK=64MHz, tangent calculation in while loop; CORDIC circular rotation, no keep, autostart; 32-by-32 bit signed DIV, autostart, DVS right shift by 11

- 10) Active current is measured with: module enabled, MCLK=32 MHz, time-out mode; WLB = 0, WUB = 0x00008000; WDT serviced every 1s

40

11) Active current is measured with: module enabled, MCLK=32 MHz, Periodic interrupt enabled

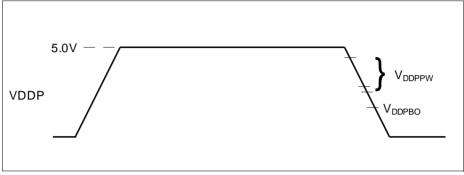

## 3.3.3 Power-Up and Supply Threshold Charcteristics

Table 20 provides the characteristics of the supply threshold in XMC1300.

# Table 20Power-Up and Supply Threshold Parameters (Operating Conditions apply) 1)

| Parameter                            | Symbol                         | \<br>\                                                           | /alues |                 | Unit | Note /                                                                      |  |

|--------------------------------------|--------------------------------|------------------------------------------------------------------|--------|-----------------|------|-----------------------------------------------------------------------------|--|

|                                      |                                | Min.                                                             | Тур.   | Max.            |      | Test Condition                                                              |  |

| $V_{\rm DDP}$ ramp-up time           | t <sub>RAMPUP</sub> SR         | $\begin{array}{c} V_{\rm DDP} / \\ S_{\rm VDDPrise} \end{array}$ | -      | 10 <sup>7</sup> | μS   |                                                                             |  |

| $V_{\text{DDP}}$ slew rate           | $S_{\rm VDDPOP}{ m SR}$        | 0                                                                | -      | 0.1             | V/µs | Slope during normal operation                                               |  |

|                                      | $S_{\rm VDDP10}~{ m SR}$       | 0                                                                | -      | 10              | V/µs | Slope during fast transient within +/- 10% of $V_{\rm DDP}$                 |  |

|                                      | S <sub>VDDPrise</sub> SR       | 0                                                                | -      | 10              | V/µs | Slope during<br>power-on or<br>restart after<br>brownout event              |  |

|                                      | $S_{\rm VDDPfall}^{2)}{ m SR}$ | 0                                                                | _      | 0.25            | V/µs | Slope during<br>supply falling out<br>of the +/-10%<br>limits <sup>3)</sup> |  |

| $V_{\text{DDP}}$ prewarning voltage  | $V_{DDPPW}CC$                  | 2.1                                                              | 2.25   | 2.4             | V    | ANAVDEL.VDEL_<br>SELECT = 00 <sub>B</sub>                                   |  |

|                                      |                                | 2.85                                                             | 3      | 3.15            | V    | ANAVDEL.VDEL_<br>SELECT = 01 <sub>B</sub>                                   |  |

|                                      |                                | 4.2                                                              | 4.4    | 4.6             | V    | ANAVDEL.VDEL_<br>SELECT = 10 <sub>B</sub>                                   |  |

| $V_{\rm DDP}$ brownout reset voltage | V <sub>DDPBO</sub> CC          | 1.55                                                             | 1.62   | 1.75            | V    | calibrated, before<br>user code starts<br>running                           |  |

| Start-up time from<br>power-on reset | t <sub>SSW</sub> SR            | _                                                                | 320    | -               | μs   | Time to the first<br>user code<br>instruction <sup>4)</sup>                 |  |

1) Not all parameters are 100% tested, but are verified by design/characterisation.

A capacitor of at least 100 nF has to be added between V<sub>DDP</sub> and V<sub>SSP</sub> to fulfill the requirement as stated for this parameter.

44

- 3) Valid for a 100 nF buffer capacitor connected to supply pin where current from capacitor is forwarded only to the chip. A larger capacitor value has to be chosen if the power source sink a current.

- 4) This values does not include the ramp-up time. During startup firmware execution, MCLK is running at 32 MHz and the clocks to peripheral as specified in register CGATSTAT0 are gated.

45

Figure 13 Supply Threshold Parameters

## 3.3.4 On-Chip Oscillator Characteristics

Table 21 provides the characteristics of the 64 MHz clock output from the digital controlled oscillator, DCO1 in XMC1300.

| Parameter                                                   | Symbol              |    | Lir  | nit Val | ues  | Unit | Test Conditions                                                                                             |

|-------------------------------------------------------------|---------------------|----|------|---------|------|------|-------------------------------------------------------------------------------------------------------------|

|                                                             |                     |    | Min. | Тур.    | Max. |      |                                                                                                             |

| Nominal frequency                                           | $f_{\sf NOM}$       | CC | 63.5 | 64      | 64.5 | MHz  | under nominal<br>conditions <sup>1)</sup> after<br>trimming                                                 |

| Accuracy                                                    | $\Delta f_{\rm LT}$ | CC | -1.7 | -       | 3.4  | %    | with respect to $f_{NOM}(typ)$ ,<br>over temperature<br>$(T_A = 0 \ ^{\circ}C \ to \ 85 \ ^{\circ}C)^{2)}$  |

|                                                             |                     |    | -3.9 | -       | 4.0  | %    | with respect to $f_{NOM}(typ)$ ,<br>over temperature<br>$(T_A = -40 \text{ °C to } 105 \text{ °C})^{2)}$    |

| Accuracy with<br>calibration based on<br>temperature sensor | $\Delta f_{LTT}$    | CC | -1.3 | -       | 1.25 | %    | with respect to $f_{NOM}(typ)$ ,<br>over temperature<br>$(T_A = 0 \ ^{\circ}C \ to \ 105 \ ^{\circ}C)^{2)}$ |

|                                                             |                     |    | -2.6 | -       | 1.25 | %    | with respect to $f_{NOM}$ (typ),<br>over temperature<br>$(T_A = -40 \text{ °C to } 105 \text{ °C})^{2)}$    |

1) The deviation is relative to the factory trimmed frequency at nominal  $V_{\text{DDC}}$  and  $T_{\text{A}}$  = + 25 °C.

2) Not subject to production test, verified by design/characterisation.

## 3.3.7 Peripheral Timings

## 3.3.7.1 Synchronous Serial Interface (USIC SSC) Timing

The following parameters are applicable for a USIC channel operated in SSC mode. *Note: Operating Conditions apply.*

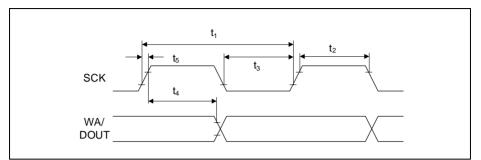

#### Table 25 USIC SSC Master Mode Timing

| Parameter                                                               | Symbol                |    |      | Values | 8    | Unit | Note /         |

|-------------------------------------------------------------------------|-----------------------|----|------|--------|------|------|----------------|

|                                                                         |                       |    | Min. | Тур.   | Max. |      | Test Condition |

| Slave select output SELO<br>active to first SCLKOUT<br>transmit edge    | <i>t</i> <sub>1</sub> | CC | 80   | -      | -    | ns   |                |

| Slave select output SELO<br>inactive after last<br>SCLKOUT receive edge | <i>t</i> <sub>2</sub> | CC | 0    | -      | -    | ns   |                |

| Data output DOUT[3:0] valid time                                        | <i>t</i> <sub>3</sub> | СС | -10  | -      | 10   | ns   |                |

| Receive data input<br>DX0/DX[5:3] setup time to<br>SCLKOUT receive edge | <i>t</i> <sub>4</sub> | SR | 80   | -      | -    | ns   |                |

| Data input DX0/DX[5:3]<br>hold time from SCLKOUT<br>receive edge        | <i>t</i> <sub>5</sub> | SR | 0    | -      | -    | ns   |                |

#### Table 26 USIC SSC Slave Mode Timing

| Parameter                                                                         | Symbol                   |   | Values |      |      | Unit | Note /         |

|-----------------------------------------------------------------------------------|--------------------------|---|--------|------|------|------|----------------|

|                                                                                   |                          |   | Min.   | Тур. | Max. |      | Test Condition |

| Select input DX2 setup to first clock input DX1 transmit edge <sup>1)</sup>       | <i>t</i> <sub>10</sub> S | R | 10     | _    | _    | ns   |                |

| Select input DX2 hold after<br>last clock input DX1 receive<br>edge <sup>1)</sup> | <i>t</i> <sub>11</sub> S | R | 10     | _    | _    | ns   |                |

Note: These parameters are not subject to production test, but verified by design and/or characterization.

time

#### **Electrical Parameter**

| Table 20 USIC SSC Slave Mode Timing (cont d)                                              |                 |    |           |       |    |                |        |  |

|-------------------------------------------------------------------------------------------|-----------------|----|-----------|-------|----|----------------|--------|--|

| Parameter                                                                                 | Symbol          |    |           | Value | S  | Unit           | Note / |  |

|                                                                                           |                 |    | Min. Typ. | Max.  |    | Test Condition |        |  |

| Receive data input<br>DX0/DX[5:3] setup time to<br>shift clock receive edge <sup>1)</sup> | t <sub>12</sub> | SR | 10        | -     | _  | ns             |        |  |

| Data input DX0/DX[5:3] hold<br>time from clock input DX1<br>receive edge <sup>1)</sup>    | t <sub>13</sub> | SR | 10        | -     | _  | ns             |        |  |

| Data output DOUT[3:0] valid                                                               | t <sub>14</sub> | CC | -         | -     | 80 | ns             |        |  |

## Table 26 USIC SSC Slave Mode Timing (cont'd)

1) These input timings are valid for asynchronous input signal handling of slave select input, shift clock input, and receive data input (bits DXnCR.DSEN = 0).

| Figure 18 | USIC IIS Master | Transmitter Timin | g |

|-----------|-----------------|-------------------|---|

|-----------|-----------------|-------------------|---|

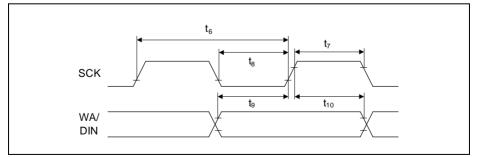

| Parameter    | Symbol             |                             | Values |      | Unit | Note /<br>Test Condition |

|--------------|--------------------|-----------------------------|--------|------|------|--------------------------|

|              |                    | Min.                        | Тур.   | Max. |      |                          |

| Clock period | t <sub>6</sub> SR  | 4/f <sub>MCLK</sub>         | -      | -    | ns   |                          |

| Clock HIGH   | t <sub>7</sub> SR  | 0.35 x<br>t <sub>6min</sub> | -      | -    | ns   |                          |

| Clock Low    | t <sub>8</sub> SR  | 0.35 x<br>t <sub>6min</sub> | -      | -    | ns   |                          |

| Set-up time  | t <sub>9</sub> SR  | 0.2 x<br>t <sub>6min</sub>  | -      | -    | ns   |                          |

| Hold time    | t <sub>10</sub> SR | 10                          | -      | -    | ns   |                          |

| Table 30 | USIC IIS Slave | Receiver | Timing |

|----------|----------------|----------|--------|

|----------|----------------|----------|--------|

Figure 19 USIC IIS Slave Receiver Timing

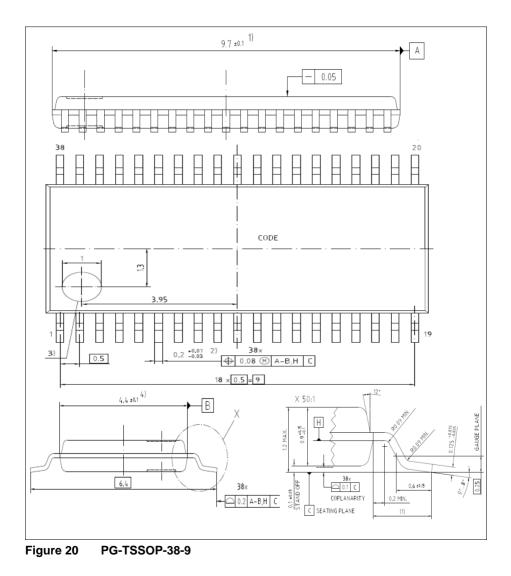

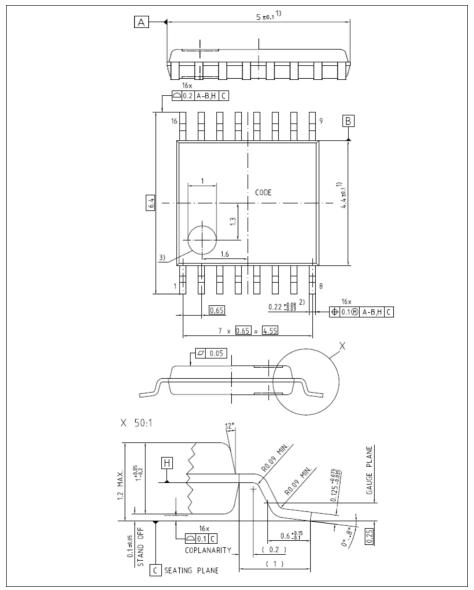

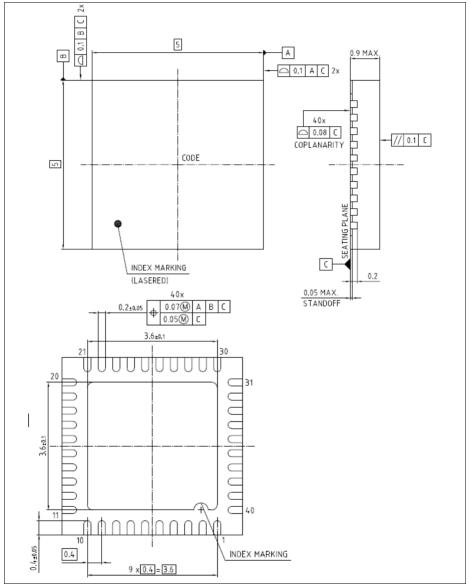

Package and Reliability

## 4.2 Package Outlines

## XMC1300 XMC1000 Family

## Package and Reliability

Figure 21 PG-TSSOP-16-8

### Package and Reliability

## Figure 23 PG-VQFN-40-13

All dimensions in mm.

www.infineon.com

Published by Infineon Technologies AG