#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 120MHz                                                                   |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, Memory Card, SPI, SSC, UART/USART, USB  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                               |

| Number of I/O              | 79                                                                       |

| Program Memory Size        | 1MB (1M x 8)                                                             |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                             |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                    |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 100-LQFP                                                                 |

| Supplier Device Package    | 100-LQFP (14x14)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4s16ca-an |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 16.6.1 RTC Control Register

| Name:    | RTC_CR     |    |    |    |    |          |        |

|----------|------------|----|----|----|----|----------|--------|

| Address: | 0x400E1460 |    |    |    |    |          |        |

| Access:  | Read/Write |    |    |    |    |          |        |

| 31       | 30         | 29 | 28 | 27 | 26 | 25       | 24     |

| _        | -          | _  | -  | _  | -  | _        | -      |

| 23       | 22         | 21 | 20 | 19 | 18 | 17       | 16     |

| _        | -          | _  | _  | _  | _  | CALE     | VSEL   |

| 15       | 14         | 13 | 12 | 11 | 10 | 9        | 8      |

| _        | -          | _  | _  | _  | _  | TIMEVSEL |        |

| 7        | 6          | 5  | 4  | 3  | 2  | 1        | 0      |

| -        | _          | _  | _  | _  | _  | UPDCAL   | UPDTIM |

This register can only be written if the WPEN bit is cleared in the System Controller Write Protection Mode Register (SYSC\_WPMR).

#### • UPDTIM: Update Request Time Register

0: No effect.

1: Stops the RTC time counting.

Time counting consists of second, minute and hour counters. Time counters can be programmed once this bit is set and acknowledged by the bit ACKUPD of the RTC\_SR.

#### • UPDCAL: Update Request Calendar Register

0: No effect.

1: Stops the RTC calendar counting.

Calendar counting consists of day, date, month, year and century counters. Calendar counters can be programmed once this bit is set and acknowledged by the bit ACKUPD of the RTC\_SR.

# • TIMEVSEL: Time Event Selection

The event that generates the flag TIMEV in RTC\_SR depends on the value of TIMEVSEL.

| Value | Name     | Description           |  |  |  |

|-------|----------|-----------------------|--|--|--|

| 0     | MINUTE   | Minute change         |  |  |  |

| 1     | HOUR     | Hour change           |  |  |  |

| 2     | MIDNIGHT | Every day at midnight |  |  |  |

| 3     | NOON     | Every day at noon     |  |  |  |

## Table 21-4. Write Handshake (Continued)

| Step | Programmer Action              | Device Action                        | Data I/O |

|------|--------------------------------|--------------------------------------|----------|

| 4    | Releases MODE and DATA signals | Executes command and polls NCMD high | Input    |

| 5    | Sets NCMD signal               | Executes command and polls NCMD high | Input    |

| 6    | Waits for RDY high             | Sets RDY                             | Input    |

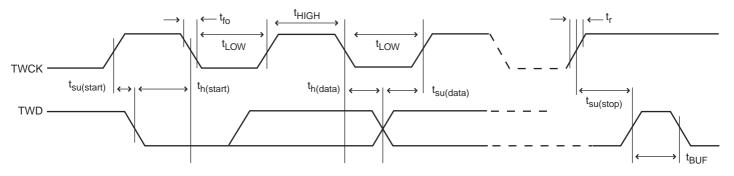

#### 21.3.4.2 Read Handshaking

For details on the read handshaking sequence, refer to Figure 21-3 and Table 21-5.

## Figure 21-3. Parallel Programming Timing, Read Sequence

#### Table 21-5. Read Handshake

| Step | Programmer Action            | Device Action                                                | DATA I/O |

|------|------------------------------|--------------------------------------------------------------|----------|

| 1    | Sets MODE and DATA signals   | Waits for NCMD low                                           | Input    |

| 2    | Clears NCMD signal           | Latch MODE and DATA                                          | Input    |

| 3    | Waits for RDY low            | Clears RDY signal                                            | Input    |

| 4    | Sets DATA signal in tristate | Waits for NOE Low                                            | Input    |

| 5    | Clears NOE signal            | _                                                            | Tristate |

| 6    | Waits for NVALID low         | Sets DATA bus in output mode and outputs the flash contents. | Output   |

| 7    | -                            | Clears NVALID signal                                         | Output   |

| 8    | Reads value on DATA Bus      | Waits for NOE high                                           | Output   |

| 9    | Sets NOE signal              |                                                              | Output   |

| 10   | Waits for NVALID high        | Sets DATA bus in input mode                                  | X        |

| 11   | Sets DATA in output mode     | Sets NVALID signal                                           | Input    |

| 12   | Sets NCMD signal             | Waits for NCMD high                                          | Input    |

| 13   | Waits for RDY high           | Sets RDY signal                                              | Input    |

# 23.7.13 CRCCU Interrupt Disable Register

| Name:    | CRCCU_IDR  |    |    |    |    |    |        |

|----------|------------|----|----|----|----|----|--------|

| Address: | 0x40044044 |    |    |    |    |    |        |

| Access:  | Write-only |    |    |    |    |    |        |

| 31       | 30         | 29 | 28 | 27 | 26 | 25 | 24     |

| _        | -          | _  | _  | -  | _  | _  | —      |

| 23       | 22         | 21 | 20 | 19 | 18 | 17 | 16     |

| -        | -          | -  | -  | -  | -  | -  | -      |

| 15       | 14         | 13 | 12 | 11 | 10 | 9  | 8      |

| -        | -          | -  | -  | -  | -  | -  | -      |

| 7        | 6          | 5  | 4  | 3  | 2  | 1  | 0      |

| _        | -          | _  | _  | _  | _  | _  | ERRIDR |

# • ERRIDR: CRC Error Interrupt Disable

0: No effect

1: Disable interrupt

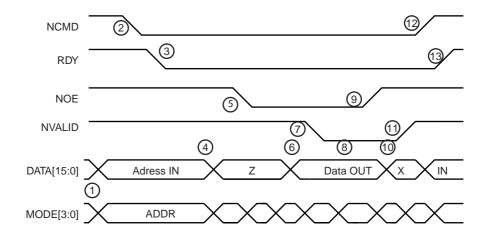

# 28.3 Block Diagram

Atmel

# 29.17.3 PMC System Clock Status Register

| Name:    | PMC_SCSR   |    |    |    |      |      |      |

|----------|------------|----|----|----|------|------|------|

| Address: | 0x400E0408 |    |    |    |      |      |      |

| Access:  | Read-only  |    |    |    |      |      |      |

| 31       | 30         | 29 | 28 | 27 | 26   | 25   | 24   |

| —        | -          | _  | _  | _  | _    | _    | _    |

|          |            |    |    |    |      |      |      |

| 23       | 22         | 21 | 20 | 19 | 18   | 17   | 16   |

| -        | -          | -  | -  | -  | -    | -    | -    |

|          | -          | -  | -  | -  | -    | -    |      |

| 15       | 14         | 13 | 12 | 11 | 10   | 9    | 8    |

| -        | _          | -  | -  | -  | PCK2 | PCK1 | PCK0 |

|          |            |    |    |    |      |      |      |

| 7        | 6          | 5  | 4  | 3  | 2    | 1    | 0    |

| UDP      | -          | _  | _  | _  | _    | _    | _    |

# • UDP: USB Device Port Clock Status

0: The 48 MHz clock (UDPCK) of the USB Device Port is disabled.

1: The 48 MHz clock (UDPCK) of the USB Device Port is enabled.

#### • PCKx: Programmable Clock x Output Status

0: The corresponding Programmable Clock output is disabled.

1: The corresponding Programmable Clock output is enabled.

#### 31.5.15 Register Write Protection

To prevent any single software error from corrupting PIO behavior, certain registers in the address space can be write-protected by setting the WPEN bit in the PIO Write Protection Mode Register (PIO\_WPMR).

If a write access to a write-protected register is detected, the WPVS flag in the PIO Write Protection Status Register (PIO\_WPSR) is set and the field WPVSRC indicates the register in which the write access has been attempted.

The WPVS bit is automatically cleared after reading the PIO\_WPSR.

The following registers can be write-protected:

- PIO Enable Register

- PIO Disable Register

- PIO Output Enable Register

- PIO Output Disable Register

- PIO Input Filter Enable Register

- PIO Input Filter Disable Register

- PIO Multi-driver Enable Register

- PIO Multi-driver Disable Register

- PIO Pull-Up Disable Register

- PIO Pull-Up Enable Register

- PIO Peripheral ABCD Select Register 1

- PIO Peripheral ABCD Select Register 2

- PIO Output Write Enable Register

- PIO Output Write Disable Register

- PIO Pad Pull-Down Disable Register

- PIO Pad Pull-Down Enable Register

- PIO Parallel Capture Mode Register

# 31.6.27 PIO Input Filter Slow Clock Enable Register

PIO\_IFSCER

| Address:<br>Access: | 0x400E0E84 (PI<br>Write-only | OA), 0x400E10 | 084 (PIOB), 0x4 | 00E1284 (PIO | C)  |     |     |

|---------------------|------------------------------|---------------|-----------------|--------------|-----|-----|-----|

| 31                  | 30                           | 29            | 28              | 27           | 26  | 25  | 24  |

| P31                 | P30                          | P29           | P28             | P27          | P26 | P25 | P24 |

| 23                  | 22                           | 21            | 20              | 19           | 18  | 17  | 16  |

| P23                 | P22                          | P21           | P20             | P19          | P18 | P17 | P16 |

| 15                  | 14                           | 13            | 12              | 11           | 10  | 9   | 8   |

| P15                 | P14                          | P13           | P12             | P11          | P10 | P9  | P8  |

| 7                   | 6                            | 5             | 4               | 3            | 2   | 1   | 0   |

| P7                  | P6                           | P5            | P4              | P3           | P2  | P1  | P0  |

# • P0–P31: Slow Clock Debouncing Filtering Select

0: No effect.

Name:

1: The debouncing filter is able to filter pulses with a duration <  $t_{div_{slck}}/2$ .

# 31.6.30 PIO Pad Pull-Down Disable Register

Name: PIO\_PPDDR

# Address: 0x400E0E90 (PIOA), 0x400E1090 (PIOB), 0x400E1290 (PIOC)

Access: Write-only

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

| P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

| P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

This register can only be written if the WPEN bit is cleared in the PIO Write Protection Mode Register.

# • P0-P31: Pull-Down Disable

0: No effect.

1: Disables the pull-down resistor on the I/O line.

# 36.7.22 USART Write Protection Mode Register

| Name:    | US_WPMR                        |    |     |     |    |    |      |  |  |  |

|----------|--------------------------------|----|-----|-----|----|----|------|--|--|--|

| Address: | 0x400240E4 (0), 0x400280E4 (1) |    |     |     |    |    |      |  |  |  |

| Access:  | Read/Write                     |    |     |     |    |    |      |  |  |  |

| 31       | 30                             | 29 | 28  | 27  | 26 | 25 | 24   |  |  |  |

|          |                                |    | WP  | KEY |    |    |      |  |  |  |

| 23       | 22                             | 21 | 20  | 19  | 18 | 17 | 16   |  |  |  |

|          |                                |    | VVP | KEY |    |    |      |  |  |  |

| 15       | 14                             | 13 | 12  | 11  | 10 | 9  | 8    |  |  |  |

|          |                                |    | WP  | KEY |    |    |      |  |  |  |

| 7        | 6                              | 5  | 4   | 3   | 2  | 1  | 0    |  |  |  |

| _        | _                              | _  | _   | _   | _  | _  | WPEN |  |  |  |

# • WPEN: Write Protection Enable

0: Disables the write protection if WPKEY corresponds to 0x555341 ("USA" in ASCII).

1: Enables the write protection if WPKEY corresponds to 0x555341 ("USA" in ASCII).

See Section 36.6.10 "Register Write Protection" for the list of registers that can be write-protected.

# • WPKEY: Write Protection Key

| Value    | Name   | Description                                                                                          |

|----------|--------|------------------------------------------------------------------------------------------------------|

| 0x555341 | PASSWD | Writing any other value in this field aborts the write operation of the WPEN bit. Always reads as 0. |

#### 39.7.1 PWM Clock Register

| Name:<br>Address: | PWM_CLK<br>0x40020000 |    |    |    |    |    |    |

|-------------------|-----------------------|----|----|----|----|----|----|

| Access:           | Read/Write            |    |    |    |    |    |    |

| 31                | 30                    | 29 | 28 | 27 | 26 | 25 | 24 |

| -                 | -                     | -  | -  |    | PR | EB |    |

| 23                | 22                    | 21 | 20 | 19 | 18 | 17 | 16 |

|                   |                       |    | DI | VB |    |    |    |

| 15                | 14                    | 13 | 12 | 11 | 10 | 9  | 8  |

| _                 | -                     | -  | _  |    | PR | EA |    |

| 7                 | 6                     | 5  | 4  | 3  | 2  | 1  | 0  |

|                   |                       |    | DI | VA |    |    |    |

This register can only be written if bits WPSWS0 and WPHWS0 are cleared in the PWM Write Protection Status Register.

#### • DIVA: CLKA Divide Factor

| Value | Name      | Description                                                 |

|-------|-----------|-------------------------------------------------------------|

| 0     | CLKA_POFF | CLKA clock is turned off                                    |

| 1     | PREA      | CLKA clock is clock selected by PREA                        |

| 2–255 | PREA_DIV  | CLKA clock is clock selected by PREA divided by DIVA factor |

#### • DIVB: CLKB Divide Factor

| Value | Name      | Description                                                 |

|-------|-----------|-------------------------------------------------------------|

| 0     | CLKB_POFF | CLKB clock is turned off                                    |

| 1     | PREB      | CLKB clock is clock selected by PREB                        |

| 2–255 | PREB_DIV  | CLKB clock is clock selected by PREB divided by DIVB factor |

## PREA: CLKA Source Clock Selection

| Value | Name       | Description          |

|-------|------------|----------------------|

| 0     | CLK        | Peripheral clock     |

| 1     | CLK_DIV2   | Peripheral clock/2   |

| 2     | CLK_DIV4   | Peripheral clock/4   |

| 3     | CLK_DIV8   | Peripheral clock/8   |

| 4     | CLK_DIV16  | Peripheral clock/16  |

| 5     | CLK_DIV32  | Peripheral clock/32  |

| 6     | CLK_DIV64  | Peripheral clock/64  |

| 7     | CLK_DIV128 | Peripheral clock/128 |

| 8     | CLK_DIV256 | Peripheral clock/256 |

# 39.7.5 PWM Interrupt Enable Register 1

| Name:    | PWM_IER1                 |    |    |        |        |        |        |

|----------|--------------------------|----|----|--------|--------|--------|--------|

| Address: | 0x40020010<br>Write-only |    |    |        |        |        |        |

| Access:  | write-only               |    |    |        |        |        |        |

| 31       | 30                       | 29 | 28 | 27     | 26     | 25     | 24     |

| -        | -                        | _  | -  | -      | -      | —      | -      |

|          | -                        | -  | -  | -      | -      | -      |        |

| 23       | 22                       | 21 | 20 | 19     | 18     | 17     | 16     |

| -        | -                        | -  | —  | FCHID3 | FCHID2 | FCHID1 | FCHID0 |

|          | -                        | -  | -  | -      | -      | -      |        |

| 15       | 14                       | 13 | 12 | 11     | 10     | 9      | 8      |

| -        | -                        | -  | -  | -      | -      | —      | -      |

|          |                          |    |    |        |        |        |        |

| 7        | 6                        | 5  | 4  | 3      | 2      | 1      | 0      |

| —        | —                        | —  | —  | CHID3  | CHID2  | CHID1  | CHID0  |

CHIDx: Counter Event on Channel x Interrupt Enable

• FCHIDx: Fault Protection Trigger on Channel x Interrupt Enable

# 39.7.12 PWM Sync Channels Update Period Update Register

| Name:    | PWM_SCUPUP | D  |    |    |     |     |    |

|----------|------------|----|----|----|-----|-----|----|

| Address: | 0x40020030 |    |    |    |     |     |    |

| Access:  | Write-only |    |    |    |     |     |    |

| 31       | 30         | 29 | 28 | 27 | 26  | 25  | 24 |

| _        | _          | —  | _  | —  | —   | _   | —  |

|          | -          | -  | -  | -  | -   | -   | -  |

| 23       | 22         | 21 | 20 | 19 | 18  | 17  | 16 |

| -        | -          | -  | _  | -  | -   | -   | -  |

| 15       | 14         | 13 | 12 | 11 | 10  | 9   | 8  |

| -        | -          | -  | —  | -  | -   | -   | -  |

| 7        | 6          | 5  | 4  | 3  | 2   | 1   | 0  |

| _        | —          | _  | _  |    | UPR | UPD |    |

This register acts as a double buffer for the UPR value. This prevents an unexpected automatic trigger of the update of synchronous channels.

## • UPRUPD: Update Period Update

Defines the wanted time between each update of the synchronous channels if automatic trigger of the update is activated (UPDM = 1 or UPDM = 2 in PWM Sync Channels Mode Register). This time is equal to UPR+1 periods of the synchronous channels.

This flag is used to generate a Data IN transaction (device to host). Device firmware checks that it can write a data payload in the FIFO, checking that TXPKTRDY is cleared. Transfer to the FIFO is done by writing in the UDP\_FDRx. Once the data payload has been transferred to the FIFO, the firmware notifies the USB device setting TXPKTRDY to one. USB bus transactions can start. TXCOMP is set once the data payload has been received by the host.

After setting or clearing this bit, a wait time of 3 UDPCK clock cycles and 3 peripheral clock cycles is required before accessing DPR.

# • FORCESTALL: Force Stall (used by Control, Bulk and Isochronous Endpoints)

Read:

0: Normal state

1: Stall state

Write:

0: Return to normal state

1: Send STALL to the host

Refer to chapters 8.4.5 and 9.4.5 of the Universal Serial Bus Specification, Rev. 2.0 for more information on the STALL handshake.

Control endpoints: During the data stage and status stage, this bit indicates that the microcontroller cannot complete the request.

Bulk and interrupt endpoints: This bit notifies the host that the endpoint is halted.

The host acknowledges the STALL, device firmware is notified by the STALLSENT flag.

# • RX\_DATA\_BK1: Receive Data Bank 1 (only used by endpoints with ping-pong attributes)

This flag generates an interrupt while it is set to one.

Write (cleared by the firmware):

0: Notifies USB device that data have been read in the FIFO's Bank 1.

1: To leave the read value unchanged.

Read (Set by the USB peripheral):

0: No data packet has been received in the FIFO's Bank 1.

1: A data packet has been received, it has been stored in FIFO's Bank 1.

When the device firmware has polled this bit or has been interrupted by this signal, it must transfer data from the FIFO to microcontroller memory. The number of bytes received is available in RXBYTECNT field. Bank 1 FIFO values are read through UDP\_FDRx. Once a transfer is done, the device firmware must release Bank 1 to the USB device by clearing RX\_DATA\_BK1.

After setting or clearing this bit, a wait time of 3 UDPCK clock cycles and 3 peripheral clock cycles is required before accessing DPR.

# • DIR: Transfer Direction (only available for control endpoints) (Read/Write)

0: Allows Data OUT transactions in the control data stage.

1: Enables Data IN transactions in the control data stage.

Refer to Chapter 8.5.3 of the Universal Serial Bus Specification, Rev. 2.0 for more information on the control data stage.

This bit must be set before UDP\_CSRx/RXSETUP is cleared at the end of the setup stage. According to the request sent in the setup data packet, the data stage is either a device to host (DIR = 1) or host to device (DIR = 0) data transfer. It is not necessary to check this bit to reverse direction for the status stage.

# 41.7.3 ACC Interrupt Enable Register

| Name:    | ACC_IER    |    |    |    |    |    |    |

|----------|------------|----|----|----|----|----|----|

| Address: | 0x40040024 |    |    |    |    |    |    |

| Access:  | Write-only |    |    |    |    |    |    |

| 31       | 30         | 29 | 28 | 27 | 26 | 25 | 24 |

| _        | -          | -  | -  | -  | -  | _  | -  |

| 23       | 22         | 21 | 20 | 19 | 18 | 17 | 16 |

| _        | -          | -  | —  | -  | —  | _  | -  |

| 15       | 14         | 13 | 12 | 11 | 10 | 9  | 8  |

| -        | -          | -  | -  | -  | -  | -  | -  |

| 7        | 6          | 5  | 4  | 3  | 2  | 1  | 0  |

| -        | —          | _  | _  | _  | _  | _  | CE |

# • CE: Comparison Edge

0: No effect.

1: Enables the interrupt when the selected edge (defined by EDGETYP) occurs.

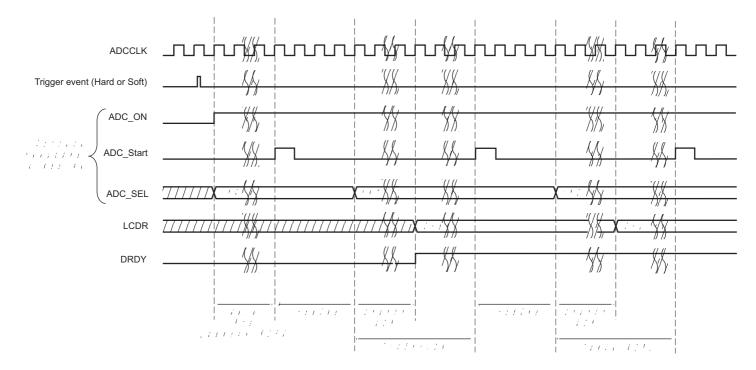

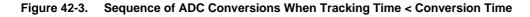

#### Figure 42-2. Sequence of ADC Conversions When Tracking Time > Conversion Time

Atmel

#### 42.6.2 ADC Clock

The ADC uses the ADC clock (ADCCLK) to perform conversions. The ADC clock frequency is selected in the PRESCAL field of ADC\_MR.

The ADC clock frequency is between  $f_{peripheral clock}/2$ , if PRESCAL is 0, and  $f_{peripheral clock}/512$ , if PRESCAL is set to 255 (0xFF).

PRESCAL must be programmed to provide the ADC clock frequency parameter given in the section 'Electrical Characteristics'.

#### 42.6.3 ADC Reference Voltage

The conversion is performed on a full range between 0V and the reference voltage pin ADVREF. Analog inputs between these voltages convert to values based on a linear conversion.

#### 42.6.4 Conversion Resolution

The ADC analog cell features12-bit resolution.

#### 42.6.5 Conversion Results

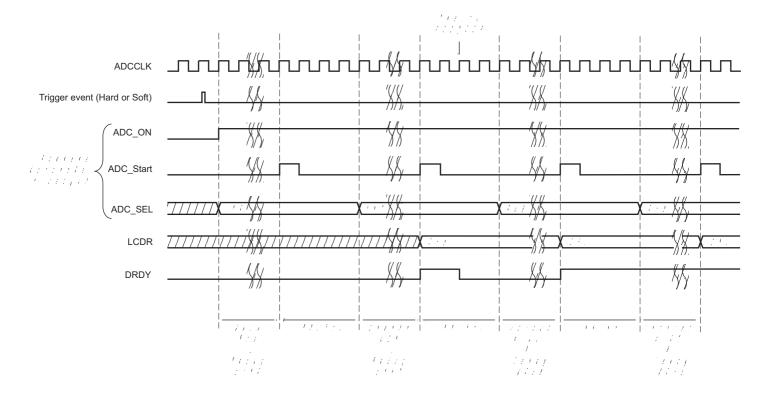

When a conversion is completed, the resulting digital value is stored in the Channel Data register (ADC\_CDRx) of the current channel and in the ADC Last Converted Data register (ADC\_LCDR). By setting the TAG option in the Extended Mode Register (ADC\_EMR), the ADC\_LCDR presents the channel number associated with the last converted data in the CHNB field.

The channel EOC bit and the DRDY bit in the Interrupt Status register (ADC\_ISR) are set. In the case of a connected PDC channel, DRDY rising triggers a data request. In any case, either EOC and DRDY can trigger an interrupt.

Reading one of the ADC\_CDRx clears the corresponding EOC bit. Reading ADC\_LCDR clears the DRDY bit.

#### Figure 42-4. EOCx and DRDY Flag Behavior

If ADC\_CDR is not read before further incoming data is converted, the corresponding OVREx flag is set in the Overrun Status register (ADC\_OVER).

New data converted when DRDY is high sets the GOVRE bit in ADC\_ISR.

# Atmel

| Symbol                | Parameter                          | Conditions                                                                               | Min | Тур | Max | Unit |

|-----------------------|------------------------------------|------------------------------------------------------------------------------------------|-----|-----|-----|------|

| R <sub>PULLDOWN</sub> | Pull-down Resistor                 | PA0-PA31, PB0-PB14, PC0-PC31, NRST                                                       | 70  | 100 | 130 | kΩ   |

|                       | On-die Series                      | PA4-PA31, PB0-PB9, PB12-PB14, PC0-PC31                                                   | _   | 36  | _   |      |

| R <sub>ODT</sub>      | Termination Resistor               | PA0-PA3                                                                                  | _   | 18  | _   | Ω    |

|                       |                                    | Random 144-bit Read @ 25°C:<br>Maximum read frequency at VDDCORE = 1.2V,<br>VDDIO = 3.3V | _   | 16  | 25  |      |

| I <sub>cc</sub>       | Flash Active Current on<br>VDDCORE | Random 72-bit Read @ 25°C:<br>Maximum read frequency at VDDCORE = 1.2V,<br>VDDIO = 3.3V  | _   | 10  | 18  | mA   |

|                       |                                    | Program <sup>(3)</sup> onto VDDCORE = 1.2V,<br>VDDIO = $3.3V @ 25^{\circ}C$              | _   | 3   | 5   |      |

|                       |                                    | Random 144-bit read:<br>Maximum read frequency at VDDCORE = 1.2V,<br>VDDIO = 3.3V @ 25°C | _   | 3   | 16  |      |

| I <sub>CC33</sub>     | Flash Active Current on VDDIO      | Random 72-bit read:Maximum read frequency at VDDCORE = 1.2V,VDDIO = 3.3V @ 25°C          |     | 3   | 5   | mA   |

|                       |                                    | Program <sup>(3)</sup> onto VDDCORE = 1.2V,<br>VDDIO = 3.3V @ 25°C                       | _   | 10  | 15  |      |

Table 44-3. DC Characteristics (Continued)

Note: 1. PA[4–11], PA[15–25], PB[0–9], PB[12–14], PC[0–31]

2. Refer to Section 5.2.2 "VDDIO Versus VDDIN"

3. The Flash programming characteristics are applicable at operating temperature range:  $T_A = -40$  to 85 °C.

- 2. Pin Group 2 = PA[4–11], PA[15–25], PA[30–31], PB[0–9], PB[12–14], PC[0–31]

- 3. Pin Group 3 = PA[12–13], PA[26–28], PA[30–31]

- 4. Pin Group 4 = PA[0–3]

- 5. Pin Group 5 = PB[10–11]

#### Table 44-66. SSC Timings

| Symbol                 | Parameter                                      | Conditions           |                                 | Min                                                    | Max                                            | Unit     |  |

|------------------------|------------------------------------------------|----------------------|---------------------------------|--------------------------------------------------------|------------------------------------------------|----------|--|

|                        | •                                              |                      | Transmitter                     |                                                        |                                                |          |  |

|                        | TK Edge to TF/TD                               | 1.8V dom             | ain                             | -3                                                     | 5.4                                            |          |  |

| SSC <sub>0</sub>       | (TK Output, TF Output)                         | 3.3V dom             | ain                             | -2.6                                                   | 5.0                                            | ns       |  |

|                        | TK Edge to TF/TD                               | 1.8V dom             | ain                             | 4.5                                                    | 19.6                                           |          |  |

| SSC <sub>1</sub>       | (TK Input, TF Output)                          | 3.3V dom             | ain                             | 3.8                                                    | 13.3                                           | ns       |  |

|                        | TF Setup Time before TK Edge                   | 1.8V dom             | ain                             | 18.9                                                   |                                                |          |  |

| SSC <sub>2</sub>       | (TK Output)                                    | 3.3V dom             | ain                             | 12.0                                                   | _                                              | ns       |  |

| SSC <sub>3</sub> TF Ho | TF Hold Time after TK Edge                     | 1.8V dom             | ain                             | 0                                                      | _                                              | ns       |  |

| 0003                   | (TK Output)                                    | 3.3V dom             | ain                             | 0                                                      | _                                              | 113      |  |

|                        |                                                | 4.0) (               | _                               | 2.6                                                    | 5.4                                            |          |  |

|                        | TK Edge to TF/TD                               | 1.8V<br>domain       | STTDLY = 0<br>START = 4, 5 or 7 | 2.6 + (2 × t <sub>CPMCK)</sub> <sup>(1)</sup>          | 5.4 + (2 × t <sub>CPMCK)</sub> <sup>(1)</sup>  |          |  |

| $SSC_4$                | (TK Output, TF Input)                          |                      | _                               | 2.3                                                    | 5.0                                            | ns       |  |

|                        |                                                | 3.3V<br>domain       | STTDLY = 0<br>START = 4, 5 or 7 | 2.3 + (2 × t <sub>CPMCK)</sub> <sup>(1)</sup>          | 5.0 + (2 × t <sub>CPMCK)</sub> <sup>(1)</sup>  | +        |  |

| $SSC_5$                | TF Setup Time before TK Edge<br>(TK Input)     | 1.8V dom<br>3.3V dom |                                 | 0                                                      | -                                              | ns       |  |

| $SSC_6$                | TF Hold Time after TK edge<br>(TK Input)       | 1.8V dom<br>3.3V dom |                                 | t <sub>CPMCK</sub>                                     | -                                              | ns       |  |

|                        |                                                |                      | _                               | 4.5                                                    | 16.3                                           |          |  |

|                        | TK Edge to TF/TD                               | 1.8V<br>domain       | STTDLY = 0<br>START = 4, 5 or 7 | 4.5 + (3 × t <sub>СРМСК)</sub> <sup>(1)</sup>          | 16.3 + (3 × t <sub>CPMCK)</sub> <sup>(1)</sup> |          |  |

| SSC <sub>7</sub>       | (TK Input, TF Input)                           |                      | -                               | 3.8                                                    | 13.3                                           | ns       |  |

|                        |                                                | 3.3V<br>domain       | STTDLY = 0<br>START = 4, 5 or 7 | 3.8 + (3 × t <sub>СРМСК)</sub> <sup>(1)</sup>          | 13.3 + $(3 \times t_{CPMCK)}^{(1)}$            |          |  |

|                        |                                                |                      | Receiver                        |                                                        |                                                |          |  |

| SSC <sub>8</sub>       | RF/RD Setup Time before RK<br>Edge (RK Input)  | 1.8V dom<br>3.3V dom |                                 | 0                                                      | -                                              | ns       |  |

| SSC <sub>9</sub>       | RF/RD Hold Time after RK<br>Edge (RK Input)    | 1.8V dom<br>3.3V dom |                                 | t <sub>CPMCK</sub>                                     | -                                              | ns       |  |

| SSC <sub>10</sub>      | RK Edge to RF (RK Input)                       | 1.8V dom<br>3.3V dom |                                 | 4.7<br>4                                               | 16.1<br>12.8                                   | ns       |  |

| SSC <sub>11</sub>      | RF/RD Setup Time before RK<br>Edge (RK Output) | 1.8V dom<br>3.3V dom |                                 | 15.8 - t <sub>СРМСК</sub><br>12.5 - t <sub>СРМСК</sub> | _                                              | ns       |  |

| SSC <sub>12</sub>      | RF/RD Hold Time after RK<br>Edge (RK Output)   | 1.8V dom<br>3.3V dom | ain                             | t <sub>СРМСК</sub> - 4.3<br>t <sub>СРМСК</sub> - 3.6   | -                                              | ns       |  |

| SSC <sub>13</sub>      | RK Edge to RF (RK Output)                      | 1.8V dom<br>3.3V dom | ain                             | -3<br>-2.6                                             | 4.3<br>3.8                                     | ns       |  |

|                        |                                                | 5.5 v u011           |                                 | -2.0                                                   | 5.0                                            | <u> </u> |  |