Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 120MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, IrDA, Memory Card, SPI, SSC, UART/USART, USB          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                              |

| Number of I/O              | 34                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 64K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                            |

| Data Converters            | A/D 8x12b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 48-LQFP                                                                 |

| Supplier Device Package    | 48-LQFP (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4s2ab-an |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 8.1.3.4 Error Code Correction (ECC)

The Flash embeds an ECC module with 8 parity bits for each 64 data bits. The ECC is able to correct one unique error. The errors are detected while a read access is performed into memory array. The ECC (Hamming Algorithm) is a mechanism that encodes data in a manner that makes possible the identification and correction of certain errors in data. The ECC is capable of single bit error correction.

#### 8.1.3.5 Lock Regions

Several lock bits are used to protect write and erase operations on lock regions. A lock region is composed of several consecutive pages, and each lock region has its associated lock bit.

| Product      | Number of Lock Bits | Lock Region Size |

|--------------|---------------------|------------------|

| SAM4SD32     | 256 (128 + 128)     | 8 Kbytes         |

| SAM4SD16     | 128 (64 + 64)       | 8 Kbytes         |

| SAM4S16/SA16 | 128                 | 8 Kbytes         |

| SAM4S8       | 64                  | 8 Kbytes         |

| SAM4S4       | 32                  | 8 Kbytes         |

| SAM4S2       | 16                  | 8 Kbytes         |

#### Table 8-2. Lock Bit Number

If a locked region erase or program command occurs, the command is aborted and the EEFC triggers an interrupt.

The lock bits are software programmable through the EEFC User Interface. The command "Set Lock Bit" enables the protection. The command "Clear Lock Bit" unlocks the lock region.

Asserting the ERASE pin clears the lock bits, thus unlocking the entire Flash.

#### 8.1.3.6 Security Bit

The SAM4SD32/SD16/S16/SA16/S8/S4/S2 feature one security bit based on a specific General Purpose NVM bit (GPNVM bit 0). When the security bit is enabled, any access to the Flash, SRAM, core registers and internal peripherals through the ICE interface or through the Fast Flash Programming Interface, is forbidden. This ensures the confidentiality of the code programmed in the Flash.

This security bit can only be enabled through the command "Set General Purpose NVM Bit 0" of the EEFC User Interface. Disabling the security bit can only be achieved by asserting the ERASE pin at 1, and after a full Flash erase is performed. When the security bit is deactivated, all accesses to the Flash, SRAM, Core registers, Internal Peripherals are permitted.

The ERASE pin integrates a permanent pull-down. Consequently, it can be left unconnected during normal operation. However, it is recommended, in harsh environment, to connect it directly to GND if the erase operation is not used in the application.

To avoid unexpected erase at power-up, a minimum ERASE pin assertion time is required. This time is defined in Table 44-74 "AC Flash Characteristics".

The erase operation is not performed when the system is in Wait mode with the Flash in deep-power-down mode.

To make sure that the erase operation is performed after power-up, the system must not reconfigure the ERASE pin as GPIO or enter Wait mode with Flash in Deep-power-down mode before the ERASE pin assertion time has elapsed.

The following sequence ensures the erase operation in all cases:

- 1. Assert the ERASE pin (High)

- 2. Assert the NRST pin (Low)

- 3. Power cycle the device

#### 12.6.4.4 LDR and STR, Unprivileged

Load and Store with unprivileged access.

| Syntax      |                                                                 |

|-------------|-----------------------------------------------------------------|

| op{         | <pre>type}T{cond} Rt, [Rn {, #offset}] ; immediate offset</pre> |

| where:      |                                                                 |

| ор          | is one of:                                                      |

| LDR         | Load Register.                                                  |

| STR         | Store Register.                                                 |

| type is one | of:                                                             |

| В           | unsigned byte, zero extend to 32 bits on loads.                 |

| SB          | signed byte, sign extend to 32 bits (LDR only).                 |

| Н           | unsigned halfword, zero extend to 32 bits on loads.             |

| SH          | signed halfword, sign extend to 32 bits (LDR only).             |

| -           | omit, for word.                                                 |

| cond        | is an optional condition code, see "Conditional Execution".     |

| Rt          | is the register to load or store.                               |

| Rn          | is the register on which the memory address is based.           |

| offset      | is an offset from <i>Rn</i> and can be 0 to 255.                |

|             | If offset is omitted, the address is the value in Rn.           |

| Operation   |                                                                 |

#### Operation

These load and store instructions perform the same function as the memory access instructions with immediate offset, see "LDR and STR, Immediate Offset". The difference is that these instructions have only unprivileged access even when used in privileged software.

When used in unprivileged software, these instructions behave in exactly the same way as normal memory access instructions with immediate offset.

Restrictions

In these instructions:

- *Rn* must not be PC

- *Rt* must not be SP and must not be PC.

#### **Condition Flags**

These instructions do not change the flags.

#### Examples

| STRBTEQ | R4, | [R7]     | ; Conditionally store least significant byte in     |

|---------|-----|----------|-----------------------------------------------------|

|         |     |          | ; R4 to an address in R7, with unprivileged access  |

| LDRHT   | R2, | [R2, #8] | ; Load halfword value from an address equal to      |

|         |     |          | ; sum of R2 and 8 into R2, with unprivileged access |

Atmel

| 12.8.3.6 | Interrupt Priority Registers |    |    |     |    |    |    |  |  |

|----------|------------------------------|----|----|-----|----|----|----|--|--|

| Name:    | NVIC_IPRx [x=0.              | 8] |    |     |    |    |    |  |  |

| Access:  | Read/Write                   |    |    |     |    |    |    |  |  |

| Reset:   | 0x000000000                  |    |    |     |    |    |    |  |  |

| 31       | 30                           | 29 | 28 | 27  | 26 | 25 | 24 |  |  |

|          |                              |    | PF | RI3 |    |    |    |  |  |

| 23       | 22                           | 21 | 20 | 19  | 18 | 17 | 16 |  |  |

|          |                              |    | PF | RI2 |    |    |    |  |  |

| 15       | 14                           | 13 | 12 | 11  | 10 | 9  | 8  |  |  |

|          |                              |    | PF | RI1 |    |    |    |  |  |

| 7        | 6                            | 5  | 4  | 3   | 2  | 1  | 0  |  |  |

|          |                              |    | PF | RIO |    |    |    |  |  |

The NVIC\_IPR0–NVIC\_IPR registers provide a 8-bit priority field for each interrupt. These registers are byte-accessible. Each register holds four priority fields that map up to four elements in the CMSIS interrupt priority array IP[0] to IP[ ].

#### • PRI3: Priority (4m+3)

Priority, Byte Offset 3, refers to register bits [31:24].

#### • PRI2: Priority (4m+2)

Priority, Byte Offset 2, refers to register bits [23:16].

#### • PRI1: Priority (4m+1)

Priority, Byte Offset 1, refers to register bits [15:8].

#### • PRI0: Priority (4m)

Priority, Byte Offset 0, refers to register bits [7:0].

- Notes: 1. Each priority field holds a priority value, 0–15. The lower the value, the greater the priority of the corresponding interrupt. The processor implements only bits[7:4] of each field; bits[3:0] read as zero and ignore writes.

- 2. For more information about the IP[0] to IP[34] interrupt priority array, that provides the software view of the interrupt priorities, see Table 12-29, "CMSIS Functions for NVIC Control".

- 3. The corresponding IPR number *n* is given by n = m DIV 4.

- 4. The byte offset of the required Priority field in this register is *m* MOD 4.

| 12.9.1.4 | Vector Table Offset Register |    |     |     |    |    |    |  |

|----------|------------------------------|----|-----|-----|----|----|----|--|

| Name:    | SCB_VTOR                     |    |     |     |    |    |    |  |

| Access:  | Read/Write                   |    |     |     |    |    |    |  |

| 31       | 30                           | 29 | 28  | 27  | 26 | 25 | 24 |  |

|          |                              |    | TBL | OFF |    |    |    |  |

| 23       | 22                           | 21 | 20  | 19  | 18 | 17 | 16 |  |

|          |                              |    | TBL | OFF |    |    |    |  |

| 15       | 14                           | 13 | 12  | 11  | 10 | 9  | 8  |  |

|          |                              |    | TBL | OFF |    |    |    |  |

| 7        | 6                            | 5  | 4   | 3   | 2  | 1  | 0  |  |

| TBLOFI   | = _                          | -  | -   | -   | -  | _  | -  |  |

The SCB\_VTOR indicates the offset of the vector table base address from memory address 0x00000000.

# • TBLOFF: Vector Table Base Offset

It contains bits [29:7] of the offset of the table base from the bottom of the memory map.

Bit [29] determines whether the vector table is in the code or SRAM memory region:

0: Code.

1: SRAM.

It is sometimes called the TBLBASE bit.

Note: When setting TBLOFF, the offset must be aligned to the number of exception entries in the vector table. Configure the next statement to give the information required for your implementation; the statement reminds the user of how to determine the alignment requirement. The minimum alignment is 32 words, enough for up to 16 interrupts. For more interrupts, adjust the alignment by rounding up to the next power of two. For example, if 21 interrupts are required, the alignment must be on a 64-word boundary because the required table size is 37 words, and the next power of two is 64.

Table alignment requirements mean that bits[6:0] of the table offset are always zero.

#### 13.5.6.3 5.4.3. How to Configure the TPIU

This example only concerns the asynchronous trace mode.

- Set the TRCENA bit to 1 into the Debug Exception and Monitor Register (0xE000EDFC) to enable the use of trace and debug blocks.

- Write 0x2 into the Selected Pin Protocol Register

- Select the Serial Wire Output NRZ

- Write 0x100 into the Formatter and Flush Control Register

- Set the suitable clock prescaler value into the Async Clock Prescaler Register to scale the baud rate of the asynchronous output (this can be done automatically by the debugging tool).

# 13.5.7 IEEE<sup>®</sup> 1149.1 JTAG Boundary Scan

IEEE 1149.1 JTAG Boundary Scan allows pin-level access independent of the device packaging technology.

IEEE 1149.1 JTAG Boundary Scan is enabled when TST is tied to low, while JTAGSEL is high during power-up, and must be kept in this state during the whole boundary scan operation. The SAMPLE, EXTEST and BYPASS functions are implemented. In SWD/JTAG debug mode, the ARM processor responds with a non-JTAG chip ID that identifies the processor. This is not IEEE 1149.1 JTAG-compliant.

It is not possible to switch directly between JTAG Boundary Scan and SWJ Debug Port operations. A chip reset must be performed after JTAGSEL is changed.

A Boundary-scan Descriptor Language (BSDL) file is provided on Atmel's web site to set up the test.

#### 13.5.7.1 JTAG Boundary-scan Register

The Boundary-scan Register (BSR) contains a number of bits which correspond to active pins and associated control signals.

Each SAM4 input/output pin corresponds to a 3-bit register in the BSR. The OUTPUT bit contains data that can be forced on the pad. The INPUT bit facilitates the observability of data applied to the pad. The CONTROL bit selects the direction of the pad.

For more information, please refer to BDSL files available for the SAM4 Series.

# 15.5 Real-time Timer (RTT) User Interface

#### Table 15-1. Register Mapping

| Offset | Register        | Name   | Access     | Reset       |

|--------|-----------------|--------|------------|-------------|

| 0x00   | Mode Register   | RTT_MR | Read/Write | 0x0000_8000 |

| 0x04   | Alarm Register  | RTT_AR | Read/Write | 0xFFFF_FFFF |

| 0x08   | Value Register  | RTT_VR | Read-only  | 0x0000_0000 |

| 0x0C   | Status Register | RTT_SR | Read-only  | 0x0000_0000 |

### 16.6.6 RTC Calendar Alarm Register

| Name:    | RTC_CALALR |    |    |    |       |    |    |

|----------|------------|----|----|----|-------|----|----|

| Address: | 0x400E1474 |    |    |    |       |    |    |

| Access:  | Read/Write |    |    |    |       |    |    |

| 31       | 30         | 29 | 28 | 27 | 26    | 25 | 24 |

| DATEEN   | -          |    |    | DA | ATE   |    |    |

| 23       | 22         | 21 | 20 | 19 | 18    | 17 | 16 |

| MTHEN    | -          | -  |    |    | MONTH |    |    |

| 15       | 14         | 13 | 12 | 11 | 10    | 9  | 8  |

| _        | -          | _  | -  | _  | -     | -  | -  |

| 7        | 6          | 5  | 4  | 3  | 2     | 1  | 0  |

| _        | _          | _  | _  | _  | _     | _  | -  |

This register can only be written if the WPEN bit is cleared in the System Controller Write Protection Mode Register (SYSC\_WPMR).

Note: To change one of the DATE, MONTH fields, it is recommended to disable the field before changing the value and then re-enable it after the change has been made. This requires up to three accesses to the RTC\_CALALR. The first access clears the enable corresponding to the field to change (DATEEN, MTHEN). If the field is already cleared, this access is not required. The second access performs the change of the value (DATE, MONTH). The third access is required to re-enable the field by writing 1 in DATEEN, MTHEN fields.

#### • MONTH: Month Alarm

This field is the alarm field corresponding to the BCD-coded month counter.

#### • MTHEN: Month Alarm Enable

- 0: The month-matching alarm is disabled.

- 1: The month-matching alarm is enabled.

#### • DATE: Date Alarm

This field is the alarm field corresponding to the BCD-coded date counter.

#### • DATEEN: Date Alarm Enable

- 0: The date-matching alarm is disabled.

- 1: The date-matching alarm is enabled.

# 16.6.8 RTC Status Clear Command Register

| Name:    | RTC_SCCR   |          |        |        |        |        |        |

|----------|------------|----------|--------|--------|--------|--------|--------|

| Address: | 0x400E147C |          |        |        |        |        |        |

| Access:  | Write-only |          |        |        |        |        |        |

| 31       | 30         | 29       | 28     | 27     | 26     | 25     | 24     |

| _        | -          | -        | _      | _      | _      | _      | -      |

| 23       | 22         | 21       | 20     | 19     | 18     | 17     | 16     |

| _        | -          | -        | -      | -      | _      | -      | -      |

| 15       | 14         | 13       | 12     | 11     | 10     | 9      | 8      |

| _        | -          | -        | -      | -      | -      | -      | -      |

| 7        | 6          | 5        | 4      | 3      | 2      | 1      | 0      |

| _        | -          | TDERRCLR | CALCLR | TIMCLR | SECCLR | ALRCLR | ACKCLR |

#### • ACKCLR: Acknowledge Clear

0: No effect.

1: Clears corresponding status flag in the Status Register (RTC\_SR).

#### • ALRCLR: Alarm Clear

0: No effect.

1: Clears corresponding status flag in the Status Register (RTC\_SR).

#### • SECCLR: Second Clear

0: No effect.

1: Clears corresponding status flag in the Status Register (RTC\_SR).

#### • TIMCLR: Time Clear

0: No effect.

1: Clears corresponding status flag in the Status Register (RTC\_SR).

#### • CALCLR: Calendar Clear

0: No effect.

1: Clears corresponding status flag in the Status Register (RTC\_SR).

#### • TDERRCLR: Time and/or Date Free Running Error Clear

0: No effect.

1: Clears corresponding status flag in the Status Register (RTC\_SR).

# 23.7.9 CRCCU Control Register

| Name:    | CRCCU_CR   |    |    |    |    |    |       |

|----------|------------|----|----|----|----|----|-------|

| Address: | 0x40044034 |    |    |    |    |    |       |

| Access:  | Write-only |    |    |    |    |    |       |

| 31       | 30         | 29 | 28 | 27 | 26 | 25 | 24    |

| _        | -          | _  | -  | _  | _  | _  | -     |

| 23       | 22         | 21 | 20 | 19 | 18 | 17 | 16    |

| _        | -          | _  | -  | _  | _  | _  | -     |

| 15       | 14         | 13 | 12 | 11 | 10 | 9  | 8     |

| -        | -          | -  | -  | -  | -  | _  | -     |

| 7        | 6          | 5  | 4  | 3  | 2  | 1  | 0     |

| _        | -          | _  | _  | _  | -  | _  | RESET |

# • RESET: CRC Computation Reset

0: No effect

1: Sets the CRCCU\_SR to 0xFFFFFFF

# 25.8.7 Write Protection Status Register

| Name:<br>Address:<br>Access: | MATRIX_WPSR<br>0x400E03E8<br>Read-only | R. |     |      |    |    |      |

|------------------------------|----------------------------------------|----|-----|------|----|----|------|

| Reset:                       | See Table 25-4                         |    |     |      |    |    |      |

| 31                           | 30                                     | 29 | 28  | 27   | 26 | 25 | 24   |

| -                            | -                                      | -  | -   | -    | -  | -  | -    |

| 23                           | 22                                     | 21 | 20  | 19   | 18 | 17 | 16   |

|                              |                                        |    | WPV | /SRC |    |    |      |

| 15                           | 14                                     | 13 | 12  | 11   | 10 | 9  | 8    |

|                              |                                        |    | WPV | /SRC |    |    |      |

| 7                            | 6                                      | 5  | 4   | 3    | 2  | 1  | 0    |

| -                            | -                                      | -  | -   | -    | -  | -  | WPVS |

# • WPVS: Write Protection Violation Status

0: No write protection violation has occurred since the last read of the MATRIX\_WPSR.

1: A write protection violation has occurred since the last read of the MATRIX\_WPSR. If this violation is an unauthorized attempt to write a protected register, the associated violation is reported into field WPVSRC.

#### • WPVSRC: Write Protection Violation Source

When WPVS = 1, WPVSRC indicates the register address offset at which a write access has been attempted.

Atmel

- "SMC Cycle Register"

- "SMC MODE Register"

#### 26.9.6 Coding Timing Parameters

All timing parameters are defined for one chip select and are grouped together in one SMC REGISTER according to their type.

The SMC SETUP register groups the definition of all setup parameters:

NRD SETUP, NCS RD SETUP, NWE SETUP, NCS WR SETUP

The SMC\_PULSE register groups the definition of all pulse parameters:

• NRD PULSE, NCS RD PULSE, NWE PULSE, NCS WR PULSE

The SMC\_CYCLE register groups the definition of all cycle parameters:

NRD\_CYCLE, NWE\_CYCLE

Table 26-4 shows how the timing parameters are coded and their permitted range.

#### Table 26-4. **Coding and Range of Timing Parameters**

|             |                |                               | Permitted Range |                 |

|-------------|----------------|-------------------------------|-----------------|-----------------|

| Coded Value | Number of Bits | Effective Value               | Coded Value     | Effective Value |

| setup [5:0] | 6              | 128 x setup[5] + setup[4:0]   | 0 ≤ ≤ 31        | 0 ≤ ≤ 128+31    |

| pulse [6:0] | 7              | 256 x pulse[6] + pulse[5:0]   | 0 ≤ ≤ 63        | 0 ≤ ≤ 256+63    |

|             |                |                               |                 | 0 ≤ ≤ 256+127   |

| cycle [8:0] | 9              | 256 x cycle[8:7] + cycle[6:0] | 0 ≤ ≤ 127       | 0 ≤ ≤ 512+127   |

|             |                |                               |                 | 0 ≤ ≤ 768+127   |

#### 26.9.7 Reset Values of Timing Parameters

Table 26-5 gives the default value of timing parameters at reset.

| Table 26-5.         Reset Values of Timing Parameters |             |                                                                                       |  |  |  |  |  |

|-------------------------------------------------------|-------------|---------------------------------------------------------------------------------------|--|--|--|--|--|

| Register                                              | Reset Value | Definition                                                                            |  |  |  |  |  |

| SMC_SETUP                                             | 0x01010101  | All setup timings are set to 1.                                                       |  |  |  |  |  |

| SMC_PULSE                                             | 0x01010101  | All pulse timings are set to 1.                                                       |  |  |  |  |  |

| SMC_CYCLE                                             | 0x00030003  | The read and write operations last 3 Master Clo<br>cycles and provide one hold cycle. |  |  |  |  |  |

| WRITE_MODE                                            | 1           | Write is controlled with NWE.                                                         |  |  |  |  |  |

1

# 26.9.8 Usage Restriction

READ\_MODE

The SMC does not check the validity of the user-programmed parameters. If the sum of SETUP and PULSE parameters is larger than the corresponding CYCLE parameter, this leads to unpredictable behavior of the SMC. For read operations:

Read is controlled with NRD.

ock

Null but positive setup and hold of address and NRD and/or NCS can not be guaranteed at the memory interface because of the propagation delay of theses signals through external logic and pads. If positive setup and hold values must be verified, then it is strictly recommended to program non-null values so as to cover possible skews between address, NCS and NRD signals.

Atmel

# 29.15 Clock Switching Details

#### 29.15.1 Master Clock Switching Timings

Table 29-1 and Table 29-2 give the worst case timings required for the master clock to switch from one selected clock to another one. This is in the event that the prescaler is de-activated. When the prescaler is activated, an additional time of 64 clock cycles of the newly selected clock has to be added.

| From       | Main Clock                                                                | SLCK                                               | PLL Clock                                          |  |

|------------|---------------------------------------------------------------------------|----------------------------------------------------|----------------------------------------------------|--|

| То         |                                                                           |                                                    |                                                    |  |

| Main Clock | _                                                                         | 4 x SLCK +<br>2.5 x Main Clock                     | 3 x PLL Clock +<br>4 x SLCK +<br>1 x Main Clock    |  |

| SLCK       | 0.5 x Main Clock +<br>4.5 x SLCK                                          | -                                                  | 3 x PLL Clock +<br>5 x SLCK                        |  |

| PLL Clock  | 0.5 x Main Clock +<br>4 x SLCK +<br>PLLCOUNT x SLCK +<br>2.5 x PLLx Clock | 2.5 x PLL Clock +<br>5 x SLCK +<br>PLLCOUNT x SLCK | 2.5 x PLL Clock +<br>4 x SLCK +<br>PLLCOUNT x SLCK |  |

Table 29-1.

Clock Switching Timings (Worst Case)

Notes: 1. PLL designates either the PLLA or the PLLB Clock.

2. PLLCOUNT designates either PLLACOUNT or PLLBCOUNT.

| From       |  | PLLA Clock                                           | PLLB Clock                                           |

|------------|--|------------------------------------------------------|------------------------------------------------------|

| То         |  |                                                      |                                                      |

| PLLA Clock |  | 2.5 x PLLA Clock +<br>4 x SLCK +<br>PLLACOUNT x SLCK | 3 x PLLA Clock +<br>4 x SLCK +<br>1.5 x PLLA Clock   |

| PLLB Clock |  | 3 x PLLB Clock +<br>4 x SLCK +<br>1.5 x PLLB Clock   | 2.5 x PLLB Clock +<br>4 x SLCK +<br>PLLBCOUNT x SLCK |

#### Table 29-2. Clock Switching Timings between Two PLLs (Worst Case)

#### 31.5.15 Register Write Protection

To prevent any single software error from corrupting PIO behavior, certain registers in the address space can be write-protected by setting the WPEN bit in the PIO Write Protection Mode Register (PIO\_WPMR).

If a write access to a write-protected register is detected, the WPVS flag in the PIO Write Protection Status Register (PIO\_WPSR) is set and the field WPVSRC indicates the register in which the write access has been attempted.

The WPVS bit is automatically cleared after reading the PIO\_WPSR.

The following registers can be write-protected:

- PIO Enable Register

- PIO Disable Register

- PIO Output Enable Register

- PIO Output Disable Register

- PIO Input Filter Enable Register

- PIO Input Filter Disable Register

- PIO Multi-driver Enable Register

- PIO Multi-driver Disable Register

- PIO Pull-Up Disable Register

- PIO Pull-Up Enable Register

- PIO Peripheral ABCD Select Register 1

- PIO Peripheral ABCD Select Register 2

- PIO Output Write Enable Register

- PIO Output Write Disable Register

- PIO Pad Pull-Down Disable Register

- PIO Pad Pull-Down Enable Register

- PIO Parallel Capture Mode Register

# 31.6.22 PIO Pull-Up Enable Register

| Name:    | PIO_PUER                                                |     |     |     |     |     |     |  |  |  |

|----------|---------------------------------------------------------|-----|-----|-----|-----|-----|-----|--|--|--|

| Address: | 0x400E0E64 (PIOA), 0x400E1064 (PIOB), 0x400E1264 (PIOC) |     |     |     |     |     |     |  |  |  |

| Access:  | Write-only                                              |     |     |     |     |     |     |  |  |  |

| 31       | 30                                                      | 29  | 28  | 27  | 26  | 25  | 24  |  |  |  |

| P31      | P30                                                     | P29 | P28 | P27 | P26 | P25 | P24 |  |  |  |

| 23       | 22                                                      | 21  | 20  | 19  | 18  | 17  | 16  |  |  |  |

| P23      | P22                                                     | P21 | P20 | P19 | P18 | P17 | P16 |  |  |  |

| 15       | 14                                                      | 13  | 12  | 11  | 10  | 9   | 8   |  |  |  |

| P15      | P14                                                     | P13 | P12 | P11 | P10 | P9  | P8  |  |  |  |

| 7        | 6                                                       | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

| P7       | P6                                                      | P5  | P4  | P3  | P2  | P1  | P0  |  |  |  |

This register can only be written if the WPEN bit is cleared in the PIO Write Protection Mode Register.

## • P0-P31: Pull-Up Enable

0: No effect.

1: Enables the pull-up resistor on the I/O line.

# 33.2 Embedded Characteristics

- Master or Slave Serial Peripheral Bus Interface

- 8-bit to 16-bit programmable data length per chip select

- Programmable phase and polarity per chip select

- Programmable transfer delay between consecutive transfers and delay before SPI clock per chip select

- Programmable delay between chip selects

- Selectable mode fault detection

- Master Mode can drive SPCK up to Peripheral Clock

- Master Mode Bit Rate can be Independent of the Processor/Peripheral Clock

- Slave mode operates on SPCK, asynchronously with core and bus clock

- Four chip selects with external decoder support allow communication with up to 15 peripherals

- Communication with Serial External Devices Supported

- Serial memories, such as DataFlash and 3-wire EEPROMs

- Serial peripherals, such as ADCs, DACs, LCD controllers, CAN controllers and sensors

- External coprocessors

- Connection to PDC Channel Capabilities, Optimizing Data Transfers

- One channel for the receiver

- One channel for the transmitter

- Register Write Protection

#### • CTSIC: Clear to Send Input Change Flag (cleared on read)

0: No input change has been detected on the CTS pin since the last read of US\_CSR.

1: At least one input change has been detected on the CTS pin since the last read of US\_CSR.

#### • RI: Image of RI Input

0: RI input is driven low.

1: RI input is driven high.

# • DSR: Image of DSR Input

0: DSR input is driven low.

1: DSR input is driven high.

## • DCD: Image of DCD Input

0: DCD input is driven low.

1: DCD input is driven high.

## • CTS: Image of CTS Input

0: CTS input is driven low.

1: CTS input is driven high.

# • MANERR: Manchester Error (cleared by writing a one to the bit US\_CR.RSTSTA)

0: No Manchester error has been detected since the last RSTSTA.

1: At least one Manchester error has been detected since the last RSTSTA.

#### 38.14.12HSMCI Status Register

| Name:    | HSMCI_SR   |         |          |         |           |       |          |

|----------|------------|---------|----------|---------|-----------|-------|----------|

| Address: | 0x40000040 |         |          |         |           |       |          |

| Access:  | Read-only  |         |          |         |           |       |          |

| 31       | 30         | 29      | 28       | 27      | 26        | 25    | 24       |

| UNRE     | OVRE       | ACKRCVE | ACKRCV   | XFRDONE | FIFOEMPTY | —     | -        |

| 23       | 22         | 21      | 20       | 19      | 18        | 17    | 16       |

| CSTOE    | DTOE       | DCRCE   | RTOE     | RENDE   | RCRCE     | RDIRE | RINDE    |

| 15       | 14         | 13      | 12       | 11      | 10        | 9     | 8        |

| TXBUFE   | RXBUFF     | CSRCV   | SDIOWAIT | _       | _         | —     | SDIOIRQA |

| 7        | 6          | 5       | 4        | 3       | 2         | 1     | 0        |

| ENDTX    | ENDRX      | NOTBUSY | DTIP     | BLKE    | TXRDY     | RXRDY | CMDRDY   |

#### • CMDRDY: Command Ready (cleared by writing in HSMCI\_CMDR)

- 0: A command is in progress.

- 1: The last command has been sent.

#### • RXRDY: Receiver Ready (cleared by reading HSMCI\_RDR)

- 0: Data has not yet been received since the last read of HSMCI\_RDR.

- 1: Data has been received since the last read of HSMCI\_RDR.

#### • TXRDY: Transmit Ready (cleared by writing in HSMCI\_TDR)

- 0: The last data written in HSMCI\_TDR has not yet been transferred in the Shift Register.

- 1: The last data written in HSMCI\_TDR has been transferred in the Shift Register.

#### • BLKE: Data Block Ended (cleared on read)

This flag must be used only for Write Operations.

0: A data block transfer is not yet finished.

1: A data block transfer has ended, including the CRC16 Status transmission. The flag is set for each transmitted CRC Status.

Refer to the MMC or SD Specification for more details concerning the CRC Status.

#### • DTIP: Data Transfer in Progress (cleared at the end of CRC16 calculation)

0: No data transfer in progress.

1: The current data transfer is still in progress, including CRC16 calculation.

#### • NOTBUSY: HSMCI Not Busy

A block write operation uses a simple busy signalling of the write operation duration on the data (DAT0) line: during a data transfer block, if the card does not have a free data receive buffer, the card indicates this condition by pulling down the data line (DAT0) to LOW. The card stops pulling down the data line as soon as at least one receive buffer for the defined data transfer block length becomes free.

Refer to the MMC or SD Specification for more details concerning the busy behavior.

### 39.7.29 PWM Stepper Motor Mode Register

| Name:    | PWM_SMMR   |    |    |    |    |       |       |

|----------|------------|----|----|----|----|-------|-------|

| Address: | 0x400200B0 |    |    |    |    |       |       |

| Access:  | Read/Write |    |    |    |    |       |       |

| 31       | 30         | 29 | 28 | 27 | 26 | 25    | 24    |

| _        | -          | _  | _  | _  | _  | _     | -     |

|          |            |    |    |    |    |       |       |

| 23       | 22         | 21 | 20 | 19 | 18 | 17    | 16    |

| _        | -          | -  | -  | -  | -  | DOWN1 | DOWN0 |

|          |            |    |    |    |    |       |       |

| 15       | 14         | 13 | 12 | 11 | 10 | 9     | 8     |

| _        | -          | _  | -  | -  | _  | -     | _     |

|          |            |    |    |    |    |       |       |

| 7        | 6          | 5  | 4  | 3  | 2  | 1     | 0     |

| -        | _          | _  | -  | —  | -  | GCEN1 | GCEN0 |

# • GCENx: Gray Count ENable

0: Disable gray count generation on PWML[2\*x], PWMH[2\*x], PWML[2\*x+1], PWMH[2\*x+1]

1: Enable gray count generation on PWML[2\*x], PWMH[2\*x], PWML[2\*x +1], PWMH[2\*x +1.

#### DOWNx: DOWN Count

0: Up counter.

1: Down counter.

#### • WAKEUP: USB Bus Wakeup Interrupt

0: USB Bus Wakeup Interrupt is disabled

1: USB Bus Wakeup Interrupt is enabled

Note: When the USB block is in suspend mode, the application may power down the USB logic. In this case, any USB HOST resume request that is made must be taken into account and, thus, the reset value of the RXRSM bit of the register UDP\_IMR is enabled.

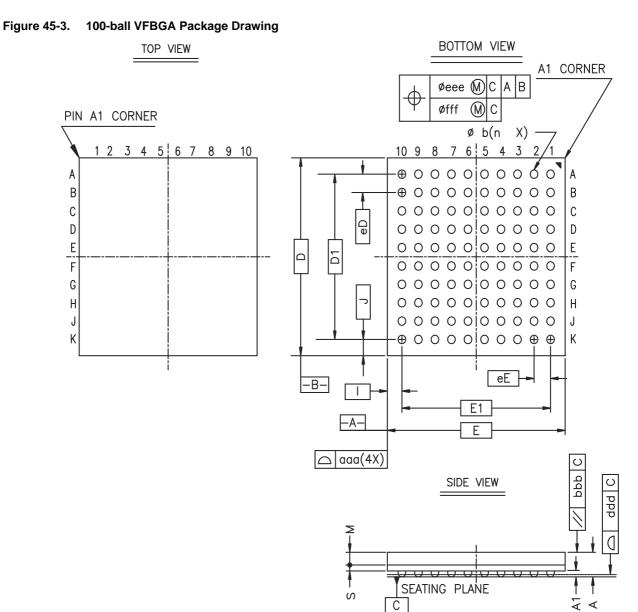

# 45.3 100-ball VFBGA Mechanical Characteristics

| Table 45-8. VFBGA Package Dimens | ions |

|----------------------------------|------|

|----------------------------------|------|

|                      |   | Symbol | Common Dimensions (mm) |

|----------------------|---|--------|------------------------|

| Package:             |   |        | VFBGA                  |

| Darky Cizar          | Х | E      | $7.000 \pm 0.100$      |

| Body Size:           | Y | D      | $7.000 \pm 0.100$      |

|                      | Х | еE     | 0.650                  |

| Ball Pitch:          | Y | eD     | 0.650                  |

| Total Thickness:     |   | А      | 1.000 max              |

| Mold Thickness:      |   | М      | 0.450 ref.             |

| Substrate Thickness: |   | S      | 0.210 ref.             |

# Atmel