Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 120MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, IrDA, Memory Card, SPI, SSC, UART/USART, USB          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                              |

| Number of I/O              | 34                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 64K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                            |

| Data Converters            | A/D 8x12b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 48-LQFP                                                                 |

| Supplier Device Package    | 48-LQFP (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4s4ab-an |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 12.6.4.2 LDR and STR, Immediate Offset

Load and Store with immediate offset, pre-indexed immediate offset, or post-indexed immediate offset.

| Current                                                                                                                                             |                                                                                                                                             |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| <pre>op{type}{cond} Rt, [Rn, #offset]! op{type}{cond} Rt, [Rn], #offset opD{cond} Rt, Rt2, [Rn {, #offset}] opD{cond} Rt, Rt2, [Rn, #offset]!</pre> | <pre>; immediate offset ; pre-indexed ; post-indexed ; immediate offset, two words ; pre-indexed, two words ; post-indexed, two words</pre> |  |  |  |  |  |  |

| where:                                                                                                                                              |                                                                                                                                             |  |  |  |  |  |  |

| op is one of:                                                                                                                                       |                                                                                                                                             |  |  |  |  |  |  |

| LDR Load Register.                                                                                                                                  |                                                                                                                                             |  |  |  |  |  |  |

| STR Store Register.                                                                                                                                 |                                                                                                                                             |  |  |  |  |  |  |

| type is one of:                                                                                                                                     |                                                                                                                                             |  |  |  |  |  |  |

| B unsigned byte, zero extend to 32 bits on loads.                                                                                                   |                                                                                                                                             |  |  |  |  |  |  |

| SB signed byte, sign extend to 32 bits (LDR only).                                                                                                  |                                                                                                                                             |  |  |  |  |  |  |

| H unsigned halfword, zero extend to 32 bits on loads                                                                                                | S.                                                                                                                                          |  |  |  |  |  |  |

| SH signed halfword, sign extend to 32 bits (LDR only)                                                                                               | ).                                                                                                                                          |  |  |  |  |  |  |

| - omit, for word.                                                                                                                                   |                                                                                                                                             |  |  |  |  |  |  |

| cond is an optional condition code, see "Conditional Ex                                                                                             | ecution".                                                                                                                                   |  |  |  |  |  |  |

| Rt is the register to load or store.                                                                                                                |                                                                                                                                             |  |  |  |  |  |  |

| Rn is the register on which the memory address is ba                                                                                                | is the register on which the memory address is based.                                                                                       |  |  |  |  |  |  |

| offset is an offset from <i>Rn</i> . If <i>offset</i> is omitted, the addres                                                                        | is an offset from Rn. If offset is omitted, the address is the contents of Rn.                                                              |  |  |  |  |  |  |

| Rt2 is the additional register to load or store for two-we                                                                                          | 2 is the additional register to load or store for two-word operations.                                                                      |  |  |  |  |  |  |

| Operation                                                                                                                                           |                                                                                                                                             |  |  |  |  |  |  |

| LDR instructions load one or two registers with a value from mer                                                                                    | mory.                                                                                                                                       |  |  |  |  |  |  |

STR instructions store one or two register values to memory.

Load and store instructions with immediate offset can use the following addressing modes:

Offset Addressing

The offset value is added to or subtracted from the address obtained from the register *Rn*. The result is used as the address for the memory access. The register Rn is unaltered. The assembly language syntax for this mode is:

[Rn, #offset]

Atmel

# Examples

| SHASX | R7, R4, R2 | ; Adds top halfword of R4 to bottom halfword of R2     |

|-------|------------|--------------------------------------------------------|

|       |            | ; and writes halved result to top halfword of R7       |

|       |            | ; Subtracts top halfword of R2 from bottom halfword of |

|       |            | ; R4 and writes halved result to bottom halfword of R7 |

| SHSAX | R0, R3, R5 | ; Subtracts bottom halfword of R5 from top halfword    |

|       |            | ; of R3 and writes halved result to top halfword of R0 |

|       |            | ; Adds top halfword of R5 to bottom halfword of R3 and |

|       |            | ; writes halved result to bottom halfword of R0.       |

- All conditional instructions except B*cond* must be inside an IT block. B*cond* can be either outside or inside an IT block but has a larger branch range if it is inside one

- Each instruction inside the IT block must specify a condition code suffix that is either the same or logical inverse as for the other instructions in the block.

Your assembler might place extra restrictions on the use of IT blocks, such as prohibiting the use of assembler directives within them.

Condition Flags

This instruction does not change the flags.

Example

| ADDSNE    | R2, R2,      | #1  | ;<br>; | Next 3 instructions are conditional<br>ANDNE does not update condition flags<br>ADDSNE updates condition flags<br>Conditional move |

|-----------|--------------|-----|--------|------------------------------------------------------------------------------------------------------------------------------------|

| CMP       | R0, #9<br>GT |     | ;      | Convert R0 hex value (0 to 15) into ASCII<br>('0'-'9', 'A'-'F')<br>Next 2 instructions are conditional                             |

|           | -            | #55 |        | Convert 0xA -> 'A'                                                                                                                 |

|           |              |     |        | Convert 0x0 -> '0'                                                                                                                 |

|           |              |     |        | IT block with only one conditional instruction<br>Increment R1 conditionally                                                       |

| ITTEE     | EQ           |     | ;      | Next 4 instructions are conditional                                                                                                |

| MOVEQ     | R0, R1       |     | ;      | Conditional move                                                                                                                   |

| ADDEQ     | R2, R2,      | #10 | ;      | Conditional add                                                                                                                    |

|           |              |     |        | Conditional AND                                                                                                                    |

| BNE.W     | dloop        |     |        | Branch instruction can only be used in the last                                                                                    |

| IT<br>ADD |              |     | ;      | instruction of an IT block<br>Next instruction is conditional<br>Syntax error: no condition code used in IT block                  |

#### 12.6.10.4 TBB and TBH

Table Branch Byte and Table Branch Halfword.

Syntax

TBB [*Rn*, *Rm*] TBH [*Rn*, *Rm*, LSL #1]

where:

| Rn | is the register containing the address of the table of branch lengths.                                                                                            |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | If <i>Rn</i> is PC, then the address of the table is the address of the byte immediately following the TBB or TBH instruction.                                    |

| Rm | is the index register. This contains an index into the table. For halfword tables, LSL #1 doubles the value in <i>Rm</i> to form the right offset into the table. |

| 12.11.2.1 | MPU Type Register |    |      |      |    |    |          |  |  |

|-----------|-------------------|----|------|------|----|----|----------|--|--|

| Name:     | MPU_TYPE          |    |      |      |    |    |          |  |  |

| Access:   | Read/Write        |    |      |      |    |    |          |  |  |

| 31        | 30                | 29 | 28   | 27   | 26 | 25 | 24       |  |  |

| -         | -                 | _  | -    | -    | -  | -  | -        |  |  |

| 23        | 22                | 21 | 20   | 19   | 18 | 17 | 16       |  |  |

|           |                   |    | IREC | GION |    |    |          |  |  |

| 15        | 14                | 13 | 12   | 11   | 10 | 9  | 8        |  |  |

|           |                   |    | DRE  | GION |    |    |          |  |  |

| 7         | 6                 | 5  | 4    | 3    | 2  | 1  | 0        |  |  |

| -         | -                 | _  | _    | _    | _  | _  | SEPARATE |  |  |

The MPU\_TYPE register indicates whether the MPU is present, and if so, how many regions it supports.

# • IREGION: Instruction Region

Indicates the number of supported MPU instruction regions.

Always contains 0x00. The MPU memory map is unified and is described by the DREGION field.

#### • DREGION: Data Region

Indicates the number of supported MPU data regions: 0x08 = Eight MPU regions.

# • SEPARATE: Separate Instruction

Indicates support for unified or separate instruction and date memory maps:

0: Unified.

# 14.5 Reset Controller (RSTC) User Interface

|        | · · · · · · · · · · · · · · · · · · · |         |            |                            |

|--------|---------------------------------------|---------|------------|----------------------------|

| Offset | Register                              | Name    | Access     | Reset                      |

| 0x00   | Control Register                      | RSTC_CR | Write-only | _                          |

| 0x04   | Status Register                       | RSTC_SR | Read-only  | 0x0000_0000 <sup>(1)</sup> |

| 0x08   | Mode Register                         | RSTC_MR | Read/Write | 0x0000 0001                |

#### Table 14-1. Register Mapping

Note: 1. This value assumes that a general reset has been performed, subject to change if other types of reset are generated.

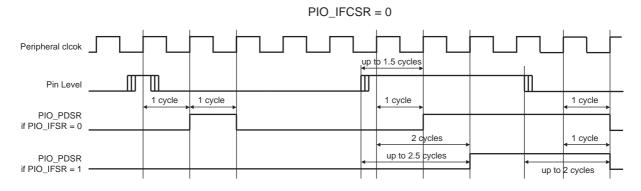

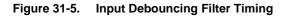

The glitch filters are controlled by the Input Filter Enable Register (PIO\_IFER), the Input Filter Disable Register (PIO\_IFDR) and the Input Filter Status Register (PIO\_IFSR). Writing PIO\_IFER and PIO\_IFDR respectively sets and clears bits in PIO\_IFSR. This last register enables the glitch filter on the I/O lines.

When the glitch and/or debouncing filter is enabled, it does not modify the behavior of the inputs on the peripherals. It acts only on the value read in PIO\_PDSR and on the input change interrupt detection. The glitch and debouncing filters require that the peripheral clock is enabled.

#### 31.5.10 Input Edge/Level Interrupt

The PIO Controller can be programmed to generate an interrupt when it detects an edge or a level on an I/O line. The Input Edge/Level interrupt is controlled by writing the Interrupt Enable Register (PIO\_IER) and the Interrupt Disable Register (PIO\_IDR), which enable and disable the input change interrupt respectively by setting and clearing the corresponding bit in the Interrupt Mask Register (PIO\_IMR). As input change detection is possible only by comparing two successive samplings of the input of the I/O line, the peripheral clock must be enabled. The Input Change interrupt is available regardless of the configuration of the I/O line, i.e., configured as an input only, controlled by the PIO Controller or assigned to a peripheral function.

By default, the interrupt can be generated at any time an edge is detected on the input.

Some additional interrupt modes can be enabled/disabled by writing in the Additional Interrupt Modes Enable Register (PIO\_AIMER) and Additional Interrupt Modes Disable Register (PIO\_AIMDR). The current state of this selection can be read through the Additional Interrupt Modes Mask Register (PIO\_AIMMR).

These additional modes are:

# Atmel

#### 32.8.1 Clock Management

The transmitter clock can be generated by:

- an external clock received on the TK I/O pad

- the receiver clock

- the internal clock divider

The receiver clock can be generated by:

- an external clock received on the RK I/O pad

- the transmitter clock

- the internal clock divider

Furthermore, the transmitter block can generate an external clock on the TK I/O pad, and the receiver block can generate an external clock on the RK I/O pad.

This allows the SSC to support many Master and Slave Mode data transfers.

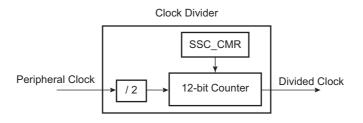

#### 32.8.1.1 Clock Divider

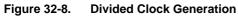

#### Figure 32-7. Divided Clock Block Diagram

The peripheral clock divider is determined by the 12-bit field DIV counter and comparator (so its maximal value is 4095) in the Clock Mode Register (SSC\_CMR), allowing a peripheral clock division by up to 8190. The Divided Clock is provided to both the Receiver and Transmitter. When this field is programmed to 0, the Clock Divider is not used and remains inactive.

When DIV is set to a value equal to or greater than 1, the Divided Clock has a frequency of peripheral clock divided by 2 times DIV. Each level of the Divided Clock has a duration of the peripheral clock multiplied by DIV. This ensures a 50% duty cycle for the Divided Clock regardless of whether the DIV value is even or odd.

# 32.9 Synchronous Serial Controller (SSC) User Interface

| Offset      | Register                         | Name     | Access     | Reset      |

|-------------|----------------------------------|----------|------------|------------|

| 0x0         | Control Register                 | SSC_CR   | Write-only | -          |

| 0x4         | Clock Mode Register              | SSC_CMR  | Read/Write | 0x0        |

| 0x8–0xC     | Reserved                         | -        | _          | _          |

| 0x10        | Receive Clock Mode Register      | SSC_RCMR | Read/Write | 0x0        |

| 0x14        | Receive Frame Mode Register      | SSC_RFMR | Read/Write | 0x0        |

| 0x18        | Transmit Clock Mode Register     | SSC_TCMR | Read/Write | 0x0        |

| 0x1C        | Transmit Frame Mode Register     | SSC_TFMR | Read/Write | 0x0        |

| 0x20        | Receive Holding Register         | SSC_RHR  | Read-only  | 0x0        |

| 0x24        | Transmit Holding Register        | SSC_THR  | Write-only | _          |

| 0x28-0x2C   | Reserved                         | -        | _          | _          |

| 0x30        | Receive Sync. Holding Register   | SSC_RSHR | Read-only  | 0x0        |

| 0x34        | Transmit Sync. Holding Register  | SSC_TSHR | Read/Write | 0x0        |

| 0x38        | Receive Compare 0 Register       | SSC_RC0R | Read/Write | 0x0        |

| 0x3C        | Receive Compare 1 Register       | SSC_RC1R | Read/Write | 0x0        |

| 0x40        | Status Register                  | SSC_SR   | Read-only  | 0x000000CC |

| 0x44        | Interrupt Enable Register        | SSC_IER  | Write-only | _          |

| 0x48        | Interrupt Disable Register       | SSC_IDR  | Write-only | _          |

| 0x4C        | Interrupt Mask Register          | SSC_IMR  | Read-only  | 0x0        |

| 0x50-0xE0   | Reserved                         | -        | _          | _          |

| 0xE4        | Write Protection Mode Register   | SSC_WPMR | Read/Write | 0x0        |

| 0xE8        | Write Protection Status Register | SSC_WPSR | Read-only  | 0x0        |

| 0xEC-0xFC   | Reserved                         | _        | _          | _          |

| 0x100–0x128 | Reserved for PDC registers       | -        | -          | _          |

### Table 32-5. Register Mapping

| 32.9.9 SSC Receive Synchronization Holding Register |            |    |     |     |    |    |    |  |  |  |

|-----------------------------------------------------|------------|----|-----|-----|----|----|----|--|--|--|

| Name:                                               | SSC_RSHR   |    |     |     |    |    |    |  |  |  |

| Address:                                            | 0x40004030 |    |     |     |    |    |    |  |  |  |

| Access:                                             | Read-only  |    |     |     |    |    |    |  |  |  |

| 31                                                  | 30         | 29 | 28  | 27  | 26 | 25 | 24 |  |  |  |

| -                                                   | -          | -  | -   | -   | -  | -  | -  |  |  |  |

| 23                                                  | 22         | 21 | 20  | 19  | 18 | 17 | 16 |  |  |  |

| -                                                   | -          | -  | -   | -   | -  | -  | -  |  |  |  |

| 15                                                  | 14         | 13 | 12  | 11  | 10 | 9  | 8  |  |  |  |

|                                                     | RSDAT      |    |     |     |    |    |    |  |  |  |

| 7                                                   | 6          | 5  | 4   | 3   | 2  | 1  | 0  |  |  |  |

|                                                     |            |    | RSI | DAT |    |    |    |  |  |  |

• RSDAT: Receive Synchronization Data

#### 33.7.3 Master Mode Operations

When configured in Master mode, the SPI operates on the clock generated by the internal programmable baud rate generator. It fully controls the data transfers to and from the slave(s) connected to the SPI bus. The SPI drives the chip select line to the slave and the serial clock signal (SPCK).

The SPI features two holding registers, the Transmit Data Register (SPI\_TDR) and the Receive Data Register (SPI\_RDR), and a single shift register. The holding registers maintain the data flow at a constant rate.

After enabling the SPI, a data transfer starts when the processor writes to the SPI\_TDR. The written data is immediately transferred in the Shift register and the transfer on the SPI bus starts. While the data in the Shift register is shifted on the MOSI line, the MISO line is sampled and shifted in the Shift register. Data cannot be loaded in the SPI\_RDR without transmitting data. If there is no data to transmit, dummy data can be used (SPI\_TDR filled with ones). When the SPI\_MR.WDRBT bit is set, new data cannot be transmitted if the SPI\_RDR has not been read. If Receiving mode is not required, for example when communicating with a slave receiver only (such as an LCD), the receive status flags in the SPI Status register (SPI\_SR) can be discarded.

Before writing the SPI\_TDR, the PCS field in the SPI\_MR must be set in order to select a slave.

If new data is written in the SPI\_TDR during the transfer, it is kept in the SPI\_TDR until the current transfer is completed. Then, the received data is transferred from the Shift register to the SPI\_RDR, the data in the SPI\_TDR is loaded in the Shift register and a new transfer starts.

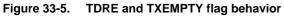

As soon as the SPI\_TDR is written, the Transmit Data Register Empty (TDRE) flag in the SPI\_SR is cleared. When the data written in the SPI\_TDR is loaded into the Shift register, the TDRE flag in the SPI\_SR is set. The TDRE bit is used to trigger the Transmit PDC channel.

See Figure 33-5.

The end of transfer is indicated by the TXEMPTY flag in the SPI\_SR. If a transfer delay (DLYBCT) is greater than 0 for the last transfer, TXEMPTY is set after the completion of this delay. The peripheral clock can be switched off at this time.

Note: When the SPI is enabled, the TDRE and TXEMPTY flags are set.

The transfer of received data from the Shift register to the SPI\_RDR is indicated by the Receive Data Register Full (RDRF) bit in the SPI\_SR. When the received data is read, the RDRF bit is cleared.

If the SPI\_RDR has not been read before new data is received, the Overrun Error (OVRES) bit in the SPI\_SR is set. As long as this flag is set, data is loaded in the SPI\_RDR. The user has to read the SPI\_SR to clear the OVRES bit.

Figure 33-6, shows a block diagram of the SPI when operating in Master mode. Figure 33-7 on page 695 shows a flow chart describing how transfers are handled.

# Atmel

#### 33.8.3 SPI Receive Data Register

| Name:    | SPI_RDR    |    |    |    |    |    |    |

|----------|------------|----|----|----|----|----|----|

| Address: | 0x40008008 |    |    |    |    |    |    |

| Access:  | Read-only  |    |    |    |    |    |    |

| 31       | 30         | 29 | 28 | 27 | 26 | 25 | 24 |

| _        | -          | _  | -  | _  | -  | -  | -  |

| 23       | 22         | 21 | 20 | 19 | 18 | 17 | 16 |

| _        | -          | _  | -  |    | PC | S  |    |

| 15       | 14         | 13 | 12 | 11 | 10 | 9  | 8  |

|          |            |    | R  | D  |    |    |    |

| 7        | 6          | 5  | 4  | 3  | 2  | 1  | 0  |

|          |            |    | R  | D  |    |    |    |

#### • RD: Receive Data

Data received by the SPI Interface is stored in this register in a right-justified format. Unused bits are read as zero.

#### • PCS: Peripheral Chip Select

In Master mode only, these bits indicate the value on the NPCS pins at the end of a transfer. Otherwise, these bits are read as zero.

Note: When using Variable peripheral select mode (PS = 1 in SPI\_MR), it is mandatory to set the SPI\_MR.WDRBT bit to 1 if the PCS field must be processed in SPI\_RDR.

The BITS field determines the number of data bits transferred. Reserved values should not be used.

| Value | Name   | Description          |

|-------|--------|----------------------|

| 0     | 8_BIT  | 8 bits for transfer  |

| 1     | 9_BIT  | 9 bits for transfer  |

| 2     | 10_BIT | 10 bits for transfer |

| 3     | 11_BIT | 11 bits for transfer |

| 4     | 12_BIT | 12 bits for transfer |

| 5     | 13_BIT | 13 bits for transfer |

| 6     | 14_BIT | 14 bits for transfer |

| 7     | 15_BIT | 15 bits for transfer |

| 8     | 16_BIT | 16 bits for transfer |

| 9     | -      | Reserved             |

| 10    | -      | Reserved             |

| 11    | -      | Reserved             |

| 12    | -      | Reserved             |

| 13    | -      | Reserved             |

| 14    | -      | Reserved             |

| 15    | -      | Reserved             |

# • SCBR: Serial Clock Bit Rate

In Master mode, the SPI Interface uses a modulus counter to derive the SPCK bit rate from the peripheral clock. The bit rate is selected by writing a value from1 to 255 in the SCBR field. The following equation determines the SPCK bit rate:

SCBR = f<sub>peripheral clock</sub> / SPCK Bit Rate

Programming the SCBR field to 0 is forbidden. Triggering a transfer while SCBR is at 0 can lead to unpredictable results.

If BRSRCCLK = 1 in SPI\_MR, SCBR must be programmed with a value greater than 1.

At reset, SCBR is 0 and the user has to program it at a valid value before performing the first transfer.

Note: If one of the SCBR fields in SPI\_CSRx is set to 1, the other SCBR fields in SPI\_CSRx must be set to 1 as well, if they are used to process transfers. If they are not used to transfer data, they can be set at any value.

# • DLYBS: Delay Before SPCK

This field defines the delay from NPCS falling edge (activation) to the first valid SPCK transition.

When DLYBS = 0, the delay is half the SPCK clock period.

Otherwise, the following equation determines the delay:

DLYBS = Delay Before SPCK × f<sub>peripheral clock</sub>

# DLYBCT: Delay Between Consecutive Transfers

This field defines the delay between two consecutive transfers with the same peripheral without removing the chip select. The delay is always inserted after each transfer and before removing the chip select if needed.

When DLYBCT = 0, no delay between consecutive transfers is inserted and the clock keeps its duty cycle over the character transfers.

Otherwise, the following equation determines the delay:

DLYBCT = Delay Between Consecutive Transfers × f<sub>peripheral clock</sub> / 32

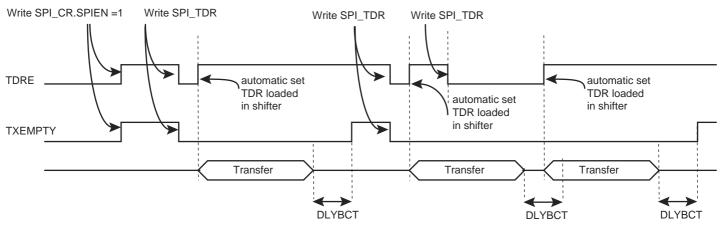

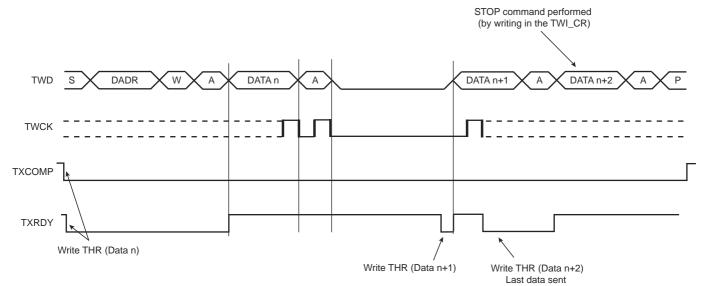

After a master write transfer, the SCL is stretched (tied low) as long as no new data is written in the TWI\_THR or until a STOP command is performed.

See Figure 34-5, Figure 34-6, and Figure 34-7.

Figure 34-5. Master Write with One Data Byte

# • ETRGS: External Trigger Status (cleared on read)

0: External trigger has not occurred since the last read of the Status Register.

1: External trigger has occurred since the last read of the Status Register.

### • CLKSTA: Clock Enabling Status

0: Clock is disabled.

1: Clock is enabled.

# • MTIOA: TIOA Mirror

0: TIOA is low. If TC\_CMRx.WAVE = 0, this means that TIOA pin is low. If TC\_CMRx.WAVE = 1, this means that TIOA is driven low.

1: TIOA is high. If TC\_CMRx.WAVE = 0, this means that TIOA pin is high. If TC\_CMRx.WAVE = 1, this means that TIOA is driven high.

# • MTIOB: TIOB Mirror

0: TIOB is low. If TC\_CMRx.WAVE = 0, this means that TIOB pin is low. If TC\_CMRx.WAVE = 1, this means that TIOB is driven low.

1: TIOB is high. If TC\_CMRx.WAVE = 0, this means that TIOB pin is high. If TC\_CMRx.WAVE = 1, this means that TIOB is driven high.

# 37.7.15 TC QDEC Interrupt Enable Register

| Name:    | TC_QIER                        |    |    |    |      |        |     |  |  |

|----------|--------------------------------|----|----|----|------|--------|-----|--|--|

| Address: | 0x400100C8 (0), 0x400140C8 (1) |    |    |    |      |        |     |  |  |

| Access:  | Write-only                     |    |    |    |      |        |     |  |  |

| 31       | 30                             | 29 | 28 | 27 | 26   | 25     | 24  |  |  |

| _        | -                              | _  | -  | -  | _    | _      | —   |  |  |

| 23       | 22                             | 21 | 20 | 19 | 18   | 17     | 16  |  |  |

| -        | -                              | -  | -  | -  | -    | -      | -   |  |  |

| 15       | 14                             | 13 | 12 | 11 | 10   | 9      | 8   |  |  |

| -        | —                              | -  | -  | -  | -    | -      | -   |  |  |

| 7        | 6                              | 5  | 4  | 3  | 2    | 1      | 0   |  |  |

| -        | -                              | _  | -  | _  | QERR | DIRCHG | IDX |  |  |

# • IDX: Index

0: No effect.

1: Enables the interrupt when a rising edge occurs on IDX input.

#### • DIRCHG: Direction Change

0: No effect.

1: Enables the interrupt when a change on rotation direction is detected.

#### • QERR: Quadrature Error

0: No effect.

1: Enables the interrupt when a quadrature error occurs on PHA, PHB.

# 39.7.2 PWM Enable Register

| Name:<br>Address: | PWM_ENA<br>0x40020004 |    |    |       |       |       |       |

|-------------------|-----------------------|----|----|-------|-------|-------|-------|

| Access:           | Write-only            |    |    |       |       |       |       |

| 31                | 30                    | 29 | 28 | 27    | 26    | 25    | 24    |

| _                 | -                     | -  | _  | _     | _     | _     | —     |

| 23                | 22                    | 21 | 20 | 19    | 18    | 17    | 16    |

| _                 | -                     | -  | _  | _     | _     | _     | _     |

| 15                | 14                    | 13 | 12 | 11    | 10    | 9     | 8     |

| -                 | -                     | _  | _  | _     | _     | _     | -     |

| 7                 | 6                     | 5  | 4  | 3     | 2     | 1     | 0     |

| -                 | -                     | -  | _  | CHID3 | CHID2 | CHID1 | CHID0 |

#### • CHIDx: Channel ID

0: No effect.

1: Enable PWM output for channel x.

#### 40.7.12 UDP FIFO Data Register

| Name:    | UDP_FDRx [x = 07] |    |       |       |    |    |    |  |

|----------|-------------------|----|-------|-------|----|----|----|--|

| Address: | 0x40034050        |    |       |       |    |    |    |  |

| Access:  | Read/Write        |    |       |       |    |    |    |  |

| 31       | 30                | 29 | 28    | 27    | 26 | 25 | 24 |  |

| -        | -                 | _  | -     | -     | -  | -  | -  |  |

| 23       | 22                | 21 | 20    | 19    | 18 | 17 | 16 |  |

| —        | -                 | -  | -     | -     | -  | -  | -  |  |

| 15       | 14                | 13 | 12    | 11    | 10 | 9  | 8  |  |

| -        | -                 | _  | -     | _     | _  | _  | _  |  |

| 7        | 6                 | 5  | 4     | 3     | 2  | 1  | 0  |  |

|          |                   |    | FIFO_ | _DATA |    |    |    |  |

#### • FIFO\_DATA[7:0]: FIFO Data Value

The microcontroller can push or pop values in the FIFO through this register.

RXBYTECNT in the corresponding UDP\_CSRx is the number of bytes to be read from the FIFO (sent by the host).

The maximum number of bytes to write is fixed by the Max Packet Size in the Standard Endpoint Descriptor. It can not be more than the physical memory size associated to the endpoint. Refer to the *Universal Serial Bus Specification, Rev. 2.0* for more information.

# 41.7.7 ACC Analog Control Register

| Name:    | ACC_ACR    |    |    |    |    |     |      |

|----------|------------|----|----|----|----|-----|------|

| Address: | 0x40040094 |    |    |    |    |     |      |

| Access:  | Read/Write |    |    |    |    |     |      |

| 31       | 30         | 29 | 28 | 27 | 26 | 25  | 24   |

| —        | -          | -  | -  | -  | -  | —   | -    |

| 23       | 22         | 21 | 20 | 19 | 18 | 17  | 16   |

| -        | -          | —  | -  | -  | -  | -   | -    |

| 15       | 14         | 13 | 12 | 11 | 10 | 9   | 8    |

| _        | -          | —  | —  | -  | -  | -   | -    |

| 7        | 6          | 5  | 4  | 3  | 2  | 1   | 0    |

| -        | -          | -  | -  | -  | HY | ′SΤ | ISEL |

This register can only be written if the WPEN bit is cleared in ACC Write Protection Mode Register.

# • ISEL: Current Selection

Refer to the section on ACC electrical characteristics in the datasheet.

0 (LOPW): Low-power option.

1 (HISP): High-speed option.

# • HYST: Hysteresis Selection

0 to 3: Refer to the section on ACC electrical characteristics in the datasheet.

|              | @ 2                       | 25°C                      | @ 85°C                    | @ 105°C                   |      |

|--------------|---------------------------|---------------------------|---------------------------|---------------------------|------|

| Conditions   | (AMP1)<br>Configuration A | (AMP1)<br>Configuration B | (AMP1)<br>Configuration A | (AMP1)<br>Configuration A | Unit |

| VDDIO = 3.6V | 1.9                       | 1.8                       | 6.8                       | 14.6                      |      |

| VDDIO = 3.3V | 1.7                       | 1.6                       | 6.2                       | 13.4                      |      |

| VDDIO = 3.0V | 1.5                       | 1.4                       | 5.7                       | 12.5                      | μA   |

| VDDIO = 2.5V | 1.3                       | 1.2                       | 5.1                       | 11.3                      |      |

| VDDIO = 1.8V | 0.9                       | 0.8                       | 4.4                       | 9.9                       |      |

#### Table 44-9. Typical Power Consumption for Backup Mode (SAM4S4/S2 rev A)

#### Table 44-10. Typical Power Consumption for Backup Mode (SAM4SD32/SD16/SA16 rev A)

|              | @:                        | 25°C                      | @ 85°C                    | @ 105°C                   |      |

|--------------|---------------------------|---------------------------|---------------------------|---------------------------|------|

| Conditions   | (AMP1)<br>Configuration A | (AMP1)<br>Configuration B | (AMP1)<br>Configuration A | (AMP1)<br>Configuration A | Unit |

| VDDIO = 3.6V | 2.1                       | 2.0                       | 13.9                      | 22.5                      |      |

| VDDIO = 3.3V | 1.8                       | 1.8                       | -                         | _                         |      |

| VDDIO = 3.0V | 1.7                       | 1.6                       | -                         | _                         | μA   |

| VDDIO = 2.5V | 1.3                       | 1.3                       | -                         | _                         |      |

| VDDIO = 1.8V | 0.9                       | 0.9                       | _                         | _                         |      |

#### Table 44-11. Typical Power Consumption for Backup Mode (SAM4S16/S8 rev A)

|              | @ 25°C                    |                           | @ 85°C                    | @ 105°C                   |      |

|--------------|---------------------------|---------------------------|---------------------------|---------------------------|------|

| Conditions   | (AMP1)<br>Configuration A | (AMP1)<br>Configuration B | (AMP1)<br>Configuration A | (AMP1)<br>Configuration A | Unit |

| VDDIO = 3.6V | 2.7                       | 2.5                       | 12.1                      | 20.1                      |      |

| VDDIO = 3.3V | 2.0                       | 1.8                       | _                         | _                         |      |

| VDDIO = 3.0V | 1.8                       | 1.7                       | _                         | _                         | μA   |

| VDDIO = 2.5V | 1.5                       | 1.4                       | -                         | _                         |      |

| VDDIO = 1.8V | 1                         | 0.9                       | _                         | _                         |      |

#### 44.5.7 3 to 20 MHz Crystal Characteristics

| Symbol             | Parameter                       | Conditions           | Min | Тур | Max | Unit |

|--------------------|---------------------------------|----------------------|-----|-----|-----|------|

| ESR                |                                 | Fundamental @ 3 MHz  |     |     | 200 |      |

|                    |                                 | Fundamental @ 8 MHz  |     |     | 100 |      |

|                    | Equivalent Series Resistor (Rs) | Fundamental @ 12 MHz |     | 80  | Ω   |      |

|                    |                                 | Fundamental @ 16 MHz |     |     | 80  |      |

|                    |                                 | Fundamental @ 20 MHz |     |     | 50  |      |

| C <sub>m</sub>     | Motional Capacitance            |                      | _   | _   | 8   | fF   |

| C <sub>SHUNT</sub> | Shunt Capacitance               |                      | -   | _   | 7   | pF   |

Table 44-32. 3 to 20 MHz Crystal Characteristics

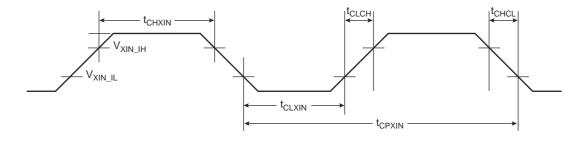

#### 44.5.8 3 to 20 MHz XIN Clock Input Characteristics in Bypass Mode

#### Table 44-33. XIN Clock Electrical Characteristics (In Bypass Mode)

| Symbol                     | Parameter                                        | Conditions | Min                         | Тур | Max                                             | Unit |

|----------------------------|--------------------------------------------------|------------|-----------------------------|-----|-------------------------------------------------|------|

| 1/(t <sub>CPXIN</sub> )    | XIN Clock Frequency                              | (1)        | _                           | _   | 50                                              | MHz  |

| t <sub>CPXIN</sub>         | XIN Clock Period                                 | (1)        | 20                          | _   | _                                               | ns   |

| t <sub>CHXIN</sub>         | XIN Clock High Half-period                       | (1)        | 8                           | _   | _                                               | ns   |

| t <sub>CLXIN</sub>         | XIN Clock Low Half-period                        | (1)        | 8                           | _   | _                                               | ns   |

| t <sub>CLCH</sub>          | Rise Time                                        | (1)        | 2.2                         | _   | _                                               | ns   |

| t <sub>CHCL</sub>          | Fall Time                                        | (1)        | 2.2                         | _   | _                                               | ns   |

| $V_{XIN_{IL}}$             | V <sub>XIN</sub> Input Low-level Voltage         | (1)        | -0.3                        | _   | $[0.8\text{V:}0.3\times\text{V}_{\text{DDIO}}]$ | V    |

| V <sub>XIN_IH</sub>        | V <sub>XIN</sub> Input High-level Voltage        | (1)        | $[2.0V:0.7\times V_{DDIO}]$ | _   | V <sub>DDIO</sub> + 0.3V                        | V    |

| C <sub>para(standby)</sub> | Internal Parasitic Capacitance<br>During Standby | (1)        | _                           | 5.5 | 6.3                                             | pF   |

| R <sub>para(standby)</sub> | Internal Parasitic Resistance<br>During Standby  | (1)        | _                           | 300 | _                                               | Ω    |

Note: 1. These characteristics apply only when the 3–20 MHz crystal oscillator is in Bypass mode.

#### Figure 44-16. XIN Clock Timing