Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | ARM® Cortex®-M4                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 120MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, Memory Card, SPI, SSC, UART/USART, USB           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                               |

| Number of I/O              | 47                                                                       |

| Program Memory Size        | 256KB (256K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 64K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                             |

| Data Converters            | A/D 11x12b; D/A 2x12b                                                    |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-LQFP                                                                  |

| Supplier Device Package    | 64-LQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4s4bb-anr |

4) 40 the entiority TST Voltage Regulator PCK[2:0] ◆ → PLLA JTAG and Serial Wire PLLB RC Osc 4/8/12 MHz In-Circuit Emulator Cortex-M4 Processor XIN **◆** 3–20 MHz Oscillator f<sub>MAX</sub> 120 MHz XOUT **←→** ERASE ←→ WKUP[15:0] **←** Backup XIN32 4 32K Cryst Osc Flash User Signature XOUT32 ← Unique Identifier 32K typ RC Osc I/D VDDIO VDDCORE Flash 1024/512 Kbytes VDDPLL RTCOUT0 RTCOUT1 4-layer AHB Bus Matrix SRAM f<sub>MAX</sub> 120 MHz 128 Kbytes NRST ◀ ROM S 16 Kbytes **▶** D[7:0] External Bus → A[23:0] AHB/APB Interface → A21/NANDALE System Controller PDC Bridge → A22/NANDCLE → NANDOE NANDWE → NWAIT TWCK0 → NCS[3:0] TWD0 → NRD **▶** NWE TWCK1 TWD1 URXD0 **▶** DDP UTXD0 → DDM URXD1 UTXD1 MCCK MCCDA SCK0 TXD0 MCDA[3:0] RXD0 RTS0 MISO → MOSI CTS0 → SPCK SCK1 NPCS[3:0] TXD1 TD RTS1 RD CTS1 DTR1 ΤK → RK DSR1 DCD1 → TF → RF RI1 PIODC[7:0] PIODCCLK PIODCEN[2:1] TCLK[2:0] → TIOA[2:0] PDC TIOB[2:0] AD[14:0] **4** ADC ADTRG ◀ TCLK[5:3] TIOA[5:3] **Event System** ADVREF TIOB[5:3] DAC[1:0] ◀ DAC DATRG 4 PWMH[3:0]

Figure 2-3. SAM4S16/S8 100-pin Version Block Diagram

→ PWML[3:0]

PWMFI0

ADC DAC

Temp Sensor

Analog Comparator

# 5.4 Typical Powering Schematics

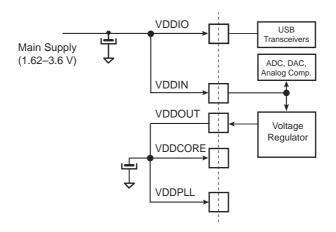

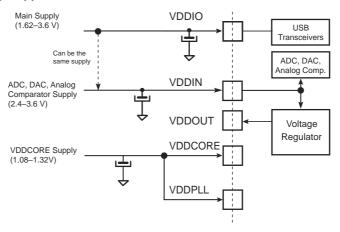

The SAM4S supports a 1.62–3.6 V single supply mode. The internal regulator input is connected to the source and its output feeds VDDCORE. Figure 5-2 below shows the power schematics.

As VDDIN powers the voltage regulator, the ADC, DAC and the analog comparator, when the user does not want to use the embedded voltage regulator, it can be disabled by software via the SUPC (note that this is different from Backup mode).

Figure 5-2. Single Supply

Note: Restrictions:

For USB, VDDIO needs to be greater than 3.0V.

For ADC, DAC and Analog Comparator, VDDIN needs to be greater than 2.4V.

Figure 5-3. Core Externally Supplied

Note: Restrictions:

For USB, VDDIO needs to be greater than 3.0V.

For ADC, DAC and Analog Comparator, VDDIN needs to be greater than 2.4V.

# 9. Real Time Event Management

The events generated by peripherals are designed to be directly routed to peripherals managing/using these events without processor intervention. Peripherals receiving events contain logic by which to select the one required.

# 9.1 Embedded Characteristics

- Timers, PWM, IO peripherals generate event triggers which are directly routed to event managers such as ADC or DACC, for example, to start measurement/conversion without processor intervention.

- UART, USART, SPI, TWI, SSC, PWM, HSMCI, ADC, DACC, PIO also generate event triggers directly connected to Peripheral DMA Controller (PDC) for data transfer without processor intervention.

- Parallel capture logic is directly embedded in PIO and generates trigger event to PDC to capture data without processor intervention.

- PWM security events (faults) are in combinational form and directly routed from event generators (ADC, ACC, PMC, TIMER) to PWM module.

- PMC security event (clock failure detection) can be programmed to switch the MCK on reliable main RC internal clock without processor intervention.

# 12.4.1.10 Interrupt Program Status Register

Name: IPSR

Access: Read/Write

**Reset:** 0x000000000

| 31 | 30 | 29 | 28     | 27    | 26 | 25 | 24         |

|----|----|----|--------|-------|----|----|------------|

|    |    |    | _      | -     |    |    |            |

| 23 | 22 | 21 | 20     | 19    | 18 | 17 | 16         |

|    |    |    |        | -     |    |    |            |

| 15 | 14 | 13 | 12     | 11    | 10 | 9  | 8          |

|    |    |    | _      |       |    |    | ISR_NUMBER |

| 7  | 6  | 5  | 4      | 3     | 2  | 1  | 0          |

|    |    |    | ISR_NU | JMBER |    |    |            |

The IPSR contains the exception type number of the current Interrupt Service Routine (ISR).

# • ISR\_NUMBER: Number of the Current Exception

0 = Thread mode

1 = Reserved

2 = NMI

3 = Hard fault

4 = Memory management fault

5 = Bus fault

6 = Usage fault

7-10 = Reserved

11 = SVCall

12 = Reserved for Debug

13 = Reserved

14 = PendSV

15 = SysTick

16 = IRQ0

49 = IRQ34

See "Exception Types" for more information.

### Examples

```

AND R9, R2, #0xFF00

ORREQ R2, R0, R5

ANDS R9, R8, #0x19

EORS R7, R11, #0x18181818

BIC R0, R1, #0xab

ORN R7, R11, R14, ROR #4

ORNS R7, R11, R14, ASR #32

```

### 12.6.5.3 ASR, LSL, LSR, ROR, and RRX

Arithmetic Shift Right, Logical Shift Left, Logical Shift Right, Rotate Right, and Rotate Right with Extend.

### **Syntax**

```

op{S}{cond} Rd, Rm, Rs

op{S}{cond} Rd, Rm, #n

RRX{S}{cond} Rd, Rm

```

#### where:

op is one of:

ASR Arithmetic Shift Right.

LSL Logical Shift Left.

LSR Logical Shift Right.

ROR Rotate Right.

S is an optional suffix. If S is specified, the condition code flags are updated on the result of the operation, see "Conditional Execution".

Rd is the destination register.

Rm is the register holding the value to be shifted.

Rs is the register holding the shift length to apply to the value in *Rm*. Only the least

significant byte is used and can be in the range 0 to 255.

n is the shift length. The range of shift length depends on the instruction:

ASR shift length from 1 to 32 LSL shift length from 0 to 31 LSR shift length from 1 to 32 ROR shift length from 0 to 31

MOVS Rd, Rm is the preferred syntax for LSLS Rd, Rm, #0.

### Operation

ASR, LSL, LSR, and ROR move the bits in the register *Rm* to the left or right by the number of places specified by constant *n* or register *Rs*.

RRX moves the bits in register *Rm* to the right by 1.

In all these instructions, the result is written to *Rd*, but the value in register *Rm* remains unchanged. For details on what result is generated by the different instructions, see "Shift Operations".

#### Restrictions

Do not use SP and do not use PC.

Condition Flags

### 12.6.6.12 SDIV and UDIV

Signed Divide and Unsigned Divide.

### Syntax

```

SDIV\{cond\} {Rd,} Rn, Rm UDIV\{cond\} {Rd,} Rn, Rm

```

#### where:

cond is an optional condition code, see "Conditional Execution".

Rd is the destination register. If *Rd* is omitted, the destination register is *Rn*.

Rn is the register holding the value to be divided.

Rm is a register holding the divisor.

### Operation

SDIV performs a signed integer division of the value in *Rn* by the value in *Rm*.

UDIV performs an unsigned integer division of the value in Rn by the value in Rm.

For both instructions, if the value in *Rn* is not divisible by the value in *Rm*, the result is rounded towards zero.

# Restrictions

Do not use SP and do not use PC.

# Condition Flags

These instructions do not change the flags.

# Examples

```

SDIV R0, R2, R4 ; Signed divide, R0 = R2/R4 UDIV R8, R8, R1 ; Unsigned divide, R8 = R8/R1

```

#### 12.9.1.10 System Handler Priority Register 2

Name: SCB\_SHPR2 Access: Read/Write

| 31 | 30 | 29 | 28 | 27  | 26 | 25 | 24 |

|----|----|----|----|-----|----|----|----|

|    |    |    | PR | _11 |    |    |    |

| 23 | 22 | 21 | 20 | 19  | 18 | 17 | 16 |

| _  | _  | -  | _  | _   | _  | ı  | _  |

| 15 | 14 | 13 | 12 | 11  | 10 | 9  | 8  |

| _  | _  | -  | _  | _   | _  | ı  | _  |

| 7  | 6  | 5  | 4  | 3   | 2  | 1  | 0  |

| _  | _  | _  | _  | _   | _  | -  | _  |

# • PRI\_11: Priority

Priority of system handler 11, SVCall.

### 16.6.2 RTC Mode Register

Name: RTC\_MR

Address: 0x400E1464

Access: Read/Write

| 31      | 30 | 29   | 28     | 27         | 26 | 25      | 24    |

|---------|----|------|--------|------------|----|---------|-------|

| _       | 1  | TPE  | RIOD   | _          |    | THIGH   |       |

| 23      | 22 | 21   | 20     | 19         | 18 | 17      | 16    |

| _       |    | OUT1 |        | _          |    | OUT0    |       |

| 15      | 14 | 13   | 12     | 11         | 10 | 9       | 8     |

| HIGHPPM |    |      |        | CORRECTION |    |         |       |

| 7       | 6  | 5    | 4      | 3          | 2  | 1       | 0     |

| _       | _  | _    | NEGPPM | _          | _  | PERSIAN | HRMOD |

This register can only be written if the WPEN bit is cleared in the System Controller Write Protection Mode Register (SYSC\_WPMR).

#### • HRMOD: 12-/24-hour Mode

0: 24-hour mode is selected.

1: 12-hour mode is selected.

#### PERSIAN: PERSIAN Calendar

0: Gregorian calendar.

1: Persian calendar.

### • NEGPPM: NEGative PPM Correction

0: Positive correction (the divider will be slightly higher than 32768).

1: Negative correction (the divider will be slightly lower than 32768).

Refer to CORRECTION and HIGHPPM field descriptions.

Note: NEGPPM must be cleared to correct a crystal slower than 32.768 kHz.

### • CORRECTION: Slow Clock Correction

0: No correction

1–127: The slow clock will be corrected according to the formula given in HIGHPPM description.

### • HIGHPPM: HIGH PPM Correction

0: Lower range ppm correction with accurate correction.

1: Higher range ppm correction with accurate correction.

If the absolute value of the correction to be applied is lower than 30 ppm, it is recommended to clear HIGHPPM. HIGHPPM set to 1 is recommended for 30 ppm correction and above.

#### Formula:

If HIGHPPM = 0, then the clock frequency correction range is from 1.5 ppm up to 98 ppm. The RTC accuracy is less than 1 ppm for a range correction from 1.5 ppm up to 30 ppm.

The correction field must be programmed according to the required correction in ppm; the formula is as follows:

The **Memory Write** command **(WRAM)** is optimized for consecutive writes. Write handshaking can be chained; an internal address buffer is automatically increased.

Table 21-14. Write Command

| Step | Handshake Sequence | MODE[3:0] | DATA[15:0]         |

|------|--------------------|-----------|--------------------|

| 1    | Write handshaking  | CMDE      | WRAM               |

| 2    | Write handshaking  | ADDR0     | Memory Address LSB |

| 3    | Write handshaking  | ADDR1     | Memory Address     |

| 4    | Write handshaking  | DATA      | *Memory Address++  |

| 5    | Write handshaking  | DATA      | *Memory Address++  |

|      |                    |           |                    |

| n    | Write handshaking  | ADDR0     | Memory Address LSB |

| n+1  | Write handshaking  | ADDR1     | Memory Address     |

| n+2  | Write handshaking  | DATA      | *Memory Address++  |

| n+3  | Write handshaking  | DATA      | *Memory Address++  |

|      |                    |           |                    |

### 21.3.5.8 Get Version Command

The Get Version (GVE) command retrieves the version of the FFPI interface.

Table 21-15. Get Version Command

| Step | Handshake Sequence | MODE[3:0] | DATA[15:0] |  |

|------|--------------------|-----------|------------|--|

| 1    | Write handshaking  | CMDE      | GVE        |  |

| 2    | Read handshaking   | DATA      | Version    |  |

# 31.6.29 PIO Slow Clock Divider Debouncing Register

Name: PIO\_SCDR

**Address:** 0x400E0E8C (PIOA), 0x400E108C (PIOB), 0x400E128C (PIOC)

Access: Read/Write

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 |

|----|----|----|----|----|----|----|----|

| _  | _  | ı  | _  | 1  | -  | ı  | _  |

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| _  | _  | ı  | _  | 1  | -  | 1  | _  |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  |

| _  | _  |    |    | D  | IV |    |    |

| 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|    |    |    | D  | IV |    | _  |    |

# • DIV: Slow Clock Divider Selection for Debouncing

$$t_{\text{div\_slck}} = ((\text{DIV} + 1) \times 2) \times t_{\text{slck}}$$

# • TXBUFE: TX Buffer Empty (cleared by writing SPI\_TCR or SPI\_TNCR)

0: SPI\_TCR<sup>(1)</sup> or SPI\_TNCR<sup>(1)</sup> has a value other than 0.

1: Both SPI TCR<sup>(1)</sup> and SPI TNCR<sup>(1)</sup> have a value of 0.

### . NSSR: NSS Rising (cleared on read)

0: No rising edge detected on NSS pin since the last read of SPI\_SR.

1: A rising edge occurred on NSS pin since the last read of SPI\_SR.

# • TXEMPTY: Transmission Registers Empty (cleared by writing SPI\_TDR)

0: As soon as data is written in SPI\_TDR.

1: SPI\_TDR and internal shift register are empty. If a transfer delay has been defined, TXEMPTY is set after the end of this delay.

# • UNDES: Underrun Error Status (Slave mode only) (cleared on read)

0: No underrun has been detected since the last read of SPI\_SR.

1: A transfer starts whereas no data has been loaded in SPI\_TDR.

### • SPIENS: SPI Enable Status

0: SPI is disabled.

1: SPI is enabled.

Note: 1. SPI\_RCR, SPI\_RNCR, SPI\_TCR, SPI\_TNCR are PDC registers.

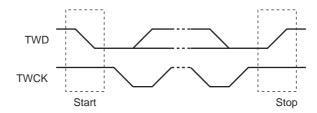

Figure 34-2. START and STOP Conditions

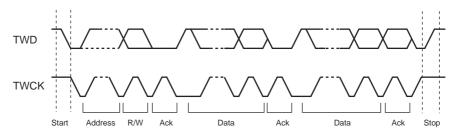

Figure 34-3. Transfer Format

# 34.7.2 Modes of Operation

The TWI has different modes of operations:

- Master transmitter mode

- Master receiver mode

- Multi-master transmitter mode

- Multi-master receiver mode

- Slave transmitter mode

- Slave receiver mode

These modes are described in the following sections.

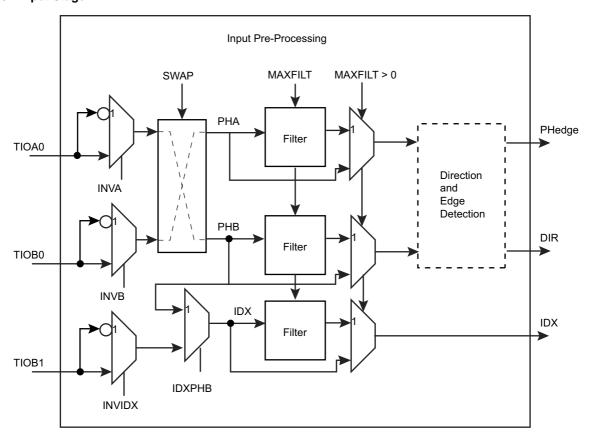

Figure 37-16. Input Stage

Input filtering can efficiently remove spurious pulses that might be generated by the presence of particulate contamination on the optical or magnetic disk of the rotary sensor.

Spurious pulses can also occur in environments with high levels of electro-magnetic interference. Or, simply if vibration occurs even when rotation is fully stopped and the shaft of the motor is in such a position that the beginning of one of the reflective or magnetic bars on the rotary sensor disk is aligned with the light or magnetic (Hall) receiver cell of the rotary sensor. Any vibration can make the PHA, PHB signals toggle for a short duration.

# 39.7.18 PWM Output Selection Register

Name: PWM\_OS

Address: 0x40020048

Access: Read/Write

| Access: | Read/write |    |    |      |          |      |      |

|---------|------------|----|----|------|----------|------|------|

| 31      | 30         | 29 | 28 | 27   | 26       | 25   | 24   |

| _       | _          | _  | _  | _    | _        | _    | _    |

| 23      | 22         | 21 | 20 | 19   | 18       | 17   | 16   |

| _       | -          | -  | -  | OSL3 | OSL2     | OSL1 | OSL0 |

| 15      | 14         | 13 | 12 | 11   | 10       | 9    | 8    |

| _       | _          | _  | 1  | 1    | 1        | 1    | _    |

| 7       | 6          | 5  | 4  | 3    | 2        | 1    | 0    |

| _       | _          | _  | _  | OSH3 | OSH2     | OSH1 | OSH0 |

|         |            | •  | •  | •    | <u> </u> | •    |      |

# • OSHx: Output Selection for PWMH output of the channel x

0: Dead-time generator output DTOHx selected as PWMH output of channel x.

# • OSLx: Output Selection for PWML output of the channel x

0: Dead-time generator output DTOLx selected as PWML output of channel x.

1: Output override value OOVLx selected as PWML output of channel x.

<sup>1:</sup> Output override value OOVHx selected as PWMH output of channel x.

# 39.7.26 PWM Fault Protection Value Register

Name: PWM\_FPV

Address: 0x40020068

Access: Read/Write

| Access: | Read/Write |    |    |       |       |       |       |

|---------|------------|----|----|-------|-------|-------|-------|

| 31      | 30         | 29 | 28 | 27    | 26    | 25    | 24    |

| _       | -          | _  | _  | _     | _     | _     | -     |

| 23      | 22         | 21 | 20 | 19    | 18    | 17    | 16    |

| _       | _          | _  | -  | FPVL3 | FPVL2 | FPVL1 | FPVL0 |

| 15      | 14         | 13 | 12 | 11    | 10    | 9     | 8     |

| _       | _          | _  | _  | _     | _     | _     | _     |

| 7       | 6          | 5  | 4  | 3     | 2     | 1     | 0     |

| _       | _          | _  | _  | FPVH3 | FPVH2 | FPVH1 | FPVH0 |

This register can only be written if bits WPSWS5 and WPHWS5 are cleared in the PWM Write Protection Status Register.

# • FPVHx: Fault Protection Value for PWMH output on channel x

0: PWMH output of channel x is forced to '0' when fault occurs.

1: PWMH output of channel x is forced to '1' when fault occurs.

# • FPVLx: Fault Protection Value for PWML output on channel x

0: PWML output of channel x is forced to '0' when fault occurs.

1: PWML output of channel x is forced to '1' when fault occurs.

# 41.7.7 ACC Analog Control Register

Name: ACC\_ACR

Address: 0x40040094

Access: Read/Write

| 31 | 30 | 29 | 28 | 27 | 26 | 25  | 24   |

|----|----|----|----|----|----|-----|------|

| _  | _  | -  | -  | _  | _  | -   | _    |

| 23 | 22 | 21 | 20 | 19 | 18 | 17  | 16   |

| _  | -  | _  | _  | _  | -  | _   | _    |

| 15 | 14 | 13 | 12 | 11 | 10 | 9   | 8    |

| _  | -  | _  | _  | _  | 1  | _   | _    |

| 7  | 6  | 5  | 4  | 3  | 2  | 1   | 0    |

| _  | _  | _  | _  | _  | HY | 'ST | ISEL |

This register can only be written if the WPEN bit is cleared in ACC Write Protection Mode Register.

# • ISEL: Current Selection

Refer to the section on ACC electrical characteristics in the datasheet.

0 (LOPW): Low-power option.1 (HISP): High-speed option.

# • HYST: Hysteresis Selection

1080

0 to 3: Refer to the section on ACC electrical characteristics in the datasheet.

**Atmel**

# 42.7.5 ADC Channel Enable Register

Name: ADC\_CHER

Address: 0x40038010

Access: Write-only

| 31   | 30   | 29   | 28   | 27   | 26   | 25  | 24  |

|------|------|------|------|------|------|-----|-----|

| _    | _    | _    | _    | _    | _    | _   | _   |

| 23   | 22   | 21   | 20   | 19   | 18   | 17  | 16  |

| _    | _    | _    | _    | _    | _    | _   | _   |

| 15   | 14   | 13   | 12   | 11   | 10   | 9   | 8   |

| CH15 | CH14 | CH13 | CH12 | CH11 | CH10 | CH9 | CH8 |

| 7    | 6    | 5    | 4    | 3    | 2    | 1   | 0   |

| CH7  | CH6  | CH5  | CH4  | CH3  | CH2  | CH1 | CH0 |

This register can only be written if the WPEN bit is cleared in the ADC Write Protection Mode Register.

# • CHx: Channel x Enable

0: No effect.

Note: If USEQ = 1 in the ADC\_MR, CHx corresponds to the xth channel of the sequence described in ADC\_SEQR1 and ADC\_SEQR2.

<sup>1:</sup> Enables the corresponding channel.

# 43.7.13 DACC Write Protection Status Register

Name: DACC\_WPSR

Address: 0x4003C0E8

Access: Read-only

| Access. | ixeau-only |    |     |      |    |    |      |

|---------|------------|----|-----|------|----|----|------|

| 31      | 30         | 29 | 28  | 27   | 26 | 25 | 24   |

| _       | _          | _  | _   | _    | _  | _  | _    |

| 23      | 22         | 21 | 20  | 19   | 18 | 17 | 16   |

| _       | _          | _  | _   | _    | _  | -  | _    |

| 15      | 14         | 13 | 12  | 11   | 10 | 9  | 8    |

|         |            |    | WPV | /SRC |    |    |      |

| 7       | 6          | 5  | 4   | 3    | 2  | 1  | 0    |

| _       | -          | _  | -   | _    | _  | _  | WPVS |

### • WPVS: Write Protection Violation Status

0: No write protection violation has occurred since the last read of the DACC\_WPSR.

#### WPVSRC: Write Protection Violation Source

When WPVS = 1, WPVSRC indicates the register address offset at which a write access has been attempted.

<sup>1:</sup> A write protection violation has occurred since the last read of the DACC\_WPSR. If this violation is an unauthorized attempt to write a protected register, the associated violation is reported into field WPVSRC.

# 48.3 Errata SAM4S4/S2 Rev. A Parts

The errata are applicable to the devices in Table 48-3.

Table 48-3. Device List for Errata Described in Section 48.3

| Device Name | Revision | Chip ID     |

|-------------|----------|-------------|

| SAM4S4C     | A        | 0x28AB_09E0 |

| SAM4S4B     | A        | 0x289B_09E0 |

| SAM4S4A     | A        | 0x288B_09E0 |

| SAM4S2C     | A        | 0x28AB_07E0 |

| SAM4S2B     | A        | 0x289B_07E0 |

| SAM4S2A     | A        | 0x288B_07E0 |

# 48.3.1 Flash Controller (EEFC)

Issue: Erase Sector (ES) Command Cannot Be Performed If a Subsector Is Locked (ONLY in Flash sector 0)

If one of the subsectors

- small sector 0

- small sector 1

- larger sector

is locked within the Flash sector 0, the erase sector (ES) command cannot be processed on non-locked subsectors. Refer to the Flash overview in Section 8. "Memories".

**Workaround:** All the lock bits of the sector 0 must be cleared prior to issuing the ES command. After the ES command has been issued, the lock bits must be reverted to the state before clearing them.

### 48.3.2 Flash

### Issue: Incorrect Flash Read May Occur Depending on VDDIO Voltage and Flash Wait State

Flash read issues leading to wrong instruction fetch or incorrect data read may occur under the following operating

VDDIO < 2.4V and Flash wait state<sup>(1)</sup>  $\geq$  1

If the core clock frequency does not require the use of the Flash wait state<sup>(2)</sup> (FWS = 0 in EEFC\_FMR) or if only data reads are performed on the Flash (e.g., if the code is running out of SRAM), there are no constraints on VDDIO voltage. The usable voltage range for VDDIO is defined in Table 44-3 "DC Characteristics".

Notes: 1. Defined by the FWS field in EEFC\_FMR.

2. See Section 44.12.9 "Embedded Flash Characteristics" for the maximum core clock frequency at zero (0) wait state.

Workaround: Two workarounds are available:

- 1. Reduce the device speed to decrease the number of wait states to 0.

- 2. Copy the code from Flash to SRAM at 0 wait states and then run the code out of SRAM.

The issue will be corrected in the next device revision, Marketing Revision Level B (MRL B). Please contact your local Sales Representative for further details.

| 12. | ARM          | Cortex-M4 Processor                         | 55    |

|-----|--------------|---------------------------------------------|-------|

|     | 12.1         | Description                                 | 55    |

|     | 12.2         | Embedded Characteristics                    | 56    |

|     | 12.3         | Block Diagram                               | 56    |

|     | 12.4         | Cortex-M4 Models                            | 57    |

|     | 12.5         | Power Management                            |       |

|     | 12.6         | Cortex-M4 Instruction Set                   |       |

|     | 12.7         | Cortex-M4 Core Peripherals                  |       |

|     | 12.8         | Nested Vectored Interrupt Controller (NVIC) |       |

|     | 12.9         | System Control Block (SCB)                  |       |

|     |              | System Timer (SysTick)                      |       |

|     | 12.11        |                                             |       |

|     | 12.12        | Glossary                                    | . 262 |

| 13. | Debu         | ug and Test Features                        | . 267 |

|     | 13.1         | Description                                 |       |

|     | 13.2         | Embedded Characteristics                    |       |

|     | 13.3         | Application Examples                        |       |

|     | 13.4         | Debug and Test Pin Description              | . 269 |

|     | 13.5         | Functional Description                      | . 270 |

|     | _            | ( O ( U (DOTO)                              |       |

| 14. |              | et Controller (RSTC)                        |       |

|     | 14.1         | Description                                 |       |

|     | 14.2         | Embedded Characteristics                    |       |

|     | 14.3         | Block Diagram                               |       |

|     | 14.4<br>14.5 | Functional Description                      |       |

|     | 14.5         | reset Controller (NOTC) Oser Interface      | . 201 |

| 15. | Real         | -time Timer (RTT)                           | . 285 |

|     | 15.1         | Description                                 | . 285 |

|     | 15.2         | Embedded Characteristics                    | . 285 |

|     | 15.3         | Block Diagram                               | . 285 |

|     | 15.4         | Functional Description                      | . 286 |

|     | 15.5         | Real-time Timer (RTT) User Interface        | . 288 |

| 16  | <b>Dool</b>  | -time Clock (RTC)                           | 202   |

| 10. |              | Description                                 |       |

|     | 16.1<br>16.2 | Embedded Characteristics                    |       |

|     | 16.3         | Block Diagram                               |       |

|     | 16.4         | Product Dependencies                        |       |

|     | 16.5         | Functional Description.                     |       |

|     | 16.6         | Real-time Clock (RTC) User Interface        |       |

|     |              |                                             |       |

| 17. | Wato         | chdog Timer (WDT)                           |       |

|     | 17.1         | Description                                 | . 319 |

|     | 17.2         | Embedded Characteristics                    |       |

|     | 17.3         | Block Diagram                               |       |

|     | 17.4         | Functional Description                      |       |

|     | 17.5         | Watchdog Timer (WDT) User Interface         | . 323 |

| 18  | Sunr         | oly Controller (SUPC)                       | 329   |

|     |              | Description                                 |       |