Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 120MHz                                                                   |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, Memory Card, SPI, SSC, UART/USART, USB  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                               |

| Number of I/O              | 79                                                                       |

| Program Memory Size        | 512KB (512K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | ·                                                                        |

| RAM Size                   | 128K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                             |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                    |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 100-VFBGA                                                                |

| Supplier Device Package    | 100-VFBGA (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4s8ca-cfn |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

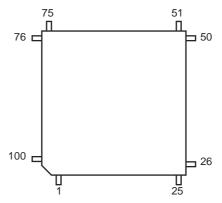

# 4. Package and Pinout

SAM4S devices are pin-to-pin compatible with SAM3N, SAM3S products in 48-, 64- and 100-pin versions, SAM4N and SAM7S legacy products in 64-pin versions.

# 4.1 100-lead Packages and Pinouts

Refer to Table 1-1 and Table 1-2 for the overview of devices available in 100-lead packages.

# 4.1.1 100-lead LQFP Package Outline

## Figure 4-1. Orientation of the 100-lead LQFP Package

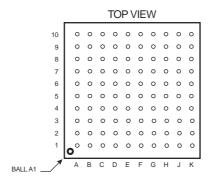

# 4.1.2 100-ball TFBGA Package Outline

The 100-ball TFBGA package has a 0.8 mm ball pitch and respects Green Standards. Its dimensions are 9 x 9 x 1.1 mm. Figure 4-2 shows the orientation of the 100-ball TFBGA package.

### Figure 4-2. Orientation of the 100-ball TFBGA Package

# 12.6.6.6 SMLSD and SMLSLD

# Signed Multiply Subtract Dual and Signed Multiply Subtract Long Dual

Syntax

$op{X}{cond} Rd, Rn, Rm, Ra$

where:

| ор     | is one of:                                                                                                                                                                         |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | SMLSD Signed Multiply Subtract Dual.                                                                                                                                               |

|        | SMLSDX Signed Multiply Subtract Dual Reversed.                                                                                                                                     |

|        | SMLSLD Signed Multiply Subtract Long Dual.                                                                                                                                         |

|        | SMLSLDX Signed Multiply Subtract Long Dual Reversed.                                                                                                                               |

|        | SMLAW Signed Multiply Accumulate (word by halfword).                                                                                                                               |

|        | If X is present, the multiplications are bottom $\times$ top and top $\times$ bottom.<br>If the X is omitted, the multiplications are bottom $\times$ bottom and top $\times$ top. |

| cond   | is an optional condition code, see "Conditional Execution".                                                                                                                        |

| Rd     | is the destination register.                                                                                                                                                       |

| Rn, Rm | are registers holding the first and second operands.                                                                                                                               |

| De     | is the register holding the accumulate value                                                                                                                                       |

Ra is the register holding the accumulate value.

# Operation

The SMLSD instruction interprets the values from the first and second operands as four signed halfwords. This instruction:

- Optionally rotates the halfwords of the second operand.

- Performs two signed 16 x 16-bit halfword multiplications.

- Subtracts the result of the upper halfword multiplication from the result of the lower halfword multiplication.

- Adds the signed accumulate value to the result of the subtraction.

- Writes the result of the addition to the destination register.

The SMLSLD instruction interprets the values from *Rn* and *Rm* as four signed halfwords.

This instruction:

- Optionally rotates the halfwords of the second operand.

- Performs two signed 16 × 16-bit halfword multiplications.

- Subtracts the result of the upper halfword multiplication from the result of the lower halfword multiplication.

- Adds the 64-bit value in *RdHi* and *RdLo* to the result of the subtraction.

- Writes the 64-bit result of the addition to the *RdHi* and *RdLo*.

# Restrictions

In these instructions:

• Do not use SP and do not use PC.

# **Condition Flags**

This instruction sets the Q flag if the accumulate operation overflows. Overflow cannot occur during the multiplications or subtraction.

For the Thumb instruction set, these instructions do not affect the condition code flags.

Examples

SMLSD R0, R4, R5, R6 ; Multiplies bottom halfword of R4 with bottom ; halfword of R5, multiplies top halfword of R4

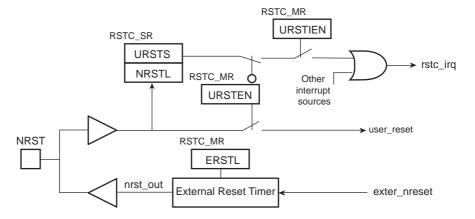

# 14.4 Functional Description

# 14.4.1 Reset Controller Overview

The Reset Controller is made up of an NRST manager and a reset state manager. It runs at slow clock and generates the following reset signals:

- proc\_nreset: processor reset line (also resets the Watchdog Timer)

- periph\_nreset: affects the whole set of embedded peripherals

- nrst\_out: drives the NRST pin

These reset signals are asserted by the Reset Controller, either on events generated by peripherals, events on NRST pin, or on software action. The reset state manager controls the generation of reset signals and provides a signal to the NRST manager when an assertion of the NRST pin is required.

The NRST manager shapes the NRST assertion during a programmable time, thus controlling external device resets.

The Reset Controller Mode Register (RSTC\_MR), used to configure the Reset Controller, is powered with VDDIO, so that its configuration is saved as long as VDDIO is on.

### 14.4.2 NRST Manager

The NRST manager samples the NRST input pin and drives this pin low when required by the reset state manager. Figure 14-2 shows the block diagram of the NRST manager.

### Figure 14-2. NRST Manager

## 14.4.2.1 NRST Signal or Interrupt

The NRST manager samples the NRST pin at slow clock speed. When the line is detected low, a User Reset is reported to the reset state manager.

However, the NRST manager can be programmed to not trigger a reset when an assertion of NRST occurs. Writing a 0 to the URSTEN bit in the RSTC\_MR disables the User Reset trigger.

The level of the pin NRST can be read at any time in the bit NRSTL (NRST level) in the Reset Controller Status Register (RSTC\_SR). As soon as the NRST pin is asserted, bit URSTS in the RSTC\_SR is set. This bit is cleared only when the RSTC\_SR is read.

The Reset Controller can also be programmed to generate an interrupt instead of generating a reset. To do so, set the URSTIEN bit in the RSTC\_MR.

Atmel

# 15.5.4 Real-time Timer Status Register

| Name:<br>Address: | RTT_SR<br>0x400E143C |    |    |    |    |        |      |

|-------------------|----------------------|----|----|----|----|--------|------|

| Access:           | Read-only            |    |    |    |    |        |      |

| 31                | 30                   | 29 | 28 | 27 | 26 | 25     | 24   |

| —                 | -                    | -  | -  | -  | -  | _      | _    |

| 23                | 22                   | 21 | 20 | 19 | 18 | 17     | 16   |

| -                 | -                    | -  | -  | -  | -  | -      | -    |

| 15                | 14                   | 13 | 12 | 11 | 10 | 9      | 8    |

| _                 | -                    | —  | —  | —  | _  | _      | -    |

| 7                 | 6                    | 5  | 4  | 3  | 2  | 1      | 0    |

| -                 | -                    | _  | -  | -  | -  | RTTINC | ALMS |

# • ALMS: Real-time Alarm Status (cleared on read)

0: The Real-time Alarm has not occurred since the last read of RTT\_SR.

1: The Real-time Alarm occurred since the last read of RTT\_SR.

# • RTTINC: Prescaler Roll-over Status (cleared on read)

- 0: No prescaler roll-over occurred since the last read of the RTT\_SR.

- 1: Prescaler roll-over occurred since the last read of the RTT\_SR.

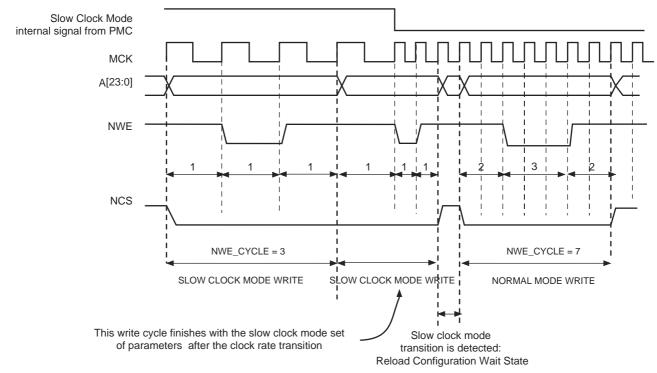

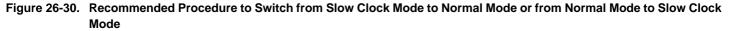

# 26.14.2 Switching from (to) Slow Clock Mode to (from) Normal Mode

When switching from Slow clock mode to Normal mode, the current Slow clock mode transfer is completed at high clock rate, with the set of Slow clock mode parameters. See Figure 26-29. The external device may not be fast enough to support such timings.

Figure 26-30 illustrates the recommended procedure to properly switch from one mode to the other.

#### Figure 26-29. Clock Rate Transition Occurs while the SMC is Performing a Write Operation

Atmel

# 26.16.3 SMC Cycle Register

|          | e e y e le meglenel |              |                |               |        |    |           |  |

|----------|---------------------|--------------|----------------|---------------|--------|----|-----------|--|

| Name:    | SMC_CYCLE[03]       |              |                |               |        |    |           |  |

| Address: | 0x400E0008 [0],     | 0x400E0018 [ | 1], 0x400E0028 | [2], 0x400E00 | 38 [3] |    |           |  |

| Access:  | Read/Write          |              |                |               |        |    |           |  |

| 31       | 30                  | 29           | 28             | 27            | 26     | 25 | 24        |  |

| -        | -                   | —            | —              | —             | —      | -  | NRD_CYCLE |  |

| 23       | 22                  | 21           | 20             | 19            | 18     | 17 | 16        |  |

|          |                     |              | NRD_           | CYCLE         |        |    |           |  |

| 15       | 14                  | 13           | 12             | 11            | 10     | 9  | 8         |  |

| -        | -                   | -            | -              | -             | -      | Ι  | NWE_CYCLE |  |

| 7        | 6                   | 5            | 4              | 3             | 2      | 1  | 0         |  |

|          |                     |              | NWE_           | CYCLE         |        |    |           |  |

This register can only be written if the WPEN bit is cleared in the "SMC Write Protection Mode Register" .

# • NWE\_CYCLE: Total Write Cycle Length

The total write cycle length is the total duration in clock cycles of the write cycle. It is equal to the sum of the setup, pulse and hold steps of the NWE and NCS signals. It is defined as:

Write cycle length = (NWE\_CYCLE[8:7]\*256 + NWE\_CYCLE[6:0]) clock cycles

# • NRD\_CYCLE: Total Read Cycle Length

The total read cycle length is the total duration in clock cycles of the read cycle. It is equal to the sum of the setup, pulse and hold steps of the NRD and NCS signals. It is defined as:

Read cycle length = (NRD\_CYCLE[8:7]\*256 + NRD\_CYCLE[6:0]) clock cycles

#### 26.16.7 SMC OCMS Key2 Register Name: SMC\_KEY2 Address: 0x400E0088 Access: Write Once KEY2 KEY2 KEY2 KEY2

# • KEY2: Off Chip Memory Scrambling (OCMS) Key Part 2

When off-chip memory scrambling is enabled, setting the SMC\_OCMS and SMC\_TIMINGS registers in accordance, the data scrambling depends on KEY2 and KEY1 values.

# 27.6.3 Transmit Pointer Register

| Name:   | PERIPH_TPR |    |     |     |    |    |    |

|---------|------------|----|-----|-----|----|----|----|

| Access: | Read/Write |    |     |     |    |    |    |

| 31      | 30         | 29 | 28  | 27  | 26 | 25 | 24 |

|         |            |    | TXF | ۲R  |    |    |    |

| 23      | 22         | 21 | 20  | 19  | 18 | 17 | 16 |

|         |            |    | TXF | ۲R  |    |    |    |

| 15      | 14         | 13 | 12  | 11  | 10 | 9  | 8  |

|         |            |    | TXF | PTR |    |    |    |

| 7       | 6          | 5  | 4   | 3   | 2  | 1  | 0  |

|         |            |    | TXF | ۲R  |    |    |    |

# • TXPTR: Transmit Counter Register

TXPTR must be set to transmit buffer address.

When a half-duplex peripheral is connected to the PDC, RXPTR = TXPTR.

# 31. Parallel Input/Output Controller (PIO)

# 31.1 Description

The Parallel Input/Output Controller (PIO) manages up to 32 fully programmable input/output lines. Each I/O line may be dedicated as a general-purpose I/O or be assigned to a function of an embedded peripheral. This ensures effective optimization of the pins of the product.

Each I/O line is associated with a bit number in all of the 32-bit registers of the 32-bit wide user interface.

Each I/O line of the PIO Controller features:

- An input change interrupt enabling level change detection on any I/O line.

- Additional Interrupt modes enabling rising edge, falling edge, low-level or high-level detection on any I/O line.

- A glitch filter providing rejection of glitches lower than one-half of peripheral clock cycle.

- A debouncing filter providing rejection of unwanted pulses from key or push button operations.

- Multi-drive capability similar to an open drain I/O line.

- Control of the pull-up and pull-down of the I/O line.

- Input visibility and output control.

The PIO Controller also features a synchronous output providing up to 32 bits of data output in a single write operation.

An 8-bit parallel capture mode is also available which can be used to interface a CMOS digital image sensor, an ADC, a DSP synchronous port in synchronous mode, etc.

# 31.6.23 PIO Pull-Up Status Register

| Name:    | PIO_PUSR      |               |                 |               |     |     |     |

|----------|---------------|---------------|-----------------|---------------|-----|-----|-----|

| Address: | 0x400E0E68 (P | IOA), 0x400E1 | 068 (PIOB), 0x4 | 100E1268 (PIO | C)  |     |     |

| Access:  | Read-only     |               |                 |               |     |     |     |

| 31       | 30            | 29            | 28              | 27            | 26  | 25  | 24  |

| P31      | P30           | P29           | P28             | P27           | P26 | P25 | P24 |

| 23       | 22            | 21            | 20              | 19            | 18  | 17  | 16  |

| P23      | P22           | P21           | P20             | P19           | P18 | P17 | P16 |

| 15       | 14            | 13            | 12              | 11            | 10  | 9   | 8   |

| P15      | P14           | P13           | P12             | P11           | P10 | P9  | P8  |

| 7        | 6             | 5             | 4               | 3             | 2   | 1   | 0   |

| P7       | P6            | P5            | P4              | P3            | P2  | P1  | P0  |

# • P0-P31: Pull-Up Status

0: Pull-up resistor is enabled on the I/O line.

1: Pull-up resistor is disabled on the I/O line.

# 33.2 Embedded Characteristics

- Master or Slave Serial Peripheral Bus Interface

- 8-bit to 16-bit programmable data length per chip select

- Programmable phase and polarity per chip select

- Programmable transfer delay between consecutive transfers and delay before SPI clock per chip select

- Programmable delay between chip selects

- Selectable mode fault detection

- Master Mode can drive SPCK up to Peripheral Clock

- Master Mode Bit Rate can be Independent of the Processor/Peripheral Clock

- Slave mode operates on SPCK, asynchronously with core and bus clock

- Four chip selects with external decoder support allow communication with up to 15 peripherals

- Communication with Serial External Devices Supported

- Serial memories, such as DataFlash and 3-wire EEPROMs

- Serial peripherals, such as ADCs, DACs, LCD controllers, CAN controllers and sensors

- External coprocessors

- Connection to PDC Channel Capabilities, Optimizing Data Transfers

- One channel for the receiver

- One channel for the transmitter

- Register Write Protection

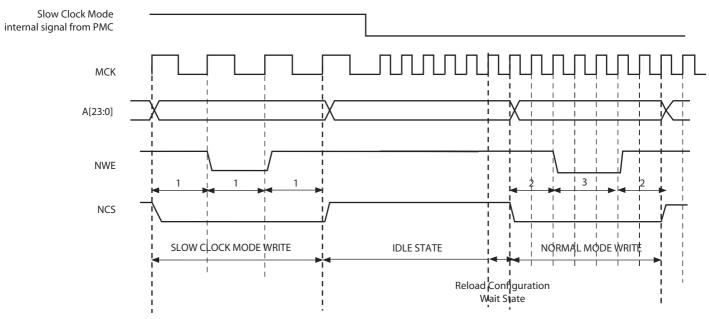

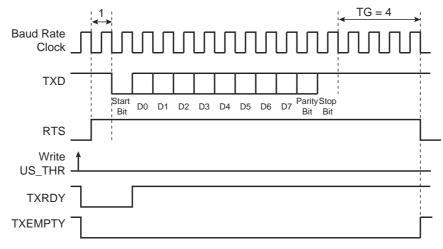

Figure 36-35. Typical Connection to a RS485 Bus

The USART is set in RS485 mode by writing the value 0x1 to the USART\_MODE field in US\_MR.

The RTS pin is at a level inverse to the TXEMPTY bit. Significantly, the RTS pin remains high when a timeguard is programmed so that the line can remain driven after the last character completion. Figure 36-36 gives an example of the RTS waveform during a character transmission when the timeguard is enabled.

## 38.8.4 Write Operation

In write operation, the HSMCI Mode Register (HSMCI\_MR) is used to define the padding value when writing nonmultiple block size. If the bit PADV is 0, then 0x00 value is used when padding data, otherwise 0xFF is used.

If set, the bit PDCMODE enables PDC transfer.

The flowchart in Figure 38-9 shows how to write a single block with or without use of PDC facilities. Polling or interrupt method can be used to wait for the end of write according to the contents of the HSMCI Interrupt Mask Register (HSMCI\_IMR).

of the channel 0 is center-aligned (CALG = 1 in PWM Channel Mode Register), the bit CVM in PWM\_CMPVx defines if the comparison is made when the counter is counting up or counting down (in Left-alignment mode CALG = 0, this bit is useless).

If a fault is active on the channel 0, the comparison is disabled and cannot match (see Section 39.6.2.6 "Fault Protection").

The user can define the periodicity of the comparison x by the fields CTR and CPR in PWM\_CMPMx. The comparison is performed periodically once every CPR+1 periods of the counter of the channel 0, when the value of the comparison period counter CPRCNT in PWM\_CMPMx reaches the value defined by CTR. CPR is the maximum value of the comparison period counter CPRCNT. If CPR = CTR = 0, the comparison is performed at each period of the counter of the channel 0.

The comparison x configuration can be modified while the channel 0 is enabled by using the PWM Comparison x Mode Update Register (PWM\_CMPMUPDx registers for the comparison x). In the same way, the comparison x value can be modified while the channel 0 is enabled by using the PWM Comparison x Value Update Register (PWM\_CMPVUPDx registers for the comparison x).

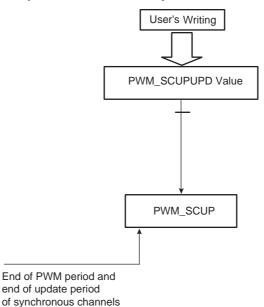

The update of the comparison x configuration and the comparison x value is triggered periodically after the comparison x update period. It is defined by the field CUPR in the PWM\_CMPMx. The comparison unit has an update period counter independent from the period counter to trigger this update. When the value of the comparison update period counter CUPRCNT (in PWM\_CMPMx) reaches the value defined by CUPR, the update is triggered. The comparison x update period CUPR itself can be updated while the channel 0 is enabled by using the PWM\_CMPMUPDx register.

**<u>CAUTION</u>**: The write of PWM\_CMPVUPDx must be followed by a write of PWM\_CMPMUPDx.

The comparison match and the comparison update can be source of an interrupt, but only if it is enabled and not masked. These interrupts can be enabled by the PWM Interrupt Enable Register 2 and disabled by the PWM Interrupt Disable Register 2. The comparison match interrupt and the comparison update interrupt are reset by reading the PWM Interrupt Status Register 2.

Figure 39-19. Synchronized Update of Update Period Value of Synchronous Channels

# 39.6.5.5 Changing the Comparison Value and the Comparison Configuration

It is possible to change the comparison values and the comparison configurations while the channel 0 is enabled (see Section 39.6.3 "PWM Comparison Units").

To prevent unexpected comparison match, the user must use the PWM Comparison x Value Update Register (PWM\_CMPVUPDx) and the PWM Comparison x Mode Update Register (PWM\_CMPMUPDx) to change, respectively, the comparison values and the comparison configurations while the channel 0 is still enabled. These registers hold the new values until the end of the comparison update period (when CUPRCNT is equal to CUPR in PWM Comparison x Mode Register (PWM\_CMPMx) and the end of the current PWM period, then update the values for the next period.

**<u>CAUTION</u>**: The write of the register PWM\_CMPVUPDx must be followed by a write of the register PWM\_CMPMUPDx.

Note: If the update registers PWM\_CMPVUPDx and PWM\_CMPMUPDx are written several times between two updates, only the last written value are taken into account.

# 39.7 Pulse Width Modulation Controller (PWM) User Interface

| Offset    | Register                                        | Name        | Access     | Reset |

|-----------|-------------------------------------------------|-------------|------------|-------|

| 0x00      | PWM Clock Register                              | PWM_CLK     | Read/Write | 0x0   |

| 0x04      | PWM Enable Register                             | PWM_ENA     | Write-only | _     |

| 0x08      | PWM Disable Register                            | PWM_DIS     | Write-only | _     |

| 0x0C      | PWM Status Register                             | PWM_SR      | Read-only  | 0x0   |

| 0x10      | PWM Interrupt Enable Register 1                 | PWM_IER1    | Write-only | _     |

| 0x14      | PWM Interrupt Disable Register 1                | PWM_IDR1    | Write-only | _     |

| 0x18      | PWM Interrupt Mask Register 1                   | PWM_IMR1    | Read-only  | 0x0   |

| 0x1C      | PWM Interrupt Status Register 1                 | PWM_ISR1    | Read-only  | 0x0   |

| 0x20      | PWM Sync Channels Mode Register                 | PWM_SCM     | Read/Write | 0x0   |

| 0x24      | Reserved                                        | -           | -          | _     |

| 0x28      | PWM Sync Channels Update Control Register       | PWM_SCUC    | Read/Write | 0x0   |

| 0x2C      | PWM Sync Channels Update Period Register        | PWM_SCUP    | Read/Write | 0x0   |

| 0x30      | PWM Sync Channels Update Period Update Register | PWM_SCUPUPD | Write-only | _     |

| 0x34      | PWM Interrupt Enable Register 2                 | PWM_IER2    | Write-only | _     |

| 0x38      | PWM Interrupt Disable Register 2                | PWM_IDR2    | Write-only | _     |

| 0x3C      | PWM Interrupt Mask Register 2                   | PWM_IMR2    | Read-only  | 0x0   |

| 0x40      | PWM Interrupt Status Register 2                 | PWM_ISR2    | Read-only  | 0x0   |

| 0x44      | PWM Output Override Value Register              | PWM_OOV     | Read/Write | 0x0   |

| 0x48      | PWM Output Selection Register                   | PWM_OS      | Read/Write | 0x0   |

| 0x4C      | PWM Output Selection Set Register               | PWM_OSS     | Write-only | _     |

| 0x50      | PWM Output Selection Clear Register             | PWM_OSC     | Write-only | _     |

| 0x54      | PWM Output Selection Set Update Register        | PWM_OSSUPD  | Write-only | _     |

| 0x58      | PWM Output Selection Clear Update Register      | PWM_OSCUPD  | Write-only | _     |

| 0x5C      | PWM Fault Mode Register                         | PWM_FMR     | Read/Write | 0x0   |

| 0x60      | PWM Fault Status Register                       | PWM_FSR     | Read-only  | 0x0   |

| 0x64      | PWM Fault Clear Register                        | PWM_FCR     | Write-only | _     |

| 0x68      | PWM Fault Protection Value Register             | PWM_FPV     | Read/Write | 0x0   |

| 0x6C      | PWM Fault Protection Enable Register            | PWM_FPE     | Read/Write | 0x0   |

| 0x70–0x78 | Reserved                                        | _           | -          | _     |

| 0x7C      | PWM Event Line 0 Mode Register                  | PWM_ELMR0   | Read/Write | 0x0   |

| 0x80      | PWM Event Line 1 Mode Register                  | PWM_ELMR1   | Read/Write | 0x0   |

| 0x84–0x9C | Reserved                                        | _           | _          | _     |

| 0xA0–0xAC | Reserved                                        | -           | -          | _     |

| 0xB0      | PWM Stepper Motor Mode Register                 | PWM_SMMR    | Read/Write | 0x0   |

| 0xB4–0xBC | Reserved                                        | _           | _          | _     |

## Table 39-6.Register Mapping

## 40.6.3.7 Receiving a Host Resume

In suspend mode, a resume event on the USB bus line is detected asynchronously, transceiver and clocks are disabled (however the pull-up shall not be removed).

Once the resume is detected on the bus, the WAKEUP signal in the UDP\_ISR is set. It may generate an interrupt if the corresponding bit in the UDP\_IMR is set. This interrupt may be used to wake up the core, enable PLL and main oscillators and configure clocks.

**Warning**: Read, write operations to the UDP registers are allowed only if MCK is enabled for the UDP peripheral. MCK for the UDP must be enabled before clearing the WAKEUP bit in the UDP\_ICR and clearing TXVDIS in the UDP\_TXVC register.

# 40.6.3.8 Sending a Device Remote Wakeup Request

In Suspend state it is possible to wake up the host sending an external resume.

- The device must wait at least 5 ms after being entered in suspend before sending an external resume.

- The device has 10 ms from the moment it starts to drain current and it forces a K state to resume the host.

- The device must force a K state from 1 to 15 ms to resume the host

Before sending a K state to the host, MCK, UDPCK and the transceiver must be enabled. Then to enable the remote wakeup feature, the RMWUPE bit in the UDP\_GLB\_STAT register must be enabled. To force the K state on the line, a transition of the ESR bit from 0 to 1 has to be done in the UDP\_GLB\_STAT register by first writing a 0 in the ESR bit and then writing a 1.

The K state is automatically generated and released according to the USB 2.0 specification.

Atmel

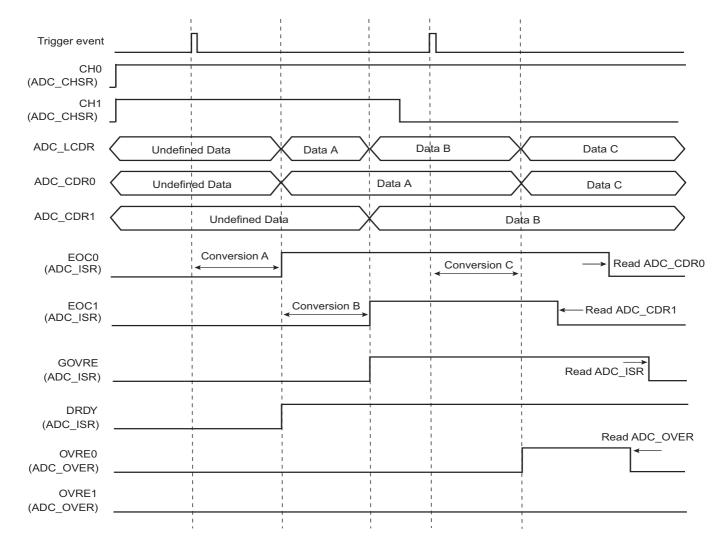

The OVREx flag is automatically cleared when ADC\_OVER is read, and the GOVRE flag is automatically cleared when ADC\_ISR is read.

Figure 42-5. EOCx, OVREx and GOVREx Flag Behavior

**Warning:** If the corresponding channel is disabled during a conversion or if it is disabled and then reenabled during a conversion, its associated data and corresponding EOCx and GOVRE flags in ADC\_ISR and OVREx flags in ADC\_OVER are unpredictable.

Atmel

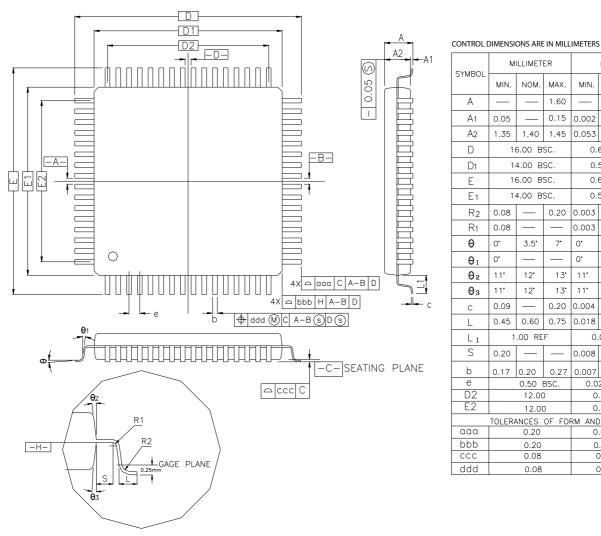

#### 45. **Mechanical Characteristics**

All packages of the SAM4S devices respect the recommendations of the NEMI User Group.

#### 45.1 **100-lead LQFP Mechanical Characteristics**

#### Figure 45-1. 100-lead LQFP Package Mechanical Drawing

| CONTROL DIMENSIONS ARE IN MILLIMETERS |             |         |       |           |        |       |  |

|---------------------------------------|-------------|---------|-------|-----------|--------|-------|--|

| SYMBOL                                | М           | ILLIMET | ER    | INCH      |        |       |  |

| STMBUL                                | MIN.        | NOM.    | MAX.  | MIN.      | NOM.   | MAX.  |  |

| A                                     | —           | _       | 1.60  | —         | —      | 0.063 |  |

| A1                                    | 0.05        |         | 0.15  | 0.002     |        | 0.006 |  |

| A2                                    | 1.35        | 1.40    | 1.45  | 0.053     | 0.055  | 0.057 |  |

| D                                     | 10          | 6.00 B  | SC.   | 0.        | 630 BS | SC.   |  |

| D1                                    | 1.          | 4.00 B  | SC.   | 0.        | 551 BS | 5C.   |  |

| E                                     | 10          | 6.00 B  | SC.   | 0.        | 630 BS | SC.   |  |

| E1                                    | 1.          | 4.00 B  | SC.   | 0.        | 551 BS | SC.   |  |

| R2                                    | 0.08        | —       | 0.20  | 0.003     | —      | 0.008 |  |

| R1                                    | 0.08        | —       |       | 0.003     | —      | —     |  |

| θ                                     | 0*          | 3.5*    | 7•    | 0.        | 3.5*   | 7*    |  |

| θ1                                    | 0*          | _       |       | 0*        | —      |       |  |

| θε                                    | 11.         | 12*     | 1.3°  | 11°       | 12*    | 1.3°  |  |

| θз                                    | 11*         | 12*     | 13*   | 11*       | 12*    | 13*   |  |

| С                                     | 0.09        | —       | 0.20  | 0.004     | —      | 0.008 |  |

| L                                     | 0.45        | 0.60    | 0.75  | 0.018     | 0.024  | 0.030 |  |

| L <sub>1</sub>                        | 1           | .00 RE  | F     | 0.039 REF |        |       |  |

| S                                     | 0.20        | —       |       | 0.008     | —      |       |  |

| b                                     | 0.17        | 0.20    | 0.27  | 0.007     | 0.008  | 0.011 |  |

| е                                     |             | 0.50    | BSC.  | 0.0       | 20 BS( | c.    |  |

| D2                                    |             | 12.00   | )     | 0         | .472   |       |  |

| E2                                    | 12.00 0.472 |         |       |           |        |       |  |

|                                       | TOLERA      | ANCES   | OF FO | RM AND    | POSI   | ION   |  |

| aaa                                   |             | 0.20    |       | 0         | .008   |       |  |

| bbb                                   |             | 0.20    |       | 0         | .008   |       |  |

| ссс                                   |             | 0.08    |       | 0         | 0.003  |       |  |

| ddd                                   |             | 0.08    |       |           | 0.003  |       |  |

Note: 1. This drawing is for general information only. Refer to JEDEC Drawing MS-026 for additional information.

#### Table 45-1. **Device and LQFP Package Maximum Weight**

| SAM4S                   |                   | 800    | mg |  |

|-------------------------|-------------------|--------|----|--|

| Table 45-2.             | Package Reference |        |    |  |

| JEDEC Drawing Reference |                   | MS-026 |    |  |

| JESD97 Classification   |                   | e3     |    |  |

# Table 49-6. SAM4S Datasheet Rev. 11100F 29-Jan-14 Revision History (Continued)

| Doc. Date | Changes                                                                                                                                                                                                                                                                                                                                                                       |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | Section 16. "Real-time Clock (RTC)"                                                                                                                                                                                                                                                                                                                                           |

|           | Section 16.1 "Description": updated to explain need for accurate external 32.768 kHz clock                                                                                                                                                                                                                                                                                    |

|           | Section 16.2 "Embedded Characteristics": added feature "Write-Protected Registers"                                                                                                                                                                                                                                                                                            |

|           | Section 16.5.6 "Updating Time/Calendar": reworded second paragraph for clarity                                                                                                                                                                                                                                                                                                |

|           | Section 16.5.7 "RTC Accurate Clock Calibration": replaced sentence "The period interval between 2 correction events is programmable in order to cover the possible crystal oscillator clock variations" with "According to the CORRECTION, NEGPPM and HIGHPPM values configured in the RTC Mode Register (RTC_MR), the period interval between two correction events differs" |

|           | Section 16.6.1 "RTC Control Register", Section 16.6.2 "RTC Mode Register", Section 16.6.5 "RTC Time Alarm Register", Section 16.6.6 "RTC Calendar Alarm Register": added sentence "This register can only be written if the WPEN bit is cleared in the System Controller Write Protection Mode Register (SYSC_WPMR)" and updated description of UPDCAL bit                    |

|           | Section 16.6.2 "RTC Mode Register": corrected typo (THIGH value 2 description now reads "3.91 ms")                                                                                                                                                                                                                                                                            |

|           | Section 18. "Supply Controller (SUPC)"                                                                                                                                                                                                                                                                                                                                        |

|           | Section 18.1 "Embedded Characteristics": added bullets on tamper detection and on anti-tampering.                                                                                                                                                                                                                                                                             |

|           | Figure 18-1 "Supply Controller Block Diagram" modified.                                                                                                                                                                                                                                                                                                                       |

|           | Section 18.3.4 "Supply Monitor": Supply Monitor sampling mode, power reduction factor: replaced incorrect values of 32, 256 or 2048 by the correct values of 2, 16 and 128.                                                                                                                                                                                                   |

|           | Section 18.3.6.2 "Brownout Detector Reset": Reworked 1st paragraph for clarity                                                                                                                                                                                                                                                                                                |

|           | Section 18.3.7.1 "Wake-up Inputs": corrected WKUPPLx pins to WKUPTx pins. WKUP0, WKUP15 references changed to WKUPx.                                                                                                                                                                                                                                                          |

|           | Figure 18-4 "Wake-up Sources": Defined a section of the graphic as Low-power Tamper Detection Logic.                                                                                                                                                                                                                                                                          |

|           | Section 18.3.7.2 "Low-power Tamper Detection and Anti-Tampering": Changed all references to RTCOUT1 and RTCOUT 0 to RTCOUTx. Other minor modifications to improve clarity.                                                                                                                                                                                                    |

|           | Figure 18-5 "Low-power Debouncer (Push-to-Make Switch, Pull-up Resistors)", Figure 18-6 "Low-power Debouncer (Push-to-Break Switch, Pull-down Resistors)", Figure 18-7 "Using WKUP Pins Without RTCOUTx Pins": Modified pin names.                                                                                                                                            |

|           | Added Section 18.3.8 "Register Write Protection". In Section 18.4.9 "System Controller Write Protection Mode Register", updated register name and bit descriptions.                                                                                                                                                                                                           |

|           | Added Section 18.3.9 "Register Bits in Backup Domain (VDDIO)".                                                                                                                                                                                                                                                                                                                |

|           | Section 18.4.3 "Supply Controller Control Register": Added sentence on WPEN bit below register table and added note to descriptions of bits VROFF and XTALSEL indicating the bits are in the backup domain.                                                                                                                                                                   |

|           | Section 18.4.5 "Supply Controller Mode Register": Added sentence on WPEN bit below register table and added note to all bit descriptions except bit KEY indicating the bits are in the backup domain                                                                                                                                                                          |

|           | Section 18.4.4 "Supply Controller Supply Monitor Mode Register", , Section 18.4.6 "Supply Controller Wake-up Mode Register" and Section 18.4.7 "Supply Controller Wake-up Inputs Register": Added sentence on WPEN bit below register table and added a sentence below the register tables stating that the register is located in the backup domain                          |

|           | Section 18.4.7 "Supply Controller Wake-up Inputs Register": corrected register name (was "System Controller Wake-<br>Up Inputs Register")                                                                                                                                                                                                                                     |