Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 120MHz                                                                   |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, Memory Card, SPI, SSC, UART/USART, USB  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                               |

| Number of I/O              | 79                                                                       |

| Program Memory Size        | 512KB (512K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | ·                                                                        |

| RAM Size                   | 128K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                             |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                    |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 100-VFBGA                                                                |

| Supplier Device Package    | 100-VFBGA (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4s8cb-cfn |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 4. Maintain the ERASE pin high for at least the minimum assertion time.

#### 8.1.3.7 Calibration Bits

NVM bits are used to calibrate the brownout detector and the voltage regulator. These bits are factory configured and cannot be changed by the user. The ERASE pin has no effect on the calibration bits.

#### 8.1.3.8 Unique Identifier

Each device integrates its own 128-bit unique identifier. These bits are factory-configured and cannot be changed by the user. The ERASE pin has no effect on the unique identifier.

#### 8.1.3.9 User Signature

Each device contains a user signature of 512 bytes. It can be used by the user to store user information such as trimming, keys, etc., that the customer does not want to be erased by asserting the ERASE pin or by software ERASE command. Read, write and erase of this area is allowed.

#### 8.1.3.10 Fast Flash Programming Interface

The Fast Flash Programming Interface allows programming the device through a multiplexed fully-handshaked parallel port. It allows gang programming with market-standard industrial programmers.

The FFPI supports read, page program, page erase, full erase, lock, unlock and protect commands.

#### 8.1.3.11 SAM-BA Boot

The SAM-BA Boot is a default Boot Program which provides an easy way to program in-situ the on-chip Flash memory.

The SAM-BA Boot Assistant supports serial communication via the UART and USB.

The SAM-BA Boot provides an interface with SAM-BA Graphic User Interface (GUI).

The SAM-BA Boot is in ROM and is mapped in Flash at address 0x0 when GPNVM bit 1 is set to 0.

#### 8.1.3.12 GPNVM Bits

The SAM4S16/S8/S4/S2 feature two GPNVM bits.

The SAM4SA16/SD32/SD16 feature three GPNVM bits, coming from Flash 0, that can be cleared or set, respectively, through the "Clear GPNVM Bit" and "Set GPNVM Bit" commands of the EEFC0 User Interface.

There is no GPNVM bit on Flash 1.

The GPNVM0 is the security bit.

The GPNVM1 is used to select the boot mode (boot always at 0x00) on ROM or Flash.

The SAM4SD32/16 embeds an additional GPNVM bit, GPNVM2. GPNVM2 is used only to swap the Flash 0 and Flash 1. If GPNVM2 is ENABLE, the Flash 1 is mapped at address 0x0040\_0000 (Flash 1 and Flash 0 are

Atmel

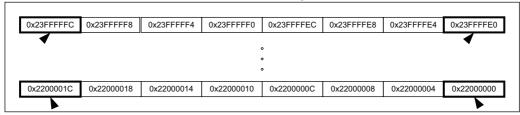

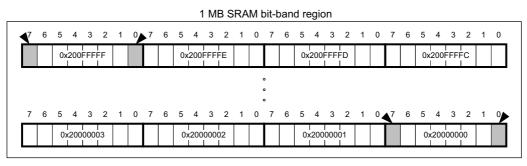

#### Figure 12-4. Bit-band Mapping

32 MB alias region

### Directly Accessing an Alias Region

Writing to a word in the alias region updates a single bit in the bit-band region.

Bit[0] of the value written to a word in the alias region determines the value written to the targeted bit in the bitband region. Writing a value with bit[0] set to 1 writes a 1 to the bit-band bit, and writing a value with bit[0] set to 0 writes a 0 to the bit-band bit.

Bits[31:1] of the alias word have no effect on the bit-band bit. Writing 0x01 has the same effect as writing 0xFF. Writing 0x00 has the same effect as writing 0x0E.

Reading a word in the alias region:

- 0x00000000 indicates that the targeted bit in the bit-band region is set to 0

- 0x00000001 indicates that the targeted bit in the bit-band region is set to 1

#### Directly Accessing a Bit-band Region

"Behavior of Memory Accesses" describes the behavior of direct byte, halfword, or word accesses to the bit-band regions.

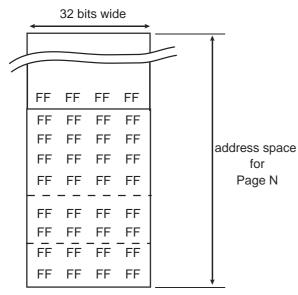

#### 12.4.2.6 Memory Endianness

The processor views memory as a linear collection of bytes numbered in ascending order from zero. For example, bytes 0–3 hold the first stored word, and bytes 4–7 hold the second stored word. "Little-endian Format" describes how words of data are stored in memory.

# Little-endian Format

In little-endian format, the processor stores the least significant byte of a word at the lowest-numbered byte, and the most significant byte at the highest-numbered byte. For example:

Atmel

S is an optional suffix. If S is specified, the condition code flags are updated on the result of the operation, see "Conditional Execution" .

cond is an optional condition code, see "Conditional Execution" .

Rd is the destination register.

Rn is the register holding the first operand.

Operand2 is a flexible second operand. See "Flexible Second Operand" for details of the options.

# Operation

The AND, EOR, and ORR instructions perform bitwise AND, Exclusive OR, and OR operations on the values in *Rn* and *Operand2*.

The BIC instruction performs an AND operation on the bits in *Rn* with the complements of the corresponding bits in the value of *Operand*2.

The ORN instruction performs an OR operation on the bits in *Rn* with the complements of the corresponding bits in the value of *Operand*2.

Restrictions

Do not use SP and do not use PC.

**Condition Flags**

If S is specified, these instructions:

- Update the N and Z flags according to the result

- Can update the C flag during the calculation of *Operand2*, see "Flexible Second Operand"

- Do not affect the V flag.

# 17.4 Functional Description

The Watchdog Timer is used to prevent system lock-up if the software becomes trapped in a deadlock. It is supplied with VDDCORE. It restarts with initial values on processor reset.

The watchdog is built around a 12-bit down counter, which is loaded with the value defined in the field WDV of the Mode Register (WDT\_MR). The Watchdog Timer uses the slow clock divided by 128 to establish the maximum watchdog period to be 16 seconds (with a typical slow clock of 32.768 kHz).

After a processor reset, the value of WDV is 0xFFF, corresponding to the maximum value of the counter with the external reset generation enabled (field WDRSTEN at 1 after a backup reset). This means that a default watchdog is running at reset, i.e., at power-up. The user can either disable the WDT by setting bit WDT\_MR.WDDIS or reprogram the WDT to meet the maximum watchdog period the application requires.

If the watchdog is restarted by writing into the Control Register (WDT\_CR), WDT\_MR must not be programmed during a period of time of three slow clock periods following the WDT\_CR write access. In any case, programming a new value in WDT\_MR automatically initiates a restart instruction.

WDT\_MR can be written only once. Only a processor reset resets it. Writing WDT\_MR reloads the timer with the newly programmed mode parameters.

In normal operation, the user reloads the watchdog at regular intervals before the timer underflow occurs, by setting bit WDT\_CR.WDRSTT. The watchdog counter is then immediately reloaded from WDT\_MR and restarted, and the slow clock 128 divider is reset and restarted. WDT\_CR is write-protected. As a result, writing WDT\_CR without the correct hard-coded key has no effect. If an underflow does occur, the "wdt\_fault" signal to the Reset Controller is asserted if bit WDT\_MR.WDRSTEN is set. Moreover, the bit WDUNF is set in the Status Register (WDT\_SR).

To prevent a software deadlock that continuously triggers the watchdog, the reload of the watchdog must occur while the watchdog counter is within a window between 0 and WDD, WDD is defined in WDT\_MR.

Any attempt to restart the watchdog while the watchdog counter is between WDV and WDD results in a watchdog error, even if the watchdog is disabled. The bit WDT\_SR.WDERR is updated and the "wdt\_fault" signal to the Reset Controller is asserted.

Note that this feature can be disabled by programming a WDD value greater than or equal to the WDV value. In such a configuration, restarting the Watchdog Timer is permitted in the whole range [0; WDV] and does not generate an error. This is the default configuration on reset (the WDD and WDV values are equal).

The status bits WDUNF (Watchdog Underflow) and WDERR (Watchdog Error) trigger an interrupt, provided the bit WDT\_MR.WDFIEN is set. The signal "wdt\_fault" to the Reset Controller causes a watchdog reset if the WDRSTEN bit is set as already explained in the Reset Controller documentation. In this case, the processor and the Watchdog Timer are reset, and the WDERR and WDUNF flags are reset.

If a reset is generated or if WDT\_SR is read, the status bits are reset, the interrupt is cleared, and the "wdt\_fault" signal to the reset controller is deasserted.

Writing WDT\_MR reloads and restarts the down counter.

While the processor is in debug state or in idle mode, the counter may be stopped depending on the value programmed for the bits WDIDLEHLT and WDDBGHLT in WDT\_MR.

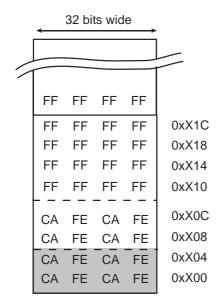

Step 1: Flash array after page erase

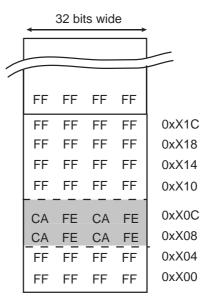

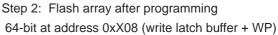

Step 3: Flash array after programming a second 64-bit data at address 0xX00 (write latch buffer + WP)

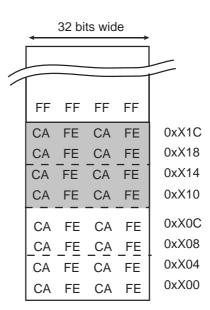

Step 4: Flash array after programming a 128-bit data word at address 0xX10 (write latch buffer + WP)

# 25.8.5 SMC NAND Flash Chip Select Configuration Register

| Name: CCF     | Name: CCFG_SMCNFCS |    |    |           |           |           |           |  |

|---------------|--------------------|----|----|-----------|-----------|-----------|-----------|--|

| Address: 0x40 | 0E031C             |    |    |           |           |           |           |  |

| Type: Read    | d/Write            |    |    |           |           |           |           |  |

| Reset: 0x00   | 000_000            |    |    |           |           |           |           |  |

| 31            | 30                 | 29 | 28 | 27        | 26        | 25        | 24        |  |

| -             | -                  | -  | -  | -         | -         | -         | -         |  |

|               |                    |    |    |           |           |           |           |  |

| 23            | 22                 | 21 | 20 | 19        | 18        | 17        | 16        |  |

| -             | -                  | _  | -  | -         | -         | -         | -         |  |

|               |                    |    |    |           |           |           |           |  |

| 15            | 14                 | 13 | 12 | 11        | 10        | 9         | 8         |  |

| -             | -                  | -  | -  | -         | _         | _         | -         |  |

|               |                    |    |    |           |           |           |           |  |

| 7             | 6                  | 5  | 4  | 3         | 2         | 1         | 0         |  |

| -             | -                  | _  | _  | SMC_NFCS3 | SMC_NFCS2 | SMC_NFCS1 | SMC_NFCS0 |  |

# • SMC\_NFCS0: SMC NAND Flash Chip Select 0 Assignment

0: NCS0 is not assigned to a NAND Flash (NANDOE and NANWE not used for NCS0)

1: NCS0 is assigned to a NAND Flash (NANDOE and NANWE used for NCS0)

# SMC\_NFCS1: SMC NAND Flash Chip Select 1 Assignment

0: NCS1 is not assigned to a NAND Flash (NANDOE and NANWE not used for NCS1)1: NCS1 is assigned to a NAND Flash (NANDOE and NANWE used for NCS1)

# • SMC\_NFCS2: SMC NAND Flash Chip Select 2 Assignment

0: NCS2 is not assigned to a NAND Flash (NANDOE and NANWE not used for NCS2)

1: NCS2 is assigned to a NAND Flash (NANDOE and NANWE used for NCS2)

# • SMC\_NFCS3: SMC NAND Flash Chip Select 3 Assignment

0: NCS3 is not assigned to a NAND Flash (NANDOE and NANWE not used for NCS3)

1: NCS3 is assigned to a NAND Flash (NANDOE and NANWE used for NCS3)

# 29.17.14PMC Interrupt Enable Register

| Name:<br>Address: | PMC_IER<br>0x400E0460 |    |    |        |               |               |                |

|-------------------|-----------------------|----|----|--------|---------------|---------------|----------------|

| Access:           | Write-only            |    |    |        |               |               |                |

| 31                | 30                    | 29 | 28 | 27     | 26            | 25            | 24             |

| _                 | —                     | —  | —  | —      | —             | —             | —              |

| 23                | 22                    | 21 | 20 | 19     | 18<br>CFDEV   | 17<br>MOSCRCS | 16<br>MOSCSELS |

| 15                | 14                    | 13 | 12 | 11     | 10<br>PCKRDY2 | 9<br>PCKRDY1  | 8<br>PCKRDY0   |

| _                 | -                     | _  | -  | -      | PUREDIZ       | FUREDTI       | FUREDIU        |

| 7                 | 6                     | 5  | 4  | 3      | 2             | 1             | 0              |

| _                 | -                     | _  | _  | MCKRDY | LOCKB         | LOCKA         | MOSCXTS        |

The following configuration values are valid for all listed bit names of this register:

0: No effect.

- 1: Enables the corresponding interrupt.

- MOSCXTS: Main Crystal Oscillator Status Interrupt Enable

- LOCKA: PLLA Lock Interrupt Enable

- LOCKB: PLLB Lock Interrupt Enable

- MCKRDY: Master Clock Ready Interrupt Enable

- PCKRDYx: Programmable Clock Ready x Interrupt Enable

- MOSCSELS: Main Oscillator Selection Status Interrupt Enable

- MOSCRCS: Main On-Chip RC Status Interrupt Enable

- CFDEV: Clock Failure Detector Event Interrupt Enable

| Value | Name | Description |

|-------|------|-------------|

| 12    | 128K | 128 Kbytes  |

| 13    | 256K | 256 Kbytes  |

| 14    | 96K  | 96 Kbytes   |

| 15    | 512K | 512 Kbytes  |

### • ARCH: Architecture Identifier

| Value | Name    | Description               |

|-------|---------|---------------------------|

| 0x88  | SAM4SxA | SAM4SxA (48-pin version)  |

| 0x89  | SAM4SxB | SAM4SxB (64-pin version)  |

| 0x8A  | SAM4SxC | SAM4SxC (100-pin version) |

# NVPTYP: Nonvolatile Program Memory Type

| Value | Name      | Description                   |

|-------|-----------|-------------------------------|

| 0     | ROM       | ROM                           |

| 1     | ROMLESS   | ROMless or on-chip Flash      |

| 2     | FLASH     | Embedded Flash Memory         |

|       |           | ROM and Embedded Flash Memory |

| 3     | ROM_FLASH | NVPSIZ is ROM size            |

|       |           | NVPSIZ2 is Flash size         |

| 4     | SRAM      | SRAM emulating ROM            |

# • EXT: Extension Flag

0: Chip ID has a single register definition without extension.

1: An extended Chip ID exists.

# 31.6.18 PIO Multi-driver Enable Register

Name: PIO\_MDER

# Address: 0x400E0E50 (PIOA), 0x400E1050 (PIOB), 0x400E1250 (PIOC)

Access: Write-only

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

| P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

| P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

This register can only be written if the WPEN bit is cleared in the PIO Write Protection Mode Register.

# • P0-P31: Multi-drive Enable

0: No effect.

1: Enables multi-drive on the I/O line.

# 31.6.40 PIO Level Select Register

| Name:<br>Address:<br>Access: | PIO_LSR<br>0x400E0EC4 (P<br>Write-only | 'IOA), 0x400E1 | 0C4 (PIOB), 0x | 400E12C4 (PIC | PC) |     |     |

|------------------------------|----------------------------------------|----------------|----------------|---------------|-----|-----|-----|

| 31                           | 30                                     | 29             | 28             | 27            | 26  | 25  | 24  |

| P31                          | P30                                    | P29            | P28            | P27           | P26 | P25 | P24 |

| 23                           | 22                                     | 21             | 20             | 19            | 18  | 17  | 16  |

| P23                          | P22                                    | P21            | P20            | P19           | P18 | P17 | P16 |

| 15                           | 14                                     | 13             | 12             | 11            | 10  | 9   | 8   |

| P15                          | P14                                    | P13            | P12            | P11           | P10 | P9  | P8  |

| 7                            | 6                                      | 5              | 4              | 3             | 2   | 1   | 0   |

| P7                           | P6                                     | P5             | P4             | P3            | P2  | P1  | P0  |

# • P0-P31: Level Interrupt Selection

0: No effect.

1: The interrupt source is a level-detection event.

# 32.9.15 SSC Interrupt Disable Register

| Name:<br>Address: | SSC_IDR<br>0x40004048 |            |            |             |            |              |            |

|-------------------|-----------------------|------------|------------|-------------|------------|--------------|------------|

| Access:           | Write-only            |            |            |             |            |              |            |

| 31                | 30                    | 29         | 28         | 27          | 26         | 25           | 24         |

| _                 | -                     | -          | -          | -           | _          | _            | —          |

| 23                | 22                    | 21         | 20         | 19          | 18         | 17           | 16         |

| _                 |                       | _          | _          | _           | _          | _            | _          |

| 15                | 14                    | 13         | 12         | 11          | 10         | 9            | 8          |

| _                 | _                     | _          | —          | RXSYN       | TXSYN      | CP1          | CP0        |

| 7<br>RXBUFF       | 6<br>ENDRX            | 5<br>OVRUN | 4<br>RXRDY | 3<br>TXBUFE | 2<br>ENDTX | 1<br>TXEMPTY | 0<br>TXRDY |

| KABUFF            | ENDRA                 | OVRUN      | KARDI      | INDUFE      | ENDIX      |              | IARDY      |

### • TXRDY: Transmit Ready Interrupt Disable

0: No effect.

1: Disables the Transmit Ready Interrupt.

# • TXEMPTY: Transmit Empty Interrupt Disable

0: No effect.

1: Disables the Transmit Empty Interrupt.

### • ENDTX: End of Transmission Interrupt Disable

- 0: No effect.

- 1: Disables the End of Transmission Interrupt.

# • TXBUFE: Transmit Buffer Empty Interrupt Disable

0: No effect.

1: Disables the Transmit Buffer Empty Interrupt.

# • RXRDY: Receive Ready Interrupt Disable

0: No effect.

1: Disables the Receive Ready Interrupt.

# • OVRUN: Receive Overrun Interrupt Disable

0: No effect.

1: Disables the Receive Overrun Interrupt.

# • ENDRX: End of Reception Interrupt Disable

- 0: No effect.

- 1: Disables the End of Reception Interrupt.

# 34.8.7 TWI Interrupt Enable Register

| Name:    | TWI_IER         |                |       |        |        |        |        |

|----------|-----------------|----------------|-------|--------|--------|--------|--------|

| Address: | 0x40018024 (0), | , 0x4001C024 ( | 1)    |        |        |        |        |

| Access:  | Write-only      |                |       |        |        |        |        |

| 31       | 30              | 29             | 28    | 27     | 26     | 25     | 24     |

| —        | -               | -              | -     | -      | -      | -      | —      |

|          |                 |                |       |        |        |        |        |

| 23       | 22              | 21             | 20    | 19     | 18     | 17     | 16     |

| -        | -               | -              | -     | -      | -      | -      | -      |

|          | -               | -              | -     | -      | -      | -      |        |

| 15       | 14              | 13             | 12    | 11     | 10     | 9      | 8      |

| TXBUFE   | RXBUFF          | ENDTX          | ENDRX | EOSACC | SCL_WS | ARBLST | NACK   |

|          |                 |                |       |        |        |        |        |

| 7        | 6               | 5              | 4     | 3      | 2      | 1      | 0      |

| —        | OVRE            | GACC           | SVACC | _      | TXRDY  | RXRDY  | TXCOMP |

The following configuration values are valid for all listed bit names of this register:

0: No effect.

- 1: Enables the corresponding interrupt.

- TXCOMP: Transmission Completed Interrupt Enable

- RXRDY: Receive Holding Register Ready Interrupt Enable

- TXRDY: Transmit Holding Register Ready Interrupt Enable

- SVACC: Slave Access Interrupt Enable

- GACC: General Call Access Interrupt Enable

- OVRE: Overrun Error Interrupt Enable

- NACK: Not Acknowledge Interrupt Enable

- ARBLST: Arbitration Lost Interrupt Enable

- SCL\_WS: Clock Wait State Interrupt Enable

- EOSACC: End Of Slave Access Interrupt Enable

- ENDRX: End of Receive Buffer Interrupt Enable

- ENDTX: End of Transmit Buffer Interrupt Enable

- RXBUFF: Receive Buffer Full Interrupt Enable

- TXBUFE: Transmit Buffer Empty Interrupt Enable

| Peripheral Clock | Baud Rate (bit/s) | CD  | Baud Rate Error | Pulse Time (µs) |

|------------------|-------------------|-----|-----------------|-----------------|

| 3,686,400        | 19,200            | 12  | 0.00%           | 9.77            |

| 20,000,000       | 19,200            | 65  | 0.16%           | 9.77            |

| 32,768,000       | 19,200            | 107 | 0.31%           | 9.77            |

| 40,000,000       | 19,200            | 130 | 0.16%           | 9.77            |

| 3,686,400        | 9,600             | 24  | 0.00%           | 19.53           |

| 20,000,000       | 9,600             | 130 | 0.16%           | 19.53           |

| 32,768,000       | 9,600             | 213 | 0.16%           | 19.53           |

| 40,000,000       | 9,600             | 260 | 0.16%           | 19.53           |

| 3,686,400        | 2,400             | 96  | 0.00%           | 78.13           |

| 20,000,000       | 2,400             | 521 | 0.03%           | 78.13           |

| 32,768,000       | 2,400             | 853 | 0.04%           | 78.13           |

### Table 36-12. IrDA Baud Rate Error (Continued)

#### 36.6.5.3 IrDA Demodulator

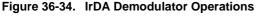

The demodulator is based on the IrDA Receive filter comprised of an 8-bit down counter which is loaded with the value programmed in US\_IF. When a falling edge is detected on the RXD pin, the Filter Counter starts counting down at the peripheral clock speed. If a rising edge is detected on the RXD pin, the counter stops and is reloaded with US\_IF. If no rising edge is detected when the counter reaches 0, the input of the receiver is driven low during one bit time.

Figure 36-34 illustrates the operations of the IrDA demodulator.

The programmed value in the US\_IF register must always meet the following criteria:

$t_{peripheral clock} \times (IRDA_FILTER + 3) < 1.41 \ \mu s$

As the IrDA mode uses the same logic as the ISO7816, note that the FI\_DI\_RATIO field in US\_FIDI must be set to a value higher than 0 in order to make sure IrDA communications operate correctly.

#### 36.6.6 RS485 Mode

The USART features the RS485 mode to enable line driver control. While operating in RS485 mode, the USART behaves as though in Asynchronous or Synchronous mode and configuration of all the parameters is possible. The difference is that the RTS pin is driven high when the transmitter is operating. The behavior of the RTS pin is controlled by the TXEMPTY bit. A typical connection of the USART to an RS485 bus is shown in Figure 36-35.

CPOL is used to determine the inactive state value of the serial clock (SPCK). It is used with CPHA to produce the required clock/data relationship between master and slave devices.

# CLKO: Clock Output Select

0: The USART does not drive the SCK pin.

1: The USART drives the SCK pin if USCLKS does not select the external clock SCK.

# • WRDBT: Wait Read Data Before Transfer

0: The character transmission starts as soon as a character is written into US\_THR (assuming TXRDY was set).

1: The character transmission starts when a character is written and only if RXRDY flag is cleared (Receive Holding Register has been read).

Figure 37-17. Filtering Examples

| Peripheral Clock                              | MAXFILT = 2                                            |

|-----------------------------------------------|--------------------------------------------------------|

|                                               | particulate contamination                              |

| PHA,B                                         |                                                        |

| Filter Out                                    |                                                        |

| Optical/Magnetic disk strips                  | ▲                                                      |

| РНА                                           |                                                        |

| РНВ                                           | motor shaft stopped in such a position that            |

| rotation                                      | rotary sensor cell is aligned with an edge of the disk |

| PHA                                           |                                                        |

| PHB                                           | → PHB Edge area due to system vibration                |

| Resulting PHA, PHB electrical waveforms       | stop                                                   |

| РНА                                           | mechanical shock on system                             |

| PHB                                           |                                                        |

|                                               | vibration                                              |

| PHA, PHB electrical waveforms after filtering |                                                        |

| РНА                                           |                                                        |

| PHB                                           |                                                        |

Atmel

## OPDCMD: Open Drain Command

0 (PUSHPULL): Push pull command.

1 (OPENDRAIN): Open drain command.

### • MAXLAT: Max Latency for Command to Response

0 (5): 5-cycle max latency.

1 (64): 64-cycle max latency.

#### • TRCMD: Transfer Command

| Value | Name           | Description         |

|-------|----------------|---------------------|

| 0     | NO_DATA        | No data transfer    |

| 1     | START_DAT<br>A | Start data transfer |

| 2     | STOP_DATA      | Stop data transfer  |

| 3     | -              | Reserved            |

### • TRDIR: Transfer Direction

0 (WRITE): Write.

1 (READ): Read.

#### • TRTYP: Transfer Type

| Value | Name     | Description                |

|-------|----------|----------------------------|

| 0     | SINGLE   | MMC/SD Card Single Block   |

| 1     | MULTIPLE | MMC/SD Card Multiple Block |

| 2     | STREAM   | MMC Stream                 |

| 4     | BYTE     | SDIO Byte                  |

| 5     | BLOCK    | SDIO Block                 |

### • IOSPCMD: SDIO Special Command

| Value | Name    | Description                 |

|-------|---------|-----------------------------|

| 0     | STD     | Not an SDIO Special Command |

| 1     | SUSPEND | SDIO Suspend Command        |

| 2     | RESUME  | SDIO Resume Command         |

### ATACS: ATA with Command Completion Signal

0 (NORMAL): Normal operation mode.

1 (COMPLETION): This bit indicates that a completion signal is expected within a programmed amount of time (HSMCI\_CSTOR).

#### BOOT\_ACK: Boot Operation Acknowledge

The master can choose to receive the boot acknowledge from the slave when a Boot Request command is issued. When set to one this field indicates that a Boot acknowledge is expected within a programmable amount of time defined with DTOMUL and DTOCYC fields located in the HSMCI\_DTOR. If the acknowledge pattern is not received then an acknowledge timeout error is raised. If the acknowledge pattern is corrupted then an acknowledge pattern error is set.

### 39.6.6 Register Write Protection

To prevent any single software error that may corrupt PWM behavior, the registers listed below can be writeprotected by writing the field WPCMD in the PWM Write Protection Control Register (PWM\_WPCR). They are divided into six groups:

- Register group 0:

- PWM Clock Register

- Register group 1:

- PWM Disable Register

- Register group 2:

- PWM Sync Channels Mode Register

- PWM Channel Mode Register

- PWM Stepper Motor Mode Register

- Register group 3:

- PWM Channel Period Register

- PWM Channel Period Update Register

- Register group 4:

- PWM Channel Dead Time Register

- PWM Channel Dead Time Update Register

- Register group 5:

- PWM Fault Mode Register

- PWM Fault Protection Value Register

There are two types of write protection:

- SW write protection—can be enabled or disabled by software

- HW write protection—can be enabled by software but only disabled by a hardware reset of the PWM controller

Both types of write protection can be applied independently to a particular register group by means of the WPCMD and WPRGx fields in the PWM\_WPCR. If at least one type of write protection is active, the register group is write-protected. The value of field WPCMD defines the action to be performed:

- 0: Disables SW write protection of the register groups of which the bit WPRGx is at '1'

- 1: Enables SW write protection of the register groups of which the bit WPRGx is at '1'

- 2: Enables HW write protection of the register groups of which the bit WPRGx is at '1'

At any time, the user can determine whether SW or HW write protection is active in a particular register group by the fields WPSWS and WPHWS in the PWM Write Protection Status Register (PWM\_WPSR).

If a write access to a write-protected register is detected, the WPVS flag in the PWM\_WPSR is set and the field WPVSRC indicates the register in which the write access has been attempted.

The WPVS and WPVSRC fields are automatically cleared after reading the PWM\_WPSR.

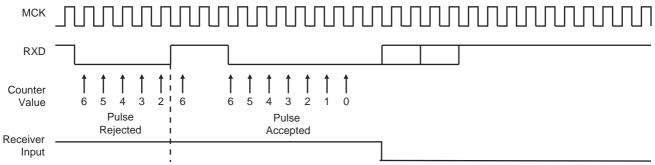

# 40.3 Block Diagram

Access to the UDP is via the APB bus interface. Read and write to the data FIFO are done by reading and writing 8-bit values to APB registers.

The UDP peripheral requires two clocks: one peripheral clock used by the Master Clock domain (MCK) and a 48 MHz clock (UDPCK) used by the 12 MHz domain.

A USB 2.0 full-speed pad is embedded and controlled by the Serial Interface Engine (SIE).

The signal external\_resume is optional. It allows the UDP peripheral to wake up once in system mode. The host is then notified that the device asks for a resume. This optional feature must also be negotiated with the host during the enumeration.

### 40.3.1 Signal Description

| Table 40-2. Signal Names |                                                      |       |  |  |  |  |

|--------------------------|------------------------------------------------------|-------|--|--|--|--|

| Signal Name              | Description                                          | Туре  |  |  |  |  |

| UDPCK                    | 48 MHz clock                                         | Input |  |  |  |  |

| МСК                      | Master clock                                         | Input |  |  |  |  |

| udp_int                  | Interrupt line connected to the Interrupt Controller | Input |  |  |  |  |

| DDP                      | USB D+ line                                          | I/O   |  |  |  |  |

| DDM                      | USB D- line                                          | I/O   |  |  |  |  |

- WAKEUP: Disable USB Bus Interrupt

- 0: No effect

- 1: Disables USB Bus Wakeup Interrupt

# 41.7.7 ACC Analog Control Register

| Name:    | ACC_ACR    |    |    |    |      |    |      |  |

|----------|------------|----|----|----|------|----|------|--|

| Address: | 0x40040094 |    |    |    |      |    |      |  |

| Access:  | Read/Write |    |    |    |      |    |      |  |

| 31       | 30         | 29 | 28 | 27 | 26   | 25 | 24   |  |

| —        | -          | -  | -  | -  | -    | —  | -    |  |

| 23       | 22         | 21 | 20 | 19 | 18   | 17 | 16   |  |

| -        | -          | —  | -  | -  | -    | -  | -    |  |

| 15       | 14         | 13 | 12 | 11 | 10   | 9  | 8    |  |

| _        | -          | —  | —  | -  | -    | -  | -    |  |

| 7        | 6          | 5  | 4  | 3  | 2    | 1  | 0    |  |

| -        | -          | -  | -  | -  | HYST |    | ISEL |  |

This register can only be written if the WPEN bit is cleared in ACC Write Protection Mode Register.

# • ISEL: Current Selection

Refer to the section on ACC electrical characteristics in the datasheet.

0 (LOPW): Low-power option.

1 (HISP): High-speed option.

# • HYST: Hysteresis Selection

0 to 3: Refer to the section on ACC electrical characteristics in the datasheet.