#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 120MHz                                                                  |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, Memory Card, SPI, SSC, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                              |

| Number of I/O              | 79                                                                      |

| Program Memory Size        | 512KB (512K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 128K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                            |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 100-TFBGA                                                               |

| Supplier Device Package    | 100-TFBGA (9x9)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4s8cb-cn |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| ASR #n | arithmetic shift right <i>n</i> bits, $1 \le n \le 32$ . |

|--------|----------------------------------------------------------|

|--------|----------------------------------------------------------|

LSL #*n* logical shift left *n* bits,  $1 \le n \le 31$ .

- LSR #*n* logical shift right *n* bits,  $1 \le n \le 32$ .

- ROR #*n* rotate right *n* bits,  $1 \le n \le 31$ .

- RRX rotate right one bit, with extend.

if omitted, no shift occurs, equivalent to LSL #0.

If the user omits the shift, or specifies LSL #0, the instruction uses the value in Rm.

If the user specifies a shift, the shift is applied to the value in Rm, and the resulting 32-bit value is used by the instruction. However, the contents in the register Rm remains unchanged. Specifying a register with shift also updates the carry flag when used with certain instructions. For information on the shift operations and how they affect the carry flag, see "Flexible Second Operand".

## 12.6.3.4 Shift Operations

Register shift operations move the bits in a register left or right by a specified number of bits, the *shift length*. Register shift can be performed:

- Directly by the instructions ASR, LSR, LSL, ROR, and RRX, and the result is written to a destination register

- During the calculation of *Operand2* by the instructions that specify the second operand as a register with shift. See "Flexible Second Operand". The result is used by the instruction.

The permitted shift lengths depend on the shift type and the instruction. If the shift length is 0, no shift occurs. Register shift operations update the carry flag except when the specified shift length is 0. The following subsections describe the various shift operations and how they affect the carry flag. In these descriptions, Rm is the register containing the value to be shifted, and n is the shift length.

## ASR

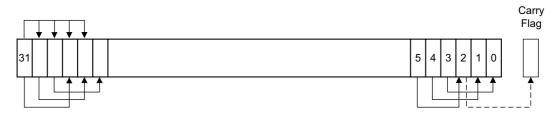

Arithmetic shift right by *n* bits moves the left-hand 32-n bits of the register, Rm, to the right by *n* places, into the right-hand 32-n bits of the result. And it copies the original bit[31] of the register into the left-hand *n* bits of the result. See Figure 12-8.

The ASR #n operation can be used to divide the value in the register Rm by  $2^n$ , with the result being rounded towards negative-infinity.

When the instruction is ASRS or when ASR #n is used in *Operand2* with the instructions MOVS, MVNS, ANDS, ORRS, ORNS, EORS, BICS, TEQ or TST, the carry flag is updated to the last bit shifted out, bit[*n*-1], of the register *Rm*.

- If *n* is 32 or more, then all the bits in the result are set to the value of bit[31] of *Rm*.

- If *n* is 32 or more and the carry flag is updated, it is updated to the value of bit[31] of *Rm*.

## Figure 12-8. ASR #3

## LSR

Logical shift right by n bits moves the left-hand 32-n bits of the register Rm, to the right by *n* places, into the right-hand 32-n bits of the result. And it sets the left-hand n bits of the result to 0. See Figure 12-9.

## • MEMFAULTPENDED: Memory Management Fault Exception Pending

Read:

0: The exception is not pending.

1: The exception is pending.

Note: The user can write to these bits to change the pending status of the exceptions.

## • USGFAULTPENDED: Usage Fault Exception Pending

Read:

0: The exception is not pending.

1: The exception is pending.

Note: The user can write to these bits to change the pending status of the exceptions.

## SYSTICKACT: SysTick Exception Active

Read:

0: The exception is not active.

1: The exception is active.

Note: The user can write to these bits to change the active status of the exceptions.

- Caution: A software that changes the value of an active bit in this register without a correct adjustment to the stacked content can cause the processor to generate a fault exception. Ensure that the software writing to this register retains and subsequently restores the current active status.

- Caution: After enabling the system handlers, to change the value of a bit in this register, the user must use a read-modify-write procedure to ensure that only the required bit is changed.

## • PENDSVACT: PendSV Exception Active

0: The exception is not active.

1: The exception is active.

## • MONITORACT: Debug Monitor Active

0: Debug monitor is not active.

1: Debug monitor is active.

## • SVCALLACT: SVC Call Active

0: SVC call is not active.

1: SVC call is active.

## • USGFAULTACT: Usage Fault Exception Active

0: Usage fault exception is not active.

1: Usage fault exception is active.

## • BUSFAULTACT: Bus Fault Exception Active

0: Bus fault exception is not active.

1: Bus fault exception is active.

## • MEMFAULTACT: Memory Management Fault Exception Active

0: Memory management fault exception is not active.

1: Memory management fault exception is active.

### 16.6.4 RTC Calendar Register

| Name:    | RTC_CALR   |       |    |      |     |    |    |

|----------|------------|-------|----|------|-----|----|----|

| Address: | 0x400E146C |       |    |      |     |    |    |

| Access:  | Read/Write |       |    |      |     |    |    |

| 31       | 30         | 29    | 28 | 27   | 26  | 25 | 24 |

| _        | -          |       |    | DA   | ATE |    |    |

| 23       | 22         | 21    | 20 | 19   | 18  | 17 | 16 |

|          | DAY        | MONTH |    |      |     |    |    |

| 15       | 14         | 13    | 12 | 11   | 10  | 9  | 8  |

|          |            |       | YE | AR   |     |    |    |

| 7        | 6          | 5     | 4  | 3    | 2   | 1  | 0  |

| _        |            |       |    | CENT |     |    |    |

#### • CENT: Current Century

The range that can be set is 19–20 (gregorian) or 13–14 (persian) (BCD). The lowest four bits encode the units. The higher bits encode the tens.

### • YEAR: Current Year

The range that can be set is 00–99 (BCD).

The lowest four bits encode the units. The higher bits encode the tens.

## • MONTH: Current Month

The range that can be set is 01–12 (BCD).

The lowest four bits encode the units. The higher bits encode the tens.

## • DAY: Current Day in Current Week

The range that can be set is 1–7 (BCD).

The coding of the number (which number represents which day) is user-defined as it has no effect on the date counter.

## • DATE: Current Day in Current Month

The range that can be set is 01–31 (BCD).

The lowest four bits encode the units. The higher bits encode the tens.

All non-significant bits read zero.

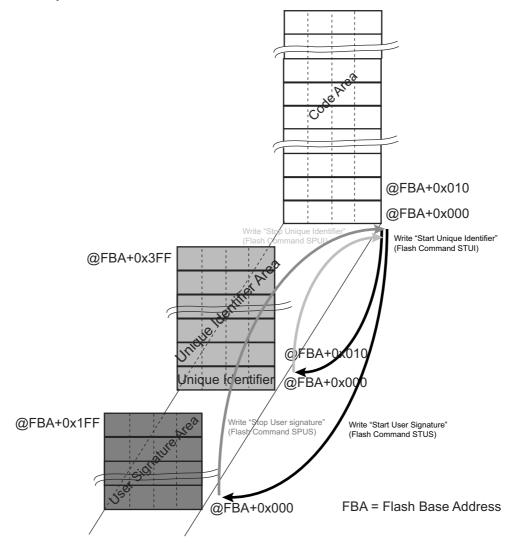

## • FARG: Flash Command Argument

| GETD, GLB,<br>GGPB, STUI,<br>SPUI, GCALB,<br>WUS, EUS, STUS,<br>SPUS, EA | Commands<br>requiring no<br>argument, including<br>Erase all command | FARG is meaningless, must be written with 0                                                 |

|--------------------------------------------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| ES                                                                       | Erase sector<br>command                                              | FARG must be written with any page number within the sector to be erased                    |

|                                                                          |                                                                      | FARG[1:0] defines the number of pages to be erased                                          |

|                                                                          | Erase pages<br>command                                               | The start page must be written in FARG[15:2].                                               |

|                                                                          |                                                                      | FARG[1:0] = 0: Four pages to be erased. FARG[15:2] = Page_Number / 4                        |

|                                                                          |                                                                      | FARG[1:0] = 1: Eight pages to be erased. FARG[15:3] = Page_Number / 8, FARG[2]=0            |

| EPA                                                                      |                                                                      | FARG[1:0] = 2: Sixteen pages to be erased. FARG[15:4] = Page_Number / 16,<br>FARG[3:2]=0    |

|                                                                          |                                                                      | FARG[1:0] = 3: Thirty-two pages to be erased. FARG[15:5] = Page_Number / 32,<br>FARG[4:2]=0 |

|                                                                          |                                                                      | Refer to Table 20-4 "EEFC_FCR.FARG Field for EPA Command".                                  |

| WP, WPL, EWP,<br>EWPL                                                    | Programming commands                                                 | FARG must be written with the page number to be programmed                                  |

| SLB, CLB                                                                 | Lock bit commands                                                    | FARG defines the page number to be locked or unlocked                                       |

| SGPB, CGPB                                                               | GPNVM commands                                                       | FARG defines the GPNVM number to be programmed                                              |

## • FKEY: Flash Writing Protection Key

| Value | Name   | Description                                                                                                                                                                  |

|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x5A  | PASSWD | The 0x5A value enables the command defined by the bits of the register. If the field is written with a different value, the write is not performed and no action is started. |

## 23.7.7 CRCCU DMA Interrupt Mask Register

| Name:    | CRCCU_DMA_IMR |            |    |    |    |    |        |  |  |

|----------|---------------|------------|----|----|----|----|--------|--|--|

| Address: | 0x4004401C    | 0x4004401C |    |    |    |    |        |  |  |

| Access:  | Read-only     |            |    |    |    |    |        |  |  |

| 31       | 30            | 29         | 28 | 27 | 26 | 25 | 24     |  |  |

| -        | -             | _          | -  | -  | -  | -  | -      |  |  |

| 23       | 22            | 21         | 20 | 19 | 18 | 17 | 16     |  |  |

| -        | -             | -          | -  | -  | -  | -  | -      |  |  |

| 15       | 14            | 13         | 12 | 11 | 10 | 9  | 8      |  |  |

| -        | -             | -          | -  | -  | -  | -  | -      |  |  |

| 7        | 6             | 5          | 4  | 3  | 2  | 1  | 0      |  |  |

| _        | -             | _          | -  | _  | -  | —  | DMAIMR |  |  |

## • DMAIMR: Interrupt Mask

0: Buffer Transfer Completed interrupt disabled

1: Buffer Transfer Completed interrupt enabled

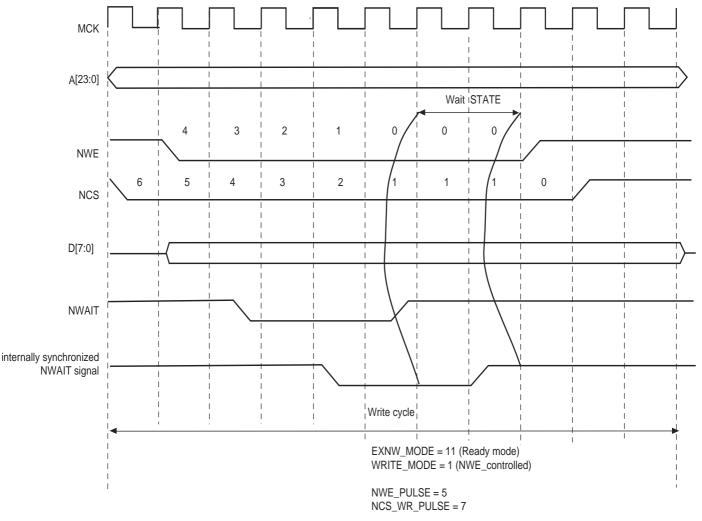

#### 26.13.3 Ready Mode

In Ready mode (EXNW\_MODE = 11), the SMC behaves differently. Normally, the SMC begins the access by down counting the setup and pulse counters of the read/write controlling signal. In the last cycle of the pulse phase, the resynchronized NWAIT signal is examined.

If asserted, the SMC suspends the access as shown in Figure 26-25 and Figure 26-26. After deassertion, the access is completed: the hold step of the access is performed.

This mode must be selected when the external device uses deassertion of the NWAIT signal to indicate its ability to complete the read or write operation.

If the NWAIT signal is deasserted before the end of the pulse, or asserted after the end of the pulse of the controlling read/write signal, it has no impact on the access length as shown in Figure 26-26.

Figure 26-25. NWAIT Assertion in Write Access: Ready Mode (EXNW\_MODE = 11)

## 27.3 Peripheral DMA Controller Connections

The Peripheral DMA Controller handles the data transfer between peripherals and memory and receives triggers from the peripherals listed in the following table.

The Peripheral DMA Controller handles transfer requests from the channel according to the following priorities (Channel 0 is high priority):

| Instance Name | Channel T/R | Channel Number |

|---------------|-------------|----------------|

| PWM           | Transmit    | 21             |

| TWI1          | Transmit    | 20             |

| TWIO          | Transmit    | 19             |

| UART1         | Transmit    | 18             |

| UART0         | Transmit    | 17             |

| USART1        | Transmit    | 16             |

| USART0        | Transmit    | 15             |

| DACC          | Transmit    | 14             |

| SPI           | Transmit    | 13             |

| SSC           | Transmit    | 12             |

| HSMCI         | Transmit    | 11             |

| PIOA          | Receive     | 10             |

| TWI1          | Receive     | 9              |

| TWIO          | Receive     | 8              |

| UART1         | Receive     | 7              |

| UART0         | Receive     | 6              |

| USART1        | Receive     | 5              |

| USART0        | Receive     | 4              |

| ADC           | Receive     | 3              |

| SPI           | Receive     | 2              |

| SSC           | Receive     | 1              |

| HSMCI         | Receive     | 0              |

Table 27-1.Peripheral DMA Controller

## 29.17.10PMC Clock Generator PLLB Register

| Name:    | CKGR_PLLBR |           |    |    |    |      |    |  |

|----------|------------|-----------|----|----|----|------|----|--|

| Address: | 0x400E042C |           |    |    |    |      |    |  |

| Access:  | Read/Write |           |    |    |    |      |    |  |

| 31       | 30         | 29        | 28 | 27 | 26 | 25   | 24 |  |

| -        | -          | _         | -  | -  |    | MULB |    |  |

| 23       | 22         | 21        | 20 | 19 | 18 | 17   | 16 |  |

|          | MULB       |           |    |    |    |      |    |  |

| 15       | 14         | 13        | 12 | 11 | 10 | 9    | 8  |  |

| -        | -          | PLLBCOUNT |    |    |    |      |    |  |

| 7        | 6          | 5         | 4  | 3  | 2  | 1    | 0  |  |

|          |            |           | DI | VB |    |      |    |  |

Possible limitations on PLLB input frequencies and multiplier factors should be checked before using the PMC. This register can only be written if the WPEN bit is cleared in the PMC Write Protection Mode Register.

## • DIVB: PLLB Front-End Divider

- 0: Divider output is stuck at 0 and PLLB is disabled.

- 1: Divider is bypassed (divide by 1)

- 2-255: Clock is divided by DIVB

## PLLBCOUNT: PLLB Counter

Specifies the number of Slow Clock cycles before the LOCKB bit is set in PMC\_SR after CKGR\_PLLBR is written.

#### • MULB: PLLB Multiplier

0: The PLLB is deactivated (PLLB also disabled if DIVB = 0).

7 up to 62: The PLLB Clock frequency is the PLLB input frequency multiplied by MULB + 1.

Unlisted values are forbidden.

Before using the SSC transmitter, the PIO controller must be configured to dedicate the SSC transmitter I/O lines to the SSC peripheral mode.

| Instance | Signal | I/O Line | Peripheral |

|----------|--------|----------|------------|

| SSC      | RD     | PA18     | А          |

| SSC      | RF     | PA20     | А          |

| SSC      | RK     | PA19     | А          |

| SSC      | TD     | PA17     | А          |

| SSC      | TF     | PA15     | А          |

| SSC      | тк     | PA16     | А          |

#### Table 32-2. I/O Lines

#### 32.7.2 Power Management

The SSC is not continuously clocked. The SSC interface may be clocked through the Power Management Controller (PMC), therefore the programmer must first configure the PMC to enable the SSC clock.

#### 32.7.3 Interrupt

The SSC interface has an interrupt line connected to the interrupt controller. Handling interrupts requires programming the interrupt controller before configuring the SSC.

All SSC interrupts can be enabled/disabled configuring the SSC Interrupt Mask Register. Each pending and

#### Table 32-3. Peripheral IDs

| Instance | ID |

|----------|----|

| SSC      | 22 |

unmasked SSC interrupt will assert the SSC interrupt line. The SSC interrupt service routine can get the interrupt origin by reading the SSC Interrupt Status Register.

## 32.9.17 SSC Write Protection Mode Register

| Name:<br>Address: | SSC_WPMR<br>0x400040E4 |    |    |     |    |    |      |

|-------------------|------------------------|----|----|-----|----|----|------|

| Access:           | Read/Write             |    |    |     |    |    |      |

| 31                | 30                     | 29 | 28 | 27  | 26 | 25 | 24   |

|                   |                        |    | WP | KEY |    |    |      |

| 23                | 22                     | 21 | 20 | 19  | 18 | 17 | 16   |

|                   |                        |    | WP | KEY |    |    |      |

| 15                | 14                     | 13 | 12 | 11  | 10 | 9  | 8    |

|                   |                        |    | WP | KEY |    |    |      |

| 7                 | 6                      | 5  | 4  | 3   | 2  | 1  | 0    |

| -                 | -                      | —  | _  | _   | _  | _  | WPEN |

## • WPEN: Write Protection Enable

0: Disables the write protection if WPKEY corresponds to 0x535343 ("SSC" in ASCII).

1: Enables the write protection if WPKEY corresponds to 0x535343 ("SSC" in ASCII).

See Section 32.8.10 "Register Write Protection" for the list of registers that can be protected.

#### • WPKEY: Write Protection Key

| Value    | Name    | Description                                                                       |  |  |  |

|----------|---------|-----------------------------------------------------------------------------------|--|--|--|

| 0x535343 | PASSWD  | Writing any other value in this field aborts the write operation of the WPEN bit. |  |  |  |

| 0,000040 | FAGGVID | Always reads as 0.                                                                |  |  |  |

# 33. Serial Peripheral Interface (SPI)

## 33.1 Description

The Serial Peripheral Interface (SPI) circuit is a synchronous serial data link that provides communication with external devices in Master or Slave mode. It also enables communication between processors if an external processor is connected to the system.

The Serial Peripheral Interface is essentially a Shift register that serially transmits data bits to other SPIs. During a data transfer, one SPI system acts as the "master" which controls the data flow, while the other devices act as "slaves" which have data shifted into and out by the master. Different CPUs can take turn being masters (multiple master protocol, contrary to single master protocol where one CPU is always the master while all of the others are always slaves). One master can simultaneously shift data into multiple slaves. However, only one slave can drive its output to write data back to the master at any given time.

A slave device is selected when the master asserts its NSS signal. If multiple slave devices exist, the master generates a separate slave select signal for each slave (NPCS).

The SPI system consists of two data lines and two control lines:

- Master Out Slave In (MOSI)—This data line supplies the output data from the master shifted into the input(s) of the slave(s).

- Master In Slave Out (MISO)—This data line supplies the output data from a slave to the input of the master. There may be no more than one slave transmitting data during any particular transfer.

- Serial Clock (SPCK)—This control line is driven by the master and regulates the flow of the data bits. The master can transmit data at a variety of baud rates; there is one SPCK pulse for each bit that is transmitted.

- Slave Select (NSS)—This control line allows slaves to be turned on and off by hardware.

## 33.2 Embedded Characteristics

- Master or Slave Serial Peripheral Bus Interface

- 8-bit to 16-bit programmable data length per chip select

- Programmable phase and polarity per chip select

- Programmable transfer delay between consecutive transfers and delay before SPI clock per chip select

- Programmable delay between chip selects

- Selectable mode fault detection

- Master Mode can drive SPCK up to Peripheral Clock

- Master Mode Bit Rate can be Independent of the Processor/Peripheral Clock

- Slave mode operates on SPCK, asynchronously with core and bus clock

- Four chip selects with external decoder support allow communication with up to 15 peripherals

- Communication with Serial External Devices Supported

- Serial memories, such as DataFlash and 3-wire EEPROMs

- Serial peripherals, such as ADCs, DACs, LCD controllers, CAN controllers and sensors

- External coprocessors

- Connection to PDC Channel Capabilities, Optimizing Data Transfers

- One channel for the receiver

- One channel for the transmitter

- Register Write Protection

## 37.7.3 TC Channel Mode Register: Waveform Mode

Name: TC\_CMRx [x=0..2] (WAVEFORM\_MODE)

Address: 0x40010004 (0)[0], 0x40010044 (0)[1], 0x40010084 (0)[2], 0x40014004 (1)[0], 0x40014044 (1)[1], 0x40014084 (1)[2]

| Access: | Read/Write   |               |      |      |        |         |    |

|---------|--------------|---------------|------|------|--------|---------|----|

| 31      | 30           | 29            | 28   | 27   | 26     | 25      | 24 |

| BS      | BSWTRG BEEVT |               | EVT  | BCPC |        | BC      | PB |

| 23      | 22           | 21            | 20   | 19   | 18     | 17      | 16 |

| AS      | ASWTRG AEEVT |               | EVT  | AC   | PC     | ACPA    |    |

| 15      | 14           | 13            | 12   | 11   | 10     | 9       | 8  |

| WAVE    | WAV          | WAVSEL ENETRG |      | EEVT |        | EEVTEDG |    |

| 7       | 6            | 5             | 4    | 3    | 2      | 1       | 0  |

| CPCDIS  | CPCSTOP      | BL            | JRST | CLKI | TCCLKS |         |    |

This register can only be written if the WPEN bit is cleared in the TC Write Protection Mode Register.

## • TCCLKS: Clock Selection

| Value | Name         | Description                                              |

|-------|--------------|----------------------------------------------------------|

| 0     | TIMER_CLOCK1 | Clock selected: internal MCK/2 clock signal (from PMC)   |

| 1     | TIMER_CLOCK2 | Clock selected: internal MCK/8 clock signal (from PMC)   |

| 2     | TIMER_CLOCK3 | Clock selected: internal MCK/32 clock signal (from PMC)  |

| 3     | TIMER_CLOCK4 | Clock selected: internal MCK/128 clock signal (from PMC) |

| 4     | TIMER_CLOCK5 | Clock selected: internal SLCK clock signal (from PMC)    |

| 5     | XC0          | Clock selected: XC0                                      |

| 6     | XC1          | Clock selected: XC1                                      |

| 7     | XC2          | Clock selected: XC2                                      |

#### • CLKI: Clock Invert

0: Counter is incremented on rising edge of the clock.

1: Counter is incremented on falling edge of the clock.

### BURST: Burst Signal Selection

| Value | Name | Description                                   |

|-------|------|-----------------------------------------------|

| 0     | NONE | The clock is not gated by an external signal. |

| 1     | XC0  | XC0 is ANDed with the selected clock.         |

| 2     | XC1  | XC1 is ANDed with the selected clock.         |

| 3     | XC2  | XC2 is ANDed with the selected clock.         |

## • CPCSTOP: Counter Clock Stopped with RC Compare

0: Counter clock is not stopped when counter reaches RC.

1: Counter clock is stopped when counter reaches RC.

## 41.7.5 ACC Interrupt Mask Register

| Name:<br>Address: | ACC_IMR<br>0x4004002C |    |    |    |    |    |    |

|-------------------|-----------------------|----|----|----|----|----|----|

|                   |                       |    |    |    |    |    |    |

| Access:           | Read-only             |    |    |    |    |    |    |

| 31                | 30                    | 29 | 28 | 27 | 26 | 25 | 24 |

| -                 | -                     | -  | _  | -  | -  | -  | -  |

| 23                | 22                    | 21 | 20 | 19 | 18 | 17 | 16 |

| _                 | -                     | -  | -  | -  | -  | _  | -  |

| 15                | 14                    | 13 | 12 | 11 | 10 | 9  | 8  |

| -                 | -                     | -  | _  | -  | -  | -  | -  |

| 7                 | 6                     | 5  | 4  | 3  | 2  | 1  | 0  |

| _                 | -                     | _  | _  | _  | _  | _  | CE |

## • CE: Comparison Edge

0: The interrupt is disabled.

1: The interrupt is enabled.

## 42.7.6 ADC Channel Disable Register

| Name:    | ADC_CHDR   |      |      |      |      |     |     |

|----------|------------|------|------|------|------|-----|-----|

| Address: | 0x40038014 |      |      |      |      |     |     |

| Access:  | Write-only |      |      |      |      |     |     |

| 31       | 30         | 29   | 28   | 27   | 26   | 25  | 24  |

| —        | -          | _    | -    | -    | _    | _   | —   |

| 23       | 22         | 21   | 20   | 19   | 18   | 17  | 16  |

| —        | -          | _    | -    | -    | _    | —   | —   |

| 15       | 14         | 13   | 12   | 11   | 10   | 9   | 8   |

| CH15     | CH14       | CH13 | CH12 | CH11 | CH10 | CH9 | CH8 |

| 7        | 6          | 5    | 4    | 3    | 2    | 1   | 0   |

| CH7      | CH6        | CH5  | CH4  | CH3  | CH2  | CH1 | CH0 |

This register can only be written if the WPEN bit is cleared in the ADC Write Protection Mode Register.

## • CHx: Channel x Disable

0: No effect.

1: Disables the corresponding channel.

**Warning:** If the corresponding channel is disabled during a conversion or if it is disabled and then reenabled during a conversion, its associated data and corresponding EOCx and GOVRE flags in ADC\_ISR and OVREx flags in ADC\_OVER are unpredictable.

## 42.7.9 ADC Interrupt Enable Register

| Name:    | ADC_IER    |       |        |       |       |       |      |

|----------|------------|-------|--------|-------|-------|-------|------|

| Address: | 0x40038024 |       |        |       |       |       |      |

| Access:  | Write-only |       |        |       |       |       |      |

| 31       | 30         | 29    | 28     | 27    | 26    | 25    | 24   |

| —        | -          | -     | RXBUFF | ENDRX | COMPE | GOVRE | DRDY |

| 23       | 22         | 21    | 20     | 19    | 18    | 17    | 16   |

| EOCAL    | _          | _     | —      | —     | —     | —     | —    |

| 15       | 14         | 13    | 12     | 11    | 10    | 9     | 8    |

| EOC15    | EOC14      | EOC13 | EOC12  | EOC11 | EOC10 | EOC9  | EOC8 |

| 7        | 6          | 5     | 4      | 3     | 2     | 1     | 0    |

| EOC7     | EOC6       | EOC5  | EOC4   | EOC3  | EOC2  | EOC1  | EOC0 |

The following configuration values are valid for all listed bit names of this register:

- 0: No effect.

- 1: Enables the corresponding interrupt.

- EOCx: End of Conversion Interrupt Enable x

- EOCAL: End of Calibration Sequence

- DRDY: Data Ready Interrupt Enable

- GOVRE: General Overrun Error Interrupt Enable

- COMPE: Comparison Event Interrupt Enable

- ENDRX: End of Receive Buffer Interrupt Enable

- RXBUFF: Receive Buffer Full Interrupt Enable

## 42.7.12 ADC Interrupt Status Register

| Name:    | ADC_ISR    |       |        |       |       |       |      |

|----------|------------|-------|--------|-------|-------|-------|------|

| Address: | 0x40038030 |       |        |       |       |       |      |

| Access:  | Read-only  |       |        |       |       |       |      |

| 31       | 30         | 29    | 28     | 27    | 26    | 25    | 24   |

| —        | -          | -     | RXBUFF | ENDRX | COMPE | GOVRE | DRDY |

| 23       | 22         | 21    | 20     | 19    | 18    | 17    | 16   |

| EOCAL    | -          | —     | —      | —     | —     | —     | —    |

| 15       | 14         | 13    | 12     | 11    | 10    | 9     | 8    |

| EOC15    | EOC14      | EOC13 | EOC12  | EOC11 | EOC10 | EOC9  | EOC8 |

| 7        | 6          | 5     | 4      | 3     | 2     | 1     | 0    |

| EOC7     | EOC6       | EOC5  | EOC4   | EOC3  | EOC2  | EOC1  | EOC0 |

## • EOCx: End of Conversion x (automatically set / cleared)

0: The corresponding analog channel is disabled, or the conversion is not finished. This flag is cleared when reading the corresponding ADC\_CDRx registers.

1: The corresponding analog channel is enabled and conversion is complete.

#### • EOCAL: End of Calibration Sequence

- 0: Calibration sequence is ongoing, or no calibration sequence has been requested.

- 1: Calibration sequence is complete.

#### • DRDY: Data Ready (automatically set / cleared)

- 0: No data has been converted since the last read of ADC\_LCDR.

- 1: At least one data has been converted and is available in ADC\_LCDR.

## • GOVRE: General Overrun Error (cleared on read)

- 0: No general overrun error occurred since the last read of ADC\_ISR.

- 1: At least one general overrun error has occurred since the last read of ADC\_ISR.

## • COMPE: Comparison Event (cleared on read)

- 0: No comparison event since the last read of ADC\_ISR.

- 1: At least one comparison event (defined in the ADC\_EMR and ADC\_CWR) has occurred since the last read of ADC\_ISR.

## • ENDRX: End of Receive Transfer (cleared by writing ADC\_RCR or ADC\_RNCR)

- 0: The Receive Counter Register has not reached 0 since the last write in ADC\_RCR or ADC\_RNCR<sup>(1)</sup>.

- 1: The Receive Counter Register has reached 0 since the last write in ADC\_RCR or ADC\_RNCR<sup>(1)</sup>.

## • RXBUFF: Receive Buffer Full (cleared by writing ADC\_RCR or ADC\_RNCR)

- 0: ADC\_RCR or ADC\_RNCR<sup>(1)</sup> has a value other than 0.

- 1: Both ADC\_RCR and ADC\_RNCR<sup>(1)</sup> have a value of 0.

- Note: 1. ADC\_RCR and ADC\_RNCR are PDC registers

| Table 44-24. | SAM4SD32/SA16/SD16 Typical Active Power Consumption with VDDCORE@ 1.2V running from Flash Memory |

|--------------|--------------------------------------------------------------------------------------------------|

| (            | AMP2) or SRAM                                                                                    |

|                  | CoreMark                               |                                       |                                        |                                       |      |     |

|------------------|----------------------------------------|---------------------------------------|----------------------------------------|---------------------------------------|------|-----|

|                  | Cache Enable (CE)                      |                                       | Cache Dis                              |                                       |      |     |

| Core Clock (MHz) | 128-bit Flash<br>access <sup>(1)</sup> | 64-bit Flash<br>access <sup>(1)</sup> | 128-bit Flash<br>access <sup>(1)</sup> | 64-bit Flash<br>access <sup>(1)</sup> | SRAM | Uni |

| 120              | 23.2                                   | 23.2                                  | 27.8                                   | 20.9                                  | 22.1 |     |

| 100              | 19.6                                   | 19.6                                  | 25.3                                   | 19.0                                  | 18.5 |     |

| 84               | 16.6                                   | 16.5                                  | 21.6                                   | 16.2                                  | 15.7 |     |

| 64               | 12.8                                   | 12.8                                  | 18.0                                   | 13.7                                  | 12.1 |     |

| 48               | 9.7                                    | 9.7                                   | 14.9                                   | 11.9                                  | 9.2  |     |

| 32               | 6.7                                    | 6.7                                   | 11.2                                   | 9.5                                   | 6.3  |     |

| 24               | 5.2                                    | 5.2                                   | 9.5                                    | 8.4                                   | 4.9  | m/  |

| 12               | 2.5                                    | 2.5                                   | 5.4                                    | 4.6                                   | 2.4  |     |

| 8                | 1.8                                    | 1.8                                   | 4.5                                    | 3.9                                   | 1.7  |     |

| 4                | 1.1                                    | 1.1                                   | 2.8                                    | 2.8                                   | 1.0  |     |

| 2                | 0.7                                    | 0.7                                   | 2.0                                    | 2.0                                   | 0.7  |     |

| 1                | 0.5                                    | 0.5                                   | 1.2                                    | 1.2                                   | 0.5  |     |

| 0.5              | 0.4                                    | 0.4                                   | 0.8                                    | 0.8                                   | 0.4  |     |

Note: 1. Flash Wait State (FWS) in EEFC\_FMR adjusted versus core frequency

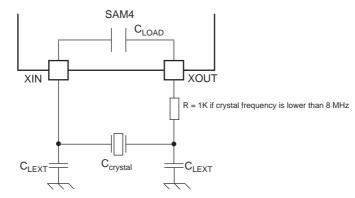

### 44.5.6 3 to 20 MHz Crystal Oscillator Characteristics

| Symbol               | Parameter                                     | Conditions                                              | Min  | Тур | Max  | Unit |

|----------------------|-----------------------------------------------|---------------------------------------------------------|------|-----|------|------|

| f <sub>OSC</sub>     | Operating Frequency                           | Normal mode with crystal                                | 3    | 16  | 20   | MHz  |

|                      | Duty Cycle                                    |                                                         | 40   | 50  | 60   | %    |

|                      |                                               | 3 MHz, C <sub>SHUNT</sub> = 3 pF                        |      |     | 14.5 |      |

|                      |                                               | 8 MHz, C <sub>SHUNT</sub> = 7 pF                        |      |     | 4    |      |

| t <sub>START</sub>   | Startup Time                                  | 16 MHz, $C_{SHUNT}$ = 7 pF with $C_m$ = 8 fF            | -    | -   | 1.4  | ms   |

|                      |                                               | 16 MHz, $C_{SHUNT}$ = 7 pF with $C_m$ = 1.6 fF          |      |     | 2.5  |      |

|                      |                                               | 20 MHz, C <sub>SHUNT</sub> = 7 pF                       |      |     | 1    |      |

|                      |                                               | 3 MHz                                                   |      | 230 | 350  |      |

|                      |                                               | 8 MHz                                                   |      | 300 | 400  | μΑ   |

| IDDON                | Current Consumption (on VDDIO)                | 16 MHz                                                  | _    | 390 | 470  |      |

|                      |                                               | 20 MHz                                                  |      | 450 | 560  |      |

|                      |                                               | 3 MHz                                                   |      |     | 15   |      |

| P <sub>ON</sub>      | Drive Level                                   | 8 MHz                                                   | _    | _   | 30   | μW   |

|                      |                                               | 16 MHz, 20 MHz                                          |      |     | 50   |      |

| R <sub>f</sub>       | Internal Resistor                             | Between XIN and XOUT                                    | _    | 0.5 | _    | MΩ   |

| C <sub>LEXT</sub>    | Maximum External Capacitor<br>on XIN and XOUT |                                                         | _    | _   | 17   | pF   |

| C <sub>crystal</sub> | Allowed Crystal Capacitance Load              | From crystal specification                              | 12.5 | _   | 17.5 | pF   |

| $C_{LOAD}$           | Internal Equivalent Load Capacitance          | Integrated load capacitance<br>(XIN and XOUT in series) | 7.5  | 9.5 | 10.5 | pF   |

| Table 44-31. | 3 to 20 MHz Crystal Oscillator Characteristics |

|--------------|------------------------------------------------|

|--------------|------------------------------------------------|

#### Figure 44-15. 3 to 20 MHz Crystal Oscillator Schematic

$\label{eq:clear} C_{\text{LEXT}} = 2 \times (C_{\text{crystal}} - C_{\text{LOAD}} - C_{\text{PCB}}).$

Where  $C_{PCB}$  is the capacitance of the printed circuit board (PCB) track layout from the crystal to the SAM4 pin.