#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 120MHz                                                                   |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, Memory Card, SPI, SSC, UART/USART, USB  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                               |

| Number of I/O              | 79                                                                       |

| Program Memory Size        | 512KB (512K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                             |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                    |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 100-TFBGA                                                                |

| Supplier Device Package    | 100-TFBGA (9x9)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4s8cb-cnr |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

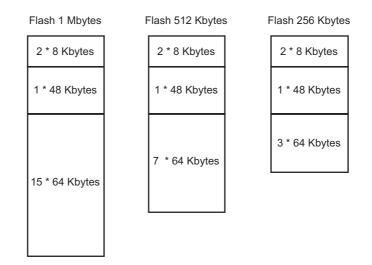

#### Figure 8-3. Flash Size

The following erase commands can be used depending on the sector size:

- 8 Kbyte small sector

- Erase and write page (EWP)

- Erase and write page and lock (EWPL)

- Erase sector (ES) with FARG set to a page number in the sector to erase

- Erase pages (EPA) with FARG [1:0] = 0 to erase four pages or FARG [1:0] = 1 to erase eight pages.

FARG [1:0] = 2 and FARG [1:0] = 3 must not be used.

- 48 Kbyte and 64 Kbyte sectors

- One block of 8 pages inside any sector, with the command Erase pages (EPA) with FARG[1:0] = 1

- One block of 16 pages inside any sector, with the command Erase pages (EPA) and FARG[1:0] = 2

- One block of 32 pages inside any sector, with the command Erase pages (EPA) and FARG[1:0] = 3

- One sector with the command Erase sector (ES) and FARG set to a page number in the sector to erase

- Entire memory plane

- The entire Flash, with the command Erase all (EA)

The Write commands of the Flash cannot be used under 330 kHz.

# 8.1.3.2 Enhanced Embedded Flash Controller

The Enhanced Embedded Flash Controller manages accesses performed by the masters of the system. It enables reading the Flash and writing the write buffer. It also contains a User Interface, mapped on the APB.

The Enhanced Embedded Flash Controller ensures the interface of the Flash block.

It manages the programming, erasing, locking and unlocking sequences of the Flash using a full set of commands. One of the commands returns the embedded Flash descriptor definition that informs the system about the Flash organization, thus making the software generic.

# 8.1.3.3 Flash Speed

The user must set the number of wait states depending on the frequency used.

For more details, refer to Section 44.12 "AC Characteristics".

#### 12.6.4.4 LDR and STR, Unprivileged

Load and Store with unprivileged access.

| Syntax      |                                                                 |

|-------------|-----------------------------------------------------------------|

| op{         | <pre>type}T{cond} Rt, [Rn {, #offset}] ; immediate offset</pre> |

| where:      |                                                                 |

| ор          | is one of:                                                      |

| LDR         | Load Register.                                                  |

| STR         | Store Register.                                                 |

| type is one | of:                                                             |

| В           | unsigned byte, zero extend to 32 bits on loads.                 |

| SB          | signed byte, sign extend to 32 bits (LDR only).                 |

| Н           | unsigned halfword, zero extend to 32 bits on loads.             |

| SH          | signed halfword, sign extend to 32 bits (LDR only).             |

| -           | omit, for word.                                                 |

| cond        | is an optional condition code, see "Conditional Execution".     |

| Rt          | is the register to load or store.                               |

| Rn          | is the register on which the memory address is based.           |

| offset      | is an offset from <i>Rn</i> and can be 0 to 255.                |

|             | If offset is omitted, the address is the value in Rn.           |

| Operation   |                                                                 |

#### Operation

These load and store instructions perform the same function as the memory access instructions with immediate offset, see "LDR and STR, Immediate Offset". The difference is that these instructions have only unprivileged access even when used in privileged software.

When used in unprivileged software, these instructions behave in exactly the same way as normal memory access instructions with immediate offset.

Restrictions

In these instructions:

- *Rn* must not be PC

- *Rt* must not be SP and must not be PC.

## **Condition Flags**

These instructions do not change the flags.

## Examples

| STRBTEQ | R4, | [R7]     | ; Conditionally store least significant byte in     |

|---------|-----|----------|-----------------------------------------------------|

|         |     |          | ; R4 to an address in R7, with unprivileged access  |

| LDRHT   | R2, | [R2, #8] | ; Load halfword value from an address equal to      |

|         |     |          | ; sum of R2 and 8 into R2, with unprivileged access |

Atmel

| 12.8.3.1 | Interrupt Set-enable Registers |                   |     |     |    |    |    |  |  |  |

|----------|--------------------------------|-------------------|-----|-----|----|----|----|--|--|--|

| Name:    | NVIC_ISERx [x=                 | NVIC_ISERx [x=07] |     |     |    |    |    |  |  |  |

| Access:  | Read/Write                     |                   |     |     |    |    |    |  |  |  |

| Reset:   | 0x000000000                    |                   |     |     |    |    |    |  |  |  |

| 31       | 30                             | 29                | 28  | 27  | 26 | 25 | 24 |  |  |  |

|          | SETENA                         |                   |     |     |    |    |    |  |  |  |

| 23       | 22                             | 21                | 20  | 19  | 18 | 17 | 16 |  |  |  |

|          |                                |                   | SET | ENA |    |    |    |  |  |  |

| 15       | 14                             | 13                | 12  | 11  | 10 | 9  | 8  |  |  |  |

| SETENA   |                                |                   |     |     |    |    |    |  |  |  |

| 7        | 6                              | 5                 | 4   | 3   | 2  | 1  | 0  |  |  |  |

|          |                                |                   | SET | ENA |    |    |    |  |  |  |

These registers enable interrupts and show which interrupts are enabled.

# • SETENA: Interrupt Set-enable

Write:

0: No effect.

1: Enables the interrupt.

Read:

0: Interrupt disabled.

1: Interrupt enabled.

- Notes: 1. If a pending interrupt is enabled, the NVIC activates the interrupt based on its priority.

- 2. If an interrupt is not enabled, asserting its interrupt signal changes the interrupt state to pending, the NVIC never activates the interrupt, regardless of its priority.

Atmel

Field RSTC\_SR.RSTTYP is updated to report a backup reset.

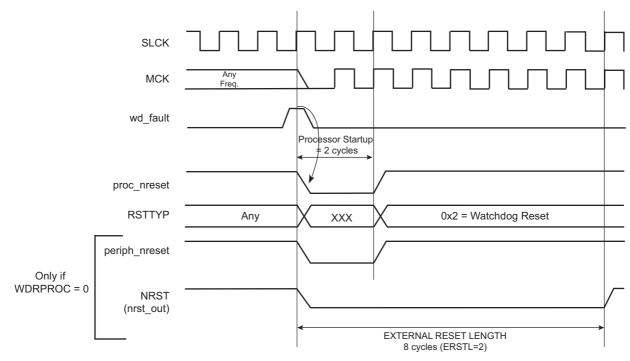

## 14.4.3.3 Watchdog Reset

The watchdog reset is entered when a watchdog fault occurs. This reset lasts three slow clock cycles.

When in watchdog reset, assertion of the reset signals depends on the WDRPROC bit in the WDT\_MR:

- If WDRPROC = 0, the processor reset and the peripheral reset are asserted. The NRST line is also

asserted, depending on how field RSTC\_MR.ERSTL is programmed. However, the resulting low level on

NRST does not result in a user reset state.

- If WDRPROC = 1, only the processor reset is asserted.

The Watchdog Timer is reset by the proc\_nreset signal. As the watchdog fault always causes a processor reset if WDRSTEN in the WDT\_MR is set, the Watchdog Timer is always reset after a watchdog reset, and the Watchdog is enabled by default and with a period set to a maximum.

When bit WDT\_MR.WDRSTEN is reset, the watchdog fault has no impact on the Reset Controller.

## Figure 14-4. Watchdog Reset

# 14.4.3.4 Software Reset

The Reset Controller offers commands to assert the different reset signals. These commands are performed by writing the Control Register (RSTC\_CR) with the following bits at 1:

- RSTC\_CR.PROCRST: Writing a 1 to PROCRST resets the processor and the watchdog timer.

- RSTC\_CR.PERRST: Writing a 1 to PERRST resets all the embedded peripherals including the memory system, and, in particular, the Remap Command. The Peripheral Reset is generally used for debug purposes.

Except for debug purposes, PERRST must always be used in conjunction with PROCRST (PERRST and PROCRST set both at 1 simultaneously).

• RSTC\_CR.EXTRST: Writing a 1 to EXTRST asserts low the NRST pin during a time defined by the field RSTC\_MR.ERSTL.

# 17.5.3 Watchdog Timer Status Register

| Name:<br>Address: | WDT_SR<br>0x400E1458 |    |    |    |    |       |       |

|-------------------|----------------------|----|----|----|----|-------|-------|

| Access            | Read-only            |    |    |    |    |       |       |

| 31                | 30                   | 29 | 28 | 27 | 26 | 25    | 24    |

| —                 | -                    | _  | _  | _  | _  | _     | —     |

| 23                | 22                   | 21 | 20 | 19 | 18 | 17    | 16    |

| 15                | 14                   | 13 | 12 | 11 | 10 | 9     | 8     |

| -                 | -                    | -  | -  | -  | -  | -     | -     |

| 7                 | 6                    | 5  | 4  | 3  | 2  | 1     | 0     |

| _                 | -                    | _  | -  | _  | -  | WDERR | WDUNF |

# • WDUNF: Watchdog Underflow (cleared on read)

0: No watchdog underflow occurred since the last read of WDT\_SR.

1: At least one watchdog underflow occurred since the last read of WDT\_SR.

## • WDERR: Watchdog Error (cleared on read)

0: No watchdog error occurred since the last read of WDT\_SR.

1: At least one watchdog error occurred since the last read of WDT\_SR.

Atmel

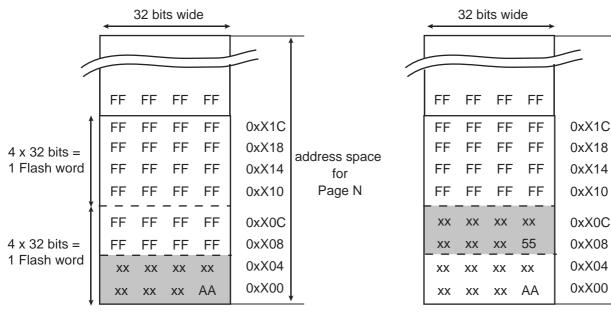

Step 1: Flash array after programming first byte (0xAA) 64-bit used at address 0xX00 (write latch buffer + WP) Step 2: Flash array after programming second byte (0x55) 64-bit used at address 0xX08 (write latch buffer + WP)

Note: The byte location shown here is for example only, it can be any byte location within a 64-bit word.

## 20.4.3.3 Erase Commands

Erase commands are allowed only on unlocked regions. Depending on the Flash memory, several commands can be used to erase the Flash:

- Erase All Memory (EA): All memory is erased. The processor must not fetch code from the Flash memory.

- Erase Pages (EPA): 8 or 16 pages are erased in the Flash sector selected. The first page to be erased is specified in the FARG[15:2] field of the EEFC\_FCR. The first page number must be a multiple of 8, 16 or 32 depending on the number of pages to erase at the same time.

- Erase Sector (ES): A full memory sector is erased. Sector size depends on the Flash memory. EEFC\_FCR.FARG must be set with a page number that is in the sector to be erased.

If the processor is fetching code from the Flash memory while the EPA or ES command is being executed, the processor accesses are stalled until the EPA command is completed. To avoid stalling the processor, the code can be run out of internal SRAM.

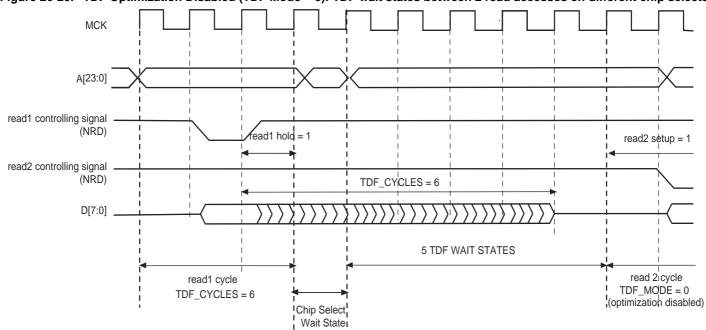

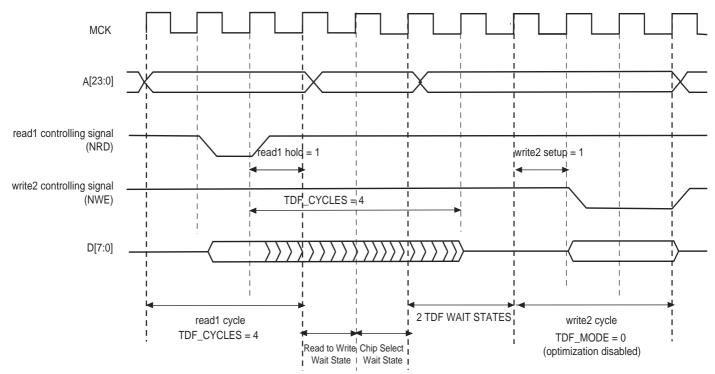

Figure 26-20. TDF Optimization Disabled (TDF Mode = 0): TDF wait states between 2 read accesses on different chip selects

Figure 26-21. TDF Mode = 0: TDF wait states between a read and a write access on different chip selects

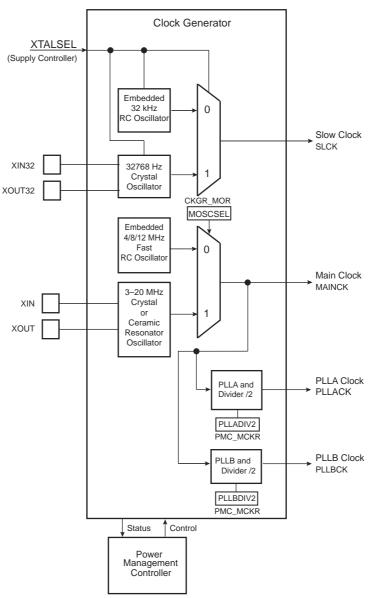

# 28.3 Block Diagram

Atmel

#### 31.4 **Product Dependencies**

# 31.4.1 Pin Multiplexing

Each pin is configurable, depending on the product, as either a general-purpose I/O line only, or as an I/O line multiplexed with one or two peripheral I/Os. As the multiplexing is hardware defined and thus product-dependent, the hardware designer and programmer must carefully determine the configuration of the PIO Controllers required by their application. When an I/O line is general-purpose only, i.e., not multiplexed with any peripheral I/O, programming of the PIO Controller regarding the assignment to a peripheral has no effect and only the PIO Controller can control how the pin is driven by the product.

## 31.4.2 Power Management

The Power Management Controller controls the peripheral clock in order to save power. Writing any of the registers of the user interface does not require the peripheral clock to be enabled. This means that the configuration of the I/O lines does not require the peripheral clock to be enabled.

However, when the clock is disabled, not all of the features of the PIO Controller are available, including glitch filtering. Note that the input change interrupt, the interrupt modes on a programmable event and the read of the pin level require the clock to be validated.

After a hardware reset, the peripheral clock is disabled by default.

The user must configure the Power Management Controller before any access to the input line information.

## 31.4.3 Interrupt Sources

For interrupt handling, the PIO Controllers are considered as user peripherals. This means that the PIO Controller interrupt lines are connected among the interrupt sources. Refer to the PIO Controller peripheral identifier in the Peripheral Identifiers table to identify the interrupt sources dedicated to the PIO Controllers. Using the PIO Controller requires the Interrupt Controller to be programmed first.

The PIO Controller interrupt can be generated only if the peripheral clock is enabled.

| Table 31-2. Peripheral IDS |    |  |  |  |  |

|----------------------------|----|--|--|--|--|

| Instance                   | ID |  |  |  |  |

| PIOA                       | 11 |  |  |  |  |

| PIOB                       | 12 |  |  |  |  |

| PIOC                       | 13 |  |  |  |  |

| Table 31-2. | Perip | heral IDs |

|-------------|-------|-----------|

| Instanc     | е     | ID        |

|             |       |           |

# 31.6.18 PIO Multi-driver Enable Register

Name: PIO\_MDER

# Address: 0x400E0E50 (PIOA), 0x400E1050 (PIOB), 0x400E1250 (PIOC)

Access: Write-only

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

| P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

| P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

This register can only be written if the WPEN bit is cleared in the PIO Write Protection Mode Register.

# • P0-P31: Multi-drive Enable

0: No effect.

1: Enables multi-drive on the I/O line.

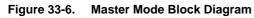

# 33.7.3.1 Master Mode Block Diagram

# 34.3 List of Abbreviations

| Table 34-2. Abbreviations |                         |

|---------------------------|-------------------------|

| Abbreviation              | Description             |

| TWI                       | Two-wire Interface      |

| A                         | Acknowledge             |

| NA                        | Non Acknowledge         |

| Р                         | Stop                    |

| S                         | Start                   |

| Sr                        | Repeated Start          |

| SADR                      | Slave Address           |

| ADR                       | Any address except SADR |

| R                         | Read                    |

| W                         | Write                   |

# Table 34-2.Abbreviations

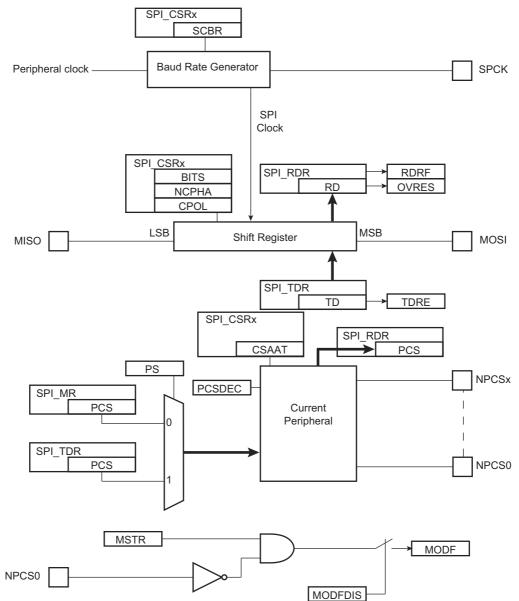

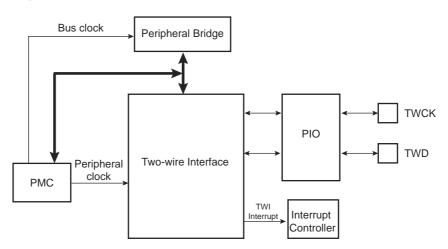

# 34.4 Block Diagram

Figure 34-1. Block Diagram

# 34.5 I/O Lines Description

#### Table 34-3. I/O Lines Description

| Name | Description                                                     | Туре         |

|------|-----------------------------------------------------------------|--------------|

| TWD  | Two-wire Serial Data (drives external serial data line – SDA)   | Input/Output |

| TWCK | Two-wire Serial Clock (drives external serial clock line – SCL) | Input/Output |

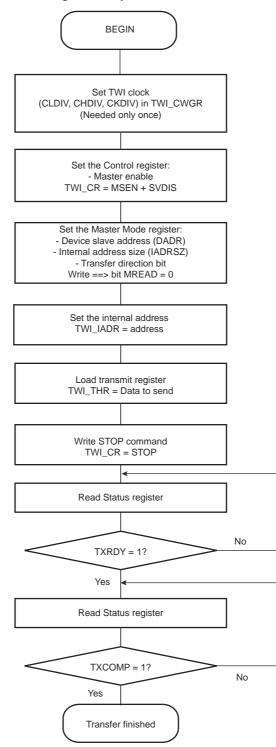

Figure 34-15. TWI Write Operation with Single Data Byte and Internal Address

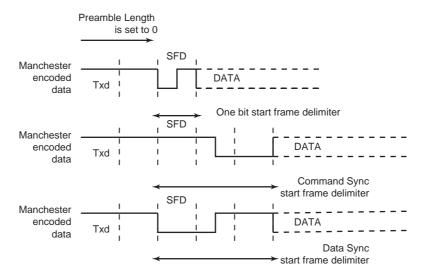

#### **Drift Compensation**

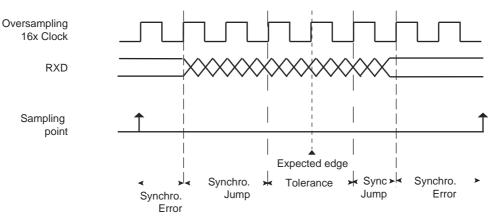

Drift compensation is available only in 16X oversampling mode. An hardware recovery system allows a larger clock drift. To enable the hardware system, the bit in the USART\_MAN register must be set. If the RXD edge is one 16X clock cycle from the expected edge, this is considered as normal jitter and no corrective actions is taken. If the RXD event is between 4 and 2 clock cycles before the expected edge, then the current period is shortened by one clock cycle. If the RXD event is between 2 and 3 clock cycles after the expected edge, then the current period is lengthened by one clock cycle. These intervals are considered to be drift and so corrective actions are automatically taken.

#### 36.6.3.3 Asynchronous Receiver

If the USART is programmed in Asynchronous operating mode (SYNC = 0), the receiver oversamples the RXD input line. The oversampling is either 16 or 8 times the baud rate clock, depending on the OVER bit in the US\_MR.

The receiver samples the RXD line. If the line is sampled during one half of a bit time to 0, a start bit is detected and data, parity and stop bits are successively sampled on the bit rate clock.

If the oversampling is 16 (OVER = 0), a start is detected at the eighth sample to 0. Data bits, parity bit and stop bit are assumed to have a duration corresponding to 16 oversampling clock cycles. If the oversampling is 8 (OVER = 1), a start bit is detected at the fourth sample to 0. Data bits, parity bit and stop bit are assumed to have a duration corresponding to 8 oversampling clock cycles.

Atmel

# • FCS: Force SPI Chip Select

Applicable if USART operates in SPI master mode (USART\_MODE = 0xE):

0: No effect.

1: Forces the Slave Select Line NSS (RTS pin) to 0, even if USART is not transmitting, in order to address SPI slave devices supporting the CSAAT mode (Chip Select Active After Transfer).

# • RCS: Release SPI Chip Select

Applicable if USART operates in SPI master mode (USART\_MODE = 0xE):

- 0: No effect.

- 1: Releases the Slave Select Line NSS (RTS pin).

# 39.7.6 PWM Interrupt Disable Register 1

| Name:    | PWM_IDR1   |    |    |              |              |              |        |

|----------|------------|----|----|--------------|--------------|--------------|--------|

| Address: | 0x40020014 |    |    |              |              |              |        |

| Access:  | Write-only |    |    |              |              |              |        |

| 31       | 30         | 29 | 28 | 27           | 26           | 25           | 24     |

| -        | -          | -  | -  | -            | -            | -            | -      |

| 23       | 22         | 21 | 20 | 19<br>FCHID3 | 18<br>FCHID2 | 17<br>FCHID1 |        |

| -        | -          | _  | -  | FCHID3       | FCHIDZ       | FCHIDT       | FCHID0 |

| 15       | 14         | 13 | 12 | 11           | 10           | 9            | 8      |

| _        | -          | _  | —  | -            | -            | -            | -      |

| 7        | 6          | 5  | 4  | 3            | 2            | 1            | 0      |

| -        | -          | _  | -  | CHID3        | CHID2        | CHID1        | CHID0  |

CHIDx: Counter Event on Channel x Interrupt Disable

• FCHIDx: Fault Protection Trigger on Channel x Interrupt Disable

# 39.7.35 PWM Comparison x Mode Update Register

## Name: PWM\_CMPMUPDx

Address: 0x4002013C [0], 0x4002014C [1], 0x4002015C [2], 0x4002016C [3], 0x4002017C [4], 0x4002018C [5], 0x4002019C [6], 0x400201AC [7]

| Access: | Write-only |     |    |        |      |      |        |  |

|---------|------------|-----|----|--------|------|------|--------|--|

| 31      | 30         | 29  | 28 | 27     | 26   | 25   | 24     |  |

| _       | _          | —   | —  | —      | —    | —    | —      |  |

| 23      | 22         | 21  | 20 | 19     | 18   | 17   | 16     |  |

| _       | -          | _   | _  |        | CUPF | RUPD |        |  |

| 15      | 14         | 13  | 12 | 11     | 10   | 9    | 8      |  |

| —       | -          | _   | -  | CPRUPD |      |      |        |  |

| 7       | 6          | 5   | 4  | 3      | 2    | 1    | 0      |  |

|         | CTR        | UPD |    | -      | -    | -    | CENUPD |  |

This register acts as a double buffer for the CEN, CTR, CPR and CUPR values. This prevents an unexpected comparison x match.

## • CENUPD: Comparison x Enable Update

0: The comparison x is disabled and can not match.

1: The comparison x is enabled and can match.

# • CTRUPD: Comparison x Trigger Update

The comparison x is performed when the value of the comparison x period counter (CPRCNT) reaches the value defined by CTR.

## • CPRUPD: Comparison x Period Update

CPR defines the maximum value of the comparison x period counter (CPRCNT). The comparison x value is performed periodically once every CPR+1 periods of the channel 0 counter.

# • CUPRUPD: Comparison x Update Period Update

Defines the time between each update of the comparison x mode and the comparison x value. This time is equal to CUPR+1 periods of the channel 0 counter.

- WAKEUP: Disable USB Bus Interrupt

- 0: No effect

- 1: Disables USB Bus Wakeup Interrupt

# 42.7.7 ADC Channel Status Register

| Name:    | ADC_CHSR   |      |      |      |      |     |     |

|----------|------------|------|------|------|------|-----|-----|

| Address: | 0x40038018 |      |      |      |      |     |     |

| Access:  | Read-only  |      |      |      |      |     |     |

| 31       | 30         | 29   | 28   | 27   | 26   | 25  | 24  |

| _        | -          | -    | -    | -    | -    | -   | -   |

| 23       | 22         | 21   | 20   | 19   | 18   | 17  | 16  |

| —        | —          | —    | -    | —    | —    | —   | -   |

| 15       | 14         | 13   | 12   | 11   | 10   | 9   | 8   |

| CH15     | CH14       | CH13 | CH12 | CH11 | CH10 | CH9 | CH8 |

| 7        | 6          | 5    | 4    | 3    | 2    | 1   | 0   |

| CH7      | CH6        | CH5  | CH4  | CH3  | CH2  | CH1 | CH0 |

# • CHx: Channel x Status

0: The corresponding channel is disabled.

1: The corresponding channel is enabled.

| Symbol                | Parameter                             | Conditions                                                                                       | Min | Тур | Max | Unit |  |

|-----------------------|---------------------------------------|--------------------------------------------------------------------------------------------------|-----|-----|-----|------|--|

| R <sub>PULLDOWN</sub> | Pull-down Resistor                    | PA0-PA31, PB0-PB14, PC0-PC31, NRST                                                               | 70  | 100 | 130 | kΩ   |  |

| R <sub>ODT</sub>      | On-die Series<br>Termination Resistor | PA4-PA31, PB0-PB9, PB12-PB14, PC0-PC31                                                           | _   | 36  | _   | Ω    |  |

|                       |                                       | PA0-PA3                                                                                          | _   | 18  | _   |      |  |

| I <sub>CC</sub>       | Flash Active Current on VDDCORE       | Random 144-bit Read @ 25°C:<br>Maximum read frequency at VDDCORE = 1.2V,<br>VDDIO = 3.3V         | _   | 16  | 25  |      |  |

|                       |                                       | Random 72-bit Read @ 25°C:<br>Maximum read frequency at VDDCORE = 1.2V,<br>VDDIO = 3.3V          | _   | 10  | 18  | mA   |  |

|                       |                                       | Program <sup>(3)</sup> onto VDDCORE = 1.2V,<br>VDDIO = 3.3V @ 25°C                               | _   | 3   | 5   |      |  |

| I <sub>CC33</sub>     | Flash Active Current on<br>VDDIO      | Random 144-bit read:<br>Maximum read frequency at VDDCORE = 1.2V,<br>VDDIO = 3.3V @ 25°C         | _   | 3   | 16  | mA   |  |

|                       |                                       | Random 72-bit read:<br>Maximum read frequency at VDDCORE = 1.2V,<br>VDDIO = $3.3V @ 25^{\circ}C$ | _   | 3   | 5   |      |  |

|                       |                                       | Program <sup>(3)</sup> onto VDDCORE = 1.2V,<br>VDDIO = 3.3V @ 25°C                               | _   | 10  | 15  |      |  |

Table 44-3. DC Characteristics (Continued)

Note: 1. PA[4–11], PA[15–25], PB[0–9], PB[12–14], PC[0–31]

2. Refer to Section 5.2.2 "VDDIO Versus VDDIN"

3. The Flash programming characteristics are applicable at operating temperature range:  $T_A = -40$  to 85 °C.