# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                           |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 120MHz                                                                    |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, Memory Card, SPI, SSC, UART/USART, USB   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                |

| Number of I/O              | 79                                                                        |

| Program Memory Size        | 1MB (1M x 8)                                                              |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 160K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                              |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                     |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 100-LQFP                                                                  |

| Supplier Device Package    | 100-LQFP (14x14)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4sa16ca-au |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

REVSH Reverse byte order in the bottom halfword, and sign extend to 32 bits. RBIT Reverse the bit order in a 32-bit word.

cond is an optional condition code, see "Conditional Execution".

Rd is the destination register.

Rn is the register holding the operand.

#### Operation

Use these instructions to change endianness of data:

REV converts either:

- 32-bit big-endian data into little-endian data

- 32-bit little-endian data into big-endian data.

REV16 converts either:

- 16-bit big-endian data into little-endian data

- 16-bit little-endian data into big-endian data.

REVSH converts either:

- 16-bit signed big-endian data into 32-bit signed little-endian data

- 16-bit signed little-endian data into 32-bit signed big-endian data.

Restrictions

Do not use SP and do not use PC.

**Condition Flags**

These instructions do not change the flags.

Examples

REV R3, R7; Reverse byte order of value in R7 and write it to R3 REV16 R0, R0; Reverse byte order of each 16-bit halfword in R0 REVSH R0, R5; Reverse Signed Halfword REVHS R3, R7; Reverse with Higher or Same condition RBIT R7, R8; Reverse bit order of value in R8 and write the result to R7.

# 12.6.8 Packing and Unpacking Instructions

The table below shows the instructions that operate on packing and unpacking data.

| Mnemonic | Description                           |

|----------|---------------------------------------|

| РКН      | Pack Halfword                         |

| SXTAB    | Extend 8 bits to 32 and add           |

| SXTAB16  | Dual extend 8 bits to 16 and add      |

| SXTAH    | Extend 16 bits to 32 and add          |

| SXTB     | Sign extend a byte                    |

| SXTB16   | Dual extend 8 bits to 16 and add      |

| SXTH     | Sign extend a halfword                |

| UXTAB    | Extend 8 bits to 32 and add           |

| UXTAB16  | Dual extend 8 bits to 16 and add      |

| UXTAH    | Extend 16 bits to 32 and add          |

| UXTB     | Zero extend a byte                    |

| UXTB16   | Dual zero extend 8 bits to 16 and add |

| UXTH     | Zero extend a halfword                |

Table 12-23.

Packing and Unpacking Instructions

Restrictions

Do not use SP and do not use PC.

**Condition Flags**

These instructions do not affect the flags.

Examples

| SXTAH | R4, | R8, | R6, | ROR | #16 | ; | Rotates R6 right by 16 bits, obtains bottom  |

|-------|-----|-----|-----|-----|-----|---|----------------------------------------------|

|       |     |     |     |     |     | ; | halfword, sign extends to 32 bits, adds      |

|       |     |     |     |     |     | ; | R8,and writes to R4                          |

| UXTAB | R3, | R4, | R10 |     |     | ; | Extracts bottom byte of R10 and zero extends |

|       |     |     |     |     |     | ; | to 32 bits, adds R4, and writes to R3.       |

# 14.5.3 Reset Controller Mode Register

| Name:    | RSTC_MR    |    |         |    |    |     |        |

|----------|------------|----|---------|----|----|-----|--------|

| Address: | 0x400E1408 |    |         |    |    |     |        |

| Access:  | Read/Write |    |         |    |    |     |        |

| 31       | 30         | 29 | 28      | 27 | 26 | 25  | 24     |

|          |            |    | KI      | ΞY |    |     |        |

| 23       | 22         | 21 | 20      | 19 | 18 | 17  | 16     |

| —        | -          | -  | -       | —  | —  | _   | -      |

| 15       | 14         | 13 | 12      | 11 | 10 | 9   | 8      |

| -        | -          | _  | _       |    | ER | STL |        |

| 7        | 6          | 5  | 4       | 3  | 2  | 1   | 0      |

| -        | -          | _  | URSTIEN | _  | _  | _   | URSTEN |

This register can only be written if the WPEN bit is cleared in the System Controller Write Protection Mode Register (SYSC\_WPMR).

#### • URSTEN: User Reset Enable

0: The detection of a low level on the NRST pin does not generate a user reset.

1: The detection of a low level on the NRST pin triggers a user reset.

#### • URSTIEN: User Reset Interrupt Enable

0: USRTS bit in RSTC\_SR at 1 has no effect on rstc\_irq.

1: USRTS bit in RSTC\_SR at 1 asserts rstc\_irq if URSTEN = 0.

#### • ERSTL: External Reset Length

This field defines the external reset length. The external reset is asserted during a time of  $2^{(\text{ERSTL+1})}$  slow clock cycles. This allows assertion duration to be programmed between 60 µs and 2 seconds. Note that synchronization cycles must also be considered when calculating the actual reset length as previously described.

#### • KEY: Write Access Password

| Value | Name   | Description                                                                             |

|-------|--------|-----------------------------------------------------------------------------------------|

| 0xA5  | PASSWD | Writing any other value in this field aborts the write operation.<br>Always reads as 0. |

#### Table 20-2. Set of Commands (Continued)

| Command                      | Value | Mnemonic |

|------------------------------|-------|----------|

| Get GPNVM bit                | 0x0D  | GGPB     |

| Start read unique identifier | 0x0E  | STUI     |

| Stop read unique identifier  | 0x0F  | SPUI     |

| Get CALIB bit                | 0x10  | GCALB    |

| Erase sector                 | 0x11  | ES       |

| Write user signature         | 0x12  | WUS      |

| Erase user signature         | 0x13  | EUS      |

| Start read user signature    | 0x14  | STUS     |

| Stop read user signature     | 0x15  | SPUS     |

In order to execute one of these commands, select the required command using the FCMD field in the Flash Command register (EEFC\_FCR). As soon as EEFC\_FCR is written, the FRDY flag and the FVALUE field in the Flash Result register (EEFC\_FRR) are automatically cleared. Once the current command has completed, the FRDY flag is automatically set. If an interrupt has been enabled by setting the bit EEFC\_FMR.FRDY, the corresponding interrupt line of the interrupt controller is activated. (Note that this is true for all commands except for the STUI command. The FRDY flag is not set when the STUI command has completed.)

All the commands are protected by the same keyword, which must be written in the eight highest bits of EEFC\_FCR.

Writing EEFC\_FCR with data that does not contain the correct key and/or with an invalid command has no effect on the whole memory plane, but the FCMDE flag is set in the Flash Status register (EEFC\_FSR). This flag is automatically cleared by a read access to EEFC\_FSR.

When the current command writes or erases a page in a locked region, the command has no effect on the whole memory plane, but the FLOCKE flag is set in EEFC\_FSR. This flag is automatically cleared by a read access to EEFC\_FSR.

# 20.5.3 EEFC Flash Status Register

| Address: | 0x400E0A08 (0), 0x400E0C08 (* | 1) |

|----------|-------------------------------|----|

|----------|-------------------------------|----|

Access: Read-only

| 31 | 30 | 29 | 28 | 27    | 26     | 25    | 24   |

|----|----|----|----|-------|--------|-------|------|

| -  | -  | -  | -  | -     | -      | -     | -    |

| 23 | 22 | 21 | 20 | 19    | 18     | 17    | 16   |

| -  | -  | -  | —  | -     | -      | -     | -    |

| 15 | 14 | 13 | 12 | 11    | 10     | 9     | 8    |

| -  | -  | -  | -  | -     | -      | -     | -    |

| 7  | 6  | 5  | 4  | 3     | 2      | 1     | 0    |

| -  | -  | -  | -  | FLERR | FLOCKE | FCMDE | FRDY |

#### • FRDY: Flash Ready Status (cleared when Flash is busy)

- 0: The EEFC is busy.

- 1: The EEFC is ready to start a new command.

When set, this flag triggers an interrupt if the FRDY flag is set in EEFC\_FMR.

This flag is automatically cleared when the EEFC is busy.

# • FCMDE: Flash Command Error Status (cleared on read or by writing EEFC\_FCR)

- 0: No invalid commands and no bad keywords were written in EEFC\_FMR.

- 1: An invalid command and/or a bad keyword was/were written in EEFC\_FMR.

# • FLOCKE: Flash Lock Error Status (cleared on read)

- 0: No programming/erase of at least one locked region has happened since the last read of EEFC\_FSR.

- 1: Programming/erase of at least one locked region has happened since the last read of EEFC\_FSR.

This flag is automatically cleared when EEFC\_FSR is read or EEFC\_FCR is written.

# • FLERR: Flash Error Status (cleared when a programming operation starts)

0: No Flash memory error occurred at the end of programming (EraseVerify or WriteVerify test has passed).

1: A Flash memory error occurred at the end of programming (EraseVerify or WriteVerify test has failed).

# 23.7.5 CRCCU DMA Interrupt Enable Register

| Name:    | CRCCU_DMA_I | ER |    |    |    |    |        |

|----------|-------------|----|----|----|----|----|--------|

| Address: | 0x40044014  |    |    |    |    |    |        |

| Access:  | Write-only  |    |    |    |    |    |        |

| 31       | 30          | 29 | 28 | 27 | 26 | 25 | 24     |

| _        | -           | _  | -  | -  | -  | _  | -      |

| 23       | 22          | 21 | 20 | 19 | 18 | 17 | 16     |

| -        | -           | _  | -  | -  | -  | _  | -      |

| 15       | 14          | 13 | 12 | 11 | 10 | 9  | 8      |

| -        | -           | -  | -  | -  | -  | -  | -      |

| 7        | 6           | 5  | 4  | 3  | 2  | 1  | 0      |

| _        | -           | -  | -  | _  | _  | _  | DMAIER |

# • DMAIER: Interrupt Enable

0: No effect

1: Enable interrupt

# 29.17.15PMC Interrupt Disable Register

| Name:<br>Address: | PMC_IDR<br>0x400E0464 |    |    |         |             |               |                |

|-------------------|-----------------------|----|----|---------|-------------|---------------|----------------|

| Access:           | Write-only            |    |    |         |             |               |                |

| 31                | 30                    | 29 | 28 | 27      | 26          | 25            | 24             |

| _                 | —                     | _  | _  | _       | _           | _             | —              |

| 23                | 22                    | 21 | 20 | 19<br>— | 18<br>CFDEV | 17<br>MOSCRCS | 16<br>MOSCSELS |

| 15                | 14                    | 13 | 12 | 11      | 10          | 9             | 8              |

| _                 | -                     | —  | -  | -       | PCKRDY2     | PCKRDY1       | PCKRDY0        |

| 7                 | 6                     | 5  | 4  | 3       | 2           | 1             | 0              |

| _                 | -                     | _  | _  | MCKRDY  | LOCKB       | LOCKA         | MOSCXTS        |

The following configuration values are valid for all listed bit names of this register:

0: No effect.

- 1: Disables the corresponding interrupt.

- MOSCXTS: Main Crystal Oscillator Status Interrupt Disable

- LOCKA: PLLA Lock Interrupt Disable

- LOCKB: PLLB Lock Interrupt Disable

- MCKRDY: Master Clock Ready Interrupt Disable

- PCKRDYx: Programmable Clock Ready x Interrupt Disable

- MOSCSELS: Main Oscillator Selection Status Interrupt Disable

- MOSCRCS: Main On-Chip RC Status Interrupt Disable

- CFDEV: Clock Failure Detector Event Interrupt Disable

| Value | Name  | Description |

|-------|-------|-------------|

| 11    | -     | Reserved    |

| 12    | 1024K | 1024 Kbytes |

| 13    | -     | Reserved    |

| 14    | 2048K | 2048 Kbytes |

| 15    | -     | Reserved    |

# NVPSIZ2: Second Nonvolatile Program Memory Size

| Value | Name  | Description |

|-------|-------|-------------|

| 0     | NONE  | None        |

| 1     | 8K    | 8 Kbytes    |

| 2     | 16K   | 16 Kbytes   |

| 3     | 32K   | 32 Kbytes   |

| 4     | -     | Reserved    |

| 5     | 64K   | 64 Kbytes   |

| 6     | -     | Reserved    |

| 7     | 128K  | 128 Kbytes  |

| 8     | -     | Reserved    |

| 9     | 256K  | 256 Kbytes  |

| 10    | 512K  | 512 Kbytes  |

| 11    | -     | Reserved    |

| 12    | 1024K | 1024 Kbytes |

| 13    | -     | Reserved    |

| 14    | 2048K | 2048 Kbytes |

| 15    | _     | Reserved    |

#### • SRAMSIZ: Internal SRAM Size

| Value | Name | Description |

|-------|------|-------------|

| 0     | 48K  | 48 Kbytes   |

| 1     | 192K | 192 Kbytes  |

| 2     | 384K | 384 Kbytes  |

| 3     | 6K   | 6 Kbytes    |

| 4     | 24K  | 24 Kbytes   |

| 5     | 4K   | 4 Kbytes    |

| 6     | 80K  | 80 Kbytes   |

| 7     | 160K | 160 Kbytes  |

| 8     | 8K   | 8 Kbytes    |

| 9     | 16K  | 16 Kbytes   |

| 10    | 32K  | 32 Kbytes   |

| 11    | 64K  | 64 Kbytes   |

# 31.6.44 PIO Fall/Rise - Low/High Status Register

Name: PIO\_FRLHSR

Address: 0x400E0ED8 (PIOA), 0x400E10D8 (PIOB), 0x400E12D8 (PIOC)

Access: Read-only

| 31  | 30   | 29  | 28  | 27   | 26  | 25  | 24       |

|-----|------|-----|-----|------|-----|-----|----------|

| P31 | P30  | P29 | P28 | P27  | P26 | P25 | P24      |

| 23  | 22   | 21  | 20  | 19   | 18  | 17  | 16       |

| P23 | P22  | P21 | P20 | P19  | P18 | P17 | P16      |

| 15  | 14   | 13  | 12  | 11   | 10  | 9   | <u>م</u> |

| P15 | P14  | P13 | P12 | P11  | P10 | P9  | °<br>P8  |

| 115 | 1 14 | 115 | 112 | I II | 110 | 19  | FO       |

| 7   | 6    | 5   | 4   | 3    | 2   | 1   | 0        |

| P7  | P6   | P5  | P4  | P3   | P2  | P1  | P0       |

# • P0–P31: Edge/Level Interrupt Source Selection

0: The interrupt source is a falling edge detection (if PIO\_ELSR = 0) or low-level detection event (if PIO\_ELSR = 1).

1: The interrupt source is a rising edge detection (if PIO\_ELSR = 0) or high-level detection event (if PIO\_ELSR = 1).

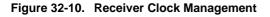

#### 32.8.1.3 Receiver Clock Management

The receiver clock is generated from the transmitter clock or the divider clock or an external clock scanned on the RK I/O pad. The Receive Clock is selected by the CKS field in SSC\_RCMR (Receive Clock Mode Register). Receive Clocks can be inverted independently by the CKI bits in SSC\_RCMR.

The receiver can also drive the RK I/O pad continuously or be limited to the actual data transfer. The clock output is configured by the SSC\_RCMR. The Receive Clock Inversion (CKI) bits have no effect on the clock outputs. Programming the SSC\_RCMR to select RK pin (CKS field) and at the same time Continuous Receive Clock (CKO field) can lead to unpredictable results.

#### 32.8.1.4 Serial Clock Ratio Considerations

The Transmitter and the Receiver can be programmed to operate with the clock signals provided on either the TK or RK pins. This allows the SSC to support many slave-mode data transfers. In this case, the maximum clock speed allowed on the RK pin is:

- Peripheral clock divided by 2 if Receiver Frame Synchro is input

- Peripheral clock divided by 3 if Receiver Frame Synchro is output

In addition, the maximum clock speed allowed on the TK pin is:

- Peripheral clock divided by 6 if Transmit Frame Synchro is input

- Peripheral clock divided by 2 if Transmit Frame Synchro is output

#### 32.8.2 Transmitter Operations

A transmitted frame is triggered by a start event and can be followed by synchronization data before data transmission.

The start event is configured by setting the SSC\_TCMR. See Section 32.8.4 "Start" on page 652.

The frame synchronization is configured setting the Transmit Frame Mode Register (SSC\_TFMR). See Section 32.8.5 "Frame Sync" on page 654.

To transmit data, the transmitter uses a shift register clocked by the transmitter clock signal and the start mode selected in the SSC\_TCMR. Data is written by the application to the SSC\_THR then transferred to the shift register according to the data format selected.

Atmel

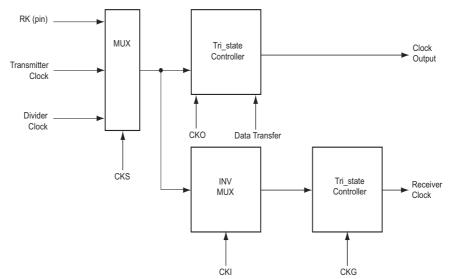

#### 34.7.3 Master Mode

#### 34.7.3.1 Definition

The master is the device that starts a transfer, generates a clock and stops it.

#### 34.7.3.2 Application Block Diagram

#### Figure 34-4. Master Mode Typical Application Block Diagram

\* Rp: Pull-up value as given by the I<sup>2</sup>C Standard

#### 34.7.3.3 Programming Master Mode

The following fields must be programmed before entering Master mode:

- 1. TWI\_MMR.DADR (+ IADRSZ + IADR if a 10-bit device is addressed): The device address is used to access slave devices in Read or Write mode.

- 2. TWI\_CWGR.CKDIV + CHDIV + CLDIV: Clock waveform.

- 3. TWI\_CR.SVDIS: Disables the Slave mode

- 4. TWI\_CR.MSEN: Enables the Master mode

- Note: If the TWI is already in Master mode, the device address (DADR) can be configured without disabling the Master mode.

#### 34.7.3.4 Master Transmitter Mode

After the master initiates a START condition when writing into the Transmit Holding register (TWI\_THR), it sends a 7-bit slave address, configured in the Master Mode register (DADR in TWI\_MMR), to notify the slave device. The bit following the slave address indicates the transfer direction—0 in this case (MREAD = 0 in TWI\_MMR).

The TWI transfers require the slave to acknowledge each received byte. During the acknowledge clock pulse (9th pulse), the master releases the data line (HIGH), enabling the slave to pull it down in order to generate the acknowledge. If the slave does not acknowledge the byte, then the Not Acknowledge flag (NACK) is set in the TWI Status Register (TWI\_SR) of the master and a STOP condition is sent. The NACK flag must be cleared by reading the TWI Status Register (TWI\_SR) before the next write into the TWI Transmit Holding Register(TWI\_THR). As with the other status bits, an interrupt can be generated if enabled in the Interrupt Enable register (TWI\_IER). If the slave acknowledges the byte, the data written in the TWI\_THR is then shifted in the internal shifter and transferred. When an acknowledge is detected, the TXRDY bit is set until a new write in the TWI\_THR.

TXRDY is used as Transmit Ready for the PDC transmit channel.

While no new data is written in the TWI\_THR, the serial clock line (SCL) is tied low. When new data is written in the TWI\_THR, the TWCK/SCL is released and the data is sent. Setting the STOP bit in TWI\_CR generates a STOP condition.

# 34.8.7 TWI Interrupt Enable Register

| Name:    | TWI_IER         |                |       |        |        |        |        |

|----------|-----------------|----------------|-------|--------|--------|--------|--------|

| Address: | 0x40018024 (0), | , 0x4001C024 ( | 1)    |        |        |        |        |

| Access:  | Write-only      |                |       |        |        |        |        |

| 31       | 30              | 29             | 28    | 27     | 26     | 25     | 24     |

| —        | -               | -              | -     | -      | -      | -      | —      |

|          |                 |                |       |        |        |        |        |

| 23       | 22              | 21             | 20    | 19     | 18     | 17     | 16     |

| -        | -               | -              | -     | -      | -      | -      | -      |

|          | -               | -              | -     | -      | -      | -      |        |

| 15       | 14              | 13             | 12    | 11     | 10     | 9      | 8      |

| TXBUFE   | RXBUFF          | ENDTX          | ENDRX | EOSACC | SCL_WS | ARBLST | NACK   |

|          |                 |                |       |        |        |        |        |

| 7        | 6               | 5              | 4     | 3      | 2      | 1      | 0      |

| _        | OVRE            | GACC           | SVACC | _      | TXRDY  | RXRDY  | TXCOMP |

The following configuration values are valid for all listed bit names of this register:

0: No effect.

- 1: Enables the corresponding interrupt.

- TXCOMP: Transmission Completed Interrupt Enable

- RXRDY: Receive Holding Register Ready Interrupt Enable

- TXRDY: Transmit Holding Register Ready Interrupt Enable

- SVACC: Slave Access Interrupt Enable

- GACC: General Call Access Interrupt Enable

- OVRE: Overrun Error Interrupt Enable

- NACK: Not Acknowledge Interrupt Enable

- ARBLST: Arbitration Lost Interrupt Enable

- SCL\_WS: Clock Wait State Interrupt Enable

- EOSACC: End Of Slave Access Interrupt Enable

- ENDRX: End of Receive Buffer Interrupt Enable

- ENDTX: End of Transmit Buffer Interrupt Enable

- RXBUFF: Receive Buffer Full Interrupt Enable

- TXBUFE: Transmit Buffer Empty Interrupt Enable

# 35.6.7 UART Receiver Holding Register

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Name:    | UART_RHR       |              |     |     |    |    |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------|--------------|-----|-----|----|----|----|

| 31       30       29       28       27       26       25       24         -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       - <td< th=""><th>Address:</th><th>0x400E0618 (0)</th><th>, 0x400E0818</th><th>(1)</th><th></th><th></th><th></th><th></th></td<> | Address: | 0x400E0618 (0) | , 0x400E0818 | (1) |     |    |    |    |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Access:  | Read-only      |              |     |     |    |    |    |

| 23     22     21     20     19     18     17     16       -     -     -     -     -     -     -     -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 31       | 30             | 29           | 28  | 27  | 26 | 25 | 24 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _        | _              | -            | _   | _   | -  | _  | -  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 23       | 22             | 21           | 20  | 19  | 18 | 17 | 16 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -        |                | -            | -   | -   | -  | _  | -  |

| <u>15 14 13 12 11 10 9 8</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 15       | 14             | 13           | 12  | 11  | 10 | 9  | 8  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _        | -              | -            | -   | -   | -  | -  | -  |

| 7 6 5 4 3 2 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7        | 6              | 5            | 4   | 3   | 2  | 1  | 0  |

| RXCHR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |                |              | RX  | CHR |    |    |    |

#### • RXCHR: Received Character

Last received character if RXRDY is set.

# • LDBDIS: Counter Clock Disable with RB Loading

0: Counter clock is not disabled when RB loading occurs.

1: Counter clock is disabled when RB loading occurs.

#### • ETRGEDG: External Trigger Edge Selection

| Value | Name    | Description                                   |

|-------|---------|-----------------------------------------------|

| 0     | NONE    | The clock is not gated by an external signal. |

| 1     | RISING  | Rising edge                                   |

| 2     | FALLING | Falling edge                                  |

| 3     | EDGE    | Each edge                                     |

# ABETRG: TIOA or TIOB External Trigger Selection

0: TIOB is used as an external trigger.

1: TIOA is used as an external trigger.

# • CPCTRG: RC Compare Trigger Enable

0: RC Compare has no effect on the counter and its clock.

1: RC Compare resets the counter and starts the counter clock.

#### • WAVE: Waveform Mode

0: Capture mode is enabled.

1: Capture mode is disabled (Waveform mode is enabled).

#### • LDRA: RA Loading Edge Selection

| Value | Name    | Description          |

|-------|---------|----------------------|

| 0     | NONE    | None                 |

| 1     | RISING  | Rising edge of TIOA  |

| 2     | FALLING | Falling edge of TIOA |

| 3     | EDGE    | Each edge of TIOA    |

#### LDRB: RB Loading Edge Selection

| Value | Name    | Description          |

|-------|---------|----------------------|

| 0     | NONE    | None                 |

| 1     | RISING  | Rising edge of TIOA  |

| 2     | FALLING | Falling edge of TIOA |

| 3     | EDGE    | Each edge of TIOA    |

# 37.7.19 TC Fault Mode Register

| Name:    | TC_FMR         |                |     |    |    |       |       |

|----------|----------------|----------------|-----|----|----|-------|-------|

| Address: | 0x400100D8 (0) | , 0x400140D8 ( | (1) |    |    |       |       |

| Access:  | Read/Write     |                |     |    |    |       |       |

| 31       | 30             | 29             | 28  | 27 | 26 | 25    | 24    |

| —        | -              | _              | _   | _  | —  | _     | —     |

|          |                |                |     |    |    |       |       |

| 23       | 22             | 21             | 20  | 19 | 18 | 17    | 16    |

| _        | -              | -              | -   | -  | -  | -     | —     |

|          | -              | -              |     | -  | -  | -     | -     |

| 15       | 14             | 13             | 12  | 11 | 10 | 9     | 8     |

| _        | _              | -              | -   | -  | -  | -     | -     |

|          |                |                |     |    |    |       |       |

| 7        | 6              | 5              | 4   | 3  | 2  | 1     | 0     |

| _        | -              | _              | _   | _  | _  | ENCF1 | ENCF0 |

This register can only be written if the WPEN bit is cleared in the TC Write Protection Mode Register.

# • ENCF0: Enable Compare Fault Channel 0

- 0: Disables the FAULT output source (CPCS flag) from channel 0.

- 1: Enables the FAULT output source (CPCS flag) from channel 0.

#### • ENCF1: Enable Compare Fault Channel 1

- 0: Disables the FAULT output source (CPCS flag) from channel 1.

- 1: Enables the FAULT output source (CPCS flag) from channel 1.

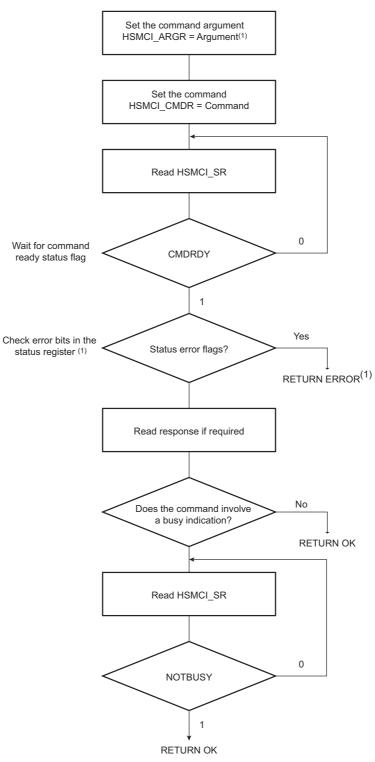

Note: If the command is SEND\_OP\_COND, the CRC error flag is always present (refer to R3 response in the High Speed MultiMedia Card specification).

# 38.14.5 HSMCI Argument Register

| Name:    | HSMCI_ARGR |    |    |    |    |    |    |

|----------|------------|----|----|----|----|----|----|

| Address: | 0x40000010 |    |    |    |    |    |    |

| Access:  | Read/Write |    |    |    |    |    |    |

| 31       | 30         | 29 | 28 | 27 | 26 | 25 | 24 |

|          |            |    | AF | RG |    |    |    |

| 23       | 22         | 21 | 20 | 19 | 18 | 17 | 16 |

|          |            |    | AF | RG |    |    |    |

| 15       | 14         | 13 | 12 | 11 | 10 | 9  | 8  |

|          |            |    | AF | RG |    |    |    |

| 7        | 6          | 5  | 4  | 3  | 2  | 1  | 0  |

|          |            |    | AF | RG |    |    |    |

• ARG: Command Argument

#### 39.6.5.6 Interrupts

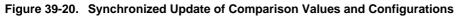

Depending on the interrupt mask in the PWM\_IMR1 and PWM\_IMR2, an interrupt can be generated at the end of the corresponding channel period (CHIDx in the PWM Interrupt Status Register 1 (PWM\_ISR1)), after a fault event (FCHIDx in the PWM\_ISR1), after a comparison match (CMPMx in the PWM\_ISR2), after a comparison update (CMPUx in the PWM\_ISR2) or according to the Transfer mode of the synchronous channels (WRDY, ENDTX, TXBUFE and UNRE in the PWM\_ISR2).

If the interrupt is generated by the flags CHIDx or FCHIDx, the interrupt remains active until a read operation in the PWM\_ISR1 occurs.

If the interrupt is generated by the flags WRDY or UNRE or CMPMx or CMPUx, the interrupt remains active until a read operation in the PWM\_ISR2 occurs.

A channel interrupt is enabled by setting the corresponding bit in PWM\_IER1 and PWM\_IER2. A channel interrupt is disabled by setting the corresponding bit in PWM\_IDR1 and PWM\_IDR2.

# Table 39-6. Register Mapping (Continued)

| Offset      | Register                               | Name         | Access     | Reset |

|-------------|----------------------------------------|--------------|------------|-------|

| 0xC0–0xE0   | Reserved                               | -            | -          | _     |

| 0xE4        | PWM Write Protection Control Register  | PWM_WPCR     | Write-only | -     |

| 0xE8        | PWM Write Protection Status Register   | PWM_WPSR     | Read-only  | 0x0   |

| 0xEC-0xFC   | Reserved                               | _            | _          | _     |

| 0x100–0x128 | Reserved for PDC registers             | _            | -          | _     |

| 0x12C       | Reserved                               | _            | _          | _     |

| 0x130       | PWM Comparison 0 Value Register        | PWM_CMPV0    | Read/Write | 0x0   |

| 0x134       | PWM Comparison 0 Value Update Register | PWM_CMPVUPD0 | Write-only | _     |

| 0x138       | PWM Comparison 0 Mode Register         | PWM_CMPM0    | Read/Write | 0x0   |

| 0x13C       | PWM Comparison 0 Mode Update Register  | PWM_CMPMUPD0 | Write-only | _     |

| 0x140       | PWM Comparison 1 Value Register        | PWM_CMPV1    | Read/Write | 0x0   |

| 0x144       | PWM Comparison 1 Value Update Register | PWM_CMPVUPD1 | Write-only | _     |

| 0x148       | PWM Comparison 1 Mode Register         | PWM_CMPM1    | Read/Write | 0x0   |

| 0x14C       | PWM Comparison 1 Mode Update Register  | PWM_CMPMUPD1 | Write-only | _     |

| 0x150       | PWM Comparison 2 Value Register        | PWM_CMPV2    | Read/Write | 0x0   |

| 0x154       | PWM Comparison 2 Value Update Register | PWM_CMPVUPD2 | Write-only | _     |

| 0x158       | PWM Comparison 2 Mode Register         | PWM_CMPM2    | Read/Write | 0x0   |

| 0x15C       | PWM Comparison 2 Mode Update Register  | PWM_CMPMUPD2 | Write-only | _     |

| 0x160       | PWM Comparison 3 Value Register        | PWM_CMPV3    | Read/Write | 0x0   |

| 0x164       | PWM Comparison 3 Value Update Register | PWM_CMPVUPD3 | Write-only | _     |

| 0x168       | PWM Comparison 3 Mode Register         | PWM_CMPM3    | Read/Write | 0x0   |

| 0x16C       | PWM Comparison 3 Mode Update Register  | PWM_CMPMUPD3 | Write-only | _     |

| 0x170       | PWM Comparison 4 Value Register        | PWM_CMPV4    | Read/Write | 0x0   |

| 0x174       | PWM Comparison 4 Value Update Register | PWM_CMPVUPD4 | Write-only | _     |

| 0x178       | PWM Comparison 4 Mode Register         | PWM_CMPM4    | Read/Write | 0x0   |

| 0x17C       | PWM Comparison 4 Mode Update Register  | PWM_CMPMUPD4 | Write-only | _     |

| 0x180       | PWM Comparison 5 Value Register        | PWM_CMPV5    | Read/Write | 0x0   |

| 0x184       | PWM Comparison 5 Value Update Register | PWM_CMPVUPD5 | Write-only | _     |

| 0x188       | PWM Comparison 5 Mode Register         | PWM_CMPM5    | Read/Write | 0x0   |

| 0x18C       | PWM Comparison 5 Mode Update Register  | PWM_CMPMUPD5 | Write-only | _     |

| 0x190       | PWM Comparison 6 Value Register        | PWM_CMPV6    | Read/Write | 0x0   |

| 0x194       | PWM Comparison 6 Value Update Register | PWM_CMPVUPD6 | Write-only | _     |

| 0x198       | PWM Comparison 6 Mode Register         | PWM_CMPM6    | Read/Write | 0x0   |

| 0x19C       | PWM Comparison 6 Mode Update Register  | PWM_CMPMUPD6 | Write-only | _     |

| 0x1A0       | PWM Comparison 7 Value Register        | PWM_CMPV7    | Read/Write | 0x0   |

| 0x1A4       | PWM Comparison 7 Value Update Register | PWM_CMPVUPD7 | Write-only | _     |

| 0x1A8       | PWM Comparison 7 Mode Register         | PWM_CMPM7    | Read/Write | 0x0   |

Atmel