# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                           |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 120MHz                                                                    |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, Memory Card, SPI, SSC, UART/USART, USB   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                |

| Number of I/O              | 79                                                                        |

| Program Memory Size        | 1MB (1M × 8)                                                              |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 160K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                              |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                     |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 100-LQFP                                                                  |

| Supplier Device Package    | 100-LQFP (14x14)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4sa16cb-an |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Atmel

# 12.4 Cortex-M4 Models

## 12.4.1 Programmers Model

This section describes the Cortex-M4 programmers model. In addition to the individual core register descriptions, it contains information about the processor modes and privilege levels for software execution and stacks.

#### 12.4.1.1 Processor Modes and Privilege Levels for Software Execution

The processor modes are:

• Thread mode

Used to execute application software. The processor enters the Thread mode when it comes out of reset.

Handler mode Used to handle exceptions. The processor returns to the Thread mode when it has finished exception processing.

The *privilege levels* for software execution are:

Unprivileged

The software:

- Has limited access to the MSR and MRS instructions, and cannot use the CPS instruction

- Cannot access the System Timer, NVIC, or System Control Block

- Might have a restricted access to memory or peripherals.

Unprivileged software executes at the unprivileged level.

• Privileged

The software can use all the instructions and has access to all resources. *Privileged software* executes at the privileged level.

In Thread mode, the Control Register controls whether the software execution is privileged or unprivileged, see "Control Register" . In Handler mode, software execution is always privileged.

Only privileged software can write to the Control Register to change the privilege level for software execution in Thread mode. Unprivileged software can use the SVC instruction to make a *supervisor call* to transfer control to privileged software.

## 12.4.1.2 Stacks

The processor uses a full descending stack. This means the stack pointer holds the address of the last stacked item in memory When the processor pushes a new item onto the stack, it decrements the stack pointer and then writes the item to the new memory location. The processor implements two stacks, the *main stack* and the *process stack*, with a pointer for each held in independent registers, see "Stack Pointer".

In Thread mode, the Control Register controls whether the processor uses the main stack or the process stack, see "Control Register" .

In Handler mode, the processor always uses the main stack.

The options for processor operations are:

| Table 12-1. | Summary of processor mode, execution privilege level, and stack use options |

|-------------|-----------------------------------------------------------------------------|

|-------------|-----------------------------------------------------------------------------|

| Processor<br>Mode | Used to Execute    | Privilege Level for<br>Software Execution | Stack Used                                 |  |

|-------------------|--------------------|-------------------------------------------|--------------------------------------------|--|

| Thread            | Applications       | Privileged or unprivileged <sup>(1)</sup> | Main stack or process stack <sup>(1)</sup> |  |

| Handler           | Exception handlers | Always privileged                         | Main stack                                 |  |

Note: 1. See "Control Register" .

#### Table 12-13. Cortex-M4 Instructions (Continued)

| Mnemonic                              | Operands                | Description                                                            | Flags   |

|---------------------------------------|-------------------------|------------------------------------------------------------------------|---------|

| QSUB16                                | {Rd,} Rn, Rm            | Saturating Subtract 16                                                 | -       |

| QSUB8                                 | {Rd,} Rn, Rm            | Saturating Subtract 8                                                  | -       |

| RBIT                                  | Rd, Rn                  | Reverse Bits                                                           | -       |

| REV                                   | Rd, Rn                  | Reverse byte order in a word                                           | -       |

| REV16                                 | Rd, Rn                  | Reverse byte order in each halfword                                    | -       |

| REVSH                                 | Rd, Rn                  | Reverse byte order in bottom halfword and sign extend                  | _       |

| ROR, RORS                             | Rd, Rm, <rs #n></rs #n> | Rotate Right                                                           | N,Z,C   |

| RRX, RRXS                             | Rd, Rm                  | Rotate Right with Extend                                               | N,Z,C   |

| RSB, RSBS                             | {Rd,} Rn, Op2           | Reverse Subtract                                                       | N,Z,C,V |

| SADD16                                | {Rd,} Rn, Rm            | Signed Add 16                                                          | GE      |

| SADD8                                 | {Rd,} Rn, Rm            | Signed Add 8 and Subtract with Exchange                                | GE      |

| SASX                                  | {Rd,} Rn, Rm            | Signed Add                                                             | GE      |

| SBC, SBCS                             | {Rd,} Rn, Op2           | Subtract with Carry                                                    | N,Z,C,V |

| SBFX                                  | Rd, Rn, #lsb, #width    | Signed Bit Field Extract                                               | -       |

| SDIV                                  | {Rd,} Rn, Rm            | Signed Divide                                                          | -       |

| SEL                                   | {Rd,} Rn, Rm            | Select bytes                                                           | -       |

| SEV                                   | -                       | Send Event                                                             | -       |

| SHADD16                               | {Rd,} Rn, Rm            | Signed Halving Add 16                                                  | -       |

| SHADD8                                | {Rd,} Rn, Rm            | Signed Halving Add 8                                                   | -       |

| SHASX                                 | {Rd,} Rn, Rm            | Signed Halving Add and Subtract with Exchange                          | -       |

| SHSAX                                 | {Rd,} Rn, Rm            | Signed Halving Subtract and Add with Exchange                          | -       |

| SHSUB16                               | {Rd,} Rn, Rm            | Signed Halving Subtract 16                                             | -       |

| SHSUB8                                | {Rd,} Rn, Rm            | Signed Halving Subtract 8                                              | -       |

| SMLABB, SMLABT,<br>SMLATB, SMLATT     | Rd, Rn, Rm, Ra          | Signed Multiply Accumulate Long (halfwords)                            | Q       |

| SMLAD, SMLADX                         | Rd, Rn, Rm, Ra          | Signed Multiply Accumulate Dual                                        | Q       |

| SMLAL                                 | RdLo, RdHi, Rn, Rm      | Signed Multiply with Accumulate ( $32 \times 32 + 64$ ), 64-bit result | -       |

| SMLALBB, SMLALBT,<br>SMLALTB, SMLALTT | RdLo, RdHi, Rn, Rm      | Signed Multiply Accumulate Long, halfwords                             | -       |

| SMLALD, SMLALDX                       | RdLo, RdHi, Rn, Rm      | Signed Multiply Accumulate Long Dual                                   | -       |

| SMLAWB, SMLAWT                        | Rd, Rn, Rm, Ra          | Signed Multiply Accumulate, word by halfword                           | Q       |

| SMLSD                                 | Rd, Rn, Rm, Ra          | Signed Multiply Subtract Dual                                          | Q       |

| SMLSLD                                | RdLo, RdHi, Rn, Rm      | Signed Multiply Subtract Long Dual                                     |         |

| SMMLA                                 | Rd, Rn, Rm, Ra          | Signed Most significant word Multiply Accumulate                       | -       |

| SMMLS, SMMLR                          | Rd, Rn, Rm, Ra          | Signed Most significant word Multiply Subtract                         | -       |

| SMMUL, SMMULR                         | {Rd,} Rn, Rm            | Signed Most significant word Multiply                                  | -       |

| SMUAD                                 | {Rd,} Rn, Rm            | Signed dual Multiply Add                                               | Q       |

Restrictions

Do not use SP and do not use PC.

**Condition Flags**

These instructions do not affect the flags.

Examples

| SXTAH | R4, | R8, | R6, | ROR | #16 | ; | Rotates R6 right by 16 bits, obtains bottom  |

|-------|-----|-----|-----|-----|-----|---|----------------------------------------------|

|       |     |     |     |     |     | ; | halfword, sign extends to 32 bits, adds      |

|       |     |     |     |     |     | ; | R8,and writes to R4                          |

| UXTAB | R3, | R4, | R10 |     |     | ; | Extracts bottom byte of R10 and zero extends |

|       |     |     |     |     |     | ; | to 32 bits, adds R4, and writes to R3.       |

| 12.11.2.1 | MPU Type Register | r  |      |      |    |    |          |

|-----------|-------------------|----|------|------|----|----|----------|

| Name:     | MPU_TYPE          |    |      |      |    |    |          |

| Access:   | Read/Write        |    |      |      |    |    |          |

| 31        | 30                | 29 | 28   | 27   | 26 | 25 | 24       |

| -         | -                 | _  | -    | -    | -  | -  | -        |

| 23        | 22                | 21 | 20   | 19   | 18 | 17 | 16       |

|           |                   |    | IREC | GION |    |    |          |

| 15        | 14                | 13 | 12   | 11   | 10 | 9  | 8        |

|           |                   |    | DRE  | GION |    |    |          |

| 7         | 6                 | 5  | 4    | 3    | 2  | 1  | 0        |

| -         | -                 | _  | _    | _    | _  | _  | SEPARATE |

The MPU\_TYPE register indicates whether the MPU is present, and if so, how many regions it supports.

# • IREGION: Instruction Region

Indicates the number of supported MPU instruction regions.

Always contains 0x00. The MPU memory map is unified and is described by the DREGION field.

#### • DREGION: Data Region

Indicates the number of supported MPU data regions: 0x08 = Eight MPU regions.

# • SEPARATE: Separate Instruction

Indicates support for unified or separate instruction and date memory maps:

0: Unified.

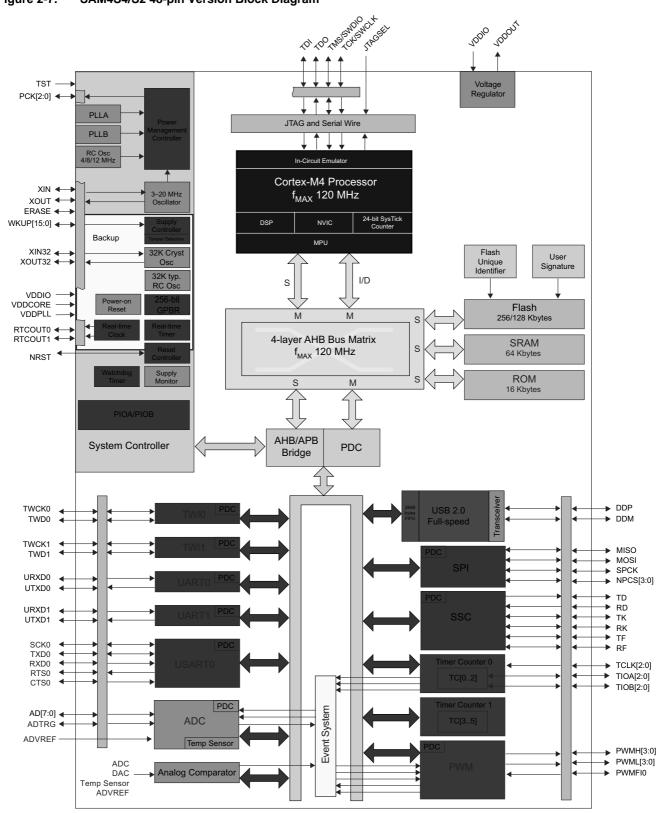

# 14. Reset Controller (RSTC)

# 14.1 Description

The Reset Controller (RSTC), based on power-on reset cells, handles all the resets of the system without any external components. It reports which reset occurred last.

The Reset Controller also drives independently or simultaneously the external reset and the peripheral and processor resets.

# 14.2 Embedded Characteristics

- Management of All System Resets, Including

- External Devices through the NRST Pin

- Processor Reset

- Processor Peripheral Set Reset

- Based on Embedded Power-on Cell

- Reset Source Status

- Status of the Last Reset

- Either Software Reset, User Reset, Watchdog Reset

- External Reset Signal Shaping

# 14.3 Block Diagram

# 19. General Purpose Backup Registers (GPBR)

# 19.1 Description

The System Controller embeds 256 bits of General Purpose Backup registers organized as Eight 32-bit registers.

It is possible to generate an immediate clear of the content of General Purpose Backup registers 0 to 3 (first half) if a Low-power Debounce event is detected on one of the wakeup pins, WKUP0 or WKUP1. The content of the other General Purpose Backup registers (second half) remains unchanged.

The Supply Controller module must be programmed accordingly. In the register SUPC\_WUMR in the Supply Controller module, LPDBCCLR, LPDBCEN0 and/or LPDBCEN1 bit must be configured to 1 and LPDBC must be other than 0.

If a Tamper event has been detected, it is not possible to write to the General Purpose Backup registers while the LPDBCS0 or LPDBCS1 flags are not cleared in the Supply Controller Status Register (SUPC\_SR).

# 19.2 Embedded Characteristics

• 256 bits of General Purpose Backup Registers

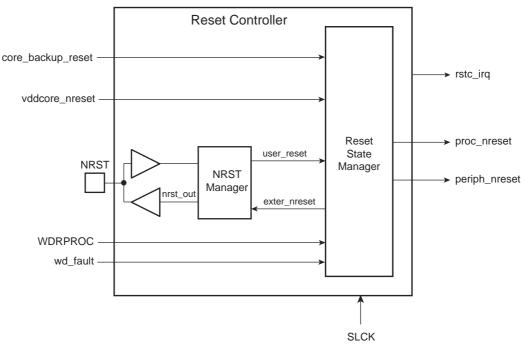

#### 20.4.2.4 Data Read Optimization

The organization of the Flash in 128 bits or 64 bits is associated with two 128-bit or 64-bit prefetch buffers and one 128-bit or 64-bit data read buffer, thus providing maximum system performance. This buffer is added in order to store the requested data plus all the data contained in the 128-bit or 64-bit aligned data. This speeds up sequential data reads if, for example, FWS is equal to 1 (see Figure 20-6). The data read optimization is enabled by default. If the bit EEFC\_FMR.SCOD is set to 1, this buffer is disabled and the data read is no longer optimized. Note: No consecutive data read accesses are mandatory to benefit from this optimization.

#### Figure 20-6. Data Read Optimization for FWS = 1

#### 20.4.3 Flash Commands

The EEFC offers a set of commands to manage programming the Flash memory, locking and unlocking lock regions, consecutive programming, locking and full Flash erasing, etc.

The commands are listed in the following table.

| Command                             | Value | Mnemonic |

|-------------------------------------|-------|----------|

| Get Flash descriptor                | 0x00  | GETD     |

| Write page                          | 0x01  | WP       |

| Write page and lock                 | 0x02  | WPL      |

| Erase page and write page           | 0x03  | EWP      |

| Erase page and write page then lock | 0x04  | EWPL     |

| Erase all                           | 0x05  | EA       |

| Erase pages                         | 0x07  | EPA      |

| Set lock bit                        | 0x08  | SLB      |

| Clear lock bit                      | 0x09  | CLB      |

| Get lock bit                        | 0x0A  | GLB      |

| Set GPNVM bit                       | 0x0B  | SGPB     |

| Clear GPNVM bit                     | 0x0C  | CGPB     |

#### Table 20-2.Set of Commands

# 25.8.4 System I/O Configuration Register

| Address: 0x40<br>Access Read | G_SYSIO<br>0E0314<br>d/Write<br>00_0000 |        |         |         |         |    |    |

|------------------------------|-----------------------------------------|--------|---------|---------|---------|----|----|

| 31                           | 30                                      | 29     | 28      | 27      | 26      | 25 | 24 |

| -                            | -                                       | -      | -       | -       | -       | -  | -  |

| 23                           | 22                                      | 21     | 20      | 19      | 18      | 17 | 16 |

| _                            | -                                       | _      | _       | -       | -       | _  | -  |

| 15                           | 14                                      | 13     | 12      | 11      | 10      | 9  | 8  |

| _                            | -                                       | -      | SYSIO12 | SYSIO11 | SYSIO10 | -  | -  |

| 7                            | 6                                       | 5      | 4       | 3       | 2       | 1  | 0  |

| SYSIO7                       | SYSIO6                                  | SYSIO5 | SYSIO4  | -       | -       | -  | -  |

#### • SYSIO4: PB4 or TDI Assignment

0: TDI function selected.

1: PB4 function selected.

## SYSIO5: PB5 or TDO/TRACESWO Assignment

0: TDO/TRACESWO function selected.

1: PB5 function selected.

# • SYSIO6: PB6 or TMS/SWDIO Assignment

- 0: TMS/SWDIO function selected.

- 1: PB6 function selected.

#### SYSIO7: PB7 or TCK/SWCLK Assignment

- 0: TCK/SWCLK function selected.

- 1: PB7 function selected.

#### • SYSIO10: PB10 or DDM Assignment

- 0: DDM function selected.

- 1: PB10 function selected.

# SYSIO11: PB11 or DDP Assignment

0: DDP function selected.

1: PB11 function selected.

## SYSIO12: PB12 or ERASE Assignment

- 0: ERASE function selected.

- 1: PB12 function selected.

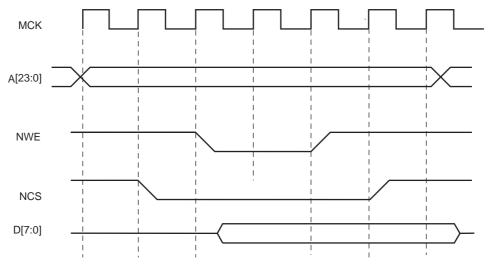

Figure 26-11. WRITE\_MODE = 1. The write operation is controlled by NWE

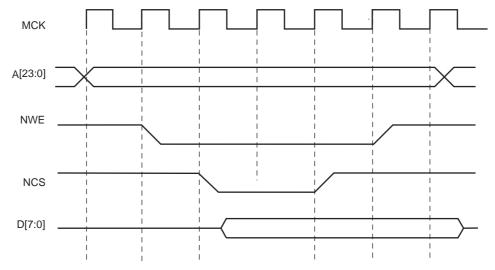

#### 26.9.4.2 Write is Controlled by NCS (WRITE\_MODE = 0)

Figure 26-12 shows the waveforms of a write operation with WRITE\_MODE cleared. The data is put on the bus during the pulse and hold steps of the NCS signal. The internal data buffers are switched to Output mode after the NCS\_WR\_SETUP time, and until the end of the write cycle, regardless of the programmed waveform on NWE.

#### Figure 26-12. WRITE\_MODE = 0. The write operation is controlled by NCS

#### 26.9.5 Register Write Protection

To prevent any single software error that may corrupt SMC behavior, the registers listed below can be writeprotected by setting the WPEN bit in the SMC Write Protection Mode register (SMC\_WPMR).

If a write access in a write-protected register is detected, the WPVS flag in the SMC Write Protection Status register (SMC\_WPSR) is set and the field WPVSRC indicates in which register the write access has been attempted.

The WPVS flag is automatically cleared after reading the SSMC\_WPSR.

The following registers can be write-protected:

- "SMC Setup Register"

- "SMC Pulse Register"

# Atmel

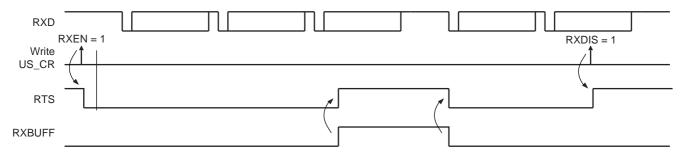

Figure 36-27. Receiver Behavior when Operating with Hardware Handshaking

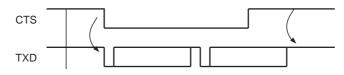

Figure 36-28 shows how the transmitter operates if hardware handshaking is enabled. The CTS pin disables the transmitter. If a character is being processed, the transmitter is disabled only after the completion of the current character and transmission of the next character happens as soon as the pin CTS falls.

Figure 36-28. Transmitter Behavior when Operating with Hardware Handshaking

#### 36.6.4 ISO7816 Mode

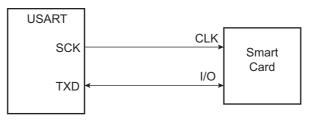

The USART features an ISO7816-compatible operating mode. This mode permits interfacing with smart cards and Security Access Modules (SAM) communicating through an ISO7816 link. Both T = 0 and T = 1 protocols defined by the ISO7816 specification are supported.

Setting the USART in ISO7816 mode is performed by writing the USART\_MODE field in US\_MR to the value 0x4 for protocol T = 0 and to the value 0x5 for protocol T = 1.

#### 36.6.4.1 ISO7816 Mode Overview

The ISO7816 is a half duplex communication on only one bidirectional line. The baud rate is determined by a division of the clock provided to the remote device (see Section 36-2 "Baud Rate Generator").

The USART connects to a smart card as shown in Figure 36-29. The TXD line becomes bidirectional and the baud rate generator feeds the ISO7816 clock on the SCK pin. As the TXD pin becomes bidirectional, its output remains driven by the output of the transmitter but only when the transmitter is active while its input is directed to the input of the receiver. The USART is considered as the master of the communication as it generates the clock.

#### Figure 36-29. Connection of a Smart Card to the USART

When operating in ISO7816, either in T = 0 or T = 1 modes, the character format is fixed. The configuration is 8 data bits, even parity and 1 or 2 stop bits, regardless of the values programmed in the CHRL, MODE9, PAR and CHMODE fields. MSBF can be used to transmit LSB or MSB first. Parity Bit (PAR) can be used to transmit in normal or inverse mode. Refer to Section 36.7.3 "USART Mode Register" and "PAR: Parity Type".

# Atmel

# 36.7.2 USART Control Register (SPI\_MODE)

| Name:    | US_CR (SPI_M   | JS_CR (SPI_MODE) |      |       |       |    |        |  |  |

|----------|----------------|------------------|------|-------|-------|----|--------|--|--|

| Address: | 0x40024000 (0) | ), 0x40028000 (  | 1)   |       |       |    |        |  |  |

| Access:  | Write-only     |                  |      |       |       |    |        |  |  |

| 31       | 30             | 29               | 28   | 27    | 26    | 25 | 24     |  |  |

| _        | -              | —                | _    | _     | -     | _  | —      |  |  |

| 23       | 22             | 21               | 20   | 19    | 18    | 17 | 16     |  |  |

| -        | -              | -                | _    | RCS   | FCS   | -  | _      |  |  |

| 15       | 14             | 13               | 12   | 11    | 10    | 9  | 8      |  |  |

|          | -              | -                | _    | -     | -     | -  | RSTSTA |  |  |

| 7        | 6              | 5                | 4    | 3     | 2     | 1  | 0      |  |  |

| TXDIS    | TXEN           | RXDIS            | RXEN | RSTTX | RSTRX | _  | _      |  |  |

This configuration is relevant only if USART\_MODE = 0xE or 0xF in the USART Mode Register.

#### • RSTRX: Reset Receiver

0: No effect.

1: Resets the receiver.

#### • RSTTX: Reset Transmitter

0: No effect.

1: Resets the transmitter.

# • RXEN: Receiver Enable

0: No effect.

1: Enables the receiver, if RXDIS is 0.

#### • RXDIS: Receiver Disable

0: No effect.

1: Disables the receiver.

#### • TXEN: Transmitter Enable

0: No effect.

1: Enables the transmitter if TXDIS is 0.

## • TXDIS: Transmitter Disable

0: No effect.

1: Disables the transmitter.

## RSTSTA: Reset Status Bits

0: No effect.

1: Resets the status bits OVRE, UNRE in US\_CSR.

#### • CHRL: Character Length

| Value | Name  | Description                |  |  |  |  |  |

|-------|-------|----------------------------|--|--|--|--|--|

| 0     | 5_BIT | Character length is 5 bits |  |  |  |  |  |

| 1     | 6_BIT | Character length is 6 bits |  |  |  |  |  |

| 2     | 7_BIT | Character length is 7 bits |  |  |  |  |  |

| 3     | 8_BIT | Character length is 8 bits |  |  |  |  |  |

#### • SYNC: Synchronous Mode Select

0: USART operates in Asynchronous mode.

1: USART operates in Synchronous mode.

#### • PAR: Parity Type

| Value | Name      | Description                |

|-------|-----------|----------------------------|

| 0     | EVEN      | Even parity                |

| 1     | ODD       | Odd parity                 |

| 2     | SPACE     | Parity forced to 0 (Space) |

| 3     | MARK      | Parity forced to 1 (Mark)  |

| 4     | NO        | No parity                  |

| 6     | MULTIDROP | Multidrop mode             |

# • NBSTOP: Number of Stop Bits

| Value | Name    | Description                                    |

|-------|---------|------------------------------------------------|

| 0     | 1_BIT   | 1 stop bit                                     |

| 1     | 1_5_BIT | 1.5 stop bit (SYNC = 0) or reserved (SYNC = 1) |

| 2     | 2_BIT   | 2 stop bits                                    |

#### • CHMODE: Channel Mode

| Value | Name            | Description                                                            |

|-------|-----------------|------------------------------------------------------------------------|

| 0     | NORMAL          | Normal mode                                                            |

| 1     | AUTOMATIC       | Automatic Echo. Receiver input is connected to the TXD pin.            |

| 2     | LOCAL_LOOPBACK  | Local Loopback. Transmitter output is connected to the Receiver Input. |

| 3     | REMOTE_LOOPBACK | Remote Loopback. RXD pin is internally connected to the TXD pin.       |

#### • MSBF: Bit Order

0: Least significant bit is sent/received first.

1: Most significant bit is sent/received first.

# • MODE9: 9-bit Character Length

0: CHRL defines character length

1: 9-bit character length

# • ETRGS: External Trigger Status (cleared on read)

0: External trigger has not occurred since the last read of the Status Register.

1: External trigger has occurred since the last read of the Status Register.

## • CLKSTA: Clock Enabling Status

0: Clock is disabled.

1: Clock is enabled.

# • MTIOA: TIOA Mirror

0: TIOA is low. If TC\_CMRx.WAVE = 0, this means that TIOA pin is low. If TC\_CMRx.WAVE = 1, this means that TIOA is driven low.

1: TIOA is high. If TC\_CMRx.WAVE = 0, this means that TIOA pin is high. If TC\_CMRx.WAVE = 1, this means that TIOA is driven high.

# • MTIOB: TIOB Mirror

0: TIOB is low. If TC\_CMRx.WAVE = 0, this means that TIOB pin is low. If TC\_CMRx.WAVE = 1, this means that TIOB is driven low.

1: TIOB is high. If TC\_CMRx.WAVE = 0, this means that TIOB pin is high. If TC\_CMRx.WAVE = 1, this means that TIOB is driven high.

| 38.14.7 HSMCI Block Register |            |    |     |     |    |    |    |

|------------------------------|------------|----|-----|-----|----|----|----|

| Name:                        | HSMCI_BLKR |    |     |     |    |    |    |

| Address:                     | 0x4000018  |    |     |     |    |    |    |

| Access:                      | Read/Write |    |     |     |    |    |    |

| 31                           | 30         | 29 | 28  | 27  | 26 | 25 | 24 |

|                              |            |    | BLK | LEN |    |    |    |

| 23                           | 22         | 21 | 20  | 19  | 18 | 17 | 16 |

|                              |            |    | BLK | LEN |    |    |    |

| 15                           | 14         | 13 | 12  | 11  | 10 | 9  | 8  |

|                              |            |    | BC  | NT  |    |    |    |

| 7                            | 6          | 5  | 4   | 3   | 2  | 1  | 0  |

|                              |            |    | BC  | NT  |    |    |    |

|                              |            |    |     |     |    |    |    |

# • BCNT: MMC/SDIO Block Count - SDIO Byte Count

This field determines the number of data byte(s) or block(s) to transfer.

The transfer data type and the authorized values for BCNT field are determined by the TRTYP field in the HSMCI Command Register (HSMCI\_CMDR).

When TRTYP = 1 (MMC/SDCARD Multiple Block), BCNT can be programmed from 1 to 65535, 0 corresponds to an infinite block transfer.

When TRTYP = 4 (SDIO Byte), BCNT can be programmed from 1 to 511, 0 corresponds to 512-byte transfer. Values in range 512 to 65536 are forbidden.

When TRTYP = 5 (SDIO Block), BCNT can be programmed from 1 to 511, 0 corresponds to an infinite block transfer. Values in range 512 to 65536 are forbidden.

<u>Warning</u>: In SDIO Byte and Block modes (TRTYP = 4 or 5), writing the 7 last bits of BCNT field with a value which differs from 0 is forbidden and may lead to unpredictable results.

#### BLKLEN: Data Block Length

20 44 7 LICMCI Disale Daniatan

This field determines the size of the data block.

Bits 16 and 17 must be configured to 0 if FBYTE is disabled.

Note: In SDIO Byte mode, BLKLEN field is not used.

After a reset of the PWM controller, DIVA (DIVB) and PREA (PREB) are set to '0'. This implies that after reset clkA (clkB) are turned off.

At reset, all clocks provided by the modulo n counter are turned off except the peripheral clock. This situation is also true when the PWM peripheral clock is turned off through the Power Management Controller.

# CAUTION:

Before using the PWM controller, the programmer must first enable the peripheral clock in the Power Management Controller (PMC).

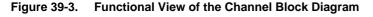

#### 39.6.2 PWM Channel

39.6.2.1 Channel Block Diagram

Each of the 4 channels is composed of six blocks:

- A clock selector which selects one of the clocks provided by the clock generator (described in Section 39.6.1 "PWM Clock Generator").

- A counter clocked by the output of the clock selector. This counter is incremented or decremented according to the channel configuration and comparators matches. The size of the counter is 16 bits.

- A comparator used to compute the OCx output waveform according to the counter value and the configuration. The counter value can be the one of the channel counter or the one of the channel 0 counter according to SYNCx bit in the PWM Sync Channels Mode Register (PWM\_SCM).

- A 2-bit configurable gray counter enables the stepper motor driver. One gray counter drives 2 channels.

- A dead-time generator providing two complementary outputs (DTOHx/DTOLx) which allows to drive external power control switches safely.

- An output override block that can force the two complementary outputs to a programmed value (OOOHx/OOOLx).

- An asynchronous fault protection mechanism that has the highest priority to override the two complementary outputs (PWMHx/PWMLx) in case of fault detection (outputs forced to '0', '1').

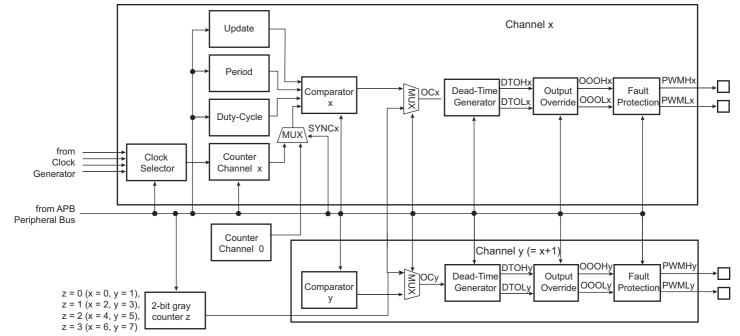

#### Figure 39-15. Comparison Waveform

#### 39.6.4 PWM Event Lines

The PWM provides 2 independent event lines intended to trigger actions in other peripherals (e.g., for the Analogto-Digital Converter (ADC)).

A pulse (one cycle of the peripheral clock) is generated on an event line, when at least one of the selected comparisons is matching. The comparisons can be selected or unselected independently by the CSEL bits in the PWM Event Line x Register (PWM\_ELMRx for the Event Line x).

An example of event generation is provided in Figure 39-17.

- Configuration of the period for each channel (CPRD in the PWM\_CPRDx register). Writing in PWM\_CPRDx register is possible while the channel is disabled. After validation of the channel, the user must use PWM\_CPRDUPDx register to update PWM\_CPRDx as explained below.

- Configuration of the duty-cycle for each channel (CDTY in the PWM\_CDTYx register). Writing in PWM\_CDTYx register is possible while the channel is disabled. After validation of the channel, the user must use PWM\_CDTYUPDx register to update PWM\_CDTYx as explained below.

- Configuration of the dead-time generator for each channel (DTH and DTL in PWM\_DTx) if enabled (DTE bit in the PWM\_CMRx). Writing in the PWM\_DTx register is possible while the channel is disabled. After validation of the channel, the user must use PWM\_DTUPDx register to update PWM\_DTx

- Selection of the synchronous channels (SYNCx in the PWM\_SCM register)

- Selection of the moment when the WRDY flag and the corresponding Peripheral DMA Controller transfer request are set (PTRM and PTRCS in the PWM\_SCM register)

- Configuration of the Update mode (UPDM in PWM\_SCM register)

- Configuration of the update period (UPR in PWM\_SCUP register) if needed

- Configuration of the comparisons (PWM\_CMPVx and PWM\_CMPMx)

- Configuration of the event lines (PWM\_ELMRx)

- Configuration of the fault inputs polarity (FPOL in PWM\_FMR)

- Configuration of the fault protection (FMOD and FFIL in PWM\_FMR, PWM\_FPV and PWM\_FPE1)

- Enable of the interrupts (writing CHIDx and FCHIDx in PWM\_IER1, and writing WRDYE, ENDTXE, TXBUFE, UNRE, CMPMx and CMPUx in PWM\_IER2)

- Enable of the PWM channels (writing CHIDx in the PWM\_ENA register)

#### 39.6.5.2 Source Clock Selection Criteria

The large number of source clocks can make selection difficult. The relationship between the value in the PWM Channel Period Register (PWM\_CPRDx) and the PWM Channel Duty Cycle Register (PWM\_CDTYx) helps the user select the appropriate clock. The event number written in the Period Register gives the PWM accuracy. The Duty-Cycle quantum cannot be lower than *1/CPRDx* value. The higher the value of PWM\_CPRDx, the greater the PWM accuracy.

For example, if the user sets 15 (in decimal) in PWM\_CPRDx, the user is able to set a value from between 1 up to 14 in PWM\_CDTYx. The resulting duty-cycle quantum cannot be lower than 1/15 of the PWM period.

#### 39.6.5.3 Changing the Duty-Cycle, the Period and the Dead-Times

It is possible to modulate the output waveform duty-cycle, period and dead-times.

To prevent unexpected output waveform, the user must use the PWM Channel Duty Cycle Update Register (PWM\_CDTYUPDx), the PWM Channel Period Update Register (PWM\_CPRDUPDx) and the PWM Channel Dead Time Update Register (PWM\_DTUPDx) to change waveform parameters while the channel is still enabled.

- If the channel is an asynchronous channel (SYNCx = 0 in PWM Sync Channels Mode Register (PWM\_SCM)), these registers hold the new period, duty-cycle and dead-times values until the end of the current PWM period and update the values for the next period.

- If the channel is a synchronous channel and update method 0 is selected (SYNCx = 1 and UPDM = 0 in PWM\_SCM register), these registers hold the new period, duty-cycle and dead-times values until the bit UPDULOCK is written at '1' (in PWM Sync Channels Update Control Register (PWM\_SCUC)) and the end of the current PWM period, then update the values for the next period.

- If the channel is a synchronous channel and update method 1 or 2 is selected (SYNCx = 1 and UPDM = 1 or 2 in PWM\_SCM register):

- registers PWM\_CPRDUPDx and PWM\_DTUPDx hold the new period and dead-times values until the bit UPDULOCK is written at '1' (in PWM\_SCUC) and the end of the current PWM period, then update the values for the next period.

# 41.7.8 ACC Write Protection Mode Register

| Name:    | ACC_WPMR   |    |    |    |    |    |      |

|----------|------------|----|----|----|----|----|------|

| Address: | 0x400400E4 |    |    |    |    |    |      |

| Access:  | Read/Write |    |    |    |    |    |      |

| 31       | 30         | 29 | 28 | 27 | 26 | 25 | 24   |

|          | WPKEY      |    |    |    |    |    |      |

| 23       | 22         | 21 | 20 | 19 | 18 | 17 | 16   |

| WPKEY    |            |    |    |    |    |    |      |

| 15       | 14         | 13 | 12 | 11 | 10 | 9  | 8    |

| WPKEY    |            |    |    |    |    |    |      |

| 7        | 6          | 5  | 4  | 3  | 2  | 1  | 0    |

| _        | -          | _  | _  | _  | -  | _  | WPEN |

#### • WPEN: Write Protection Enable

0: Disables the write protection if WPKEY corresponds to 0x414343 ("ACC" in ASCII).

1: Enables the write protection if WPKEY corresponds to 0x414343 ("ACC" in ASCII).

See "Register Write Protection" on page 1071 for the list of registers that can be write-protected.

#### • WPKEY: Write Protection Key

| Value    | Name   | Description                                                                       |

|----------|--------|-----------------------------------------------------------------------------------|

| 0x414343 | PASSWD | Writing any other value in this field aborts the write operation of the WPEN bit. |

|          |        | Always reads as 0.                                                                |

#### 48.3.3 Brownout Detector

#### Issue: Unpredictable Behavior if BOD is Disabled, VDDCORE is Lost and VDDIO is Connected

In active mode or in wait mode, if the Brownout Detector is disabled (SUPC\_MR.BODDIS = 1) and power is lost on VDDCORE while VDDIO is powered, the device might not be properly reset and may behave unpredictably.

**Workaround:** When the Brownout Detector is disabled in active or in wait mode, VDDCORE always needs to be powered.

#### 48.3.4 Low-power Mode

#### Issue: Unpredictable Behavior When Entering Sleep Mode

When entering Sleep mode, if an interrupt occurs during WFI or WFE (PMC\_FSMR.LPM = 0) instruction processing, the ARM core may read an incorrect data, thus leading to unpredictable behavior of the software. This issue is not present in Wait mode.

#### Workaround: The following conditions must be met:

- 1. The interrupt vector table must be located in Flash.

- The Matrix slave interface for the Flash must be set to 'No default master'. This is done by setting the field DEFMSTR\_TYPE to 0 in the register MATRIX\_SCFG. The code example below can be used to program the NO\_DEFAULT\_MASTER state:

MATRIX\_SCFG[2] = MATRIX\_SCFG\_SLOT\_CYCLE(0xFF) | MATRIX\_SCFG\_DEFMSTR\_TYPE(0x0); This must be done once in the software before entering Sleep mode.

#### 48.3.5 PIO

#### Issue: PB4 Input Low-level Voltage Range

The undershoot is limited to -0.1V.

In normal operating conditions, the  $V_{II}$  minimum value on PB4 is limited to 0V.

**Workaround:** The voltage on PB4 with respect to ground must be in the range -0.1V to + VDDIO + 0.4V instead of -0.3V to + VDDIO + 0.4V for all other input pins, as shown in Table 44.1 "Absolute Maximum Ratings".

The minimum  $V_{IL}$  on PB4 must be 0V instead of -0.3V for all other input pins, as shown in Table 44.3 "DC Characteristics".

Atmel