Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                           |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 120MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, Memory Card, SPI, SSC, UART/USART, USB            |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                |

| Number of I/O              | 47                                                                        |

| Program Memory Size        | 1MB (1M × 8)                                                              |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 160K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                              |

| Data Converters            | A/D 11x12b; D/A 2x12b                                                     |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 64-QFN (9x9)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4sd16bb-mn |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 12.4.1.17 Exceptions and Interrupts

The Cortex-M4 processor supports interrupts and system exceptions. The processor and the *Nested Vectored Interrupt Controller* (NVIC) prioritize and handle all exceptions. An exception changes the normal flow of software control. The processor uses the Handler mode to handle all exceptions except for reset. See "Exception Entry" and "Exception Return" for more information.

The NVIC registers control interrupt handling. See "Nested Vectored Interrupt Controller (NVIC)" for more information.

#### 12.4.1.18 Data Types

The processor supports the following data types:

- 32-bit words

- 16-bit halfwords

- 8-bit bytes

- The processor manages all data memory accesses as little-endian. Instruction memory and *Private Peripheral Bus* (PPB) accesses are always little-endian. See "Memory Regions, Types and Attributes" for more information.

## 12.4.1.19 Cortex Microcontroller Software Interface Standard (CMSIS)

For a Cortex-M4 microcontroller system, the Cortex Microcontroller Software Interface Standard (CMSIS) defines:

- A common way to:

- Access peripheral registers

- Define exception vectors

- The names of:

- The registers of the core peripherals

- The core exception vectors

- A device-independent interface for RTOS kernels, including a debug channel.

The CMSIS includes address definitions and data structures for the core peripherals in the Cortex-M4 processor.

The CMSIS simplifies the software development by enabling the reuse of template code and the combination of CMSIS-compliant software components from various middleware vendors. Software vendors can expand the CMSIS to include their peripheral definitions and access functions for those peripherals.

This document includes the register names defined by the CMSIS, and gives short descriptions of the CMSIS functions that address the processor core and the core peripherals.

Note: This document uses the register short names defined by the CMSIS. In a few cases, these differ from the architectural short names that might be used in other documents.

The following sections give more information about the CMSIS:

- Section 12.5.3 "Power Management Programming Hints"

- Section 12.6.2 "CMSIS Functions"

- Section 12.8.2.1 "NVIC Programming Hints".

| 12.9.1.12  | System Handler C       | ontrol and Stat    | e Register         |             |             |             |             |

|------------|------------------------|--------------------|--------------------|-------------|-------------|-------------|-------------|

| Name:      | SCB_SHCSR              |                    |                    |             |             |             |             |

| Access:    | Read/Write             |                    |                    |             |             |             |             |

| 31         | 30                     | 29                 | 28                 | 27          | 26          | 25          | 24          |

| -          | -                      | -                  | -                  | -           | -           | —           | -           |

| 23         | 22                     | 21                 | 20                 | 19          | 18          | 17          | 16          |

| —          | -                      | -                  | -                  | -           | USGFAULTENA | BUSFAULTENA | MEMFAULTENA |

| 15         | 14                     | 13                 | 12                 | 11          | 10          | 9           | 8           |

| SVCALLPEND | DED BUSFAULTPEND<br>ED | MEMFAULTPEND<br>ED | USGFAULTPEND<br>ED | SYSTICKACT  | PENDSVACT   | -           | MONITORACT  |

| 7          | 6                      | 5                  | 4                  | 3           | 2           | 1           | 0           |

| SVCALLAC   | т –                    | -                  | —                  | USGFAULTACT | —           | BUSFAULTACT | MEMFAULTACT |

The SHCSR enables the system handlers, and indicates the pending status of the bus fault, memory management fault, and SVC exceptions; it also indicates the active status of the system handlers.

## • USGFAULTENA: Usage Fault Enable

- 0: Disables the exception.

- 1: Enables the exception.

## • BUSFAULTENA: Bus Fault Enable

- 0: Disables the exception.

- 1: Enables the exception.

## • MEMFAULTENA: Memory Management Fault Enable

- 0: Disables the exception.

- 1: Enables the exception.

## • SVCALLPENDED: SVC Call Pending

Read:

- 0: The exception is not pending.

- 1: The exception is pending.

Note: The user can write to these bits to change the pending status of the exceptions.

## • BUSFAULTPENDED: Bus Fault Exception Pending

Read:

- 0: The exception is not pending.

- 1: The exception is pending.

Note: The user can write to these bits to change the pending status of the exceptions.

## • MEMFAULTPENDED: Memory Management Fault Exception Pending

Read:

0: The exception is not pending.

1: The exception is pending.

Note: The user can write to these bits to change the pending status of the exceptions.

## • USGFAULTPENDED: Usage Fault Exception Pending

Read:

0: The exception is not pending.

1: The exception is pending.

Note: The user can write to these bits to change the pending status of the exceptions.

## SYSTICKACT: SysTick Exception Active

Read:

0: The exception is not active.

1: The exception is active.

Note: The user can write to these bits to change the active status of the exceptions.

- Caution: A software that changes the value of an active bit in this register without a correct adjustment to the stacked content can cause the processor to generate a fault exception. Ensure that the software writing to this register retains and subsequently restores the current active status.

- Caution: After enabling the system handlers, to change the value of a bit in this register, the user must use a read-modify-write procedure to ensure that only the required bit is changed.

## • PENDSVACT: PendSV Exception Active

0: The exception is not active.

1: The exception is active.

## • MONITORACT: Debug Monitor Active

0: Debug monitor is not active.

1: Debug monitor is active.

## • SVCALLACT: SVC Call Active

0: SVC call is not active.

1: SVC call is active.

## • USGFAULTACT: Usage Fault Exception Active

0: Usage fault exception is not active.

1: Usage fault exception is active.

## • BUSFAULTACT: Bus Fault Exception Active

0: Bus fault exception is not active.

1: Bus fault exception is active.

## • MEMFAULTACT: Memory Management Fault Exception Active

0: Memory management fault exception is not active.

1: Memory management fault exception is active.

## 16.6.5 RTC Time Alarm Register

| Name:    | RTC_TIMALR |    |    |     |    |    |    |

|----------|------------|----|----|-----|----|----|----|

| Address: | 0x400E1470 |    |    |     |    |    |    |

| Access:  | Read/Write |    |    |     |    |    |    |

| 31       | 30         | 29 | 28 | 27  | 26 | 25 | 24 |

| -        | -          | -  | -  | _   | _  | -  | -  |

| 23       | 22         | 21 | 20 | 19  | 18 | 17 | 16 |

| HOUREN   | AMPM       |    |    | HO  | UR |    |    |

| 15       | 14         | 13 | 12 | 11  | 10 | 9  | 8  |

| MINEN    |            |    |    | MIN |    |    |    |

| 7        | 6          | 5  | 4  | 3   | 2  | 1  | 0  |

| SECEN    |            |    |    | SEC |    |    |    |

This register can only be written if the WPEN bit is cleared in the System Controller Write Protection Mode Register (SYSC\_WPMR).

Note: To change one of the SEC, MIN, HOUR fields, it is recommended to disable the field before changing the value and then reenable it after the change has been made. This requires up to three accesses to the RTC\_TIMALR. The first access clears the enable corresponding to the field to change (SECEN, MINEN, HOUREN). If the field is already cleared, this access is not required. The second access performs the change of the value (SEC, MIN, HOUR). The third access is required to re-enable the field by writing 1 in SECEN, MINEN, HOUREN fields.

#### SEC: Second Alarm

This field is the alarm field corresponding to the BCD-coded second counter.

#### SECEN: Second Alarm Enable

- 0: The second-matching alarm is disabled.

- 1: The second-matching alarm is enabled.

#### • MIN: Minute Alarm

This field is the alarm field corresponding to the BCD-coded minute counter.

#### • MINEN: Minute Alarm Enable

- 0: The minute-matching alarm is disabled.

- 1: The minute-matching alarm is enabled.

#### • HOUR: Hour Alarm

This field is the alarm field corresponding to the BCD-coded hour counter.

#### • AMPM: AM/PM Indicator

This field is the alarm field corresponding to the BCD-coded hour counter.

#### HOUREN: Hour Alarm Enable

- 0: The hour-matching alarm is disabled.

- 1: The hour-matching alarm is enabled.

## 18.5.7 Supply Controller Wake-up Inputs Register

| Name:               | SUPC_WUIR                |          |          |          |          |         |         |

|---------------------|--------------------------|----------|----------|----------|----------|---------|---------|

| Address:<br>Access: | 0x400E1420<br>Read/Write |          |          |          |          |         |         |

|                     |                          |          |          |          |          |         |         |

| 31                  | 30                       | 29       | 28       | 27       | 26       | 25      | 24      |

| WKUPT15             | WKUPT14                  | WKUPT13  | WKUPT12  | WKUPT11  | WKUPT10  | WKUPT9  | WKUPT8  |

|                     | -                        | -        | -        | -        | -        |         |         |

| 23                  | 22                       | 21       | 20       | 19       | 18       | 17      | 16      |

| WKUPT7              | WKUPT6                   | WKUPT5   | WKUPT4   | WKUPT3   | WKUPT2   | WKUPT1  | WKUPT0  |

|                     | -                        |          |          | -        | -        |         | -       |

| 15                  | 14                       | 13       | 12       | 11       | 10       | 9       | 8       |

| WKUPEN15            | WKUPEN14                 | WKUPEN13 | WKUPEN12 | WKUPEN11 | WKUPEN10 | WKUPEN9 | WKUPEN8 |

|                     |                          |          |          |          |          |         |         |

| 7                   | 6                        | 5        | 4        | 3        | 2        | 1       | 0       |

| WKUPEN7             | WKUPEN6                  | WKUPEN5  | WKUPEN4  | WKUPEN3  | WKUPEN2  | WKUPEN1 | WKUPEN0 |

This register is located in the VDDIO domain.

This register can only be written if the WPEN bit is cleared in the System Controller Write Protection Mode Register (SYSC\_MR).

## • WKUPEN0 - WKUPENx: Wake-up Input Enable 0 to x

0 (DISABLE): The corresponding wake-up input has no wake-up effect.

1 (ENABLE): The corresponding wake-up input is enabled for a wake-up of the core power supply.

## • WKUPT0 - WKUPTx: Wake-up Input Type 0 to x

0 (LOW): A falling edge followed by a low level for a period defined by WKUPDBC on the corresponding wake-up input forces the wake-up of the core power supply.

1 (HIGH): A rising edge followed by a high level for a period defined by WKUPDBC on the corresponding wake-up input forces the wake-up of the core power supply.

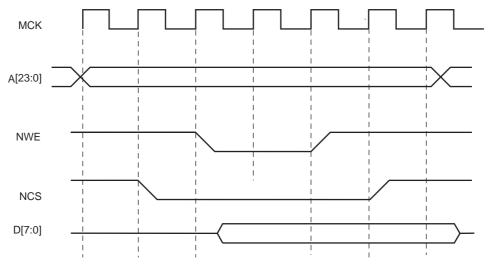

Figure 26-11. WRITE\_MODE = 1. The write operation is controlled by NWE

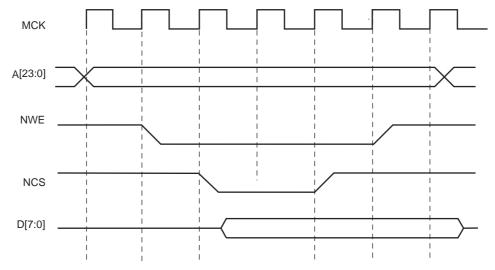

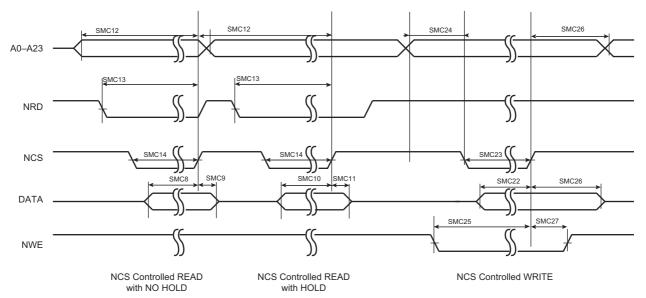

## 26.9.4.2 Write is Controlled by NCS (WRITE\_MODE = 0)

Figure 26-12 shows the waveforms of a write operation with WRITE\_MODE cleared. The data is put on the bus during the pulse and hold steps of the NCS signal. The internal data buffers are switched to Output mode after the NCS\_WR\_SETUP time, and until the end of the write cycle, regardless of the programmed waveform on NWE.

#### Figure 26-12. WRITE\_MODE = 0. The write operation is controlled by NCS

#### 26.9.5 Register Write Protection

To prevent any single software error that may corrupt SMC behavior, the registers listed below can be writeprotected by setting the WPEN bit in the SMC Write Protection Mode register (SMC\_WPMR).

If a write access in a write-protected register is detected, the WPVS flag in the SMC Write Protection Status register (SMC\_WPSR) is set and the field WPVSRC indicates in which register the write access has been attempted.

The WPVS flag is automatically cleared after reading the SSMC\_WPSR.

The following registers can be write-protected:

- "SMC Setup Register"

- "SMC Pulse Register"

# Atmel

#### 26.16.7 SMC OCMS Key2 Register Name: SMC\_KEY2 Address: 0x400E0088 Access: Write Once KEY2 KEY2 KEY2 KEY2

## • KEY2: Off Chip Memory Scrambling (OCMS) Key Part 2

When off-chip memory scrambling is enabled, setting the SMC\_OCMS and SMC\_TIMINGS registers in accordance, the data scrambling depends on KEY2 and KEY1 values.

## 29.17.15PMC Interrupt Disable Register

| Name:<br>Address: | PMC_IDR<br>0x400E0464 |    |    |         |             |               |                |

|-------------------|-----------------------|----|----|---------|-------------|---------------|----------------|

| Access:           | Write-only            |    |    |         |             |               |                |

| 31                | 30                    | 29 | 28 | 27      | 26          | 25            | 24             |

| _                 | —                     | _  | _  | _       | _           | _             | —              |

| 23                | 22                    | 21 | 20 | 19<br>— | 18<br>CFDEV | 17<br>MOSCRCS | 16<br>MOSCSELS |

| 15                | 14                    | 13 | 12 | 11      | 10          | 9             | 8              |

| _                 | -                     | —  | -  | -       | PCKRDY2     | PCKRDY1       | PCKRDY0        |

| 7                 | 6                     | 5  | 4  | 3       | 2           | 1             | 0              |

| _                 | -                     | _  | _  | MCKRDY  | LOCKB       | LOCKA         | MOSCXTS        |

The following configuration values are valid for all listed bit names of this register:

0: No effect.

- 1: Disables the corresponding interrupt.

- MOSCXTS: Main Crystal Oscillator Status Interrupt Disable

- LOCKA: PLLA Lock Interrupt Disable

- LOCKB: PLLB Lock Interrupt Disable

- MCKRDY: Master Clock Ready Interrupt Disable

- PCKRDYx: Programmable Clock Ready x Interrupt Disable

- MOSCSELS: Main Oscillator Selection Status Interrupt Disable

- MOSCRCS: Main On-Chip RC Status Interrupt Disable

- CFDEV: Clock Failure Detector Event Interrupt Disable

## Table 31-5. Register Mapping (Continued)

| Offset        | Register                                    | Name        | Access     | Reset      |

|---------------|---------------------------------------------|-------------|------------|------------|

| 0x0070        | Peripheral Select Register 1                | PIO_ABCDSR1 | Read/Write | 0x00000000 |

| 0x0074        | Peripheral Select Register 2                | PIO_ABCDSR2 | Read/Write | 0x00000000 |

| 0x0078–0x007C | Reserved                                    | _           | _          | _          |

| 0x0080        | Input Filter Slow Clock Disable Register    | PIO_IFSCDR  | Write-only | _          |

| 0x0084        | Input Filter Slow Clock Enable Register     | PIO_IFSCER  | Write-only | _          |

| 0x0088        | Input Filter Slow Clock Status Register     | PIO_IFSCSR  | Read-only  | 0x00000000 |

| 0x008C        | Slow Clock Divider Debouncing Register      | PIO_SCDR    | Read/Write | 0x00000000 |

| 0x0090        | Pad Pull-down Disable Register              | PIO_PPDDR   | Write-only | _          |

| 0x0094        | Pad Pull-down Enable Register               | PIO_PPDER   | Write-only | _          |

| 0x0098        | Pad Pull-down Status Register               | PIO_PPDSR   | Read-only  | (1)        |

| 0x009C        | Reserved                                    | _           | _          | _          |

| 0x00A0        | Output Write Enable                         | PIO_OWER    | Write-only | _          |

| 0x00A4        | Output Write Disable                        | PIO_OWDR    | Write-only | _          |

| 0x00A8        | Output Write Status Register                | PIO_OWSR    | Read-only  | 0x00000000 |

| 0x00AC        | Reserved                                    | -           | _          | _          |

| 0x00B0        | Additional Interrupt Modes Enable Register  | PIO_AIMER   | Write-only | _          |

| 0x00B4        | Additional Interrupt Modes Disable Register | PIO_AIMDR   | Write-only | _          |

| 0x00B8        | Additional Interrupt Modes Mask Register    | PIO_AIMMR   | Read-only  | 0x00000000 |

| 0x00BC        | Reserved                                    | -           | _          | _          |

| 0x00C0        | Edge Select Register                        | PIO_ESR     | Write-only | _          |

| 0x00C4        | Level Select Register                       | PIO_LSR     | Write-only | _          |

| 0x00C8        | Edge/Level Status Register                  | PIO_ELSR    | Read-only  | 0x00000000 |

| 0x00CC        | Reserved                                    | -           | _          | _          |

| 0x00D0        | Falling Edge/Low-Level Select Register      | PIO_FELLSR  | Write-only | _          |

| 0x00D4        | Rising Edge/High-Level Select Register      | PIO_REHLSR  | Write-only | _          |

| 0x00D8        | Fall/Rise - Low/High Status Register        | PIO_FRLHSR  | Read-only  | 0x00000000 |

| 0x00DC        | Reserved                                    | _           | _          | _          |

| 0x00E0        | Lock Status                                 | PIO_LOCKSR  | Read-only  | 0x00000000 |

| 0x00E4        | Write Protection Mode Register              | PIO_WPMR    | Read/Write | 0x00000000 |

| 0x00E8        | Write Protection Status Register            | PIO_WPSR    | Read-only  | 0x00000000 |

| 0x00EC-0x00FC | Reserved                                    | -           | _          | _          |

| 0x0100        | Schmitt Trigger Register                    | PIO_SCHMITT | Read/Write | 0x00000000 |

| 0x0104–0x010C | Reserved                                    | -           | _          | _          |

| 0x0110        | Reserved                                    | -           | -          | -          |

| 0x0114–0x011C | Reserved                                    | -           | _          | _          |

| 0x0120–0x014C | Reserved                                    | -           | -          | -          |

| 0x0150        | Parallel Capture Mode Register              | PIO_PCMR    | Read/Write | 0x00000000 |

## 31.6.4 PIO Output Enable Register

## Address: 0x400E0E10 (PIOA), 0x400E1010 (PIOB), 0x400E1210 (PIOC)

Access: Write-only

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

| P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

| P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

This register can only be written if the WPEN bit is cleared in the PIO Write Protection Mode Register.

## • P0-P31: Output Enable

0: No effect.

1: Enables the output on the I/O line.

## 31.6.13 PIO Pin Data Status Register

Name: PIO\_PDSR

Address: 0x400E0E3C (PIOA), 0x400E103C (PIOB), 0x400E123C (PIOC)

Access: Read-only

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

| P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

| P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

## • P0-P31: Output Data Status

0: The I/O line is at level 0.

1: The I/O line is at level 1.

## 31.6.20 PIO Multi-driver Status Register

Name: PIO\_MDSR

Address: 0x400E0E58 (PIOA), 0x400E1058 (PIOB), 0x400E1258 (PIOC)

Access: Read-only

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

| P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

| P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

## • P0-P31: Multi-drive Status

0: The multi-drive is disabled on the I/O line. The pin is driven at high- and low-level.

1: The multi-drive is enabled on the I/O line. The pin is driven at low-level only.

## 31.6.26 PIO Input Filter Slow Clock Disable Register

| Name:<br>Address: | PIO_IFSCDR<br>0x400E0E80 (PI | OA), 0x400E10 | 080 (PIOB), 0x4 | 100E1280 (PIOC | C)  |     |     |

|-------------------|------------------------------|---------------|-----------------|----------------|-----|-----|-----|

| Access:           | Write-only                   |               |                 |                |     |     |     |

| 31                | 30                           | 29            | 28              | 27             | 26  | 25  | 24  |

| P31               | P30                          | P29           | P28             | P27            | P26 | P25 | P24 |

| 23                | 22                           | 21            | 20              | 19             | 18  | 17  | 16  |

| P23               | P22                          | P21           | P20             | P19            | P18 | P17 | P16 |

| 15                | 14                           | 13            | 12              | 11             | 10  | 9   | 8   |

| P15               | P14                          | P13           | P12             | P11            | P10 | P9  | P8  |

| 7                 | 6                            | 5             | 4               | 3              | 2   | 1   | 0   |

| P7                | P6                           | P5            | P4              | P3             | P2  | P1  | P0  |

## • P0–P31: Peripheral Clock Glitch Filtering Select

0: No effect.

1: The glitch filter is able to filter glitches with a duration <  $t_{peripheral clock}/2$ .

- DSRIC: Data Set Ready Input Change Enable

- DCDIC: Data Carrier Detect Input Change Interrupt Enable

- CTSIC: Clear to Send Input Change Interrupt Enable

- MANE: Manchester Error Interrupt Enable

## 37.7 Timer Counter (TC) User Interface

## Table 37-6.Register Mapping

| Offset <sup>(1)</sup>        | Register                        | Name    | Access                    | Reset |

|------------------------------|---------------------------------|---------|---------------------------|-------|

| 0x00 + channel * 0x40 + 0x00 | Channel Control Register        | TC_CCR  | Write-only                | -     |

| 0x00 + channel * 0x40 + 0x04 | Channel Mode Register           | TC_CMR  | Read/Write                | 0     |

| 0x00 + channel * 0x40 + 0x08 | Stepper Motor Mode Register     | TC_SMMR | Read/Write                | 0     |

| 0x00 + channel * 0x40 + 0x0C | Reserved                        | -       | _                         | _     |

| 0x00 + channel * 0x40 + 0x10 | Counter Value                   | TC_CV   | Read-only                 | 0     |

| 0x00 + channel * 0x40 + 0x14 | Register A                      | TC_RA   | Read/Write <sup>(2)</sup> | 0     |

| 0x00 + channel * 0x40 + 0x18 | Register B                      | TC_RB   | Read/Write <sup>(2)</sup> | 0     |

| 0x00 + channel * 0x40 + 0x1C | Register C                      | TC_RC   | Read/Write                | 0     |

| 0x00 + channel * 0x40 + 0x20 | Status Register                 | TC_SR   | Read-only                 | 0     |

| 0x00 + channel * 0x40 + 0x24 | Interrupt Enable Register       | TC_IER  | Write-only                | -     |

| 0x00 + channel * 0x40 + 0x28 | Interrupt Disable Register      | TC_IDR  | Write-only                | _     |

| 0x00 + channel * 0x40 + 0x2C | Interrupt Mask Register         | TC_IMR  | Read-only                 | 0     |

| 0xC0                         | Block Control Register          | TC_BCR  | Write-only                | _     |

| 0xC4                         | Block Mode Register             | TC_BMR  | Read/Write                | 0     |

| 0xC8                         | QDEC Interrupt Enable Register  | TC_QIER | Write-only                | _     |

| 0xCC                         | QDEC Interrupt Disable Register | TC_QIDR | Write-only                | _     |

| 0xD0                         | QDEC Interrupt Mask Register    | TC_QIMR | Read-only                 | 0     |

| 0xD4                         | QDEC Interrupt Status Register  | TC_QISR | Read-only                 | 0     |

| 0xD8                         | Fault Mode Register             | TC_FMR  | Read/Write                | 0     |

| 0xE4                         | Write Protection Mode Register  | TC_WPMR | Read/Write                | 0     |

| 0xE8–0xFC                    | Reserved                        | _       | _                         | _     |

Notes: 1. Channel index ranges from 0 to 2.

2. Read-only if TC\_CMRx.WAVE = 0

## 43.7.3 DACC Channel Enable Register

| Name:    | DACC_CHER  |    |    |    |    |     |     |

|----------|------------|----|----|----|----|-----|-----|

| Address: | 0x4003C010 |    |    |    |    |     |     |

| Access:  | Write-only |    |    |    |    |     |     |

| 31       | 30         | 29 | 28 | 27 | 26 | 25  | 24  |

| -        | -          | -  | -  | -  | -  | -   | -   |

| 23       | 22         | 21 | 20 | 19 | 18 | 17  | 16  |

| —        | -          | —  | —  | —  | —  | —   | —   |

| 15       | 14         | 13 | 12 | 11 | 10 | 9   | 8   |

| —        | -          | —  | —  | —  | —  | —   | —   |

| 7        | 6          | 5  | 4  | 3  | 2  | 1   | 0   |

| _        | -          | -  | -  | -  | -  | CH1 | CH0 |

This register can only be written if the WPEN bit is cleared in the DACC Write Protection Mode Register.

## • CHx: Channel x Enable

0: No effect

1: Enables the corresponding channel

## 44.5 Oscillator Characteristics

## 44.5.1 32 kHz RC Oscillator Characteristics

Table 44-26. 32 kHz RC Oscillator Characteristics

| Symbol             | Parameter                        | Conditions                                                           | Min | Тур | Max | Unit |

|--------------------|----------------------------------|----------------------------------------------------------------------|-----|-----|-----|------|

| f <sub>OSC</sub>   | RC Oscillator Frequency          |                                                                      | 20  | 32  | 44  | kHz  |

|                    | Frequency Supply Dependency      |                                                                      | -3  | -   | 3   | %/V  |

|                    | Frequency Temperature Dependency | Over temperature range (-40 to 105 °C) versus<br>T <sub>A</sub> 25°C | -7  | _   | 7   | %    |

| Duty               | Duty Cycle                       |                                                                      | 45  | 50  | 55  | %    |

| t <sub>START</sub> | Startup Time                     |                                                                      | -   | -   | 100 | μs   |

|                    |                                  | After startup time                                                   |     |     |     |      |

| I <sub>DDON</sub>  | Current Consumption              | Temp. range = -40 to 125 °C                                          | -   | 540 | 860 | nA   |

|                    |                                  | Typical consumption at 2.2V supply and $\rm T_A$ 25°C                |     |     |     |      |

## 44.5.2 4/8/12 MHz RC Oscillators Characteristics

## Table 44-27. 4/8/12 MHz RC Oscillators Characteristics

| Symbol             | Parameter                                 | Conditions                                                                  | Min | Typ Max |     | Unit              |  |

|--------------------|-------------------------------------------|-----------------------------------------------------------------------------|-----|---------|-----|-------------------|--|

| f <sub>OSC</sub>   | RC Oscillator Frequency Range             | (1)                                                                         | 4   |         | 12  | MHz               |  |

| ACC <sub>4</sub>   | 4 MHz Total Accuracy                      | -40°C < Temp < +105°C<br>4 MHz output selected <sup>(1)(2)</sup>            | -   | -       | ±30 | %                 |  |

| ACC <sub>8</sub>   | 8 MHz Total Accuracy                      | -40°C < Temp < +105°C<br>8 MHz output selected <sup>(1)(3)</sup>            | -   | -       | ±5  | %                 |  |

| ACC <sub>12</sub>  | 12 MHz Total Accuracy                     | $-40^{\circ}$ C < Temp < +105°C<br>12 MHz output selected <sup>(1)(3)</sup> | -   | -       | ±5  | %                 |  |

|                    | Frequency Deviction versus Trimming Code  | 8 MHz                                                                       |     | 47      | _   | kHz/trimming and  |  |

|                    | Frequency Deviation versus Trimming Code  | 12 MHz                                                                      | _   | 64      | -   | kHz/trimming code |  |

| Duty               | Duty Cycle                                |                                                                             | 45  | 50      | 55  | %                 |  |

| t <sub>START</sub> | Startup Time                              |                                                                             | -   | _       | 10  | μs                |  |

|                    |                                           | 4 MHz                                                                       |     | 50      | 75  |                   |  |

| I <sub>DDON</sub>  | Active Current Consumption <sup>(2)</sup> | 8 MHz                                                                       | -   | 65      | 95  | μA                |  |

|                    |                                           | 12 MHz                                                                      |     | 82      | 118 |                   |  |

Notes: 1. Frequency range can be configured in the Supply Controller registers

2. Not trimmed from factory

3. After trimming from factory

The 4/8/12 MHz Fast RC oscillator is calibrated in production. This calibration can be read through the Get CALIB bit command (refer to the EEFC section) and the frequency can be trimmed by software through the PMC.

|                   |                                         | N                                                                                                                                                       | lin                                                                                                                                                    | M              |                |      |

|-------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|------|

| Symbol            | Parameter                               | 1.8V Domain                                                                                                                                             | 3.3V Domain                                                                                                                                            | 1.8V<br>Domain | 3.3V<br>Domain | Unit |

| SMC <sub>22</sub> | Data Out Valid before NCS High          | NCS_WR_PULSE<br>× t <sub>CPMCK</sub> - 6.3                                                                                                              | NCS_WR_PULSE<br>× t <sub>CPMCK</sub> - 6.2                                                                                                             | -              | _              | ns   |

| SMC <sub>23</sub> | NCS Pulse Width                         | NCS_WR_PULSE<br>× t <sub>CPMCK</sub> - 7.7                                                                                                              | NCS_WR_PULSE<br>× t <sub>CPMCK</sub> - 6.7                                                                                                             | _              | _              | ns   |

| SMC <sub>24</sub> | A0–A22 Valid before NCS Low             | NCS_WR_SETUP<br>× t <sub>CPMCK</sub> - 6.5                                                                                                              | NCS_WR_SETUP<br>× t <sub>CPMCK</sub> - 6.3                                                                                                             | _              | _              | ns   |

| SMC <sub>25</sub> | NWE Low before NCS High                 | $\begin{array}{c} (\text{NCS}_{\text{WR}} \text{SETUP} - \\ \text{NWE}_{\text{SETUP}} + \text{NCS pulse}) \\ \times t_{\text{CPMCK}} - 5.1 \end{array}$ | $\begin{array}{c} (\text{NCS}\_\text{WR}\_\text{SETUP} - \\ \text{NWE}\_\text{SETUP} + \text{NCS pulse}) \\ \times t_{\text{CPMCK}} - 4.9 \end{array}$ | _              | _              | ns   |

| SMC <sub>26</sub> | NCS High to Data Out, A0–A25,<br>Change | NCS_WR_HOLD<br>× t <sub>CPMCK</sub> - 10.2                                                                                                              | NCS_WR_HOLD<br>× t <sub>CPMCK</sub> - 8.4                                                                                                              | _              | _              | ns   |

| SMC <sub>27</sub> | NCS High to NWE Inactive                | (NCS_WR_HOLD -<br>NWE_HOLD) × t <sub>CPMCK</sub> - 2.1                                                                                                  | (NCS_WR_HOLD -<br>NWE_HOLD) × t <sub>CPMCK</sub> - 1.6                                                                                                 | -              | _              | ns   |

#### Table 44-70. SMC Write Signals - NCS Controlled (WRITE\_MODE = 0)

#### 48.3.3 Brownout Detector

#### Issue: Unpredictable Behavior if BOD is Disabled, VDDCORE is Lost and VDDIO is Connected

In active mode or in wait mode, if the Brownout Detector is disabled (SUPC\_MR.BODDIS = 1) and power is lost on VDDCORE while VDDIO is powered, the device might not be properly reset and may behave unpredictably.

**Workaround:** When the Brownout Detector is disabled in active or in wait mode, VDDCORE always needs to be powered.

#### 48.3.4 Low-power Mode

## Issue: Unpredictable Behavior When Entering Sleep Mode

When entering Sleep mode, if an interrupt occurs during WFI or WFE (PMC\_FSMR.LPM = 0) instruction processing, the ARM core may read an incorrect data, thus leading to unpredictable behavior of the software. This issue is not present in Wait mode.

#### Workaround: The following conditions must be met:

- 1. The interrupt vector table must be located in Flash.

- The Matrix slave interface for the Flash must be set to 'No default master'. This is done by setting the field DEFMSTR\_TYPE to 0 in the register MATRIX\_SCFG. The code example below can be used to program the NO\_DEFAULT\_MASTER state:

$MATRIX\_SCFG[2] = MATRIX\_SCFG\_SLOT\_CYCLE(0xFF) | MATRIX\_SCFG\_DEFMSTR\_TYPE(0x0);$ This must be done once in the software before entering Sleep mode.

#### 48.3.5 PIO

#### Issue: PB4 Input Low-level Voltage Range

The undershoot is limited to -0.1V.

In normal operating conditions, the  $V_{II}$  minimum value on PB4 is limited to 0V.

**Workaround:** The voltage on PB4 with respect to ground must be in the range -0.1V to + VDDIO + 0.4V instead of -0.3V to + VDDIO + 0.4V for all other input pins, as shown in Table 44.1 "Absolute Maximum Ratings".

The minimum  $V_{IL}$  on PB4 must be 0V instead of -0.3V for all other input pins, as shown in Table 44.3 "DC Characteristics".

Atmel

#### Table 49-3. SAM4S Datasheet Rev. 11100I Revision History

| Doc. Date | Changes                                                                                                                                                                                                                                       |  |  |  |  |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|           | Introduction of four new devices: ATSAM4SD32BA-UUR, ATSAM4SD32BB-UUR, ATSAM4SD16BA-UUR and ATSAM4SD16BB-UUR                                                                                                                                   |  |  |  |  |  |

|           | Modified "Description", Section 2. "Block Diagram", and Section 6.5, "ERASE Pin"                                                                                                                                                              |  |  |  |  |  |

|           | Updated Table 9-1 "Real-time Event Mapping List"<br>Added footnotes in Table 11-2 "Multiplexing on PIO Controller A (PIOA)", Table 11-3 "Multiplexing on PIO Controller B<br>(PIOB)" and Table 11-4 "Multiplexing on PIO Controller C (PIOC)" |  |  |  |  |  |

|           | Deleted reset value from individual register description sections (reset values are found in "register mapping" sections)                                                                                                                     |  |  |  |  |  |

|           | Section 12., "ARM Cortex-M4 Processor"                                                                                                                                                                                                        |  |  |  |  |  |

|           | Figure 12-1 "Typical Cortex-M4 Implementation"; replaced "Cortex-M4" with "Cortex-M4F"                                                                                                                                                        |  |  |  |  |  |

|           | Table 12-11 "Faults": note 1 now applied to IACCVIOL.                                                                                                                                                                                         |  |  |  |  |  |

|           | Section 12.9.1.13 "Configurable Fault Status Register": removed 'MLSPERR' bit                                                                                                                                                                 |  |  |  |  |  |

|           | Table 12-34 "System Timer (SYST) Register Mapping": corrected SYST_CSR reset value                                                                                                                                                            |  |  |  |  |  |

|           | Section 13., "Debug and Test Features"                                                                                                                                                                                                        |  |  |  |  |  |

|           | Modified Section 13.5.2 "Debug Architecture"                                                                                                                                                                                                  |  |  |  |  |  |

|           | Section 14., "Reset Controller (RSTC)"                                                                                                                                                                                                        |  |  |  |  |  |

|           | Figure 14-3 "General Reset State": corrected signal name to vddio_nreset                                                                                                                                                                      |  |  |  |  |  |

|           | Section 14.4, "Functional Description": deleted subsection "Brownout Manager" and redundant subsection "Reset Controller Status Register" (register is described in Section 14.5.2, "Reset Controller Status Register")                       |  |  |  |  |  |

|           | Updated Section 14.4.1, "Reset Controller Overview"                                                                                                                                                                                           |  |  |  |  |  |

| 03-Apr-15 | Section 14.4.3, "Reset States": organized subsections in order of reset state priority                                                                                                                                                        |  |  |  |  |  |

|           | Section 14.4.4, "Reset State Priorities": reworded first paragraph                                                                                                                                                                            |  |  |  |  |  |

|           | Section 14.5.2, "Reset Controller Status Register": updated bit and field descriptions                                                                                                                                                        |  |  |  |  |  |

|           | Section 15., "Real-time Timer (RTT)"                                                                                                                                                                                                          |  |  |  |  |  |

|           | Updated Figure 15-2 "RTT Counting" and Section 15.4 "Functional Description"                                                                                                                                                                  |  |  |  |  |  |

|           | Section 15.5.1 "Real-time Timer Mode Register": updated RTPRES field description                                                                                                                                                              |  |  |  |  |  |

|           | Modified ALMV description in Section 15.5.2 "Real-time Timer Alarm Register"                                                                                                                                                                  |  |  |  |  |  |

|           | Section 15.5.2 "Real-time Timer Alarm Register": added "(cleared on read)" to each bit description                                                                                                                                            |  |  |  |  |  |

|           | Added notes in Section 15.5.3 "Real-time Timer Value Register"                                                                                                                                                                                |  |  |  |  |  |

|           | Section 16., "Real-time Clock (RTC)"                                                                                                                                                                                                          |  |  |  |  |  |

|           | Replaced "APB" with "System Bus" in Section 16.3, "Block Diagram"                                                                                                                                                                             |  |  |  |  |  |

|           | Updated "Section 16.1, "Description" and Section 16.5, "Functional Description" (removed references to the 20th century)                                                                                                                      |  |  |  |  |  |

|           | Section 16.5.5, "RTC Internal Free Running Counter Error Checking": replaced "RTC status clear control register" with "Status Clear Command Register"                                                                                         |  |  |  |  |  |

|           | Updated Section 16.5.7, "RTC Accurate Clock Calibration" (added figures and descriptions)                                                                                                                                                     |  |  |  |  |  |

|           | Updated Section 16.6.2, "RTC Mode Register" and Section 16.6.11, "RTC Interrupt Mask Register"                                                                                                                                                |  |  |  |  |  |

|           | Section 17., "Watchdog Timer (WDT)"                                                                                                                                                                                                           |  |  |  |  |  |

|           | In Figure 17-2 "Watchdog Behavior", "WDT_CR = WDRSTT" replaced with "WDT_CR.WDRSTT=1"                                                                                                                                                         |  |  |  |  |  |

|           | Updated Section 17.5.3 "Watchdog Timer Status Register"                                                                                                                                                                                       |  |  |  |  |  |

Atmel