Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                            |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 120MHz                                                                     |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, Memory Card, SPI, SSC, UART/USART, USB    |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                 |

| Number of I/O              | 79                                                                         |

| Program Memory Size        | 1MB (1M x 8)                                                               |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 160K × 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                               |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 100-VFBGA                                                                  |

| Supplier Device Package    | 100-VFBGA (7x7)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4sd16cb-cfn |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 11. Peripherals

# 11.1 Peripheral Identifiers

Table 11-1 defines the Peripheral Identifiers of the SAM4S. A peripheral identifier is required for the control of the peripheral interrupt with the Nested Vectored Interrupt Controller and control of the peripheral clock with the Power Management Controller.

|             | r emplierar identifie |                |                                 | · · · · · · · · · · · · · · · · · · ·                        |

|-------------|-----------------------|----------------|---------------------------------|--------------------------------------------------------------|

| Instance ID | Instance Name         | NVIC Interrupt | PMC Clock Control               | Instance Description                                         |

| 0           | SUPC                  | Х              |                                 | Supply Controller                                            |

| 1           | RSTC                  | Х              | Reset Controller                |                                                              |

| 2           | RTC                   | Х              |                                 | Real-Time Clock                                              |

| 3           | RTT                   | Х              |                                 | Real-Time Timer                                              |

| 4           | WDT                   | Х              |                                 | Watchdog Timer                                               |

| 5           | PMC                   | Х              |                                 | Power Management Controller                                  |

| 6           | EEFC0                 | Х              |                                 | Enhanced Embedded Flash Controller 0                         |

| 7           | EEFC1                 | _              |                                 | Enhanced Embedded Flash Controller 1                         |

| 8           | UART0                 | х              | х                               | Universal Asynchronous Receiver<br>Transmitter 0             |

| 9           | UART1                 | х              | Х                               | Universal Asynchronous Receiver<br>Transmitter 1             |

| 10          | SMC                   | _              | Х                               | Static Memory Controller                                     |

| 11          | PIOA                  | Х              | Х                               | Parallel I/O Controller A                                    |

| 12          | PIOB                  | Х              | Х                               | Parallel I/O Controller B                                    |

| 13          | PIOC                  | Х              | Х                               | Parallel I/O Controller C                                    |

| 14          | USART0                | х              | Х                               | Universal Synchronous Asynchronous<br>Receiver Transmitter 0 |

| 15          | USART1                | х              | Х                               | Universal Synchronous Asynchronous<br>Receiver Transmitter 1 |

| 16          | _                     | _              | – Reserved                      |                                                              |

| 17          | _                     | _              | _                               | Reserved                                                     |

| 18          | HSMCI                 | Х              | Х                               | Multimedia Card Interface                                    |

| 19          | TWIO                  | Х              | Х                               | Two-Wire Interface 0                                         |

| 20          | TWI1                  | Х              | Х                               | Two-Wire Interface 1                                         |

| 21          | SPI                   | Х              | Х                               | Serial Peripheral Interface                                  |

| 22          | SSC                   | Х              | X Synchronous Serial Controller |                                                              |

| 23          | TC0                   | Х              | Х                               | Timer/Counter 0                                              |

| 24          | TC1                   | Х              | Х                               | Timer/Counter 1                                              |

| 25          | TC2                   | Х              | Х                               | Timer/Counter 2                                              |

| 26          | TC3                   | Х              | Х                               | Timer/Counter 3                                              |

| 27          | TC4                   | Х              | Х                               | Timer/Counter 4                                              |

| 28          | TC5                   | Х              | Х                               | Timer/Counter 5                                              |

Table 11-1. Peripheral Identifiers

#### Table 12-4. Memory Access Behavior

| Address Range         | Memory Region          | Memory<br>Type                      | XN | Description                                                                                                                          |

|-----------------------|------------------------|-------------------------------------|----|--------------------------------------------------------------------------------------------------------------------------------------|

| 0x00000000-0x1FFFFFF  | Code                   | Normal <sup>(1)</sup>               | _  | Executable region for program code. Data can also be put here.                                                                       |

| 0x20000000-0x3FFFFFFF | SRAM                   | Normal <sup>(1)</sup>               | _  | Executable region for data. Code can also be put here.<br>This region includes bit band and bit band alias areas,<br>see Table 12-6. |

| 0x40000000-0x5FFFFFF  | Peripheral             | Device <sup>(1)</sup>               | XN | This region includes bit band and bit band alias areas, see Table 12-6.                                                              |

| 0x60000000-0x9FFFFFF  | External RAM           | Normal <sup>(1)</sup>               | _  | Executable region for data                                                                                                           |

| 0xA0000000-0xDFFFFFF  | External device        | Device <sup>(1)</sup>               | XN | External Device memory                                                                                                               |

| 0xE0000000-0xE00FFFF  | Private Peripheral Bus | Strongly-<br>ordered <sup>(1)</sup> | XN | This region includes the NVIC, system timer, and system control block.                                                               |

| 0xE0100000-0xFFFFFFFF | Reserved               | Device <sup>(1)</sup>               | XN | Reserved                                                                                                                             |

Note: 1. See "Memory Regions, Types and Attributes" for more information.

The Code, SRAM, and external RAM regions can hold programs. However, ARM recommends that programs always use the Code region. This is because the processor has separate buses that enable instruction fetches and data accesses to occur simultaneously.

The MPU can override the default memory access behavior described in this section. For more information, see "Memory Protection Unit (MPU)".

Additional Memory Access Constraints For Caches and Shared Memory

When a system includes caches or shared memory, some memory regions have additional access constraints, and some regions are subdivided, as Table 12-5 shows.

| Address Range         | Memory Region             | Memory Type                     | Shareability                 | Cache Policy        |

|-----------------------|---------------------------|---------------------------------|------------------------------|---------------------|

| 0x00000000-0x1FFFFFF  | Code                      | Normal <sup>(1)</sup>           | _                            | WT <sup>(2)</sup>   |

| 0x20000000-0x3FFFFFF  | SRAM                      | Normal <sup>(1)</sup>           | -                            | WBWA <sup>(2)</sup> |

| 0x40000000-0x5FFFFFF  | Peripheral                | Device <sup>(1)</sup>           | -                            | _                   |

| 0x60000000-0x7FFFFFFF |                           | N                               |                              | WBWA <sup>(2)</sup> |

| 0x80000000-0x9FFFFFF  | External RAM              | Normal <sup>(1)</sup>           | -                            | WT <sup>(2)</sup>   |

| 0xA0000000-0xBFFFFFF  | Esternal desides          | Device <sup>(1)</sup>           | Shareable <sup>(1)</sup>     |                     |

| 0xC0000000-0xDFFFFFF  | External device           | Device                          | Non-shareable <sup>(1)</sup> |                     |

| 0xE0000000-0xE00FFFFF | Private Peripheral<br>Bus | Strongly-ordered <sup>(1)</sup> | Shareable <sup>(1)</sup>     | _                   |

| 0xE0100000-0xFFFFFFFF | Vendor-specific<br>device | Device <sup>(1)</sup>           | -                            | _                   |

Table 12-5. Memory Region Shareability and Cache Policies

Notes: 1. See "Memory Regions, Types and Attributes" for more information.

2. WT = Write through, no write allocate. WBWA = Write back, write allocate. See the "Glossary" for more information. *Instruction Prefetch and Branch Prediction*

The Cortex-M4 processor:

# Atmel

#### 12.6.10.3 IT

If-Then condition instruction.

Syntax

$IT{x{y{z}}} cond$

where:

- x specifies the condition switch for the second instruction in the IT block.

- y specifies the condition switch for the third instruction in the IT block.

z specifies the condition switch for the fourth instruction in the IT block.

cond specifies the condition for the first instruction in the IT block.

The condition switch for the second, third and fourth instruction in the IT block can be either:

T Then. Applies the condition *cond* to the instruction.

E Else. Applies the inverse condition of *cond* to the instruction.

It is possible to use AL (the *always* condition) for *cond* in an IT instruction. If this is done, all of the instructions in the IT block must be unconditional, and each of *x*, *y*, and *z* must be T or omitted but not E.

#### Operation

The IT instruction makes up to four following instructions conditional. The conditions can be all the same, or some of them can be the logical inverse of the others. The conditional instructions following the IT instruction form the *IT block*.

The instructions in the IT block, including any branches, must specify the condition in the {cond} part of their syntax.

The assembler might be able to generate the required IT instructions for conditional instructions automatically, so that the user does not have to write them. See the assembler documentation for details.

A BKPT instruction in an IT block is always executed, even if its condition fails.

Exceptions can be taken between an IT instruction and the corresponding IT block, or within an IT block. Such an exception results in entry to the appropriate exception handler, with suitable return information in LR and stacked PSR.

Instructions designed for use for exception returns can be used as normal to return from the exception, and execution of the IT block resumes correctly. This is the only way that a PC-modifying instruction is permitted to branch to an instruction in an IT block.

#### Restrictions

The following instructions are not permitted in an IT block:

- IT

- CBZ and CBNZ

- CPSID and CPSIE.

Other restrictions when using an IT block are:

- A branch or any instruction that modifies the PC must either be outside an IT block or must be the last instruction inside the IT block. These are:

- ADD PC, PC, Rm

- MOV PC, Rm

- B, BL, BX, BLX

- Any LDM, LDR, or POP instruction that writes to the PC

- TBB and TBH

- Do not branch to any instruction inside an IT block, except when returning from an exception handler

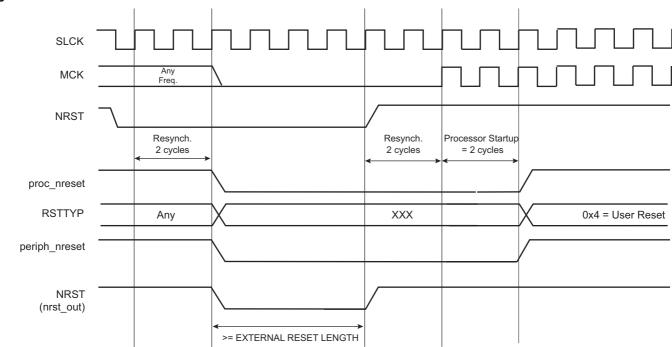

The NRST manager guarantees that the NRST line is asserted for External Reset Length slow clock cycles, as programmed in field RSTC\_MR.ERSTL. However, if NRST does not rise after External Reset Length because it is driven low externally, the internal reset lines remain asserted until NRST actually rises.

#### Figure 14-6. User Reset State

#### 14.4.4 Reset State Priorities

The reset state manager manages the priorities among the different reset sources. The resets are listed in order of priority as follows:

- 1. General reset

- 2. Backup reset

- 3. Watchdog reset

- 4. Software reset

- 5. User reset

Particular cases are listed below:

- When in user reset:

- A watchdog event is impossible because the Watchdog Timer is being reset by the proc\_nreset signal.

- A software reset is impossible, since the processor reset is being activated.

- When in software reset:

- A watchdog event has priority over the current state.

- The NRST has no effect.

- When in watchdog reset:

- The processor reset is active and so a software reset cannot be programmed.

- A user reset cannot be entered.

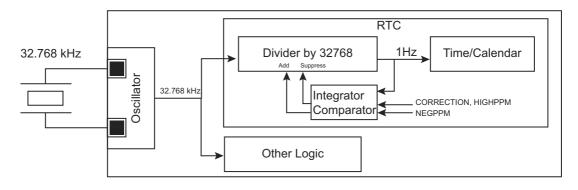

#### 16.5.7 RTC Accurate Clock Calibration

The crystal oscillator that drives the RTC may not be as accurate as expected mainly due to temperature variation. The RTC is equipped with circuitry able to correct slow clock crystal drift.

To compensate for possible temperature variations over time, this accurate clock calibration circuitry can be programmed on-the-fly and also programmed during application manufacturing, in order to correct the crystal frequency accuracy at room temperature  $(20-25^{\circ}C)$ . The typical clock drift range at room temperature is  $\pm 20$  ppm.

In the device operating temperature range, the 32.768 kHz crystal oscillator clock inaccuracy can be up to -200 ppm.

The RTC clock calibration circuitry allows positive or negative correction in a range of 1.5 ppm to 1950 ppm.

The calibration circuitry is fully digital. Thus, the configured correction is independent of temperature, voltage, process, etc., and no additional measurement is required to check that the correction is effective.

If the correction value configured in the calibration circuitry results from an accurate crystal frequency measure, the remaining accuracy is bounded by the values listed below:

- Below 1 ppm, for an initial crystal drift between 1.5 ppm up to 20 ppm, and from 30 ppm to 90 ppm

- Below 2 ppm, for an initial crystal drift between 20 ppm up to 30 ppm, and from 90 ppm to 130 ppm

- Below 5 ppm, for an initial crystal drift between 130 ppm up to 200 ppm

The calibration circuitry does not modify the 32.768 kHz crystal oscillator clock frequency but it acts by slightly modifying the 1 Hz clock period from time to time. When the period is modified, depending on the sign of the correction, the 1 Hz clock period increases or reduces by around 4 ms. Depending on the CORRECTION, NEGPPM and HIGHPPM values configured in RTC\_MR, the period interval between two correction events differs.

#### Figure 16-3. Calibration circuitry

| 16.6.3 RTC | CTime Register |    |      |     |    |    |    |  |

|------------|----------------|----|------|-----|----|----|----|--|

| Name:      | RTC_TIMR       |    |      |     |    |    |    |  |

| Address:   | 0x400E1468     |    |      |     |    |    |    |  |

| Access:    | Read/Write     |    |      |     |    |    |    |  |

| 31         | 30             | 29 | 28   | 27  | 26 | 25 | 24 |  |

| -          | _              | _  | _    | _   | _  | _  | _  |  |

| 23         | 22             | 21 | 20   | 19  | 18 | 17 | 16 |  |

| _          | AMPM           |    | HOUR |     |    |    |    |  |

| 15         | 14             | 13 | 12   | 11  | 10 | 9  | 8  |  |

| -          |                |    |      | MIN |    |    |    |  |

| 7          | 6              | 5  | 4    | 3   | 2  | 1  | 0  |  |

| -          |                |    |      | SEC |    |    |    |  |

## • SEC: Current Second

The range that can be set is 0–59 (BCD).

The lowest four bits encode the units. The higher bits encode the tens.

#### • MIN: Current Minute

The range that can be set is 0–59 (BCD).

The lowest four bits encode the units. The higher bits encode the tens.

#### • HOUR: Current Hour

The range that can be set is 1–12 (BCD) in 12-hour mode or 0–23 (BCD) in 24-hour mode.

## • AMPM: Ante Meridiem Post Meridiem Indicator

This bit is the AM/PM indicator in 12-hour mode.

0: AM.

1: PM.

All non-significant bits read zero.

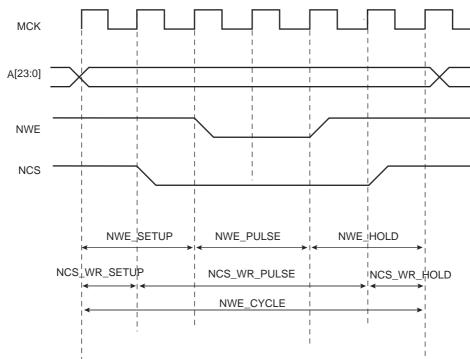

#### 26.9.3 Write Waveforms

The write protocol is similar to the read protocol. It is depicted in Figure 26-9. The write cycle starts with the address setting on the memory address bus.

#### 26.9.3.1 NWE Waveforms

The NWE signal is characterized by a setup timing, a pulse width and a hold timing.

- NWE\_SETUP—the NWE setup time is defined as the setup of address and data before the NWE falling edge;

- NWE\_PULSE—the NWE pulse length is the time between NWE falling edge and NWE rising edge;

- NWE\_HOLD—the NWE hold time is defined as the hold time of address and data after the NWE rising edge.

#### 26.9.3.2 NCS Waveforms

The NCS signal waveforms in write operation are not the same that those applied in read operations, but are separately defined:

- NCS\_WR\_SETUP—the NCS setup time is defined as the setup time of address before the NCS falling edge.

- NCS\_WR\_PULSE—the NCS pulse length is the time between NCS falling edge and NCS rising edge;

- NCS\_WR\_HOLD—the NCS hold time is defined as the hold time of address after the NCS rising edge.

#### Figure 26-9. Write Cycle

# 26.9.3.3 Write Cycle

The write\_cycle time is defined as the total duration of the write cycle, that is, from the time where address is set on the address bus to the point where address may change. The total write cycle time is equal to:

NWE\_CYCLE=NWE\_SETUP + NWE\_PULSE + NWE\_HOLD=NCS\_WR\_SETUP + NCS\_WR\_PULSE + NCS\_WR\_HOLD

All NWE and NCS (write) timings are defined separately for each chip select as an integer number of Master Clock cycles. To ensure that the NWE and NCS timings are consistent, the user must define the total write cycle instead of the hold timing. This implicitly defines the NWE hold time and NCS (write) hold times as:

In Page mode, the programming of the read timings is described in Table 26-8:

| Parameter    | Value           | Definition                                     |

|--------------|-----------------|------------------------------------------------|

| READ_MODE    | 'x'             | No impact                                      |

| NCS_RD_SETUP | 'x'             | No impact                                      |

| NCS_RD_PULSE | t <sub>pa</sub> | Access time of first access to the page        |

| NRD_SETUP    | 'x'             | No impact                                      |

| NRD_PULSE    | t <sub>sa</sub> | Access time of subsequent accesses in the page |

| NRD_CYCLE    | 'x'             | No impact                                      |

Table 26-8. Programming of Read Timings in Page Mode

The SMC does not check the coherency of timings. It will always apply the NCS\_RD\_PULSE timings as page access timing ( $t_{pa}$ ) and the NRD\_PULSE for accesses to the page ( $t_{sa}$ ), even if the programmed value for  $t_{pa}$  is shorter than the programmed value for  $t_{sa}$ .

## 26.15.2 Page Mode Restriction

The Page mode is not compatible with the use of the NWAIT signal. Using the Page mode and the NWAIT signal may lead to unpredictable behavior.

#### 26.15.3 Sequential and Non-sequential Accesses

If the chip select and the MSB of addresses as defined in Table 26-7 are identical, then the current access lies in the same page as the previous one, and no page break occurs.

Using this information, all data within the same page, sequential or not sequential, are accessed with a minimum access time ( $t_{sa}$ ). Figure 26-32 illustrates access to an 8-bit memory device in Page mode, with 8-byte pages. Access to D1 causes a page access with a long access time ( $t_{pa}$ ). Accesses to D3 and D7, though they are not sequential accesses, only require a short access time ( $t_{sa}$ ).

If the MSB of addresses are different, the SMC performs the access of a new page. In the same way, if the chip select is different from the previous access, a page break occurs. If two sequential accesses are made to the Page mode memory, but separated by an other internal or external peripheral access, a page break occurs on the second access because the chip select of the device was deasserted between both accesses.

Once all of the previous steps have been completed, the peripheral clocks can be enabled and/or disabled via registers PMC\_PCER0, PMC\_PCER, PMC\_PCDR0 and PMC\_PCDR.

## 31.6.25 PIO Peripheral ABCD Select Register 2

Access: Read/Write

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

| P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

| P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

This register can only be written if the WPEN bit is cleared in the PIO Write Protection Mode Register.

## • P0–P31: Peripheral Select

If the same bit is set to 0 in PIO\_ABCDSR1:

0: Assigns the I/O line to the Peripheral A function.

1: Assigns the I/O line to the Peripheral C function.

If the same bit is set to 1 in PIO\_ABCDSR1:

- 0: Assigns the I/O line to the Peripheral B function.

- 1: Assigns the I/O line to the Peripheral D function.

## 34.8.2 TWI Master Mode Register

| Name:<br>Address: | TWI_MMR<br>0x40018004 (0), | 0×40010004 (   | 1) |    |    |    |    |

|-------------------|----------------------------|----------------|----|----|----|----|----|

|                   |                            | , 0,40010004 ( | 1) |    |    |    |    |

| Access:           | Read/Write                 |                |    |    |    |    |    |

| 31                | 30                         | 29             | 28 | 27 | 26 | 25 | 24 |

| -                 | -                          | -              | -  | -  | -  | -  | -  |

|                   | -                          | -              |    | -  |    | -  |    |

| 23                | 22                         | 21             | 20 | 19 | 18 | 17 | 16 |

| -                 | DADR                       |                |    |    |    |    |    |

|                   | -                          |                |    |    |    |    |    |

| 15                | 14                         | 13             | 12 | 11 | 10 | 9  | 8  |

| -                 | – – MREAD – – IADRSZ       |                |    |    |    |    |    |

|                   |                            |                |    |    |    |    |    |

| 7                 | 6                          | 5              | 4  | 3  | 2  | 1  | 0  |

| _                 | _                          | _              | _  | _  | _  | _  | _  |

# • IADRSZ: Internal Device Address Size

| Value | Name   | escription                         |  |  |

|-------|--------|------------------------------------|--|--|

| 0     | NONE   | No internal device address         |  |  |

| 1     | 1_BYTE | One-byte internal device address   |  |  |

| 2     | 2_BYTE | Two-byte internal device address   |  |  |

| 3     | 3_BYTE | Three-byte internal device address |  |  |

# MREAD: Master Read Direction

0: Master write direction.

1: Master read direction.

## • DADR: Device Address

The device address is used to access slave devices in Read or Write mode. These bits are only used in Master mode.

## • Receive data

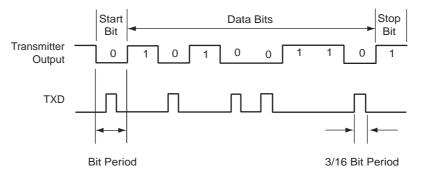

#### 36.6.5.1 IrDA Modulation

For baud rates up to and including 115.2 kbit/s, the RZI modulation scheme is used. "0" is represented by a light pulse of 3/16th of a bit time. Some examples of signal pulse duration are shown in Table 36-11.

| Baud Rate    | Pulse Duration (3/16) |

|--------------|-----------------------|

| 2.4 kbit/s   | 78.13 µs              |

| 9.6 kbit/s   | 19.53 µs              |

| 19.2 kbit/s  | 9.77 µs               |

| 38.4 kbit/s  | 4.88 µs               |

| 57.6 kbit/s  | 3.26 µs               |

| 115.2 kbit/s | 1.63 µs               |

Figure 36-33 shows an example of character transmission.

#### Figure 36-33. IrDA Modulation

#### 36.6.5.2 IrDA Baud Rate

Table 36-12 gives some examples of CD values, baud rate error and pulse duration. Note that the requirement on the maximum acceptable error of  $\pm 1.87\%$  must be met.

| Peripheral Clock | Baud Rate (bit/s) | CD | Baud Rate Error | Pulse Time (µs) |

|------------------|-------------------|----|-----------------|-----------------|

| 3,686,400        | 115,200           | 2  | 0.00%           | 1.63            |

| 20,000,000       | 115,200           | 11 | 1.38%           | 1.63            |

| 32,768,000       | 115,200           | 18 | 1.25%           | 1.63            |

| 40,000,000       | 115,200           | 22 | 1.38%           | 1.63            |

| 3,686,400        | 57,600            | 4  | 0.00%           | 3.26            |

| 20,000,000       | 57,600            | 22 | 1.38%           | 3.26            |

| 32,768,000       | 57,600            | 36 | 1.25%           | 3.26            |

| 40,000,000       | 57,600            | 43 | 0.93%           | 3.26            |

| 3,686,400        | 38,400            | 6  | 0.00%           | 4.88            |

| 20,000,000       | 38,400            | 33 | 1.38%           | 4.88            |

| 32,768,000       | 38,400            | 53 | 0.63%           | 4.88            |

| 40,000,000       | 38,400            | 65 | 0.16%           | 4.88            |

Table 36-12.

IrDA Baud Rate Error

#### 36.6.10 Register Write Protection

To prevent any single software error from corrupting USART behavior, certain registers in the address space can be write-protected by setting the WPEN bit in the USART Write Protection Mode Register (US\_WPMR).

If a write access to a write-protected register is detected, the WPVS flag in the USART Write Protection Status Register (US\_WPSR) is set and the field WPVSRC indicates the register in which the write access has been attempted.

The WPVS bit is automatically cleared after reading the US\_WPSR.

The following registers can be write-protected:

- USART Mode Register

- USART Baud Rate Generator Register

- USART Receiver Time-out Register

- USART Transmitter Timeguard Register

- USART FI DI RATIO Register

- USART IrDA Filter Register

- USART Manchester Configuration Register

# • ETRGS: External Trigger

0: No effect.

1: Enables the External Trigger Interrupt.

| 38.14.7 HSI | MCI Block Register |    |     |     |    |    |    |  |  |

|-------------|--------------------|----|-----|-----|----|----|----|--|--|

| Name:       | HSMCI_BLKR         |    |     |     |    |    |    |  |  |

| Address:    | 0x40000018         |    |     |     |    |    |    |  |  |

| Access:     | Read/Write         |    |     |     |    |    |    |  |  |

| 31          | 30                 | 29 | 28  | 27  | 26 | 25 | 24 |  |  |

|             |                    |    | BLK | LEN |    |    |    |  |  |

| 23          | 22                 | 21 | 20  | 19  | 18 | 17 | 16 |  |  |

|             |                    |    | BLK | LEN |    |    |    |  |  |

| 15          | 14                 | 13 | 12  | 11  | 10 | 9  | 8  |  |  |

|             | BCNT               |    |     |     |    |    |    |  |  |

| 7           | 6                  | 5  | 4   | 3   | 2  | 1  | 0  |  |  |

|             |                    |    | BC  | NT  |    |    |    |  |  |

|             |                    |    |     |     |    |    |    |  |  |

## • BCNT: MMC/SDIO Block Count - SDIO Byte Count

This field determines the number of data byte(s) or block(s) to transfer.

The transfer data type and the authorized values for BCNT field are determined by the TRTYP field in the HSMCI Command Register (HSMCI\_CMDR).

When TRTYP = 1 (MMC/SDCARD Multiple Block), BCNT can be programmed from 1 to 65535, 0 corresponds to an infinite block transfer.

When TRTYP = 4 (SDIO Byte), BCNT can be programmed from 1 to 511, 0 corresponds to 512-byte transfer. Values in range 512 to 65536 are forbidden.

When TRTYP = 5 (SDIO Block), BCNT can be programmed from 1 to 511, 0 corresponds to an infinite block transfer. Values in range 512 to 65536 are forbidden.

<u>Warning</u>: In SDIO Byte and Block modes (TRTYP = 4 or 5), writing the 7 last bits of BCNT field with a value which differs from 0 is forbidden and may lead to unpredictable results.

## BLKLEN: Data Block Length

20 44 7 LICMCI Disale Deviator

This field determines the size of the data block.

Bits 16 and 17 must be configured to 0 if FBYTE is disabled.

Note: In SDIO Byte mode, BLKLEN field is not used.

## 40.7.2 UDP Global State Register

| Name:<br>Address: | UDP_GLB_STA<br>0x40034004 | Т  |        |         |     |       |        |

|-------------------|---------------------------|----|--------|---------|-----|-------|--------|

| Access:           | Read/Write                |    |        |         |     |       |        |

| 31                | 30                        | 29 | 28     | 27      | 26  | 25    | 24     |

| _                 | -                         | _  | _      | _       | _   | _     | _      |

| 23                | 22                        | 21 | 20     | 19      | 18  | 17    | 16     |

| 15                | 14                        | 13 | 12     | 11      | 10  | 9     | 8      |

|                   |                           |    |        | _       | _   | _     | _      |

| 7                 | 6                         | 5  | 4      | 3       | 2   | 1     | 0      |

| —                 | -                         | —  | RMWUPE | RSMINPR | ESR | CONFG | FADDEN |

This register is used to get and set the device state as specified in Chapter 9 of the USB Serial Bus Specification, Rev.2.0.

## • FADDEN: Function Address Enable

Read:

- 0: Device is not in address state

- 1: Device is in address state

Write:

- 0: No effect, only a reset can bring back a device to the default state.

- 1: Sets device in address state. This occurs after a successful Set Address request. Beforehand, the UDP\_FADDR register must have been initialized with Set Address parameters. Set Address must complete the Status Stage before setting FAD-DEN. Refer to chapter 9 of the *Universal Serial Bus Specification, Rev. 2.0* for more details.

## • CONFG: Configured

Read:

- 0: Device is not in configured state

- 1: Device is in configured state

Write:

- 0: Sets device in a non configured state

- 1: Sets device in configured state

The device is set in configured state when it is in address state and receives a successful Set Configuration request. Refer to Chapter 9 of the *Universal Serial Bus Specification, Rev. 2.0* for more details.

## • ESR: Enable Send Resume

- 0: Mandatory value prior to starting any Remote Wakeup procedure

- 1: Starts the Remote Wakeup procedure if this bit value was 0 and if RMWUPE is enabled

## • RMWUPE: Remote Wakeup Enable

- 0: The Remote Wakeup feature of the device is disabled.

- 1: The Remote Wakeup feature of the device is enabled.

## • WAKEUP: USB Bus Wakeup Interrupt

0: USB Bus Wakeup Interrupt is disabled

1: USB Bus Wakeup Interrupt is enabled

Note: When the USB block is in suspend mode, the application may power down the USB logic. In this case, any USB HOST resume request that is made must be taken into account and, thus, the reset value of the RXRSM bit of the register UDP\_IMR is enabled.

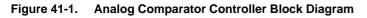

# 41. Analog Comparator Controller (ACC)

# 41.1 Description

The Analog Comparator Controller (ACC) configures the analog comparator and generates an interrupt depending on user settings. The analog comparator embeds two 8-to-1 multiplexers that generate two internal inputs. These inputs are compared, resulting in a compare output. The hysteresis level, edge detection and polarity are configurable.

The ACC also generates a compare event which can be used by the Pulse Width Modulator (PWM).

# 41.2 Embedded Characteristics

- Eight User Analog Inputs Selectable for Comparison

- Four Voltage References Selectable for Comparison: Temperature Sensor (TS), ADVREF, DAC0 and DAC1

- Interrupt Generation

- Compare Event Fault Generation for PWM

# 41.3 Block Diagram

Note: 1. Refer to Table 41-1 for the list of external analog data inputs.

## 41.7.2 ACC Mode Register

| Name:    | ACC_MR     |         |     |    |              |          |    |

|----------|------------|---------|-----|----|--------------|----------|----|

| Address: | 0x40040004 |         |     |    |              |          |    |

| Access:  | Read/Write |         |     |    |              |          |    |

| 31       | 30         | 29      | 28  | 27 | 26           | 25       | 24 |

| —        | -          | -       | -   | _  | —            | -        | -  |

| 23       | 22         | 21      | 20  | 19 | 18           | 17       | 16 |

| _        | —          | _       | _   | _  | _            | _        | -  |

| 15       | 14         | 13      | 12  | 11 | 10           | 9        | 8  |

| _        | FE         | SELFS   | INV | _  | EDGETYP ACEN |          |    |

| 7        | 6          | 5       | 4   | 3  | 2            | 1        | 0  |

| _        |            | SELPLUS |     | -  |              | SELMINUS |    |

This register can only be written if the WPEN bit is cleared in the ACC Write Protection Mode Register.

## • SELMINUS: Selection for Minus Comparator Input

| 07: Selects the input t | o apply on analog | comparator SELMINUS | comparison input. |

|-------------------------|-------------------|---------------------|-------------------|

|                         |                   |                     |                   |

| Value | Name   | Description   |

|-------|--------|---------------|

| 0     | TS     | Select TS     |

| 1     | ADVREF | Select ADVREF |

| 2     | DAC0   | Select DAC0   |

| 3     | DAC1   | Select DAC1   |

| 4     | AD0    | Select AD0    |

| 5     | AD1    | Select AD1    |

| 6     | AD2    | Select AD2    |

| 7     | AD3    | Select AD3    |

## • SELPLUS: Selection For Plus Comparator Input

0..7: Selects the input to apply on analog comparator SELPLUS comparison input.

| Value | Name | Description |

|-------|------|-------------|

| 0     | AD0  | Select AD0  |

| 1     | AD1  | Select AD1  |

| 2     | AD2  | Select AD2  |

| 3     | AD3  | Select AD3  |

| 4     | AD4  | Select AD4  |

| 5     | AD5  | Select AD5  |

| 6     | AD6  | Select AD6  |

| 7     | AD7  | Select AD7  |

# • ACEN: Analog Comparator Enable

0 (DIS): Analog comparator disabled.

1 (EN): Analog comparator enabled.

# 41.7.9 ACC Write Protection Status Register

| Name:    | ACC_WPSR   |    |    |    |    |    |      |

|----------|------------|----|----|----|----|----|------|

| Address: | 0x400400E8 |    |    |    |    |    |      |

| Access:  | Read-only  |    |    |    |    |    |      |

| 31       | 30         | 29 | 28 | 27 | 26 | 25 | 24   |

| —        | -          | _  | -  | -  | -  | —  | -    |

| 23       | 22         | 21 | 20 | 19 | 18 | 17 | 16   |

| —        | -          | —  | -  | —  | -  | -  | -    |

| 15       | 14         | 13 | 12 | 11 | 10 | 9  | 8    |

| —        | -          | —  | -  | —  | -  | -  | -    |

| 7        | 6          | 5  | 4  | 3  | 2  | 1  | 0    |

| _        | -          | -  | -  | -  | -  | —  | WPVS |

# • WPVS: Write Protection Violation Status

0: No write protection violation has occurred since the last read of ACC\_WPSR.

1: A write protection violation (WPEN = 1) has occurred since the last read of ACC\_WPSR.