#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                            |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 120MHz                                                                     |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, Memory Card, SPI, SSC, UART/USART, USB    |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                 |

| Number of I/O              | 79                                                                         |

| Program Memory Size        | 1MB (1M x 8)                                                               |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 160K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                               |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 100-TFBGA                                                                  |

| Supplier Device Package    | 100-TFBGA (9x9)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4sd16cb-cnr |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 12.6.7 Saturating Instructions

The table below shows the saturating instructions.

| Mnemonic | Description                                        |  |

|----------|----------------------------------------------------|--|

| SSAT     | Signed Saturate                                    |  |

| SSAT16   | Signed Saturate Halfword                           |  |

| USAT     | Unsigned Saturate                                  |  |

| USAT16   | Unsigned Saturate Halfword                         |  |

| QADD     | Saturating Add                                     |  |

| QSUB     | Saturating Subtract                                |  |

| QSUB16   | Saturating Subtract 16                             |  |

| QASX     | Saturating Add and Subtract with Exchange          |  |

| QSAX     | Saturating Subtract and Add with Exchange          |  |

| QDADD    | Saturating Double and Add                          |  |

| QDSUB    | Saturating Double and Subtract                     |  |

| UQADD16  | Unsigned Saturating Add 16                         |  |

| UQADD8   | Unsigned Saturating Add 8                          |  |

| UQASX    | Unsigned Saturating Add and Subtract with Exchange |  |

| UQSAX    | Unsigned Saturating Subtract and Add with Exchange |  |

| UQSUB16  | Unsigned Saturating Subtract 16                    |  |

| UQSUB8   | Unsigned Saturating Subtract 8                     |  |

Table 12-22. Saturating Instructions

For signed *n*-bit saturation, this means that:

- If the value to be saturated is less than  $-2^{n-1}$ , the result returned is  $-2^{n-1}$

- If the value to be saturated is greater than  $2^{n-1}$ -1, the result returned is  $2^{n-1}$ -1

- Otherwise, the result returned is the same as the value to be saturated.

For unsigned *n*-bit saturation, this means that:

- If the value to be saturated is less than 0, the result returned is 0

- If the value to be saturated is greater than  $2^{n}$ -1, the result returned is  $2^{n}$ -1

- Otherwise, the result returned is the same as the value to be saturated.

If the returned result is different from the value to be saturated, it is called *saturation*. If saturation occurs, the instruction sets the Q flag to 1 in the APSR. Otherwise, it leaves the Q flag unchanged. To clear the Q flag to 0, the MSR instruction must be used; see "MSR".

To read the state of the Q flag, the MRS instruction must be used; see "MRS" .

#### Examples

| QADD16 | R7, R4, R2 | ; Adds halfwords of R4 with corresponding halfword of |

|--------|------------|-------------------------------------------------------|

|        |            | ; R2, saturates to 16 bits and writes to              |

|        |            | ; corresponding halfword of R7                        |

| QADD8  | R3, R1, R6 | ; Adds bytes of R1 to the corresponding bytes of R6,  |

|        |            | ; saturates to 8 bits and writes to corresponding     |

|        |            | ; byte of R3                                          |

| QSUB16 | R4, R2, R3 | ; Subtracts halfwords of R3 from corresponding        |

|        |            | ; halfword of R2, saturates to 16 bits, writes to     |

|        |            | ; corresponding halfword of R4                        |

| QSUB8  | R4, R2, R5 | ; Subtracts bytes of R5 from the corresponding byte   |

|        |            | ; in R2, saturates to 8 bits, writes to corresponding |

|        |            | ; byte of R4.                                         |

#### 12.6.7.4 QASX and QSAX

Saturating Add and Subtract with Exchange and Saturating Subtract and Add with Exchange, signed.

Syntax

$op\{cond\}$  {Rd}, Rm, Rn

where:

| ор     | is one of:                                                  |

|--------|-------------------------------------------------------------|

|        | QASX Add and Subtract with Exchange and Saturate.           |

|        | QSAX Subtract and Add with Exchange and Saturate.           |

| cond   | is an optional condition code, see "Conditional Execution". |

| Rd     | is the destination register.                                |

| Rn, Rm | are registers holding the first and second operands.        |

#### Operation

The QASX instruction:

- 1. Adds the top halfword of the source operand with the bottom halfword of the second operand.

- 2. Subtracts the top halfword of the second operand from the bottom highword of the first operand.

- 3. Saturates the result of the subtraction and writes a 16-bit signed integer in the range  $-2^{15} \le x \le 2^{15} 1$ , where *x* equals 16, to the bottom halfword of the destination register.

- 4. Saturates the results of the sum and writes a 16-bit signed integer in the range  $-2^{15} \le x \le 2^{15} 1$ , where *x* equals 16, to the top halfword of the destination register.

#### The QSAX instruction:

- 1. Subtracts the bottom halfword of the second operand from the top highword of the first operand.

- 2. Adds the bottom halfword of the source operand with the top halfword of the second operand.

- 3. Saturates the results of the sum and writes a 16-bit signed integer in the range  $-2^{15} \le x \le 2^{15} 1$ , where *x* equals 16, to the bottom halfword of the destination register.

- 4. Saturates the result of the subtraction and writes a 16-bit signed integer in the range  $-2^{15} \le x \le 2^{15} 1$ , where *x* equals 16, to the top halfword of the destination register.

#### Restrictions

Do not use SP and do not use PC.

#### **Condition Flags**

These instructions do not affect the condition code flags.

| 12.11.2.3 | MPU Region Number Register |    |    |    |    |    |    |

|-----------|----------------------------|----|----|----|----|----|----|

| Name:     | MPU_RNR                    |    |    |    |    |    |    |

| Access:   | Read/Write                 |    |    |    |    |    |    |

| 31        | 30                         | 29 | 28 | 27 | 26 | 25 | 24 |

| _         | _                          | _  | —  | —  | —  | —  | —  |

| 23        | 22                         | 21 | 20 | 19 | 18 | 17 | 16 |

| _         | _                          | _  | —  | —  | —  | —  | —  |

| 15        | 15 14 13 12 11 10 9 8      |    |    |    |    |    |    |

| -         | -                          | -  | _  | -  | -  | -  | -  |

| 7         | 6                          | 5  | 4  | 3  | 2  | 1  | 0  |

|           | REGION                     |    |    |    |    |    |    |

The MPU\_RNR selects which memory region is referenced by the MPU\_RBAR and MPU\_RASRs.

# • REGION: MPU Region Referenced by the MPU\_RBAR and MPU\_RASRs

Indicates the MPU region referenced by the MPU\_RBAR and MPU\_RASRs.

The MPU supports 8 memory regions, so the permitted values of this field are 0–7.

Normally, the required region number is written to this register before accessing the MPU\_RBAR or MPU\_RASR. However, the region number can be changed by writing to the MPU\_RBAR with the VALID bit set to 1; see "MPU Region Base Address Register". This write updates the value of the REGION field.

# • FARG: Flash Command Argument

| GETD, GLB,<br>GGPB, STUI,<br>SPUI, GCALB,<br>WUS, EUS, STUS,<br>SPUS, EA | Commands<br>requiring no<br>argument, including<br>Erase all command | FARG is meaningless, must be written with 0                                                 |  |

|--------------------------------------------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--|

| ES                                                                       | Erase sector<br>command                                              | FARG must be written with any page number within the sector to be erased                    |  |

|                                                                          |                                                                      | FARG[1:0] defines the number of pages to be erased                                          |  |

|                                                                          |                                                                      | The start page must be written in FARG[15:2].                                               |  |

|                                                                          |                                                                      | FARG[1:0] = 0: Four pages to be erased. FARG[15:2] = Page_Number / 4                        |  |

|                                                                          | Erase pages                                                          | FARG[1:0] = 1: Eight pages to be erased. FARG[15:3] = Page_Number / 8, FARG[2]=0            |  |

| EPA command                                                              |                                                                      | FARG[1:0] = 2: Sixteen pages to be erased. FARG[15:4] = Page_Number / 16,<br>FARG[3:2]=0    |  |

|                                                                          |                                                                      | FARG[1:0] = 3: Thirty-two pages to be erased. FARG[15:5] = Page_Number / 32,<br>FARG[4:2]=0 |  |

|                                                                          |                                                                      | Refer to Table 20-4 "EEFC_FCR.FARG Field for EPA Command".                                  |  |

| WP, WPL, EWP,<br>EWPL                                                    | Programming commands                                                 | FARG must be written with the page number to be programmed                                  |  |

| SLB, CLB                                                                 | Lock bit commands                                                    | FARG defines the page number to be locked or unlocked                                       |  |

| SGPB, CGPB                                                               | GPNVM commands                                                       | FARG defines the GPNVM number to be programmed                                              |  |

# • FKEY: Flash Writing Protection Key

| Value | Name   | Description                                                                                                                                                                  |  |

|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0x5A  | PASSWD | The 0x5A value enables the command defined by the bits of the register. If the field is written with a different value, the write is not performed and no action is started. |  |

#### 21.3.5.5 Flash General-purpose NVM Commands

General-purpose NVM bits (GP NVM bits) can be set using the **Set GPNVM** command **(SGPB)**. This command also activates GP NVM bits. A bit mask is provided as argument to the command. When bit 0 of the bit mask is set, then the first GP NVM bit is activated.

In the same way, the **Clear GPNVM** command **(CGPB)** is used to clear general-purpose NVM bits. The generalpurpose NVM bit is deactivated when the corresponding bit in the pattern value is set to 1.

| Table 21-11. Set/Clear GP NVM Command |

|---------------------------------------|

|---------------------------------------|

| Step | Handshake Sequence | MODE[3:0] | DATA[15:0]               |

|------|--------------------|-----------|--------------------------|

| 1    | Write handshaking  | CMDE      | SGPB or CGPB             |

| 2    | Write handshaking  | DATA      | GP NVM bit pattern value |

General-purpose NVM bits can be read using the **Get GPNVM Bit** command **(GGPB)**. The n<sup>th</sup> GP NVM bit is active when bit n of the bit mask is set.

Table 21-12.

Get GP NVM Bit Command

| Step | Handshake Sequence | MODE[3:0] | DATA[15:0]                |

|------|--------------------|-----------|---------------------------|

| 1    | Write handshaking  | CMDE      | GGPB                      |

|      |                    |           | GP NVM Bit Mask Status    |

| 2    | Read handshaking   | DATA      | 0 = GP NVM bit is cleared |

|      |                    |           | 1 = GP NVM bit is set     |

#### 21.3.5.6 Flash Security Bit Command

A security bit can be set using the **Set Security Bit** command (SSE). Once the security bit is active, the Fast Flash programming is disabled. No other command can be run. An event on the Erase pin can erase the security bit once the contents of the Flash have been erased.

| Table 21-13. | Set Security Bit Command |

|--------------|--------------------------|

|--------------|--------------------------|

| Step | Handshake Sequence | MODE[3:0] | DATA[15:0] |

|------|--------------------|-----------|------------|

| 1    | Write handshaking  | CMDE      | SSE        |

| 2    | Write handshaking  | DATA      | 0          |

Once the security bit is set, it is not possible to access FFPI. The only way to erase the security bit is to erase the Flash.

In order to erase the Flash, the user must perform the following:

- 1. Power-off the chip.

- 2. Power-on the chip with TST = 0.

- 3. Assert Erase during a period of more than 220 ms.

- 4. Power-off the chip.

Then it is possible to return to FFPI mode and check that Flash is erased.

#### 21.3.5.7 Memory Write Command

This command is used to perform a write access to any memory location.

# 23. Cyclic Redundancy Check Calculation Unit (CRCCU)

# 23.1 Description

The Cyclic Redundancy Check Calculation Unit (CRCCU) has its own DMA which functions as a Master with the Bus Matrix. Three different polynomials are available: CCITT802.3, CASTAGNOLI and CCITT16.

The CRCCU is designed to perform data integrity checks of off-/on-chip memories as a background task without CPU intervention.

# 23.2 Embedded Characteristics

- Data Integrity Check of Off-/On-Chip Memories

- Background Task Without CPU Intervention

- Performs Cyclic Redundancy Check (CRC) Operation on Programmable Memory Area

- Programmable Bus Burden

- Note: The CRCCU is designed to verify data integrity of off-/on-chip memories, thus the CRC must be generated and verified by the CRCCU. The CRCCU performs the CRC from LSB to MSB. If the CRC has been performed with the same polynomial by another device, a bit-reverse must be done on each byte before using the CRCCU.

# 23.6.2 Transfer Control Register

| Name:   | TR_CTRL    |    |     |      |    |     |       |

|---------|------------|----|-----|------|----|-----|-------|

| Access: | Read/Write |    |     |      |    |     |       |

| 31      | 30         | 29 | 28  | 27   | 26 | 25  | 24    |

| _       | -          | _  | -   | IEN  | -  | TRW | /IDTH |

| 23      | 22         | 21 | 20  | 19   | 18 | 17  | 16    |

| _       | -          | _  | -   | _    | -  | _   | -     |

| 15      | 14         | 13 | 12  | 11   | 10 | 9   | 8     |

|         | BTSIZE     |    |     |      |    |     |       |

| 7       | 6          | 5  | 4   | 3    | 2  | 1   | 0     |

|         |            |    | BTS | SIZE |    |     |       |

#### • BTSIZE: Buffer Transfer Size

#### • TRWIDTH: Transfer Width Register

| Value | Name     | Description             |

|-------|----------|-------------------------|

| 0     | BYTE     | The data size is 8-bit  |

| 1     | HALFWORD | The data size is 16-bit |

| 2     | WORD     | The data size is 32-bit |

# • IEN: Context Done Interrupt Enable (Active Low)

0: Bit DMAISR of CRCCU\_DMA\_ISR is set at the end of the current descriptor transfer.

1: Bit DMAISR of CRCCU\_DMA\_ISR remains cleared.

#### 26.11.3.2 Slow Clock Mode Transition

A Reload Configuration Wait State is also inserted when the Slow Clock mode is entered or exited, after the end of the current transfer (see Section 26.14 "Slow Clock Mode").

#### 26.11.4 Read to Write Wait State

Due to an internal mechanism, a wait cycle is always inserted between consecutive read and write SMC accesses.

This wait cycle is referred to as a read to write wait state in this document.

This wait cycle is applied in addition to chip select and reload user configuration wait states when they are to be inserted. See Figure 26-13 on page 460.

# 27.6.8 Transmit Next Counter Register

| Name:   | PERIPH_TNCR |    |     |     |    |    |    |

|---------|-------------|----|-----|-----|----|----|----|

| Access: | Read/Write  |    |     |     |    |    |    |

| 31      | 30          | 29 | 28  | 27  | 26 | 25 | 24 |

| _       | -           | _  | -   | _   | -  | _  | -  |

| 23      | 22          | 21 | 20  | 19  | 18 | 17 | 16 |

| _       | -           | _  | -   | _   | -  | —  | -  |

| 15      | 14          | 13 | 12  | 11  | 10 | 9  | 8  |

|         |             |    | TXN | CTR |    |    |    |

| 7       | 6           | 5  | 4   | 3   | 2  | 1  | 0  |

|         |             |    | TXN | CTR |    |    |    |

# • TXNCTR: Transmit Counter Next

TXNCTR contains the next transmit buffer size.

When a half-duplex peripheral is connected to the PDC, RXNCTR = TXNCTR.

Atmel

# 31.5 Functional Description

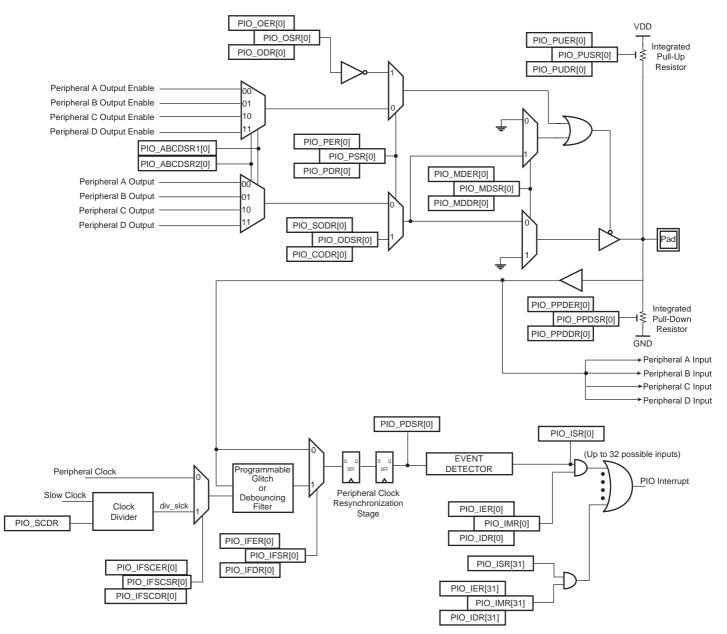

The PIO Controller features up to 32 fully-programmable I/O lines. Most of the control logic associated to each I/O is represented in Figure 31-2. In this description each signal shown represents one of up to 32 possible indexes.

#### Figure 31-2. I/O Line Control Logic

#### 31.5.1 Pull-up and Pull-down Resistor Control

Each I/O line is designed with an embedded pull-up resistor and an embedded pull-down resistor. The pull-up resistor can be enabled or disabled by writing to the Pull-up Enable Register (PIO\_PUER) or Pull-up Disable Register (PIO\_PUDR), respectively. Writing to these registers results in setting or clearing the corresponding bit in the Pull-up Status Register (PIO\_PUSR). Reading a one in PIO\_PUSR means the pull-up is disabled and reading a zero means the pull-up is enabled. The pull-down resistor can be enabled or disabled by writing the Pull-down Enable Register (PIO\_PPDER) or the Pull-down Disable Register (PIO\_PPDDR), respectively. Writing in these

# Atmel

# 31.6.5 PIO Output Disable Register

| Name:    | PIO_ODR       |                |                 |              |     |     |     |

|----------|---------------|----------------|-----------------|--------------|-----|-----|-----|

| Address: | 0x400E0E14 (P | IOA), 0x400E10 | 014 (PIOB), 0x4 | 00E1214 (PIO | C)  |     |     |

| Access:  | Write-only    |                |                 |              |     |     |     |

| 31       | 30            | 29             | 28              | 27           | 26  | 25  | 24  |

| P31      | P30           | P29            | P28             | P27          | P26 | P25 | P24 |

| 23       | 22            | 21             | 20              | 19           | 18  | 17  | 16  |

| P23      | P22           | P21            | P20             | P19          | P18 | P17 | P16 |

| 15       | 14            | 13             | 12              | 11           | 10  | 9   | 8   |

| P15      | P14           | P13            | P12             | P11          | P10 | P9  | P8  |

| 7        | 6             | 5              | 4               | 3            | 2   | 1   | 0   |

| P7       | P6            | P5             | P4              | P3           | P2  | P1  | P0  |

This register can only be written if the WPEN bit is cleared in the PIO Write Protection Mode Register.

#### • P0–P31: Output Disable

0: No effect.

1: Disables the output on the I/O line.

# 31.6.27 PIO Input Filter Slow Clock Enable Register

PIO\_IFSCER

| Address:<br>Access: | 0x400E0E84 (PI<br>Write-only | OA), 0x400E10 | 084 (PIOB), 0x4 | 100E1284 (PIO | C)  |     |     |

|---------------------|------------------------------|---------------|-----------------|---------------|-----|-----|-----|

| 31                  | 30                           | 29            | 28              | 27            | 26  | 25  | 24  |

| P31                 | P30                          | P29           | P28             | P27           | P26 | P25 | P24 |

| 23                  | 22                           | 21            | 20              | 19            | 18  | 17  | 16  |

| P23                 | P22                          | P21           | P20             | P19           | P18 | P17 | P16 |

| 15                  | 14                           | 13            | 12              | 11            | 10  | 9   | 8   |

| P15                 | P14                          | P13           | P12             | P11           | P10 | P9  | P8  |

| 7                   | 6                            | 5             | 4               | 3             | 2   | 1   | 0   |

| P7                  | P6                           | P5            | P4              | P3            | P2  | P1  | P0  |

# • P0–P31: Slow Clock Debouncing Filtering Select

0: No effect.

Name:

1: The debouncing filter is able to filter pulses with a duration <  $t_{div_{slck}}/2$ .

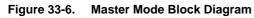

# 33. Serial Peripheral Interface (SPI)

# 33.1 Description

The Serial Peripheral Interface (SPI) circuit is a synchronous serial data link that provides communication with external devices in Master or Slave mode. It also enables communication between processors if an external processor is connected to the system.

The Serial Peripheral Interface is essentially a Shift register that serially transmits data bits to other SPIs. During a data transfer, one SPI system acts as the "master" which controls the data flow, while the other devices act as "slaves" which have data shifted into and out by the master. Different CPUs can take turn being masters (multiple master protocol, contrary to single master protocol where one CPU is always the master while all of the others are always slaves). One master can simultaneously shift data into multiple slaves. However, only one slave can drive its output to write data back to the master at any given time.

A slave device is selected when the master asserts its NSS signal. If multiple slave devices exist, the master generates a separate slave select signal for each slave (NPCS).

The SPI system consists of two data lines and two control lines:

- Master Out Slave In (MOSI)—This data line supplies the output data from the master shifted into the input(s) of the slave(s).

- Master In Slave Out (MISO)—This data line supplies the output data from a slave to the input of the master. There may be no more than one slave transmitting data during any particular transfer.

- Serial Clock (SPCK)—This control line is driven by the master and regulates the flow of the data bits. The master can transmit data at a variety of baud rates; there is one SPCK pulse for each bit that is transmitted.

- Slave Select (NSS)—This control line allows slaves to be turned on and off by hardware.

#### 33.7.3.1 Master Mode Block Diagram

# • ARBLST: Arbitration Lost (cleared on read)

This bit is only used in Master mode.

0: Arbitration won.

1: Arbitration lost. Another master of the TWI bus has won the multi-master arbitration. TXCOMP is set at the same time.

#### • SCLWS: Clock Wait State

This bit is only used in Slave mode.

0: The clock is not stretched.

1: The clock is stretched. TWI\_THR / TWI\_RHR buffer is not filled / emptied before transmission / reception of a new character.

SCLWS behavior can be seen in Figure 34-27 and Figure 34-28.

## • EOSACC: End Of Slave Access (cleared on read)

This bit is only used in Slave mode.

0: A slave access is being performed.

1: The Slave access is finished. End Of Slave Access is automatically set as soon as SVACC is reset. *EOSACC behavior* can be seen in Figure 34-29 and Figure 34-30.

# • ENDRX: End of RX buffer (cleared by writing TWI\_RCR or TWI\_RNCR)

0: The Receive Counter Register has not reached 0 since the last write in TWI\_RCR or TWI\_RNCR.

1: The Receive Counter Register has reached 0 since the last write in TWI\_RCR or TWI\_RNCR.

# • ENDTX: End of TX buffer (cleared by writing TWI\_TCR or TWI\_TNCR)

0: The Transmit Counter Register has not reached 0 since the last write in TWI\_TCR or TWI\_TNCR.

1: The Transmit Counter Register has reached 0 since the last write in TWI\_TCR or TWI\_TNCR.

# • RXBUFF: RX Buffer Full (cleared by writing TWI\_RCR or TWI\_RNCR)

0: TWI\_RCR or TWI\_RNCR have a value other than 0.

1: Both TWI\_RCR and TWI\_RNCR have a value of 0.

# • TXBUFE: TX Buffer Empty (cleared by writing TWI\_TCR or TWI\_TNCR)

0: TWI\_TCR or TWI\_TNCR have a value other than 0.

1: Both TWI\_TCR and TWI\_TNCR have a value of 0.

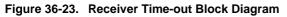

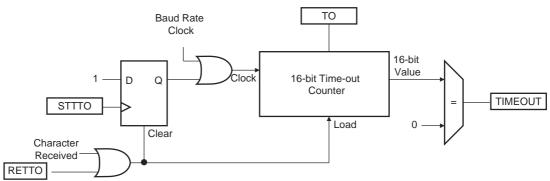

If STTTO is performed, the counter clock is stopped until a first character is received. The idle state on RXD before the start of the frame does not provide a time-out. This prevents having to obtain a periodic interrupt and enables a wait of the end of frame when the idle state on RXD is detected.

If RETTO is performed, the counter starts counting down immediately from the value TO. This enables generation of a periodic interrupt so that a user time-out can be handled, for example when no key is pressed on a keyboard.

Figure 36-23 shows the block diagram of the Receiver Time-out feature.

Table 36-10 gives the maximum time-out period for some standard baud rates.

| Baud Rate (bit/s) | Bit Time (µs) | Time-out (ms) |

|-------------------|---------------|---------------|

| 600               | 1,667         | 109,225       |

| 1,200             | 833           | 54,613        |

| 2,400             | 417           | 27,306        |

| 4,800             | 208           | 13,653        |

| 9,600             | 104           | 6,827         |

| 14,400            | 69            | 4,551         |

| 19,200            | 52            | 3,413         |

| 28,800            | 35            | 2,276         |

| 38,400            | 26            | 1,704         |

| 56,000            | 18            | 1,170         |

| 57,600            | 17            | 1,138         |

| 200,000           | 5             | 328           |

Table 36-10.

Maximum Time-out Period

#### 36.6.3.12 Framing Error

The receiver is capable of detecting framing errors. A framing error happens when the stop bit of a received character is detected at level 0. This can occur if the receiver and the transmitter are fully desynchronized.

A framing error is reported on the FRAME bit of US\_CSR. The FRAME bit is asserted in the middle of the stop bit as soon as the framing error is detected. It is cleared by writing a 1 to the RSTSTA bit in the US\_CR.

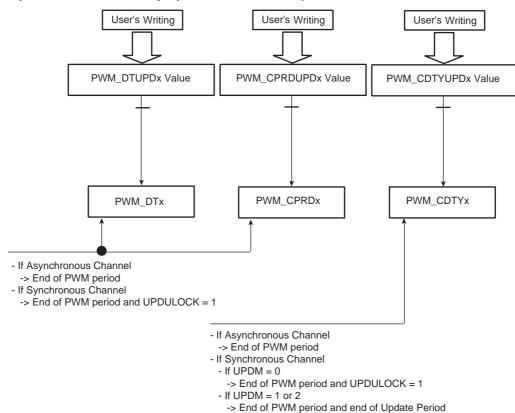

- register PWM\_CDTYUPDx holds the new duty-cycle value until the end of the update period of synchronous channels (when UPRCNT is equal to UPR in PWM Sync Channels Update Period Register (PWM\_SCUP)) and the end of the current PWM period, then updates the value for the next period.

- Note: If the update registers PWM\_CDTYUPDx, PWM\_CPRDUPDx and PWM\_DTUPDx are written several times between two updates, only the last written value is taken into account.

Figure 39-18. Synchronized Period, Duty-Cycle and Dead-Time Update

#### 39.6.5.4 Changing the Update Period of Synchronous Channels

It is possible to change the update period of synchronous channels while they are enabled. See "Method 2: Manual write of duty-cycle values and automatic trigger of the update" and "Method 3: Automatic write of duty-cycle values and automatic trigger of the update".

To prevent an unexpected update of the synchronous channels registers, the user must use the PWM Sync Channels Update Period Update Register (PWM\_SCUPUPD) to change the update period of synchronous channels while they are still enabled. This register holds the new value until the end of the update period of synchronous channels (when UPRCNT is equal to UPR in PWM\_SCUP) and the end of the current PWM period, then updates the value for the next period.

- Note: If the update register PWM\_SCUPUPD is written several times between two updates, only the last written value is taken into account.

- Note: Changing the update period does make sense only if there is one or more synchronous channels and if the update method 1 or 2 is selected (UPDM = 1 or 2 in PWM Sync Channels Mode Register).

| Table 41-1. | List of External Analog Data Inputs |

|-------------|-------------------------------------|

|             | List of External Analog Data inputs |

| Pin Name | Description             |

|----------|-------------------------|

| AD0AD7   | ACC Analog PLUS inputs  |

| AD0AD3   | ACC Analog MINUS inputs |

| ADVREF   | ADCVoltage reference    |

# 41.4 Pin Name List

| Table | 41-2. | ACC | Pin | List |

|-------|-------|-----|-----|------|

|       |       |     |     |      |

| Pin Name   | Description                 | Туре  |

|------------|-----------------------------|-------|

| AD0AD7     | External analog data inputs | Input |

| TS         | On-chip temperature sensor  | Input |

| ADVREF     | ADC voltage reference       | Input |

| DAC0, DAC1 | On-chip DAC inputs          | Input |

#### 41.5 Product Dependencies

#### 41.5.1 I/O Lines

The analog input pins (AD0–AD7 and DAC0–1) are multiplexed with digital functions (PIO) on the IO line. By writing the SELMINUS and SELPLUS fields in the ACC Mode Register (ACC\_MR), the associated IO lines are set to Analog mode.

#### 41.5.2 Power Management

The ACC is clocked through the Power Management Controller (PMC), thus the programmer must first configure the PMC to enable the ACC clock.

Note that the voltage regulator must be activated to use the analog comparator.

#### 41.5.3 Interrupt

The ACC has an interrupt line connected to the Interrupt Controller (IC). In order to handle interrupts, the Interrupt Controller must be programmed before configuring the ACC.

#### Table 41-3. Peripheral IDs

| Instance | ID |

|----------|----|

| ACC      | 33 |

#### 41.5.4 Fault Output

The ACC has the FAULT output connected to the FAULT input of PWM. Please refer to chapter Section 41.6.4 "Fault Mode" and the implementation of the PWM in the product.

Atmel

#### 42.7.11 ADC Interrupt Mask Register

| Name:    | ADC_IMR    |       |        |       |       |       |      |

|----------|------------|-------|--------|-------|-------|-------|------|

| Address: | 0x4003802C |       |        |       |       |       |      |

| Access:  | Read-only  |       |        |       |       |       |      |

| 31       | 30         | 29    | 28     | 27    | 26    | 25    | 24   |

| _        | -          | -     | RXBUFF | ENDRX | COMPE | GOVRE | DRDY |

| 23       | 22         | 21    | 20     | 19    | 18    | 17    | 16   |

| EOCAL    | -          | —     | —      | —     | —     | —     | —    |

| 15       | 14         | 13    | 12     | 11    | 10    | 9     | 8    |

| EOC15    | EOC14      | EOC13 | EOC12  | EOC11 | EOC10 | EOC9  | EOC8 |

| 7        | 6          | 5     | 4      | 3     | 2     | 1     | 0    |

| EOC7     | EOC6       | EOC5  | EOC4   | EOC3  | EOC2  | EOC1  | EOC0 |

The following configuration values are valid for all listed bit names of this register:

0: The corresponding interrupt is disabled.

1: The corresponding interrupt is enabled.

- EOCx: End of Conversion Interrupt Mask x

- EOCAL: End of Calibration Sequence

- DRDY: Data Ready Interrupt Mask

- GOVRE: General Overrun Error Interrupt Mask

- COMPE: Comparison Event Interrupt Mask

- ENDRX: End of Receive Buffer Interrupt Mask

- RXBUFF: Receive Buffer Full Interrupt Mask

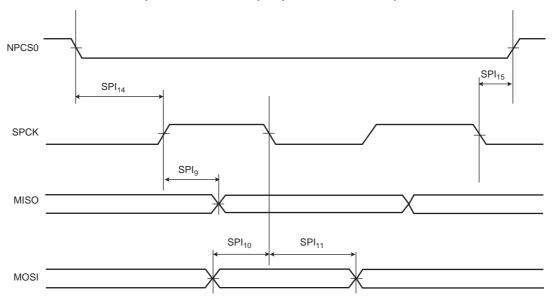

Figure 44-25. SPI Slave Mode with (CPOL = NCPHA = 0) or (CPOL = NCPHA = 1)

#### 44.12.3.1 Maximum SPI Frequency

The following formulas give maximum SPI frequency in master read and write modes and in slave read and write modes.

#### **Master Write Mode**

The SPI only sends data to a slave device such as an LCD, for example. The limit is given by  $SPI_2$  (or  $SPI_5$ ) timing. Since it gives a maximum frequency above the maximum pad speed (see Section 44.12.2 "I/O Characteristics"), the maximum SPI frequency is defined by the pin FreqMax value.

#### **Master Read Mode**

$$f_{SPCK}Max = \frac{1}{SPI_0(orSPI_3) + t_{valid}}$$

$t_{valid}$  is the slave time response to output data after detecting an SPCK edge. For a non-volatile memory with  $t_{valid}$  (or  $t_v$ ) = 12 ns Max,  $f_{SPCK}Max$  = 35.5 MHz @  $V_{DDIO}$  = 3.3V.

#### **Slave Read Mode**

In slave mode, SPCK is the input clock for the SPI. The maximum SPCK frequency is given by setup and hold timings  $SPI_7/SPI_8$  (or  $SPI_{10}/SPI_{11}$ ). Since this gives a frequency well above the pad limit, the limit in slave read mode is given by SPCK pad.

#### **Slave Write Mode**

$$f_{SPCK}Max = \frac{1}{2x(SPI_{6max}(orSPI_{9max}) + t_{su})}$$

1

For 3.3V I/O domain and SPI6,  $f_{SPCK}Max = 25$  MHz.  $t_{su}$  is the setup time from the master before sampling data.