Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                             |

| Core Size                  | 32-Bit Single-Core                                                          |

| Speed                      | 120MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, Memory Card, SPI, SSC, UART/USART, USB     |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                  |

| Number of I/O              | 79                                                                          |

| Program Memory Size        | 2MB (2M x 8)                                                                |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 160K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                                |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                       |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 100-VFBGA                                                                   |

| Supplier Device Package    | 100-VFBGA (7x7)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4sd32ca-cfur |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Table 12-13. Cortex-M4 Instructions (Continued)

| Mnemonic                              | Operands                | Description                                                            | Flags   |

|---------------------------------------|-------------------------|------------------------------------------------------------------------|---------|

| QSUB16                                | {Rd,} Rn, Rm            | Saturating Subtract 16                                                 | -       |

| QSUB8                                 | {Rd,} Rn, Rm            | Saturating Subtract 8                                                  | -       |

| RBIT                                  | Rd, Rn                  | Reverse Bits                                                           | -       |

| REV                                   | Rd, Rn                  | Reverse byte order in a word                                           | -       |

| REV16                                 | Rd, Rn                  | Reverse byte order in each halfword                                    | -       |

| REVSH                                 | Rd, Rn                  | Reverse byte order in bottom halfword and sign extend                  | _       |

| ROR, RORS                             | Rd, Rm, <rs #n></rs #n> | Rotate Right                                                           | N,Z,C   |

| RRX, RRXS                             | Rd, Rm                  | Rotate Right with Extend                                               | N,Z,C   |

| RSB, RSBS                             | {Rd,} Rn, Op2           | Reverse Subtract                                                       | N,Z,C,V |

| SADD16                                | {Rd,} Rn, Rm            | Signed Add 16                                                          | GE      |

| SADD8                                 | {Rd,} Rn, Rm            | Signed Add 8 and Subtract with Exchange                                | GE      |

| SASX                                  | {Rd,} Rn, Rm            | Signed Add                                                             | GE      |

| SBC, SBCS                             | {Rd,} Rn, Op2           | Subtract with Carry                                                    | N,Z,C,V |

| SBFX                                  | Rd, Rn, #lsb, #width    | Signed Bit Field Extract                                               | -       |

| SDIV                                  | {Rd,} Rn, Rm            | Signed Divide                                                          | -       |

| SEL                                   | {Rd,} Rn, Rm            | Select bytes                                                           | -       |

| SEV                                   | -                       | Send Event                                                             | -       |

| SHADD16                               | {Rd,} Rn, Rm            | Signed Halving Add 16                                                  | -       |

| SHADD8                                | {Rd,} Rn, Rm            | Signed Halving Add 8                                                   | -       |

| SHASX                                 | {Rd,} Rn, Rm            | Signed Halving Add and Subtract with Exchange                          | -       |

| SHSAX                                 | {Rd,} Rn, Rm            | Signed Halving Subtract and Add with Exchange                          | -       |

| SHSUB16                               | {Rd,} Rn, Rm            | Signed Halving Subtract 16                                             | -       |

| SHSUB8                                | {Rd,} Rn, Rm            | Signed Halving Subtract 8                                              | -       |

| SMLABB, SMLABT,<br>SMLATB, SMLATT     | Rd, Rn, Rm, Ra          | Signed Multiply Accumulate Long (halfwords)                            | Q       |

| SMLAD, SMLADX                         | Rd, Rn, Rm, Ra          | Signed Multiply Accumulate Dual                                        | Q       |

| SMLAL                                 | RdLo, RdHi, Rn, Rm      | Signed Multiply with Accumulate ( $32 \times 32 + 64$ ), 64-bit result | -       |

| SMLALBB, SMLALBT,<br>SMLALTB, SMLALTT | RdLo, RdHi, Rn, Rm      | Signed Multiply Accumulate Long, halfwords                             | -       |

| SMLALD, SMLALDX                       | RdLo, RdHi, Rn, Rm      | Signed Multiply Accumulate Long Dual                                   | -       |

| SMLAWB, SMLAWT                        | Rd, Rn, Rm, Ra          | Signed Multiply Accumulate, word by halfword                           | Q       |

| SMLSD                                 | Rd, Rn, Rm, Ra          | Signed Multiply Subtract Dual                                          | Q       |

| SMLSLD                                | RdLo, RdHi, Rn, Rm      | Signed Multiply Subtract Long Dual                                     |         |

| SMMLA                                 | Rd, Rn, Rm, Ra          | Signed Most significant word Multiply Accumulate                       | -       |

| SMMLS, SMMLR                          | Rd, Rn, Rm, Ra          | Signed Most significant word Multiply Subtract                         | -       |

| SMMUL, SMMULR                         | {Rd,} Rn, Rm            | Signed Most significant word Multiply                                  | -       |

| SMUAD                                 | {Rd,} Rn, Rm            | Signed dual Multiply Add                                               | Q       |

### 12.6.5.5 CMP and CMN

Compare and Compare Negative.

Syntax

CMP{cond} Rn, Operand2

CMN{cond} Rn, Operand2

where:

cond is an optional condition code, see "Conditional Execution".

Rn is the register holding the first operand.

Operand2 is a flexible second operand. See "Flexible Second Operand" for details of the options.

Operation

These instructions compare the value in a register with *Operand*2. They update the condition flags on the result, but do not write the result to a register.

The CMP instruction subtracts the value of *Operand2* from the value in *Rn*. This is the same as a SUBS instruction, except that the result is discarded.

The CMN instruction adds the value of *Operand2* to the value in *Rn*. This is the same as an ADDS instruction, except that the result is discarded.

Restrictions

In these instructions:

- Do not use PC

- Operand2 must not be SP.

### **Condition Flags**

These instructions update the N, Z, C and V flags according to the result.

Examples

CMP R2, R9 CMN R0, #6400 CMPGT SP, R7, LSL #2

| 12.8.3.6 | Interrupt Priority Registers |    |    |     |    |    |    |  |  |  |

|----------|------------------------------|----|----|-----|----|----|----|--|--|--|

| Name:    | NVIC_IPRx [x=08]             |    |    |     |    |    |    |  |  |  |

| Access:  | Read/Write                   |    |    |     |    |    |    |  |  |  |

| Reset:   | 0x000000000                  |    |    |     |    |    |    |  |  |  |

| 31       | 30                           | 29 | 28 | 27  | 26 | 25 | 24 |  |  |  |

|          | PRI3                         |    |    |     |    |    |    |  |  |  |

| 23       | 22                           | 21 | 20 | 19  | 18 | 17 | 16 |  |  |  |

|          |                              |    | PF | RI2 |    |    |    |  |  |  |

| 15       | 14                           | 13 | 12 | 11  | 10 | 9  | 8  |  |  |  |

|          |                              |    | PF | RI1 |    |    |    |  |  |  |

| 7        | 6                            | 5  | 4  | 3   | 2  | 1  | 0  |  |  |  |

|          |                              |    | PF | RIO |    |    |    |  |  |  |

The NVIC\_IPR0–NVIC\_IPR registers provide a 8-bit priority field for each interrupt. These registers are byte-accessible. Each register holds four priority fields that map up to four elements in the CMSIS interrupt priority array IP[0] to IP[ ].

### • PRI3: Priority (4m+3)

Priority, Byte Offset 3, refers to register bits [31:24].

### • PRI2: Priority (4m+2)

Priority, Byte Offset 2, refers to register bits [23:16].

### • PRI1: Priority (4m+1)

Priority, Byte Offset 1, refers to register bits [15:8].

#### • PRI0: Priority (4m)

Priority, Byte Offset 0, refers to register bits [7:0].

- Notes: 1. Each priority field holds a priority value, 0–15. The lower the value, the greater the priority of the corresponding interrupt. The processor implements only bits[7:4] of each field; bits[3:0] read as zero and ignore writes.

- 2. For more information about the IP[0] to IP[34] interrupt priority array, that provides the software view of the interrupt priorities, see Table 12-29, "CMSIS Functions for NVIC Control".

- 3. The corresponding IPR number *n* is given by n = m DIV 4.

- 4. The byte offset of the required Priority field in this register is *m* MOD 4.

The erase sequence is the following:

- 1. Erase starts as soon as one of the erase commands and the FARG field are written in EEFC\_FCR.

- For the EPA command, the two lowest bits of the FARG field define the number of pages to be erased (FARG[1:0]):

| FARG[1:0] | Number of pages to be erased with EPA command |

|-----------|-----------------------------------------------|

| 0         | 4 pages (only valid for small 8 KB sectors)   |

| 1         | 8 pages                                       |

| 2         | 16 pages                                      |

| 3         | 32 pages (not valid for small 8 KB sectors)   |

#### Table 20-4. EEFC\_FCR.FARG Field for EPA Command

2. When erasing is completed, the bit EEFC\_FSR.FRDY rises. If an interrupt has been enabled by setting the bit EEFC\_FMR.FRDY, the interrupt line of the interrupt controller is activated.

Three errors can be detected in EEFC\_FSR after an erasing sequence:

- Command Error: A bad keyword has been written in EEFC\_FCR.

- Lock Error: At least one page to be erased belongs to a locked region. The erase command has been refused, no page has been erased. A command must be run previously to unlock the corresponding region.

- Flash Error: At the end of the erase period, the EraseVerify test of the Flash memory has failed.

### 20.4.3.4 Lock Bit Protection

Lock bits are associated with several pages in the embedded Flash memory plane. This defines lock regions in the embedded Flash memory plane. They prevent writing/erasing protected pages.

The lock sequence is the following:

- 1. Execute the 'Set Lock Bit' command by writing EEFC\_FCR.FCMD with the SLB command and EEFC\_FCR.FARG with a page number to be protected.

- 2. When the locking completes, the bit EEFC\_FSR.FRDY rises. If an interrupt has been enabled by setting the bit EEFC\_FMR.FRDY, the interrupt line of the interrupt controller is activated.

- 3. The result of the SLB command can be checked running a 'Get Lock Bit' (GLB) command.

- Note: The value of the FARG argument passed together with SLB command must not exceed the higher lock bit index available in the product.

Two errors can be detected in EEFC\_FSR after a programming sequence:

- Command Error: A bad keyword has been written in EEFC\_FCR.

- Flash Error: At the end of the programming, the EraseVerify or WriteVerify test of the Flash memory has failed.

It is possible to clear lock bits previously set. After the lock bits are cleared, the locked region can be erased or programmed. The unlock sequence is the following:

- 1. Execute the 'Clear Lock Bit' command by writing EEFC\_FCR.FCMD with the CLB command and EEFC\_FCR.FARG with a page number to be unprotected.

- 2. When the unlock completes, the bit EEFC\_FSR.FRDY rises. If an interrupt has been enabled by setting the bit EEFC\_FMR.FRDY, the interrupt line of the interrupt controller is activated.

- Note: The value of the FARG argument passed together with CLB command must not exceed the higher lock bit index available in the product.

Two errors can be detected in EEFC\_FSR after a programming sequence:

• Command Error: A bad keyword has been written in EEFC\_FCR.

### 23.7.6 CRCCU DMA Interrupt Disable Register

| Name:    | CRCCU_DMA_IDR |    |    |    |    |    |        |  |  |  |

|----------|---------------|----|----|----|----|----|--------|--|--|--|

| Address: | 0x40044018    |    |    |    |    |    |        |  |  |  |

| Access:  | Write-only    |    |    |    |    |    |        |  |  |  |

| 31       | 30            | 29 | 28 | 27 | 26 | 25 | 24     |  |  |  |

| _        | -             | -  | -  | -  | -  | -  | -      |  |  |  |

| 23       | 22            | 21 | 20 | 19 | 18 | 17 | 16     |  |  |  |

| -        | -             | -  | -  | -  | -  | _  | -      |  |  |  |

| 15       | 14            | 13 | 12 | 11 | 10 | 9  | 8      |  |  |  |

| -        | -             | -  | -  | -  | -  | _  | -      |  |  |  |

| 7        | 6             | 5  | 4  | 3  | 2  | 1  | 0      |  |  |  |

| _        | -             | _  | _  | _  | _  | _  | DMAIDR |  |  |  |

### • DMAIDR: Interrupt Disable

0: No effect

1: Disable interrupt

# 27.5 Functional Description

### 27.5.1 Configuration

The PDC channel user interface enables the user to configure and control data transfers for each channel. The user interface of each PDC channel is integrated into the associated peripheral user interface.

The user interface of a serial peripheral, whether it is full- or half-duplex, contains four 32-bit pointers (RPR, RNPR, TPR, TNPR) and four 16-bit counter registers (RCR, RNCR, TCR, TNCR). However, the transmit and receive parts of each type are programmed differently: the transmit and receive parts of a full-duplex peripheral can be programmed at the same time, whereas only one part (transmit or receive) of a half-duplex peripheral can be programmed at a time.

32-bit pointers define the access location in memory for the current and next transfer, whether it is for read (transmit) or write (receive). 16-bit counters define the size of the current and next transfers. It is possible, at any moment, to read the number of transfers remaining for each channel.

The PDC has dedicated status registers which indicate if the transfer is enabled or disabled for each channel. The status for each channel is located in the associated peripheral status register. Transfers can be enabled and/or disabled by setting TXTEN/TXTDIS and RXTEN/RXTDIS in the peripheral's Transfer Control register.

At the end of a transfer, the PDC channel sends status flags to its associated peripheral. These flags are visible in the peripheral Status register (ENDRX, ENDTX, RXBUFF, and TXBUFE). Refer to Section 27.5.3 and to the associated peripheral user interface.

The peripheral where a PDC transfer is configured must have its peripheral clock enabled. The peripheral clock must be also enabled to access the PDC register set associated to this peripheral.

### 27.5.2 Memory Pointers

Each full-duplex peripheral is connected to the PDC by a receive channel and a transmit channel. Both channels have 32-bit memory pointers that point to a receive area and to a transmit area, respectively, in the target memory.

Each half-duplex peripheral is connected to the PDC by a bidirectional channel. This channel has two 32-bit memory pointers, one for current transfer and the other for next transfer. These pointers point to transmit or receive data depending on the operating mode of the peripheral.

Depending on the type of transfer (byte, half-word or word), the memory pointer is incremented respectively by 1, 2 or 4 bytes.

If a memory pointer address changes in the middle of a transfer, the PDC channel continues operating using the new address.

### 27.5.3 Transfer Counters

Each channel has two 16-bit counters, one for the current transfer and the one for the next transfer. These counters define the size of data to be transferred by the channel. The current transfer counter is decremented first as the data addressed by the current memory pointer starts to be transferred. When the current transfer counter reaches zero, the channel checks its next transfer counter. If the value of the next counter is zero, the channel stops transferring data and sets the appropriate flag. If the next counter value is greater than zero, the values of the next pointer/next counter are copied into the current pointer/current counter and the channel resumes the transfer, whereas next pointer/next counter get zero/zero as values.At the end of this transfer, the PDC channel sets the appropriate flags in the Peripheral Status register.

The following list gives an overview of how status register flags behave depending on the counters' values:

- ENDRX flag is set when the PDC Receive Counter Register (PERIPH\_RCR) reaches zero.

- RXBUFF flag is set when both PERIPH\_RCR and the PDC Receive Next Counter Register (PERIPH\_RNCR) reach zero.

- ENDTX flag is set when the PDC Transmit Counter Register (PERIPH\_TCR) reaches zero.

- TXBUFE flag is set when both PERIPH\_TCR and the PDC Transmit Next Counter Register (PERIPH\_TNCR) reach zero.

These status flags are described in the Transfer Status Register (PERIPH\_PTSR).

### 27.5.4 Data Transfers

The serial peripheral triggers its associated PDC channels' transfers using transmit enable (TXEN) and receive enable (RXEN) flags in the transfer control register integrated in the peripheral's user interface.

When the peripheral receives external data, it sends a Receive Ready signal to its PDC receive channel which then requests access to the Matrix. When access is granted, the PDC receive channel starts reading the peripheral Receive Holding register (RHR). The read data are stored in an internal buffer and then written to memory.

When the peripheral is about to send data, it sends a Transmit Ready to its PDC transmit channel which then requests access to the Matrix. When access is granted, the PDC transmit channel reads data from memory and transfers the data to the Transmit Holding register (THR) of its associated peripheral. The same peripheral sends data depending on its mechanism.

### 27.5.5 PDC Flags and Peripheral Status Register

Each peripheral connected to the PDC sends out receive ready and transmit ready flags and the PDC returns flags to the peripheral. All these flags are only visible in the peripheral's Status register.

Depending on whether the peripheral is half- or full-duplex, the flags belong to either one single channel or two different channels.

#### 27.5.5.1 Receive Transfer End

The receive transfer end flag is set when PERIPH\_RCR reaches zero and the last data has been transferred to memory.

This flag is reset by writing a non-zero value to PERIPH\_RCR or PERIPH\_RNCR.

#### 27.5.5.2 Transmit Transfer End

The transmit transfer end flag is set when PERIPH\_TCR reaches zero and the last data has been written to the peripheral THR.

This flag is reset by writing a non-zero value to PERIPH\_TCR or PERIPH\_TNCR.

#### 27.5.5.3 Receive Buffer Full

The receive buffer full flag is set when PERIPH\_RCR reaches zero, with PERIPH\_RNCR also set to zero and the last data transferred to memory.

This flag is reset by writing a non-zero value to PERIPH\_TCR or PERIPH\_TNCR.

#### 27.5.5.4 Transmit Buffer Empty

The transmit buffer empty flag is set when PERIPH\_TCR reaches zero, with PERIPH\_TNCR also set to zero and the last data written to peripheral THR.

This flag is reset by writing a non-zero value to PERIPH\_TCR or PERIPH\_TNCR.

Atmel

### 27.6.9 Transfer Control Register

| Name:   | PERIPH_PTCR |    |    |    |    |        |       |

|---------|-------------|----|----|----|----|--------|-------|

| Access: | Write-only  |    |    |    |    |        |       |

| 31      | 30          | 29 | 28 | 27 | 26 | 25     | 24    |

| -       | -           | _  | -  | -  | -  | -      | -     |

| 23      | 22          | 21 | 20 | 19 | 18 | 17     | 16    |

| _       | -           | _  | -  | -  | _  | _      | -     |

| 15      | 14          | 13 | 12 | 11 | 10 | 9      | 8     |

| _       | _           | _  | _  | _  | _  | TXTDIS | TXTEN |

| 7       | 6           | 5  | 4  | 3  | 2  | 1      | 0     |

| -       | -           | _  | -  | -  | -  | RXTDIS | RXTEN |

### • RXTEN: Receiver Transfer Enable

0: No effect.

1: Enables PDC receiver channel requests if RXTDIS is not set.

When a half-duplex peripheral is connected to the PDC, enabling the receiver channel requests automatically disables the transmitter channel requests. It is forbidden to set both TXTEN and RXTEN for a half-duplex peripheral.

### • RXTDIS: Receiver Transfer Disable

0: No effect.

1: Disables the PDC receiver channel requests.

When a half-duplex peripheral is connected to the PDC, disabling the receiver channel requests also disables the transmitter channel requests.

#### • TXTEN: Transmitter Transfer Enable

0: No effect.

1: Enables the PDC transmitter channel requests.

When a half-duplex peripheral is connected to the PDC, it enables the transmitter channel requests only if RXTEN is not set. It is forbidden to set both TXTEN and RXTEN for a half-duplex peripheral.

### • TXTDIS: Transmitter Transfer Disable

0: No effect.

1: Disables the PDC transmitter channel requests.

When a half-duplex peripheral is connected to the PDC, disabling the transmitter channel requests disables the receiver channel requests.

Atmel

### 31.6.15 PIO Interrupt Disable Register

| Name:    | PIO_IDR                                                 |     |     |     |     |     |     |  |  |  |

|----------|---------------------------------------------------------|-----|-----|-----|-----|-----|-----|--|--|--|

| Address: | 0x400E0E44 (PIOA), 0x400E1044 (PIOB), 0x400E1244 (PIOC) |     |     |     |     |     |     |  |  |  |

| Access:  | Write-only                                              |     |     |     |     |     |     |  |  |  |

| 31       | 30                                                      | 29  | 28  | 27  | 26  | 25  | 24  |  |  |  |

| P31      | P30                                                     | P29 | P28 | P27 | P26 | P25 | P24 |  |  |  |

| 23       | 22                                                      | 21  | 20  | 19  | 18  | 17  | 16  |  |  |  |

| P23      | P22                                                     | P21 | P20 | P19 | P18 | P17 | P16 |  |  |  |

| 15       | 14                                                      | 13  | 12  | 11  | 10  | 9   | 8   |  |  |  |

| P15      | P14                                                     | P13 | P12 | P11 | P10 | P9  | P8  |  |  |  |

| 7        | 6                                                       | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

| P7       | P6                                                      | P5  | P4  | P3  | P2  | P1  | P0  |  |  |  |

### • P0–P31: Input Change Interrupt Disable

0: No effect.

1: Disables the input change interrupt on the I/O line.

### 31.6.16 PIO Interrupt Mask Register

| Name:    | PIO_IMR       |                |                 |              |     |     |     |

|----------|---------------|----------------|-----------------|--------------|-----|-----|-----|

| Address: | 0x400E0E48 (P | IOA), 0x400E10 | 048 (PIOB), 0x4 | 00E1248 (PIO | C)  |     |     |

| Access:  | Read-only     |                |                 |              |     |     |     |

| 31       | 30            | 29             | 28              | 27           | 26  | 25  | 24  |

| P31      | P30           | P29            | P28             | P27          | P26 | P25 | P24 |

| 23       | 22            | 21             | 20              | 19           | 18  | 17  | 16  |

| P23      | P22           | P21            | P20             | P19          | P18 | P17 | P16 |

| 15       | 14            | 13             | 12              | 11           | 10  | 9   | 8   |

| P15      | P14           | P13            | P12             | P11          | P10 | P9  | P8  |

| 7        | 6             | 5              | 4               | 3            | 2   | 1   | 0   |

| P7       | P6            | P5             | P4              | P3           | P2  | P1  | P0  |

### • P0–P31: Input Change Interrupt Mask

0: Input change interrupt is disabled on the I/O line.

1: Input change interrupt is enabled on the I/O line.

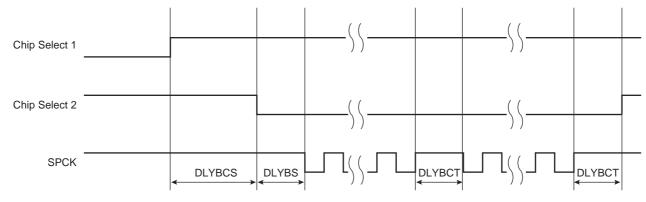

• Delay between consecutive transfers—independently programmable for each chip select by writing the DLYBCT field. The time required by the SPI slave device to process received data is managed through DLYBCT. This time depends on the SPI slave system activity.

These delays allow the SPI to be adapted to the interfaced peripherals and their speed and bus release time.

### Figure 33-10. Programmable Delays

### 33.7.3.5 Peripheral Selection

The serial peripherals are selected through the assertion of the NPCS0 to NPCS3 signals. By default, all NPCS signals are high before and after each transfer.

- Fixed Peripheral Select Mode: SPI exchanges data with only one peripheral. Fixed peripheral select mode is enabled by writing the PS bit to zero in the SPI\_MR. In this case, the current peripheral is defined by the PCS field in the SPI\_MR and the PCS field in the SPI\_TDR has no effect.

- Variable Peripheral Select Mode: Data can be exchanged with more than one peripheral without having to reprogram the NPCS field in the SPI\_MR.

Variable peripheral select mode is enabled by setting the PS bit to 1 in the SPI\_MR. The PCS field in the SPI\_TDR is used to select the current peripheral. This means that the peripheral selection can be defined for each new data. The value to write in the SPI\_TDR has the following format:

$[xxxxxx(7-bit) + LASTXFER(1-bit)^{(1)} + xxxx(4-bit) + PCS (4-bit) + DATA (8 to 16-bit)]$  with PCS equals the chip select to assert, as defined in Section 33.8.4 "SPI Transmit Data Register" and LASTXFER bit at 0 or 1 depending on the CSAAT bit.

Note: 1. Optional

CSAAT, LASTXFER and CSNAAT bits are discussed in Section 33.7.3.9 "Peripheral Deselection with PDC".

If LASTXFER is used, the command must be issued after writing the last character. Instead of LASTXFER, the user can use the SPIDIS command. After the end of the PDC transfer, it is necessary to wait for the TXEMPTY flag and then write SPIDIS into the SPI Control Register (SPI\_CR). This does not change the configuration register values). The NPCS is disabled after the last character transfer. Then, another PDC transfer can be started if the SPIEN has previously been written in the SPI\_CR.

#### 33.7.3.6 SPI Peripheral DMA Controller (PDC)

In both Fixed and Variable peripheral select modes, the Peripheral DMA Controller (PDC) can be used to reduce processor overhead.

The fixed peripheral selection allows buffer transfers with a single peripheral. Using the PDC is an optimal means, as the size of the data transfer between the memory and the SPI is either 8 bits or 16 bits. However, if the peripheral selection is modified, the SPI\_MR must be reprogrammed.

| 33.8.2 SPI | Mode Register |       |         |     |        |    |      |

|------------|---------------|-------|---------|-----|--------|----|------|

| Name:      | SPI_MR        |       |         |     |        |    |      |

| Address:   | 0x40008004    |       |         |     |        |    |      |

| Access:    | Read/Write    |       |         |     |        |    |      |

| 31         | 30            | 29    | 28      | 27  | 26     | 25 | 24   |

|            |               |       | DLY     | BCS |        |    |      |

| 23         | 22            | 21    | 20      | 19  | 18     | 17 | 16   |

| _          | -             | -     | -       |     | PC     | S  |      |

| 15         | 14            | 13    | 12      | 11  | 10     | 9  | 8    |

| -          | -             | -     | -       | —   | -      | -  | -    |

| 7          | 6             | 5     | 4       | 3   | 2      | 1  | 0    |

| LLB        | -             | WDRBT | MODFDIS | -   | PCSDEC | PS | MSTR |

This register can only be written if the WPEN bit is cleared in the SPI Write Protection Mode Register.

### • MSTR: Master/Slave Mode

22.0.0 CDI Mada Daviatar

0: SPI is in Slave mode

1: SPI is in Master mode

### • PS: Peripheral Select

0: Fixed Peripheral Select

1: Variable Peripheral Select

### • PCSDEC: Chip Select Decode

0: The chip selects are directly connected to a peripheral device.

1: The four NPCS chip select lines are connected to a 4-bit to 16-bit decoder.

When PCSDEC = 1, up to 15 Chip Select signals can be generated with the four NPCS lines using an external 4-bit to 16bit decoder. The Chip Select registers define the characteristics of the 15 chip selects, with the following rules:

SPI\_CSR0 defines peripheral chip select signals 0 to 3.

SPI\_CSR1 defines peripheral chip select signals 4 to 7.

SPI\_CSR2 defines peripheral chip select signals 8 to 11.

SPI\_CSR3 defines peripheral chip select signals 12 to 14.

### MODFDIS: Mode Fault Detection

0: Mode fault detection enabled

1: Mode fault detection disabled

### WDRBT: Wait Data Read Before Transfer

0: No Effect. In Master mode, a transfer can be initiated regardless of the SPI\_RDR state.

1: In Master mode, a transfer can start only if the SPI\_RDR is empty, i.e., does not contain any unread data. This mode prevents overrun error in reception.

Atmel

### 34.8.5 TWI Clock Waveform Generator Register

| Name:    | TWI_CWGR                       |    |    |     |    |       |    |  |  |  |

|----------|--------------------------------|----|----|-----|----|-------|----|--|--|--|

| Address: | 0x40018010 (0), 0x4001C010 (1) |    |    |     |    |       |    |  |  |  |

| Access:  | Read/Write                     |    |    |     |    |       |    |  |  |  |

| 31       | 30                             | 29 | 28 | 27  | 26 | 25    | 24 |  |  |  |

| -        | -                              | -  | -  | -   | -  | -     | -  |  |  |  |

| 23       | 22                             | 21 | 20 | 19  | 18 | 17    | 16 |  |  |  |

| —        | -                              | _  | -  | -   |    | CKDIV |    |  |  |  |

| 15       | 14                             | 13 | 12 | 11  | 10 | 9     | 8  |  |  |  |

|          |                                |    | CH | DIV |    |       |    |  |  |  |

| 7        | 6                              | 5  | 4  | 3   | 2  | 1     | 0  |  |  |  |

|          |                                |    | CL | DIV |    |       |    |  |  |  |

TWI\_CWGR is only used in Master mode.

### • CLDIV: Clock Low Divider

The TWCK low period is defined as follows:  $t_{\text{low}}$  = ((CLDIV  $\times 2^{\text{CKDIV}})$  + 4  $\times t_{\text{peripheral clock}}$

### • CHDIV: Clock High Divider

The TWCK high period is defined as follows:  $t_{high} = ((CHDIV \times 2^{CKDIV}) + 4 \times t_{peripheral clock})$

### • CKDIV: Clock Divider

The TWCK is used to increase both SCL high and low periods.

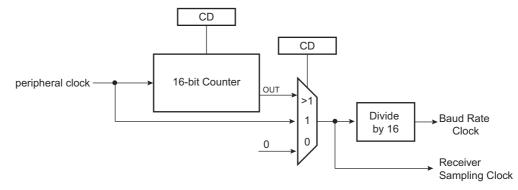

#### Figure 35-2. Baud Rate Generator

#### 35.5.2 Receiver

#### 35.5.2.1 Receiver Reset, Enable and Disable

After device reset, the UART receiver is disabled and must be enabled before being used. The receiver can be enabled by writing the Control Register (UART\_CR) with the bit RXEN at 1. At this command, the receiver starts looking for a start bit.

The programmer can disable the receiver by writing UART\_CR with the bit RXDIS at 1. If the receiver is waiting for a start bit, it is immediately stopped. However, if the receiver has already detected a start bit and is receiving the data, it waits for the stop bit before actually stopping its operation.

The receiver can be put in reset state by writing UART\_CR with the bit RSTRX at 1. In this case, the receiver immediately stops its current operations and is disabled, whatever its current state. If RSTRX is applied when data is being processed, this data is lost.

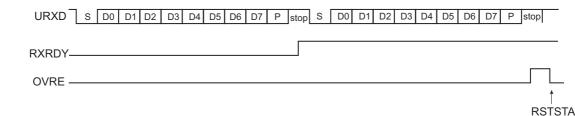

#### 35.5.2.2 Start Detection and Data Sampling

The UART only supports asynchronous operations, and this affects only its receiver. The UART receiver detects the start of a received character by sampling the URXD signal until it detects a valid start bit. A low level (space) on URXD is interpreted as a valid start bit if it is detected for more than seven cycles of the sampling clock, which is 16 times the baud rate. Hence, a space that is longer than 7/16 of the bit period is detected as a valid start bit. A space which is 7/16 of a bit period or shorter is ignored and the receiver continues to wait for a valid start bit.

When a valid start bit has been detected, the receiver samples the URXD at the theoretical midpoint of each bit. It is assumed that each bit lasts 16 cycles of the sampling clock (1-bit period) so the bit sampling point is eight cycles (0.5-bit period) after the start of the bit. The first sampling point is therefore 24 cycles (1.5-bit periods) after detecting the falling edge of the start bit.

Each subsequent bit is sampled 16 cycles (1-bit period) after the previous one.

#### Figure 35-3. Start Bit Detection

### 38.10.1 Executing an ATA Polling Command

- 1. Issue READ\_DMA\_EXT with RW\_MULTIPLE\_REGISTER (CMD60) for 8 KB of DATA.

- 2. Read the ATA status register until DRQ is set.

- 3. Issue RW\_MULTIPLE\_BLOCK (CMD61) to transfer DATA.

- 4. Read the ATA status register until DRQ && BSY are configured to 0.

#### 38.10.2 Executing an ATA Interrupt Command

- 1. Issue READ\_DMA\_EXT with RW\_MULTIPLE\_REGISTER (CMD60) for 8 KB of DATA with nIEN field set to zero to enable the command completion signal in the device.

- 2. Issue RW\_MULTIPLE\_BLOCK (CMD61) to transfer DATA.

- 3. Wait for Completion Signal Received Interrupt.

#### 38.10.3 Aborting an ATA Command

If the host needs to abort an ATA command prior to the completion signal it must send a special command to avoid potential collision on the command line. The SPCMD field of the HSMCI\_CMDR must be set to 3 to issue the CE-ATA completion Signal Disable Command.

### 38.10.4 CE-ATA Error Recovery

Several methods of ATA command failure may occur, including:

- No response to an MMC command, such as RW\_MULTIPLE\_REGISTER (CMD60).

- CRC is invalid for an MMC command or response.

- CRC16 is invalid for an MMC data packet.

- ATA Status register reflects an error by setting the ERR bit to one.

- The command completion signal does not arrive within a host specified time out period.

Error conditions are expected to happen infrequently. Thus, a robust error recovery mechanism may be used for each error event. The recommended error recovery procedure after a timeout is:

- Issue the command completion signal disable if nIEN was cleared to zero and the RW\_MULTIPLE\_BLOCK (CMD61) response has been received.

- Issue STOP\_TRANSMISSION (CMD12) and successfully receive the R1 response.

- Issue a software reset to the CE-ATA device using FAST\_IO (CMD39).

If STOP\_TRANMISSION (CMD12) is successful, then the device is again ready for ATA commands. However, if the error recovery procedure does not work as expected or there is another timeout, the next step is to issue GO\_IDLE\_STATE (CMD0) to the device. GO\_IDLE\_STATE (CMD0) is a hard reset to the device and completely resets all device states.

Note that after issuing GO\_IDLE\_STATE (CMD0), all device initialization needs to be completed again. If the CE-ATA device completes all MMC commands correctly but fails the ATA command with the ERR bit set in the ATA Status register, no error recovery action is required. The ATA command itself failed implying that the device could not complete the action requested, however, there was no communication or protocol failure. After the device signals an error by setting the ERR bit to one in the ATA Status register, the host may attempt to retry the command.

### 38.11 HSMCI Boot Operation Mode

In boot operation mode, the processor can read boot data from the slave (MMC device) by keeping the CMD line low after power-on before issuing CMD1. The data can be read from either the boot area or user area, depending on register setting. As it is not possible to boot directly on SD-CARD, a preliminary boot code must be stored in internal Flash.

#### 38.14.2 HSMCI Mode Register

| Name:    | HSMCI_MR   |       |         |         |    |        |    |

|----------|------------|-------|---------|---------|----|--------|----|

| Address: | 0x40000004 |       |         |         |    |        |    |

| Access:  | Read/Write |       |         |         |    |        |    |

| 31       | 30         | 29    | 28      | 27      | 26 | 25     | 24 |

| —        | -          | -     | _       | —       | —  | _      | -  |

| 23       | 22         | 21    | 20      | 19      | 18 | 17     | 16 |

| _        | -          | —     | —       | —       | —  | —      | -  |

| 15       | 14         | 13    | 12      | 11      | 10 | 9      | 8  |

| PDCMODE  | PADV       | FBYTE | WRPROOF | RDPROOF |    | PWSDIV |    |

| 7        | 6          | 5     | 4       | 3       | 2  | 1      | 0  |

|          |            |       | CLk     | (DIV    |    |        |    |

This register can only be written if the WPEN bit is cleared in the HSMCI Write Protection Mode Register.

### • CLKDIV: Clock Divider

High Speed MultiMedia Card Interface clock (MCCK or HSMCI\_CK) is Master Clock (MCK) divided by (2\*(CLKDIV+1)).

#### PWSDIV: Power Saving Divider

High Speed MultiMedia Card Interface clock is divided by 2<sup>(PWSDIV)</sup> + 1 when entering Power Saving Mode.

<u>Warning</u>: This value must be different from 0 before enabling the Power Save Mode in the HSMCI\_CR (HSMCI\_PWSEN bit).

### • RDPROOF: Read Proof Enable

Enabling Read Proof allows to stop the HSMCI Clock during read access if the internal FIFO is full. This will guarantee data integrity, not bandwidth.

- 0: Disables Read Proof.

- 1: Enables Read Proof.

### • WRPROOF: Write Proof Enable

Enabling Write Proof allows to stop the HSMCI Clock during write access if the internal FIFO is full. This will guarantee data integrity, not bandwidth.

0: Disables Write Proof.

1: Enables Write Proof.

### • FBYTE: Force Byte Transfer

Enabling Force Byte Transfer allow byte transfers, so that transfer of blocks with a size different from modulo 4 can be supported.

Warning: BLKLEN value depends on FBYTE.

- 0: Disables Force Byte Transfer.

- 1: Enables Force Byte Transfer.

### 39.7.21 PWM Output Selection Set Update Register

| Name:<br>Address: | PWM_OSSUPD<br>0x40020054 |    |    |               |               |               |               |

|-------------------|--------------------------|----|----|---------------|---------------|---------------|---------------|

| Access:           | Write-only               |    |    |               |               |               |               |

| 31                | 30                       | 29 | 28 | 27            | 26            | 25            | 24            |

| _                 | -                        | _  | -  | -             | -             | -             | —             |

| 23                | 22                       | 21 | 20 | 19<br>OSSUPL3 | 18<br>OSSUPL2 | 17<br>OSSUPL1 | 16<br>OSSUPL0 |

| 15                | 14                       | 13 | 12 | 11            | 10            | 9             | 8             |

| _                 | -                        | _  | _  | _             | _             | _             | -             |

| 7                 | 6                        | 5  | 4  | 3             | 2             | 1             | 0             |

| _                 | -                        | _  | _  | OSSUPH3       | OSSUPH2       | OSSUPH1       | OSSUPH0       |

### OSSUPHx: Output Selection Set for PWMH output of the channel x

0: No effect.

1: Output override value OOVHx selected as PWMH output of channel x at the beginning of the next channel x PWM period.

### OSSUPLx: Output Selection Set for PWML output of the channel x

0: No effect.

1: Output override value OOVLx selected as PWML output of channel x at the beginning of the next channel x PWM period.

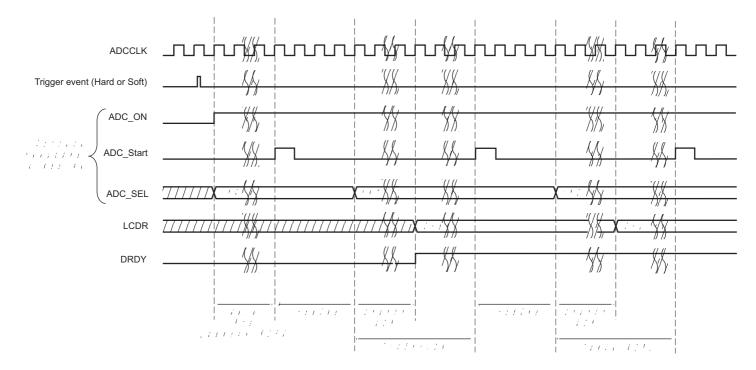

#### Figure 42-2. Sequence of ADC Conversions When Tracking Time > Conversion Time

Atmel

# 44. Electrical Characteristics

# 44.1 Absolute Maximum Ratings

#### Table 44-1. Absolute Maximum Ratings\*

| Storage Temperature                                             | C to + 150°C |

|-----------------------------------------------------------------|--------------|

| Solder Temperature                                              | 260°C        |

| Voltage on all input pins<br>with Respect to Ground0.3V to + VD | DIO + 0.4V   |

| Maximum Operating Voltage<br>(VDDCORE)                          | 1.32V        |

| Maximum Operating Voltage<br>(VDDIO)                            | 4.0V         |

| Total DC Output Current on all I/O lines                        |              |

| 100-lead LQFP                                                   | 150 mA       |

| 100-ball TFBGA                                                  |              |

| 100-ball VFBGA                                                  | 150 mA       |

| 64-lead LQFP                                                    | 100 mA       |

| 64-lead QFN                                                     |              |

| 64-lead WLCSP                                                   | 100 mA       |

\*Notice: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# 44.2 Recommended Operating Conditions

### Table 44-2. Recommended Operating Conditions

| Symbol                   | Parameter                              | Conditions                  | Min  | Тур  | Max  | Unit |

|--------------------------|----------------------------------------|-----------------------------|------|------|------|------|

| T <sub>A</sub>           | Ambient Temperature Range              |                             | -40  | _    | +105 | °C   |

| VDDCORE                  | DC Supply Core                         |                             | 1.08 | 1.20 | 1.32 | V    |

| VDDIO                    | DC Supply I/Os                         |                             | 1.62 | 3.3  | 3.6  | V    |

| V <sub>DDPLL</sub>       | PLL A, PLLB and Main Oscillator Supply |                             | 1.08 | _    | 1.32 | V    |

| V <sub>rip(VDDIO)</sub>  | Supply Ripple Voltage (on VDDIO)       | RMS value, 10 kHz to 10 MHz | _    | _    | 30   | mV   |

| V <sub>rip(VDDPLL)</sub> | Supply Ripple Voltage (on VDDPLL)      | RMS value, 10 kHz to 10 MHz | _    | _    | 20   | mV   |

|                          |                                        | RMS value > 10 MHz          | _    | _    | 10   |      |

| V <sub>rip(VDDIN)</sub>  | Supply Ripple Voltage (on VDDIN)       | RMS value, 10 kHz to 20 MHz | _    | _    | 20   | mV   |

| f <sub>MCK</sub>         | Master Clock Frequency                 | VDDCORE @ 1.20V             | _    | _    | 120  | MHz  |

|                          |                                        | VDDCORE @ 1.08V             | _    | _    | 100  |      |

# 44.12 AC Characteristics

### 44.12.1 Master Clock Characteristics

#### Table 44-63. Master Clock Waveform Parameters

| Symbol                  | Parameter              | Conditions      | Min | Max | Unit    |

|-------------------------|------------------------|-----------------|-----|-----|---------|

| 1/(t <sub>CPMCK</sub> ) | Master Clock Frequency | VDDCORE @ 1.20V | -   | 120 | MHz     |

|                         |                        | VDDCORE @ 1.08V | -   | 100 | IVII IZ |

### 44.12.2 I/O Characteristics

Criteria used to define the maximum frequency of the I/Os:

- Output duty cycle (40%–60%)

- Minimum output swing: 100 mV to V<sub>DDIO</sub> 100 mV

- Minimum output swing: 100 mV to V<sub>DDIO</sub> 100 mV

- Addition of rising and falling time inferior to 75% of the period

#### Table 44-64.I/O Characteristics

| Symbol              | Parameter                                           | Conditions |                           | Min  | Max  | Unit  |

|---------------------|-----------------------------------------------------|------------|---------------------------|------|------|-------|

| FreqMax1            | Pin Group 1 <sup>(1)</sup> Maximum Output Frequency | 10 pF      |                           | _    | 70   | - MHz |

|                     |                                                     | 30 pF      |                           | _    | 45   |       |

| PulseminH1          | Pin Group 1 <sup>(1)</sup> High Level Pulse Width   | 10 pF      |                           | _    | _    | ns    |

|                     |                                                     | 30 pF      |                           | 11   | _    |       |

| PulseminL1          | Pin Group 1 <sup>(1)</sup> Low Level Pulse Width    | 10 pF      |                           | 7.2  | _    | - ns  |

|                     |                                                     | 30 pF      |                           | 11   | -    |       |

| Free May 2          | Pin Group 2 <sup>(2)</sup> Maximum Output Frequency | 10 pF      | -                         | _    | 46   | MHz   |

| FreqMax2            |                                                     | 25 pF      | _                         | _    | 23   |       |

| PulseminH2          | Pin Group 2 <sup>(2)</sup> High Level Pulse Width   | 10 pF      |                           | 11   | _    | – ns  |

| Puiseminnz          |                                                     | 25 pF      |                           | 21.8 | _    |       |

| PulseminL2          | Pin Group 2 <sup>(2)</sup> Low Level Pulse Width    | 10 pF      |                           | 11   | -    |       |

|                     |                                                     | 25 pF      |                           | 21.8 | -    | ns    |

| Frog Moy 2          | Pin Group3 <sup>(3)</sup> Maximum Output Frequency  | 10 pF      | _                         | -    | 70   | MHz   |

| FreqMax3            |                                                     | 25 pF      | V <sub>DDIO</sub> = 1.62V | -    | 35   |       |

| PulseminH3          | Pin Group 3 <sup>(3)</sup> High Level Pulse Width   | 10 pF      |                           | 7.2  | -    | ns    |

|                     |                                                     | 25 pF      |                           | 14.2 | -    |       |

| PulseminL3          | Pin Group 3 <sup>(3)</sup> Low Level Pulse Width    | 10 pF      |                           | 7.2  | -    | ns    |

|                     |                                                     | 25 pF      |                           | 14.2 | -    |       |

| FreqMax4            | Pin Group 4 <sup>(4)</sup> Maximum Output Frequency | 10 pF      |                           | -    | 58   | – MHz |

|                     |                                                     | 25 pF      |                           | -    | 29   |       |

| PulseminH4          | Pin Group 4 <sup>(4)</sup> High Level Pulse Width   | 10 pF      |                           | 8.6  | -    | ns    |

|                     |                                                     | 25 pF      |                           | 17.2 | -    |       |

| PulseminL4          | Pin Group 4 <sup>(4)</sup> Low Level Pulse Width    | 10 pF      |                           | 8.6  | _    | – ns  |

|                     |                                                     | 25 pF      |                           | 17.2 | _    |       |

| FreqMax5            | Pin Group 5 <sup>(5)</sup> Maximum Output Frequency | 25 pF      | 1                         | -    | 25   | MHz   |

| t <sub>sk(io)</sub> | Maximum I/O skew for all I/Os except PB0            | 30 pF      |                           | -    | 800  | – ps  |

|                     | Maximum I/O skew for PB0                            | su pr      |                           | _    | 1200 |       |

Notes: 1. Pin Group 1 = PA14, PA29