Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | ARM® Cortex®-M4                                                           |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 120MHz                                                                    |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, Memory Card, SPI, SSC, UART/USART, USB   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                |

| Number of I/O              | 79                                                                        |

| Program Memory Size        | 2MB (2M x 8)                                                              |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 160K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                              |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                     |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 100-TFBGA                                                                 |

| Supplier Device Package    | 100-TFBGA (9x9)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4sd32cb-cn |

S is an optional suffix. If S is specified, the condition code flags are updated on the result of the operation, see "Conditional Execution".

cond is an optional condition code, see "Conditional Execution".

Rd is the destination register.

Rn is the register holding the first operand.

Operand2 is a flexible second operand. See "Flexible Second Operand" for details of the

options.

#### Operation

The AND, EOR, and ORR instructions perform bitwise AND, Exclusive OR, and OR operations on the values in *Rn* and *Operand*2.

The BIC instruction performs an AND operation on the bits in *Rn* with the complements of the corresponding bits in the value of *Operand2*.

The ORN instruction performs an OR operation on the bits in *Rn* with the complements of the corresponding bits in the value of *Operand2*.

#### Restrictions

Do not use SP and do not use PC.

### Condition Flags

If S is specified, these instructions:

- Update the N and Z flags according to the result

- Can update the C flag during the calculation of Operand2, see "Flexible Second Operand"

- Do not affect the V flag.

Note: 1. Each array element corresponds to a single NVIC register, for example the ICER[0] element corresponds to the ICER0.

If the user disables a system handler and the corresponding fault occurs, the processor treats the fault as a hard fault.

The user can write to this register to change the pending or active status of system exceptions. An OS kernel can write to the active bits to perform a context switch that changes the current exception type.

#### 12.9.1.13 Configurable Fault Status Register

| Name:<br>Access: | SCB_CFSR<br>Read/Write |    |         |           |             |           |            |

|------------------|------------------------|----|---------|-----------|-------------|-----------|------------|

| 31               | 30                     | 29 | 28      | 27        | 26          | 25        | 24         |

| _                | _                      | _  | _       | _         | _           | DIVBYZERO | UNALIGNED  |

| 23               | 22                     | 21 | 20      | 19        | 18          | 17        | 16         |

| _                | _                      | _  | _       | NOCP      | INVPC       | INVSTATE  | UNDEFINSTR |

| 15               | 14                     | 13 | 12      | 11        | 10          | 9         | 8          |

| BFARVALID        | -                      | _  | STKERR  | UNSTKERR  | IMPRECISERR | PRECISERR | IBUSERR    |

| 7                | 6                      | 5  | 4       | 3         | 2           | 1         | 0          |

| MMARVALID        | _                      | _  | MSTKERR | MUNSTKERR | _           | DACCVIOL  | IACCVIOL   |

#### • IACCVIOL: Instruction Access Violation Flag

This is part of "MMFSR: Memory Management Fault Status Subregister" .

0: No instruction access violation fault.

1: The processor attempted an instruction fetch from a location that does not permit execution.

This fault occurs on any access to an XN region, even when the MPU is disabled or not present.

When this bit is 1, the PC value stacked for the exception return points to the faulting instruction. The processor has not written a fault address to the SCB MMFAR.

#### DACCVIOL: Data Access Violation Flag

This is part of "MMFSR: Memory Management Fault Status Subregister".

0: No data access violation fault.

1: The processor attempted a load or store at a location that does not permit the operation.

When this bit is 1, the PC value stacked for the exception return points to the faulting instruction. The processor has loaded the SCB\_MMFAR with the address of the attempted access.

#### MUNSTKERR: Memory Manager Fault on Unstacking for a Return From Exception

This is part of "MMFSR: Memory Management Fault Status Subregister".

No unstacking fault.

1: Unstack for an exception return has caused one or more access violations.

This fault is chained to the handler. This means that when this bit is 1, the original return stack is still present. The processor has not adjusted the SP from the failing return, and has not performed a new save. The processor has not written a fault address to the SCB\_MMFAR.

### 16.6.4 RTC Calendar Register

Name: RTC\_CALR

Address: 0x400E146C

Access: Read/Write

| 31 | 30  | 29   | 28 | 27 | 26    | 25 | 24 |  |  |

|----|-----|------|----|----|-------|----|----|--|--|

| _  | _   |      |    | DA | ΤE    |    |    |  |  |

| 23 | 22  | 21   | 20 | 19 | 18    | 17 | 16 |  |  |

|    | DAY |      |    |    | MONTH |    |    |  |  |

| 15 | 14  | 13   | 12 | 11 | 10    | 9  | 8  |  |  |

|    |     |      | YE | AR |       |    |    |  |  |

| 7  | 6   | 5    | 4  | 3  | 2     | 1  | 0  |  |  |

| _  |     | CENT |    |    |       |    |    |  |  |

### • CENT: Current Century

The range that can be set is 19–20 (gregorian) or 13–14 (persian) (BCD).

The lowest four bits encode the units. The higher bits encode the tens.

#### • YEAR: Current Year

The range that can be set is 00-99 (BCD).

The lowest four bits encode the units. The higher bits encode the tens.

### • MONTH: Current Month

The range that can be set is 01-12 (BCD).

The lowest four bits encode the units. The higher bits encode the tens.

### DAY: Current Day in Current Week

The range that can be set is 1–7 (BCD).

The coding of the number (which number represents which day) is user-defined as it has no effect on the date counter.

### • DATE: Current Day in Current Month

The range that can be set is 01-31 (BCD).

The lowest four bits encode the units. The higher bits encode the tens.

All non-significant bits read zero.

### 16.6.11 RTC Interrupt Mask Register

Name: RTC\_IMR

Address: 0x400E1488

Access: Read-only

| 31 | 30 | 29    | 28  | 27  | 26  | 25  | 24  |

|----|----|-------|-----|-----|-----|-----|-----|

| _  | _  | _     | -   |     | 1   | ı   | _   |

| 23 | 22 | 21    | 20  | 19  | 18  | 17  | 16  |

| _  | _  | _     | -   |     | ı   | ı   | _   |

| 15 | 14 | 13    | 12  | 11  | 10  | 9   | 8   |

| _  | _  | _     | _   | _   | -   | _   | _   |

| 7  | 6  | 5     | 4   | 3   | 2   | 1   | 0   |

| _  | _  | TDERR | CAL | TIM | SEC | ALR | ACK |

### ACK: Acknowledge Update Interrupt Mask

0: The acknowledge for update interrupt is disabled.

1: The acknowledge for update interrupt is enabled.

#### • ALR: Alarm Interrupt Mask

0: The alarm interrupt is disabled.

1: The alarm interrupt is enabled.

### • SEC: Second Event Interrupt Mask

0: The second periodic interrupt is disabled.

1: The second periodic interrupt is enabled.

# • TIM: Time Event Interrupt Mask

0: The selected time event interrupt is disabled.

1: The selected time event interrupt is enabled.

#### CAL: Calendar Event Interrupt Mask

0: The selected calendar event interrupt is disabled.

1: The selected calendar event interrupt is enabled.

### • TDERR: Time and/or Date Error Mask

0: The time and/or date error event is disabled.

1: The time and/or date error event is enabled.

# 17.5.3 Watchdog Timer Status Register

Name: WDT\_SR

Address: 0x400E1458

Access Read-only

| Access | Read-only |    |    |    |    |       |       |

|--------|-----------|----|----|----|----|-------|-------|

| 31     | 30        | 29 | 28 | 27 | 26 | 25    | 24    |

| _      | _         | -  | -  | -  | _  | -     | _     |

| 23     | 22        | 21 | 20 | 19 | 18 | 17    | 16    |

| _      | -         | _  | _  | _  | _  | _     | _     |

| 15     | 14        | 13 | 12 | 11 | 10 | 9     | 8     |

| _      | _         | _  | _  | _  | -  | _     | _     |

| 7      | 6         | 5  | 4  | 3  | 2  | 1     | 0     |

| _      | -         | -  | -  | -  | _  | WDERR | WDUNF |

## • WDUNF: Watchdog Underflow (cleared on read)

0: No watchdog underflow occurred since the last read of WDT\_SR.

1: At least one watchdog underflow occurred since the last read of WDT\_SR.

### • WDERR: Watchdog Error (cleared on read)

0: No watchdog error occurred since the last read of WDT\_SR.

1: At least one watchdog error occurred since the last read of WDT\_SR.

### 24.4 Device Initialization

Initialization follows the steps described below:

- 1. Stack setup

- 2. Set up the Embedded Flash Controller

- 3. External Clock detection (crystal or external clock on XIN)

- 4. If external crystal or clock with supported frequency, allow USB activation

- 5. Else, does not allow USB activation and use internal 12 MHz RC oscillator

- 6. Main oscillator frequency detection if no external clock detected

- 7. Switch Master Clock on Main Oscillator

- 8. C variable initialization

- 9. PLLA setup: PLLA is initialized to generate a 48 MHz clock

- 10. Disable the Watchdog

- 11. Initialization of UART0 (115200 bauds, 8, N, 1)

- 12. Initialization of the USB Device Port (in case USB activation allowed)

- 13. Wait for one of the following events

- 1. Check if USB device enumeration has occurred

- 2. Check if characters have been received in UART0

- 14. Jump to SAM-BA Monitor (see Section 24.5 "SAM-BA Monitor")

Figure 29-2. Master Clock Controller

#### 29.5 Processor Clock Controller

The PMC features a Processor Clock Controller (HCLK) that implements the processor Sleep mode. These processor clock can be disabled by executing the WFI (WaitForInterrupt) or the WFE (WaitForEvent) processor instruction while the LPM bit is at 0 in the PMC Fast Startup Mode Register (PMC FSMR).

The Processor Clock Controller HCLK is enabled after a reset and is automatically re-enabled by any enabled interrupt. The processor Sleep mode is entered by disabling the processor clock, which is automatically re-enabled by any enabled fast or normal interrupt, or by the reset of the product.

When processor Sleep mode is entered, the current instruction is finished before the clock is stopped, but this does not prevent data transfers from other masters of the system bus.

### 29.6 SysTick Clock

The SysTick calibration value is fixed to 12500 which allows the generation of a time base of 1 ms with SysTick clock to the maximum frequency on MCK divided by 8.

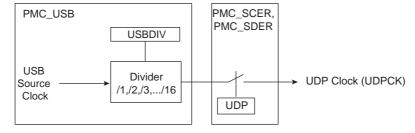

#### 29.7 USB Clock Controller

The user can select the PLLA or the PLLB output as the USB source clock by writing the USBS bit in PMC\_USB. If using the USB, the user must program the PLL to generate an appropriate frequency depending on the USBDIV bit in the USB Clock Register (PMC\_USB).

When the PLL output is stable, i.e., the LOCK bit is set, the USB device FS clock can be enabled by setting the UDP bit in the System Clock Enable Register (PMC\_SCER). To save power on this peripheral when it is not used, the user can set the UDP bit in the System Clock Disable Register (PMC\_SCDR). The UDP bit in the System Clock Status Register (PMC\_SCSR) gives the activity of this clock. The USB device port requires both the 48 MHz signal and the peripheral clock. The USB peripheral clock may be controlled by means of the Master Clock Controller.

Figure 29-3. USB Clock Controller

# 29.17.24PMC Peripheral Clock Disable Register 1

Name: PMC\_PCDR1

Address: 0x400E0504

Access: Write-only

| Access: | write-only |    |    |    |       |       |       |

|---------|------------|----|----|----|-------|-------|-------|

| 31      | 30         | 29 | 28 | 27 | 26    | 25    | 24    |

| _       | _          | _  | _  | _  | ı     | _     | _     |

| _       |            |    |    |    |       |       | _     |

| 23      | 22         | 21 | 20 | 19 | 18    | 17    | 16    |

| _       | _          | _  | _  | _  | _     | _     | _     |

|         |            |    |    |    |       |       |       |

| 15      | 14         | 13 | 12 | 11 | 10    | 9     | 8     |

| _       | _          | _  | _  | _  | _     | _     | _     |

|         |            |    |    |    |       |       |       |

| 7       | 6          | 5  | 4  | 3  | 2     | 1     | 0     |

| _       | _          | _  | _  | _  | PID34 | PID33 | PID32 |

This register can only be written if the WPEN bit is cleared in the PMC Write Protection Mode Register.

# • PIDx: Peripheral Clock x Disable

0: No effect.

Note: The values for PIDx are defined in the section "Peripheral Identifiers" in the product datasheet.

<sup>1:</sup> Disables the corresponding peripheral clock.

# 30. Chip Identifier (CHIPID)

### 30.1 Description

Chip Identifier (CHIPID) registers permit recognition of the device and its revision. These registers provide the sizes and types of the on-chip memories, as well as the set of embedded peripherals.

Two CHIPID registers are embedded: Chip ID Register (CHIPID\_CIDR) and Chip ID Extension Register (CHIPID\_EXID). Both registers contain a hard-wired value that is read-only.

The CHIPID\_CIDR contains the following fields:

- VERSION: Identifies the revision of the silicon

- EPROC: Indicates the embedded ARM processor

- NVPTYP and NVPSIZ: Identify the type of embedded non-volatile memory and the size

- SRAMSIZ: Indicates the size of the embedded SRAM

- ARCH: Identifies the set of embedded peripherals

- EXT: Shows the use of the extension identifier register

The CHIPID\_EXID register is device-dependent and reads 0 if CHIPID\_CIDR.EXT = 0.

# 31.6.5 PIO Output Disable Register

Name: PIO\_ODR

**Address:** 0x400E0E14 (PIOA), 0x400E1014 (PIOB), 0x400E1214 (PIOC)

Access: Write-only

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

| P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

| P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

This register can only be written if the WPEN bit is cleared in the PIO Write Protection Mode Register.

# • P0-P31: Output Disable

0: No effect.

1: Disables the output on the I/O line.

### 32.8.8 Loop Mode

The receiver can be programmed to receive transmissions from the transmitter. This is done by setting the Loop Mode (LOOP) bit in the SSC\_RFMR. In this case, RD is connected to TD, RF is connected to TF and RK is connected to TK.

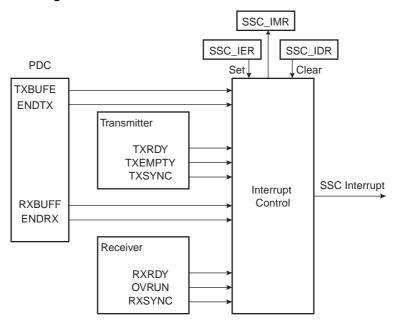

#### 32.8.9 Interrupt

Most bits in the SSC\_SR have a corresponding bit in interrupt management registers.

The SSC can be programmed to generate an interrupt when it detects an event. The interrupt is controlled by writing the Interrupt Enable Register (SSC\_IER) and Interrupt Disable Register (SSC\_IDR). These registers enable and disable, respectively, the corresponding interrupt by setting and clearing the corresponding bit in the Interrupt Mask Register (SSC\_IMR), which controls the generation of interrupts by asserting the SSC interrupt line connected to the interrupt controller.

Figure 32-19. Interrupt Block Diagram

# 32.9.5 SSC Transmit Clock Mode Register

Name: SSC\_TCMR

Address: 0x40004018

Access: Read/Write

| Access. | rcad, vviic |     |     |      |     |    |      |

|---------|-------------|-----|-----|------|-----|----|------|

| 31      | 30          | 29  | 28  | 27   | 26  | 25 | 24   |

|         |             |     | PER | RIOD |     |    |      |

| 23      | 22          | 21  | 20  | 19   | 18  | 17 | 16   |

|         |             |     | STT | DLY  |     |    |      |

| 15      | 14          | 13  | 12  | 11   | 10  | 9  | 8    |

| _       | _           | _   | _   |      | STA | RT |      |

| 7       | 6           | 5   | 4   | 3    | 2   | 1  | 0    |

|         | CKG         | CKI |     | CKO  |     | Cł | KS . |

This register can only be written if the WPEN bit is cleared in the SSC Write Protection Mode Register.

### • CKS: Transmit Clock Selection

| Value | Name | Description     |

|-------|------|-----------------|

| 0     | MCK  | Divided Clock   |

| 1     | RK   | RK Clock signal |

| 2     | TK   | TK pin          |

#### CKO: Transmit Clock Output Mode Selection

| Value | Name       | Description                                                    |

|-------|------------|----------------------------------------------------------------|

| 0     | NONE       | None, TK pin is an input                                       |

| 1     | CONTINUOUS | Continuous Transmit Clock, TK pin is an output                 |

| 2     | TRANSFER   | Transmit Clock only during data transfers, TK pin is an output |

### • CKI: Transmit Clock Inversion

0: The data outputs (Data and Frame Sync signals) are shifted out on Transmit Clock falling edge. The Frame sync signal input is sampled on Transmit clock rising edge.

1: The data outputs (Data and Frame Sync signals) are shifted out on Transmit Clock rising edge. The Frame sync signal input is sampled on Transmit clock falling edge.

CKI affects only the Transmit Clock and not the output clock signal.

### • CKG: Transmit Clock Gating Selection

| Value             | Name       | Description                            |

|-------------------|------------|----------------------------------------|

| 0 CONTINUOUS None |            | None                                   |

| 1                 | EN_TF_LOW  | Transmit Clock enabled only if TF Low  |

| 2                 | EN_TF_HIGH | Transmit Clock enabled only if TF High |

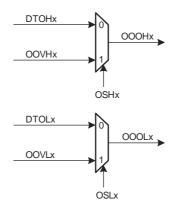

Figure 39-8. Override Output Selection

The fields OSHx and OSLx in the PWM Output Selection Register (PWM\_OS) allow the outputs of the dead-time generator DTOHx and DTOLx to be overridden by the value defined in the fields OOVHx and OOVLx in the PWM Output Override Value Register (PWM\_OOV).

The set registers PWM Output Selection Set Register (PWM\_OSS) and PWM Output Selection Set Update Register (PWM\_OSSUPD) enable the override of the outputs of a channel regardless of other channels. In the same way, the clear registers PWM Output Selection Clear Register (PWM\_OSC) and PWM Output Selection Clear Update Register (PWM\_OSCUPD) disable the override of the outputs of a channel regardless of other channels.

By using buffer registers PWM\_OSSUPD and PWM\_OSCUPD, the output selection of PWM outputs is done synchronously to the channel counter, at the beginning of the next PWM period.

By using registers PWM\_OSS and PWM\_OSC, the output selection of PWM outputs is done asynchronously to the channel counter, as soon as the register is written.

The value of the current output selection can be read in PWM\_OS.

While overriding PWM outputs, the channel counters continue to run, only the PWM outputs are forced to user defined values.

# 39.7.22 PWM Output Selection Clear Update Register

Name: PWM\_OSCUPD

Address: 0x40020058

Access: Write-only

| Access:   | write-only |    |    |         |         |         |         |

|-----------|------------|----|----|---------|---------|---------|---------|

| 31        | 30         | 29 | 28 | 27      | 26      | 25      | 24      |

| _         | _          | _  | _  | _       | _       | -       | _       |

| \ <u></u> |            | -  |    |         | -       |         | -       |

| 23        | 22         | 21 | 20 | 19      | 18      | 17      | 16      |

| _         | _          | _  | _  | OSCUPL3 | OSCUPL2 | OSCUPL1 | OSCUPL0 |

|           | -          | -  | -  |         | -       |         | -       |

| 15        | 14         | 13 | 12 | 11      | 10      | 9       | 8       |

| _         | _          | _  | _  | ı       | _       | 1       | _       |

|           |            |    |    |         |         |         | _       |

| 7         | 6          | 5  | 4  | 3       | 2       | 1       | 0       |

| _         | _          | _  | _  | OSCUPH3 | OSCUPH2 | OSCUPH1 | OSCUPH0 |

## • OSCUPHx: Output Selection Clear for PWMH output of the channel x

0: No effect.

## • OSCUPLx: Output Selection Clear for PWML output of the channel x

0: No effect.

<sup>1:</sup> Dead-time generator output DTOHx selected as PWMH output of channel x at the beginning of the next channel x PWM period.

<sup>1:</sup> Dead-time generator output DTOLx selected as PWML output of channel x at the beginning of the next channel x PWM period.

### 40.7.3 UDP Function Address Register

UDP FADDR Name: Address: 0x40034008 Access: Read/Write 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 12 10 9 8 14 13 11 **FEN**

### • FADD[6:0]: Function Address Value

6

5

The Function Address Value must be programmed by firmware once the device receives a set address request from the host, and has achieved the status stage of the no-data control sequence. Refer to the *Universal Serial Bus Specification, Rev. 2.0* for more information. After power up or reset, the function address value is set to 0.

3

FADD

2

1

4

#### • FEN: Function Enable

Read:

0: Function endpoint disabled

1: Function endpoint enabled

Write:

0: Disables function endpoint

1: Default value

7

The Function Enable bit (FEN) allows the microcontroller to enable or disable the function endpoints. The microcontroller sets this bit after receipt of a reset from the host. Once this bit is set, the USB device is able to accept and transfer data packets from and to the host.

0

# 41.7.8 ACC Write Protection Mode Register

Name: ACC\_WPMR

Address: 0x400400E4

Access: Read/Write

| 31    | 30 | 29 | 28 | 27 | 26 | 25 | 24   |

|-------|----|----|----|----|----|----|------|

| WPKEY |    |    |    |    |    |    |      |

| 23    | 22 | 21 | 20 | 19 | 18 | 17 | 16   |

| WPKEY |    |    |    |    |    |    |      |

| 15    | 14 | 13 | 12 | 11 | 10 | 9  | 8    |

| WPKEY |    |    |    |    |    |    |      |

| 7     | 6  | 5  | 4  | 3  | 2  | 1  | 0    |

| _     | _  | _  | _  | _  | -  | _  | WPEN |

### • WPEN: Write Protection Enable

0: Disables the write protection if WPKEY corresponds to 0x414343 ("ACC" in ASCII).

1: Enables the write protection if WPKEY corresponds to 0x414343 ("ACC" in ASCII).

See "Register Write Protection" on page 1071 for the list of registers that can be write-protected.

### • WPKEY: Write Protection Key

| Value    | Name   | Description                                                                       |

|----------|--------|-----------------------------------------------------------------------------------|

| 0x414343 | PASSWD | Writing any other value in this field aborts the write operation of the WPEN bit. |

|          |        | Always reads as 0.                                                                |

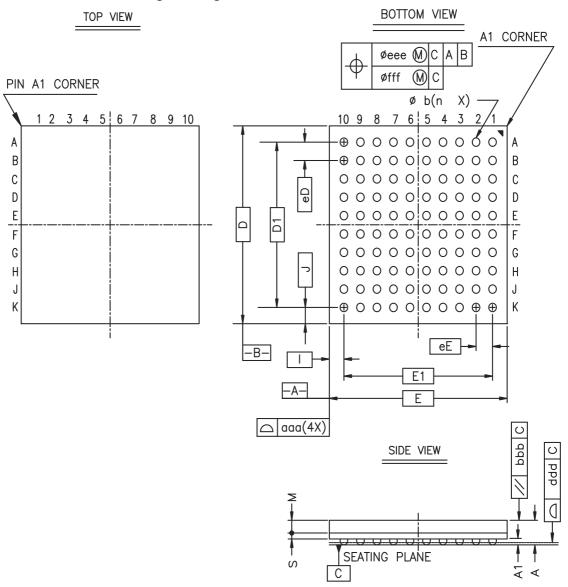

# 45.3 100-ball VFBGA Mechanical Characteristics

Figure 45-3. 100-ball VFBGA Package Drawing

Table 45-8. VFBGA Package Dimensions

|                      |   | Symbol | Common Dimensions (mm)                                             |

|----------------------|---|--------|--------------------------------------------------------------------|

| Package:             |   |        | VFBGA                                                              |

| D- 4: 0'             | Х | Е      | 7.000 ± 0.100                                                      |

| Body Size:           | Y | D      | VFBGA 7.000 ± 0.100 7.000 ± 0.100 0.650 0.650 1.000 max 0.450 ref. |

| Dall Ditala          | X | eE     | 0.650                                                              |

| Ball Pitch:          | Y | eD     | 0.650                                                              |

| Total Thickness:     |   | А      | 1.000 max                                                          |

| Mold Thickness:      |   | М      | 0.450 ref.                                                         |

| Substrate Thickness: |   | S      | 0.210 ref.                                                         |

Table 49-3. SAM4S Datasheet Rev. 11100l Revision History (Continued)

| Doc. Date | Changes                                                                                                                                                                                                                                     |  |  |  |  |  |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|           | Section 41., "Analog Comparator Controller (ACC)"                                                                                                                                                                                           |  |  |  |  |  |

|           | Added Table 41-1 "List of External Analog Data Inputs"                                                                                                                                                                                      |  |  |  |  |  |

|           | Changed all occurrences of 'MCK' to 'peripheral clock'.                                                                                                                                                                                     |  |  |  |  |  |

|           | Updated Table 41-2 "ACC Pin List"                                                                                                                                                                                                           |  |  |  |  |  |

|           | Updated Figure 41-1, "Analog Comparator Controller Block Diagram"                                                                                                                                                                           |  |  |  |  |  |

|           | Section 41.7.2, "ACC Mode Register": replaced two instances of "CF" with "CE" in SELFS bit description                                                                                                                                      |  |  |  |  |  |

|           | Section 41.7.6, "ACC Interrupt Status Register": added (cleared on read) to CE bit description                                                                                                                                              |  |  |  |  |  |

|           | Section 42., "Analog-to-Digital Converter (ADC)"                                                                                                                                                                                            |  |  |  |  |  |

|           | Corrected ADC_SR to ADC_ISR in Section 42.6.5, "Conversion Results".                                                                                                                                                                        |  |  |  |  |  |

|           | Figure 42-1 "Analog-to-Digital Converter Block Diagram": Added bus clock and added ADCClock output from Control Logic block                                                                                                                 |  |  |  |  |  |

|           | Revised Section 42.6.1, "Analog-to-Digital Conversion"                                                                                                                                                                                      |  |  |  |  |  |

|           | Added Section 42.6.2, "ADC Clock"                                                                                                                                                                                                           |  |  |  |  |  |

|           | Section 42.6.3, "ADC Reference Voltage": changed title (was "Conversion Reference")                                                                                                                                                         |  |  |  |  |  |

|           | Modified Figure 42-4 "EOCx and DRDY Flag Behavior" and Figure 42-5 "EOCx, OVREx and GOVREx Flag Behavior"                                                                                                                                   |  |  |  |  |  |

|           | Modified warning below Figure 42-5 "EOCx, OVREx and GOVREx Flag Behavior".                                                                                                                                                                  |  |  |  |  |  |

|           | Section 42.6.8, "Comparison Window": Removed paragraph on LOWRES bit use.                                                                                                                                                                   |  |  |  |  |  |

|           | Updated Section 42.6.9, "Differential Inputs"                                                                                                                                                                                               |  |  |  |  |  |

| 03-Apr-15 | Modified Table 42-5 "Gain of the Sample and Hold Unit" and Table 42-6 "Offset of the Sample and Hold Unit".                                                                                                                                 |  |  |  |  |  |

|           | Section 42.6.10, "Input Gain and Offset": all references to "OFFSET" bit changed to OFFx.                                                                                                                                                   |  |  |  |  |  |

|           | Added Figure 42-8 "Buffer Structure".                                                                                                                                                                                                       |  |  |  |  |  |

|           | Modified Section 42.7.2, "ADC Mode Register", Section 42.7.6, "ADC Channel Disable Register", Section 42.7.12, "ADC Interrupt Status Register", Section 42.7.14, "ADC Extended Mode Register", Section 42.7.16, "ADC Channel Gain Register" |  |  |  |  |  |

|           | Replaced references to vrefin by V <sub>ADVREF</sub> in text and figures.                                                                                                                                                                   |  |  |  |  |  |

|           | Section 42.6.12 "Automatic Calibration": Removed sentence on ADC running mode.                                                                                                                                                              |  |  |  |  |  |

|           | Replaced instances of "ADCClock" with "ADC clock" or acronym "ADCCLK" throughout                                                                                                                                                            |  |  |  |  |  |

|           | Section 43., "Digital-to-Analog Converter Controller (DACC)"                                                                                                                                                                                |  |  |  |  |  |

|           | MCK replaced with Peripheral clock                                                                                                                                                                                                          |  |  |  |  |  |

|           | Updated Section 43.2, "Embedded Characteristics"                                                                                                                                                                                            |  |  |  |  |  |

|           | Updated Figure 43-1 "DACC Block Diagram"                                                                                                                                                                                                    |  |  |  |  |  |

|           | Section 43.6.6, "DACC Timings": replaced two instances of "DACC clock periods" with "peripheral clock periods"                                                                                                                              |  |  |  |  |  |

|           | Table 43-3 "Register Mapping":                                                                                                                                                                                                              |  |  |  |  |  |

|           | - Removed reset value from write-only register DACC_CDR                                                                                                                                                                                     |  |  |  |  |  |

|           | - Displayed offset ranges 0x34–0x90 and 0x98–0xE0 as "Reserved"                                                                                                                                                                             |  |  |  |  |  |

|           | Modified Section 43.7.2, "DACC Mode Register"                                                                                                                                                                                               |  |  |  |  |  |

|           | Removed references to Sleep mode and refresh period                                                                                                                                                                                         |  |  |  |  |  |

|     | 25.7  | Register Write Protection                      | 434         |

|-----|-------|------------------------------------------------|-------------|

|     | 25.8  | Bus Matrix (MATRIX) (MATRIX) User Interface    | 435         |

| 26. | Stati | c Memory Controller (SMC)                      | 443         |

|     | 26.1  | Description                                    |             |

|     | 26.2  | Embedded Characteristics                       |             |

|     | 26.3  | I/O Lines Description                          | 444         |

|     | 26.4  | Product Dependencies                           | 444         |

|     | 26.5  | Multiplexed Signals                            |             |

|     | 26.6  | External Memory Mapping                        |             |

|     | 26.7  | Connection to External Devices                 |             |

|     | 26.8  | Application Example                            |             |

|     | 26.9  | Standard Read and Write Protocols              |             |

|     | 26.10 | Scrambling/Unscrambling Function               |             |

|     |       | Automatic Wait States                          |             |

|     |       | Data Float Wait States                         |             |

|     |       | External Wait                                  |             |

|     |       | Slow Clock Mode.                               |             |

|     |       | Asynchronous Page Mode                         |             |

|     |       | Static Memory Controller (SMC) User Interface  |             |

|     |       |                                                |             |

| 27. | Perip | pheral DMA Controller (PDC)                    |             |

|     | 27.1  | Description                                    |             |

|     | 27.2  | Embedded Characteristics                       |             |

|     | 27.3  | Peripheral DMA Controller Connections          |             |

|     | 27.4  | Block Diagram                                  |             |

|     | 27.5  | Functional Description                         |             |

|     | 27.6  | Peripheral DMA Controller (PDC) User Interface | 495         |

| 28. | Cloc  | k Generator                                    | 506         |

|     | 28.1  | Description                                    | 506         |

|     | 28.2  | Embedded Characteristics                       | 506         |

|     | 28.3  | Block Diagram                                  | 507         |

|     | 28.4  | Slow Clock                                     | 508         |

|     | 28.5  | Main Clock                                     | 509         |

|     | 28.6  | Divider and PLL Block                          | 513         |

| 20  | Pow   | er Management Controller (PMC)                 | <b>51 6</b> |

| 29. | 29.1  | Description                                    |             |

|     | 29.2  | Embedded Characteristics                       |             |

|     | 29.3  | Block Diagram                                  |             |

|     | 29.4  | Master Clock Controller.                       |             |

|     | 29.5  | Processor Clock Controller                     |             |

|     | 29.6  | SysTick Clock                                  |             |

|     | 29.6  | USB Clock Controller                           |             |

|     |       |                                                |             |

|     | 29.8  | Peripheral Clock Controller                    |             |

|     | 29.9  | Free-Running Processor Clock                   |             |

|     |       | Programmable Clock Output Controller           |             |

|     |       | Fast Startup.                                  |             |

|     |       | Startup from Embedded Flash                    |             |

|     |       | Main Clock Failure Detector                    |             |

|     | 29.14 | Programming Sequence                           | 522         |