Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                               |

|----------------------------|------------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                                   |

| Speed                      | 180MHz                                                                                               |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, Microwire, MMC/SD, SPI, SSI, SSP, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, WDT                                              |

| Number of I/O              | 83                                                                                                   |

| Program Memory Size        | 1MB (1M × 8)                                                                                         |

| Program Memory Type        | FLASH                                                                                                |

| EEPROM Size                | -                                                                                                    |

| RAM Size                   | 136K x 8                                                                                             |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                                          |

| Data Converters            | A/D 8x10b; D/A 1x10b                                                                                 |

| Oscillator Type            | Internal                                                                                             |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                                   |

| Mounting Type              | Surface Mount                                                                                        |

| Package / Case             | 144-LQFP                                                                                             |

| Supplier Device Package    | 144-LQFP (20x20)                                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc18s37jbd144e                              |

|                            |                                                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Chapter 3: LPC18xx One-Time Programmable (OTP) memory and API

# 3.3 General description

The OTP memory contains four memory banks of 128 bits each. The first memory bank (OTP bank 0) is reserved. The other three OTP banks are programmable. In non-secure parts, OTP banks 1 and 2 are available for general-purpose data. In secure parts, OTP banks 1 and 2 are used for AES keys. OTP bank 3 contains up to two user programmable configuration words and two more words for general-purpose use.

The virgin OTP state is all zeros. A zero value can be overwritten by a one, but a one in any of the OTP bits cannot be changed.

Programming the OTP requires a higher voltage than reading. The read voltage is generated internally. The programming voltage is supplied via pin VPP. The OTP controller automatically selects the correct voltage. If the VPP pin is not connected, then the OTP cannot be programmed. An API is provided to program data into the OTP.

The AES keys in the OTP memory used by secure parts are not readable by software.

Table 8. OTP content for secure and non-secure parts

|             | Secure device                                             | es        |                 |                                                     | Non-secure d                          | Non-secure devices |                 |                 |  |  |

|-------------|-----------------------------------------------------------|-----------|-----------------|-----------------------------------------------------|---------------------------------------|--------------------|-----------------|-----------------|--|--|

| OTP<br>bank | Content                                                   | Encrypted | Software access | ΑΡΙ                                                 | Content                               | Encrypted          | Software access | ΑΡΙ             |  |  |

| 0           | Reserved                                                  | -         | -               | -                                                   | -                                     | -                  | -               | -               |  |  |

| 1           | AES key 1 for secure boot image                           | yes       | no              | aes_ProgramKey1                                     | User-defined;<br>general<br>purpose 0 | no                 | yes             | otp_ProgGP0     |  |  |

| 2           | AES key 2 for<br>data                                     | no        | no              | aes_ProgramKey2                                     | User-defined;<br>general<br>purpose 1 | no                 | yes             | otp_ProgGP1     |  |  |

| 3           | Word 0:<br>Customer<br>control data                       | no        | yes             | otp_ProgBootSrc,<br>otp_ProgJTAGDis                 | Word 0:<br>Customer<br>control data   | no                 | yes             | otp_ProgBootSrc |  |  |

| 3           | Word 1;<br>general<br>purpose word<br>0 or USB ID         | no        | yes             | otp_ProgGP2 or<br>otp_ProgGP2_0 or<br>otp_ProgUSBID | Same as for secure devices            |                    |                 |                 |  |  |

| 3           | Words 2 to 3:<br>General<br>purpose data<br>in words 1/2. | no        | yes             | otp_ProgGP2 or<br>otp_ProgGP2_1,<br>otp_ProgGP2_2   | Same as for s                         | ecure device       | S               |                 |  |  |

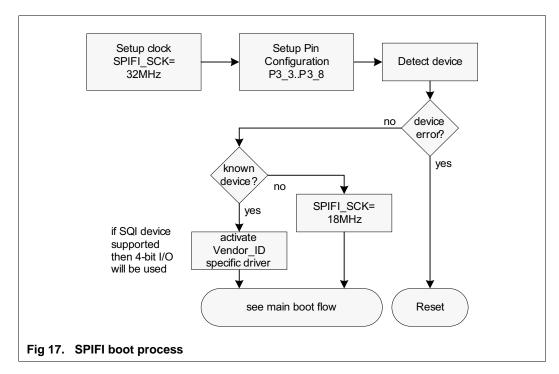

checks for the type of SPI flash device. For an SPI flash, the part boots with a 18 MHz clock. For a quad SPI flash device, the part boots with a 32 MHz clock. If the detected device is unknown, the SPIFI clock is reduced to 18 MHz.

If no header is present, it is assumed that the image is located on address 0x80000000 and is executed from there.

#### 4.3.6.4.1 Supported QSPI devices

Multiple QSPI devices from various vendors can be used with the SPIFI interface and the SPIFI API available on nxp.com.

LPC18xx devices support boot from flash. The boot code sets the SPIFI clock to 32 MHz at the beginning of the boot process and checks for the type of SPI flash device. If the detected device is not recognized by LPC18xx, the SPIFI clock is reduced to 18 MHz.

The devices listed in <u>Table 19</u> are tested to work as boot devices for the LPC18xx and with the SPIFI API.

Remark: All QSPI devices have been tested at an operating voltage of 3.3 V.

#### Chapter 9: LPC18xx Event router

| Bit   | Symbol     | Value | Description                                                                                                                         | Rese<br>value |

|-------|------------|-------|-------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 13    | TIM2_L     |       | Level detect mode for combined timer output 2 event.                                                                                | 0             |

|       |            | 0     | Detect LOW level GIMA output 25 if bit 13 in the EDGE register is 0. Detect falling edge if bit 13 in the EDGE register is 1.       | -             |

|       |            | 1     | Detect HIGH level GIMA output 25 if bit 13 in the EDGE register is 0. Detect rising edge if bit 13 in the EDGE register is 1.       |               |

| 14    | TIM6_L     |       | Level detect mode for combined timer output 6 event.                                                                                | 0             |

|       |            | 0     | Detect LOW level of GIMA output 26 if bit 14 in the EDGE register is 0. Detect falling edge if bit 14 in the EDGE register is 1.    |               |

|       |            | 1     | Detect HIGH level of GIMA output 26 if bit 14 in the EDGE register is 0. Detect rising edge if bit 14 in the EDGE register is 1.    |               |

| 15    | QEI_L      |       | Level detect mode for QEI event.                                                                                                    | 0             |

|       |            | 0     | Detect LOW level of the QEI interrupt if bit 15 in the EDGE register is 0. Detect falling edge if bit 15 in the EDGE register is 1. |               |

|       |            | 1     | Detect HIGH level of the QEI interrupt if bit 15 in the EDGE register is 0. Detect rising edge if bit 15 in the EDGE register is 1. | _             |

| 16    | TIM14_L    |       | Level detect mode for combined timer output 14 event.                                                                               | 0             |

|       |            | 0     | Detect LOW level of GIMA output 27 if bit 16 in the EDGE register is 0. Detect falling edge if bit 16 in the EDGE register is 1.    |               |

|       |            | 1     | Detect HIGH level of GIMA output 27 if bit 16 in the EDGE register is 0. Detect rising edge if bit 16 in the EDGE register is 1.    |               |

| 18:17 | -          | -     | Reserved.                                                                                                                           |               |

| 19    | RESET_L    |       | Level detect mode for Reset                                                                                                         | 0             |

|       |            | 0     | Detect LOW level if bit 19 in the EDGE register is 0.<br>Detect falling edge if bit 19 in the EDGE register is 1.                   | _             |

|       |            | 1     | Detect HIGH level if bit 19 in the EDGE register is 0.<br>Detect rising edge if bit 19 in the EDGE register is 1.                   |               |

| 20    | BODRESET_L |       | Level detect mode for BOD Reset                                                                                                     | 0             |

|       |            | 0     | Detect LOW level if bit 20 in the EDGE register is 0.<br>Detect falling edge if bit 20 in the EDGE register is 1.                   | _             |

|       |            | 1     | Detect HIGH level if bit 20 in the EDGE register is 0.<br>Detect rising edge if bit 20 in the EDGE register is 1.                   |               |

| 21    | DPDRESET_L |       | Level detect mode for Deep power-down Reset                                                                                         | 0             |

|       |            | 0     | Detect LOW level if bit 21 in the EDGE register is 0.<br>Detect falling edge if bit 21 in the EDGE register is 1.                   | _             |

|       |            | 1     | Detect HIGH level if bit 21 in the EDGE register is 0.<br>Detect rising edge if bit 21 in the EDGE register is 1.                   |               |

| 31:22 |            | _     | Reserved.                                                                                                                           |               |

#### Table 77. Level configuration register (HILO - address 0x4004 4000) bit description

# Chapter 14: LPC18xx Reset Generation Unit (RGU)

#### 0x4005 3104) bit description 1 /DESET CTRI 1 addr . . Table 157. Reset co

...continued

| ontrol register | 1 (RESET_ | _CTRL1, | address | 0x4005 | 3104) I | bit descri | ption |

|-----------------|-----------|---------|---------|--------|---------|------------|-------|

|                 |           |         |         |        |         |            |       |

|     | conunued       |                                                                                                  |                |        |

|-----|----------------|--------------------------------------------------------------------------------------------------|----------------|--------|

| Bit | Symbol         | Description                                                                                      | Reset<br>value | Access |

| 6   | MOTOCONPWM_RST | Writing a one activates the reset. This bit is automatically cleared to 0 after one clock cycle. | 0              | W      |

| 7   | QEI_RST        | Writing a one activates the reset. This bit is automatically cleared to 0 after one clock cycle. | 0              | W      |

| 8   | ADC0_RST       | Writing a one activates the reset. This bit is automatically cleared to 0 after one clock cycle. | 0              | W      |

| 9   | ADC1_RST       | Writing a one activates the reset. This bit is automatically cleared to 0 after one clock cycle. | 0              | W      |

| 10  | DAC_RST        | Writing a one activates the reset. This bit is automatically cleared to 0 after one clock cycle. | 0              | W      |

| 11  | -              | Reserved                                                                                         | -              | -      |

| 12  | UART0_RST      | Writing a one activates the reset. This bit is automatically cleared to 0 after one clock cycle. | 0              | W      |

| 13  | UART1_RST      | Writing a one activates the reset. This bit is automatically cleared to 0 after one clock cycle. | 0              | W      |

| 14  | UART2_RST      | Writing a one activates the reset. This bit is automatically cleared to 0 after one clock cycle. | 0              | W      |

| 15  | UART3_RST      | Writing a one activates the reset. This bit is automatically cleared to 0 after one clock cycle. | 0              | W      |

| 16  | I2C0_RST       | Writing a one activates the reset. This bit is automatically cleared to 0 after one clock cycle. | 0              | W      |

| 17  | I2C1_RST       | Writing a one activates the reset. This bit is automatically cleared to 0 after one clock cycle. | 0              | W      |

| 18  | SSP0_RST       | Writing a one activates the reset. This bit is automatically cleared to 0 after one clock cycle. | 0              | W      |

| 19  | SSP1_RST       | Writing a one activates the reset. This bit is automatically cleared to 0 after one clock cycle. | 0              | W      |

| 20  | I2S_RST        | Writing a one activates the reset. This bit is automatically cleared to 0 after one clock cycle. | 0              | W      |

| 21  | SPIFI_RST      | Writing a one activates the reset. This bit is automatically cleared to 0 after one clock cycle. | 0              | W      |

| 22  | CAN1_RST       | Writing a one activates the reset. This bit is automatically cleared to 0 after one clock cycle. | 0              | W      |

| 23  | CAN0_RST       | Writing a one activates the reset. This bit is automatically cleared to 0 after one clock cycle. | 0              | W      |

| 24  | -              | Reserved                                                                                         | -              | -      |

| 25  | -              | Reserved                                                                                         | -              | -      |

| 26  | -              | Reserved                                                                                         | -              | -      |

| 27  | -              | Reserved                                                                                         | -              | -      |

| 28  | -              | Reserved                                                                                         | -              | -      |

| 29  | -              | Reserved                                                                                         | -              | -      |

| 30  | -              | Reserved                                                                                         | -              | -      |

| 31  | -              | Reserved                                                                                         | -              | -      |

|     |                |                                                                                                  |                |        |

| Pin name | LBGA256 | TFBGA100 | LQFP144 | LQFP208 |     | Reset state<br>[1] | Type | Description                                                                                                                                                                                                                                                                                            |

|----------|---------|----------|---------|---------|-----|--------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P9_3     | M6      | -        | -       | 79      | [2] | N;                 | I/O  | GPIO4[15] — General purpose digital input/output pin.                                                                                                                                                                                                                                                  |

|          |         |          |         |         |     | PU                 | 0    | MCOA0 — Motor control PWM channel 0, output A.                                                                                                                                                                                                                                                         |

|          |         |          |         |         |     |                    | 0    | USB1_IND1 — USB1 Port indicator LED control output 1.                                                                                                                                                                                                                                                  |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                                                                                                                                                 |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                                                                                                                                                 |

|          |         |          |         |         |     |                    | Ι    | ENET_RXD2 — Ethernet receive data 2 (MII interface).                                                                                                                                                                                                                                                   |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                                                                                                                                                 |

|          |         |          |         |         |     |                    | 0    | <b>U3_TXD</b> — Transmitter output for USART3.                                                                                                                                                                                                                                                         |

| P9_4     | N10     | -        | -       | 92      | [2] | N;                 | -    | R — Function reserved.                                                                                                                                                                                                                                                                                 |

| -        |         |          |         |         |     | PU                 | 0    | MCOB0 — Motor control PWM channel 0, output B.                                                                                                                                                                                                                                                         |

|          |         |          |         |         |     |                    | 0    | USB1_IND0 — USB1 Port indicator LED control output 0.                                                                                                                                                                                                                                                  |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                                                                                                                                                 |

|          |         |          |         |         |     |                    | I/O  | GPIO5[17] — General purpose digital input/output pin.                                                                                                                                                                                                                                                  |

|          |         |          |         |         |     |                    | 0    | <b>ENET_TXD2</b> — Ethernet transmit data 2 (MII interface).                                                                                                                                                                                                                                           |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                                                                                                                                                 |

|          |         |          |         |         |     |                    | Ι    | <b>U3_RXD</b> — Receiver input for USART3.                                                                                                                                                                                                                                                             |

| P9_5     | M9      | -        | 69      | 9 98    | [2] | N;                 | -    | R — Function reserved.                                                                                                                                                                                                                                                                                 |

|          |         |          |         |         |     | PU                 | 0    | MCOA1 — Motor control PWM channel 1, output A.                                                                                                                                                                                                                                                         |

|          |         |          |         |         |     |                    | 0    | <b>USB1_PPWR</b> — VBUS drive signal (towards external charge pump or power management unit); indicates that VBUS must be driven (active HIGH). Add a pull-down resistor to disable the power switch at reset. This signal has opposite polarity compared to the USB_PPWR used on other NXP LPC parts. |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                                                                                                                                                 |

|          |         |          |         |         |     |                    | I/O  | GPIO5[18] — General purpose digital input/output pin.                                                                                                                                                                                                                                                  |

|          |         |          |         |         |     |                    | 0    | ENET_TXD3 — Ethernet transmit data 3 (MII interface).                                                                                                                                                                                                                                                  |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                                                                                                                                                 |

|          |         |          |         |         |     |                    | 0    | U0_TXD — Transmitter output for USART0.                                                                                                                                                                                                                                                                |

| P9_6     | L11     | -        | 72      | 103     | [2] | N;                 | I/O  | GPIO4[11] — General purpose digital input/output pin.                                                                                                                                                                                                                                                  |

|          |         |          |         |         |     | PU                 | 0    | MCOB1 — Motor control PWM channel 1, output B.                                                                                                                                                                                                                                                         |

|          |         |          |         |         |     |                    | I    | <b>USB1_PWR_FAULT</b> — USB1 Port power fault signal indicating over-current condition; this signal monitors over-current on the USB1 bus (external circuitry required to detect over-current condition).                                                                                              |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                                                                                                                                                 |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                                                                                                                                                 |

|          |         |          |         |         |     |                    | I    | ENET_COL — Ethernet Collision detect (MII interface).                                                                                                                                                                                                                                                  |

|          |         |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                                                                                                                                                 |

|          |         |          |         |         |     |                    | 1    | IIO RYD - Receiver input for LISARTO                                                                                                                                                                                                                                                                   |

I **U0\_RXD** — Receiver input for USART0.

User manual

Chapter 15: LPC18xx Pin configuration

#### Chapter 19: LPC18xx General Purpose DMA (GPDMA) controller

### 19.8.1.4 Disabling a DMA channel

A DMA channel can be disabled in three ways:

- By writing directly to the channel enable bit. Any outstanding data in the FIFO's is lost if this method is used.

- By using the active and halt bits in conjunction with the channel enable bit.

- By waiting until the transfer completes. This automatically clears the channel.

#### Disabling a DMA channel and losing data in the FIFO

Clear the relevant channel enable bit in the relevant channel configuration register. The current AHB transfer (if one is in progress) completes and the channel is disabled. Any data in the FIFO is lost.

#### Disabling the DMA channel without losing data in the FIFO

- Set the halt bit in the relevant channel configuration register. This causes any future DMA request to be ignored.

- Poll the active bit in the relevant channel configuration register until it reaches 0. This bit indicates whether there is any data in the channel that has to be transferred.

- Clear the channel enable bit in the relevant channel configuration register

#### 19.8.1.5 Setting up a new DMA transfer

To set up a new DMA transfer:

If the channel is not set aside for the DMA transaction:

- 1. Read the ENBLDCHNS controller register and find out which channels are inactive.

- 2. Choose an inactive channel that has the required priority.

- 3. Program the DMA controller

#### 19.8.1.6 Halting a DMA channel

Set the halt bit in the relevant DMA channel configuration register. The current source request is serviced. Any further source DMA request is ignored until the halt bit is cleared.

### 19.8.1.7 Programming a DMA channel

- 1. Choose a free DMA channel with the priority needed. DMA channel 0 has the highest priority and DMA channel 7 the lowest priority.

- Clear any pending interrupts on the channel to be used by writing to the IntTCClear and INTERRCLEAR register. The previous channel operation might have left interrupt active.

- 3. Write the source address into the CSRCADDR register.

- 4. Write the destination address into the CDESTADDR register.

- 5. Write the address of the next LLI into the CLLI register. If the transfer comprises of a single packet of data then 0 must be written into this register.

- 6. Write the control information into the CCONTROL register.

- 7. Write the channel configuration information into the CCONFIG register. If the enable bit is set then the DMA channel is automatically enabled.

#### Chapter 22: LPC18xx External Memory Controller (EMC)

Program the SDRAM Delay value for the EMC\_CLKn lines in the EMCDELAYCLK register in the SCU block. (See <u>Section 16.4.9</u>.) Add the SDRAM delay for most SDRAM devices running at frequencies above 96 MHz under typical conditions. Add the SDRAM delay at any frequency to compensate for variations over temperature. For details, see the LPC1850\_30\_20\_10 data sheet.

#### Table 344. EMC clocking and power control

|                                               | Base clock  | Branch clock   | Operating<br>frequency | Notes                                                                                                                                                             |

|-----------------------------------------------|-------------|----------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EMC registers<br>and EMC<br>clock<br>EMC_CCLK | BASE_M3_CLK | CLK_M3_EMC     | up to<br>180 MHz       | The maximum operating frequency depends on temperature and voltage settings and is typically 120 MHz for SDRAM devices. For details, see the LPC18xx data sheets. |

| EMC clock<br>EMC_CCLK<br>(divided clock)      | BASE_M3_CLK | CLK_M3_EMC_DIV | up to<br>180 MHz       | This is an alternative clock option for EMC_CCLK.<br>This clock can run at the same frequency as<br>BASE_M3_CLK or at half the frequency of<br>BASE_M3_CLK.       |

# 22.3 Features

- 8-bit, 16-bit, and 32-bit wide static memory support with up to four chip selects.

- Asynchronous static memory device support including RAM, ROM, and NOR Flash, with or without asynchronous page mode.

- Static memory features include:

- Asynchronous page mode read

- Programmable wait states

- Bus turnaround delay

- Output enable and write enable delays

- Extended wait

- 16-bit and 32-bit wide chip select SDRAM memory support with up to four chip selects and up to 256 MB of data.

- Controller supports 2 kbit, 4 kbit, and 8 kbit row address synchronous memory parts. That is typical 512 MB, 256 MB, and 128 MB parts, with 4, 8, 16, or 32 data bits per device.

- Dynamic memory interface support including Single Data Rate SDRAM. SDRAM maximum frequency of up to 120 MHz.

- Dynamic memory self-refresh mode controlled by software.

- Power-saving modes dynamically control EMC\_CKEOUT and EMC\_CLK to SDRAMs.

- Low transaction latency.

- Read and write buffers to reduce latency and to improve performance.

- Separate reset domains allow the for auto-refresh through a chip reset if desired.

- Programmable delay elements allow to fine-tune the EMC timing.

|      | addi   | ress 0x4000 5040) bit description                                                                                                      |                |

|------|--------|----------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Bit  | Symbol | Description                                                                                                                            | Reset<br>value |

| 3:0  | TDAL   | Data-in to active command.<br>0x0 - 0xE = n clock cycles. The delay is in EMC_CCLK cycles.<br>0xF = 15 clock cycles (POR reset value). | 0xF            |

| 31:4 | -      | Reserved, user software should not write ones to reserved bits. The value read from a reserved bit is not defined.                     | -              |

# Table 358. Dynamic Memory Data In to Active Command Time register (DYNAMICDAL - address 0x4000 5040) bit description

# 22.6.12 Dynamic Memory Write Recovery Time register

This register enables you to program the write recovery time, tWR. It is recommended that this register is modified during system initialization, or when there are no current or outstanding transactions. This can be ensured by waiting until the EMC is idle, and then entering low-power, or disabled mode. This value is normally found in SDRAM data sheets as tWR, tDPL, tRWL, or tRDL. This register is accessed with one wait state.

Note: This register is used for all four dynamic memory chip selects. Therefore the worst case value for all of the chip selects must be programmed.

|      | 0,40   |                                                                                                                                      |                |

|------|--------|--------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Bit  | Symbol | Description                                                                                                                          | Reset<br>value |

| 3:0  | TWR    | Write recovery time.<br>0x0 - 0xE = n + 1 clock cycles. The delay is in EMC_CCLK cycles.<br>0xF = 16 clock cycles (POR reset value). | 0xF            |

| 31:4 | -      | Reserved, user software should not write ones to reserved bits. The value read from a reserved bit is not defined.                   | -              |

Table 359. Dynamic Memory Write Recovery Time register (DYNAMICWR - address 0x4000 5044) bit description

# 22.6.13 Dynamic Memory Active to Active Command Period register

This register enables you to program the active to active command period, tRC. It is recommended that this register is modified during system initialization, or when there are no current or outstanding transactions. This can be ensured by waiting until the EMC is idle, and then entering low-power, or disabled mode. This value is normally found in SDRAM data sheets as tRC. This register is accessed with one wait state.

Note: This register is used for all four dynamic memory chip selects. Therefore the worst case value for all of the chip selects must be programmed.

Table 360. Dynamic Memory Active to Active Command Period register (DYNAMICRC - address 0x4000 5048) bit description

| Bit  | Symbol | Description                                                                                                                                        | Reset<br>value |

|------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 4:0  | TRC    | Active to active command period.<br>0x0 - 0x1E = n + 1 clock cycles. The delay is in EMC_CCLK cycles.<br>0x1F = 32 clock cycles (POR reset value). | 0x1F           |

| 31:5 | -      | Reserved, user software should not write ones to reserved bits. The value read from a reserved bit is not defined.                                 | -              |

#### Chapter 22: LPC18xx External Memory Controller (EMC)

# 22.7.6 External static memory interface

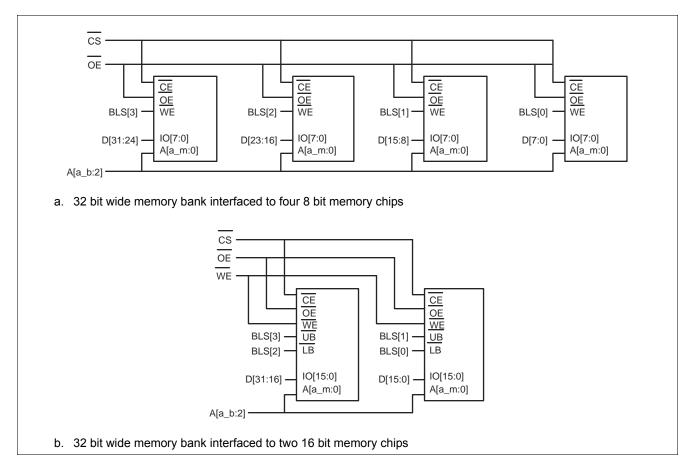

External memory interfacing depends on the bank width (32, 16 or 8 bit selected via MW bits in corresponding StaticConfig register).

If a memory bank is configured to be 32 bits wide, address lines A0 and A1 can be used as non-address lines. If a memory bank is configured to 16 bits wide, A0 is not required. However, 8 bit wide memory banks do require all address lines down to A0. Configuring A1 and/or A0 lines to provide address or non-address function is accomplished using the SYSCON registers.

Symbol a\_b in the following figures refers to the highest order address line in the data bus. Symbol a\_m refers to the highest order address line of the memory chip used in the external memory interface.

If the external memory is used as external boot memory for flashless devices, refer to <u>Section 4.2</u> on how to connect the EMC. The memory bank width for memory banks one and two is determined by the setting of the BOOT pins.

#### Chapter 23: LPC18xx USB0 Host/Device/OTG controller

| Bit   | Symbol | Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Access | Reset<br>value |

|-------|--------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 13    | SUTW   |       | Setup trip wire<br>During handling a setup packet, this bit is used as a semaphore to ensure<br>that the setup data payload of 8 bytes is extracted from a QH by the DCD<br>without being corrupted. If the setup lockout mode is off (see USBMODE<br>register) then there exists a hazard when new setup data arrives while the<br>DCD is copying the setup data payload from the QH for a previous setup<br>packet. This bit is set and cleared by software and will be cleared by | R/W    | 0              |

| 14    | ATDTW  |       | hardware when a hazard exists. (See <u>Section 23.10</u> ).<br>Add dTD trip wire                                                                                                                                                                                                                                                                                                                                                                                                     | R/W    | 0              |

|       |        |       | This bit is used as a semaphore to ensure the to proper addition of a new dTD to an active (primed) endpoint's linked list. This bit is set and cleared by software during the process of adding a new dTD. See also <u>Section 23.10</u> .                                                                                                                                                                                                                                          |        | ·              |

|       |        |       | This bit shall also be cleared by hardware when its state machine is hazard region for which adding a dTD to a primed endpoint may go unrecognized.                                                                                                                                                                                                                                                                                                                                  |        |                |

| 15    | -      |       | Not used in device mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -      | -              |

| 23:16 | ITC    |       | Interrupt threshold control.                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W    | 0x8            |

|       |        |       | The system software uses this field to set the maximum rate at which the host/device controller will issue interrupts. ITC contains the maximum interrupt interval measured in micro-frames. Valid values are shown below. All other values are reserved.<br>0x0 = Immediate (no threshold)<br>0x1 = 1 micro frame.                                                                                                                                                                  |        |                |

|       |        |       | 0x2 = 2 micro frames.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |                |

|       |        |       | 0x8 = 8 micro frames.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |                |

|       |        |       | 0x10 = 16 micro frames.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |                |

|       |        |       | 0x20 = 32 micro frames.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |                |

|       |        |       | 0x40 = 64 micro frames.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |                |

| 31:24 | -      |       | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        | 0              |

# 23.6.3.2 Host mode

Table 391. USB Command register in host mode (USBCMD\_H - address 0x4000 6140) bit description - host mode

| Bit | Symbol | Value                                                                                                                                                                                                                                                                                                                                                                                                      | Description                                                                                                                                                    | Access | Reset<br>value |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 0   | RS     |                                                                                                                                                                                                                                                                                                                                                                                                            | R/W                                                                                                                                                            | 0      |                |

|     |        | 0 When this bit is set to 0, the Host Controller completes the current transaction on the USB and then halts. The HC Halted bit in the status register indicates when the Host Controller has finished the transaction and has entered the stopped state. Software should not write a one to this field unless the host controller is in the Halted state (i.e. HCHalted in the USBSTS register is a one). |                                                                                                                                                                |        |                |

|     |        | 1                                                                                                                                                                                                                                                                                                                                                                                                          | When set to a 1, the Host Controller proceeds with the execution of the schedule. The Host Controller continues execution as long as this bit is set to a one. |        |                |

- USB descriptors data structure (<u>Table 500 "\_USB\_CORE\_DESCS\_T class</u> <u>structure</u>")

- USB device stack initialization parameter data structure (<u>Table 509</u> <u>"USBD\_API\_INIT\_PARAM class structure</u>").

- USB device stack core API functions structure (<u>Table 512 "USBD\_CORE\_API</u> <u>class structure</u>").

- Device Firmware Upgrade (DFU) class function driver

- DFU descriptors data structure (<u>Table 514 "USBD\_DFU\_INIT\_PARAM class</u> <u>structure</u>").

- DFU class API functions structure. This module exposes functions which interact directly with the USB device controller hardware (<u>Table 513 "USBD\_DFU\_API</u> <u>class structure</u>").

- HID class function driver

- struct (Table 493 "\_HID\_DESCRIPTOR class structure").

- struct (Table 495 "\_HID\_REPORT\_T class structure").

- USB descriptors data structure (<u>Table 516 "USBD\_HID\_INIT\_PARAM class</u> <u>structure</u>").

- HID class API functions structure. This structure contains pointers to all the functions exposed by the HID function driver module (<u>Table 517 "USBD\_HW\_API</u> <u>class structure"</u>).

- USB device controller driver

- Hardware API functions structure. This module exposes functions which interact directly with the USB device controller hardware (<u>Table 517 "USBD\_HW\_API class</u> <u>structure</u>").

- Mass Storage Class (MSC) function driver

- Mass Storage Class function driver initialization parameter data structure (<u>Table 519</u>).

- MSC class API functions structure. This module exposes functions which interact directly with the USB device controller hardware (<u>Table 518</u>).

# 25.4 Calling the USB device driver

A fixed location in ROM contains a pointer to the ROM driver table i.e. 0x1FFF 1FF8. The ROM driver table contains a pointer to the USB driver table. Pointers to the various USB driver functions are stored in this table. USB driver functions can be called by using a C structure. Figure 65 illustrates the pointer mechanism used to access the on-chip USB driver.

typedef struct USBD\_API

{

const USBD\_HW\_API\_T\* hw;

const USBD\_CORE\_API\_T\* core;

const USBD\_MSC\_API\_T\* msc;

UM10430

User manual

| Γ                                     |                                     |                     |          |                     |          |                     |          |                     |

|---------------------------------------|-------------------------------------|---------------------|----------|---------------------|----------|---------------------|----------|---------------------|

| WKUPFMFILTER0                         | Filter 0 Byte Mask                  |                     |          |                     |          |                     |          |                     |

| WKUPFMFILTER1                         | Filter 1 Byte Mask                  |                     |          |                     |          |                     |          |                     |

| WKUPFMFILTER2                         |                                     | Filter 2 Byte Mask  |          |                     |          |                     |          |                     |

| WKUPFMFILTER3                         | Filter 3 Byte Mask                  |                     |          |                     |          |                     |          |                     |

| WKUPFMFILTER4                         | RSVD                                | Filter 3<br>Command | RSVD     | Filter 2<br>Command | RSVD     | Filter 1<br>Command | RSVD     | Filter 0<br>Command |

| WKUPFMFILTER5                         | Filter 3                            | 3 Offset            | Filter 2 | 2 Offset            | Filter 1 | Offset              | Filter ( | 0 Offset            |

| WKUPFMFILTER6                         |                                     | Filter 1 C          | RC - 16  |                     |          | Filter 0 C          | CRC - 16 |                     |

| WKUPFMFILTER7                         | Filter 3 CRC - 16 Filter 2 CRC - 16 |                     |          |                     |          |                     |          |                     |

| Fig 68. Wake-up frame filter register |                                     |                     |          |                     |          |                     |          |                     |

#### Filter i byte mask

This register defines which bytes of the frame are examined by filter i (0, 1, 2, and 3) in order to determine whether or not the frame is a wake-up frame. The MSB (thirty-first bit) must be zero. Bit j [30:0] is the Byte Mask. If bit j (byte number) of the Byte Mask is set, then Filter i Offset + j of the incoming frame is processed by the CRC block; otherwise Filter i Offset + j is ignored.

#### Filter i command

This 4-bit command controls the filter i operation. Bit 3 specifies the address type, defining the pattern's destination address type. When the bit is set, the pattern applies to only multicast frames; when the bit is reset, the pattern applies only to unicast frame. Bit 2 and Bit 1 are reserved. Bit 0 is the enable for filter i; if Bit 0 is not set, filter i is disabled.

#### Filter i offset

This register defines the offset (within the frame) from which filter i examines the frames. This 8-bit pattern offset is the offset for the filter i first byte to be examined. The minimum allowed is 12, which refers to the 13th byte of the frame. The offset value 0 refers to the first byte of the frame.

#### Filter i CRC-16

This register contains the CRC\_16 value calculated from the pattern, as well as the byte mask programmed to the wake-up filter register block.

#### 26.7.2.2 Remote wake-up detection

When the MAC is in sleep mode and the remote wake-up bit is enabled in PMT Control and Status register (0x002C), normal operation is resumed after receiving a remote wake-up frame. The Application writes all eight wake-up filter registers by performing a sequential Write to address (0x0028). The Application enables remote wake-up by writing a 1 to Bit 2 of the PMT Control and Status register.

# UM10430

#### Chapter 31: LPC18xx Motor Control PWM (MOTOCONPWM)

| Bit   | Symbol     | Value | Description                                                  | Reset<br>value |

|-------|------------|-------|--------------------------------------------------------------|----------------|

| 14    | TC2MCI1_RE |       | Counter 2 rising edge mode, channel 1.                       | 0              |

|       |            | 0     | A rising edge on MCI1 does not affect counter 2.             |                |

|       |            | 1     | If MODE2 is 1, counter 2 advances on a rising edge on MCI1.  |                |

| 15    | TC2MCI1_FE |       | Counter 2 falling edge mode, channel 1.                      | 0              |

|       |            | 0     | A falling edge on MCI1 does not affect counter 2.            |                |

|       |            | 1     | If MODE2 is 1, counter 2 advances on a falling edge on MCI1. |                |

| 16    | TC2MCI2_RE |       | Counter 2 rising edge mode, channel 2.                       | 0              |

|       |            | 0     | A rising edge on MCI2 does not affect counter 2.             |                |

|       |            | 1     | If MODE2 is 1, counter 2 advances on a rising edge on MCI2.  |                |

| 17    | TC2MCI2_FE |       | Counter 2 falling edge mode, channel 2.                      | 0              |

|       |            | 0     | A falling edge on MCI2 does not affect counter 2.            |                |

|       |            | 1     | If MODE2 is 1, counter 2 advances on a falling edge on MCI2. |                |

| 28:18 | -          | -     | Reserved.                                                    | -              |

| 29    | CNTR0      |       | Channel 0 counter/timer mode.                                | 0              |

|       |            | 0     | Channel 0 is in timer mode.                                  |                |

|       |            | 1     | Channel 0 is in counter mode.                                |                |

| 30    | CNTR1      |       | Channel 1 counter/timer mode.                                | 0              |

|       |            | 0     | Channel 1 is in timer mode.                                  |                |

|       |            | 1     | Channel 1 is in counter mode.                                |                |

| 31    | CNTR2      |       | Channel 2 counter/timer mode.                                | 0              |

|       |            | 0     | Channel 2 is in timer mode.                                  |                |

|       |            | 1     | Channel 2 is in counter mode.                                |                |

#### Table 739. MCPWM Count Control read address (CNTCON - 0x400A 005C) bit description

# 31.7.10.2 MCPWM Count Control set address

Writing one(s) to this write-only address sets the corresponding bit(s) in CNTCON.

#### Table 740. MCPWM Count Control set address (CNTCON\_SET - 0x400A 0060) bit description

|     |                |                                                                  | -              |

|-----|----------------|------------------------------------------------------------------|----------------|

| Bit | Symbol         | Description                                                      | Reset<br>value |

| 0   | TC0MCI0_RE_SET | Writing a one sets the corresponding bit in the CNTCON register. | -              |

| 1   | TC0MCI0_FE_SET | Writing a one sets the corresponding bit in the CNTCON register. | -              |

| 2   | TC0MCI1_RE_SET | Writing a one sets the corresponding bit in the CNTCON register. | -              |

| 3   | TC0MCI1_FE_SET | Writing a one sets the corresponding bit in the CNTCON register. | -              |

| 4   | TC0MCI2_RE_SET | Writing a one sets the corresponding bit in the CNTCON register. | -              |

| 5   | TC0MCI2_FE_SET | Writing a one sets the corresponding bit in the CNTCON register. | -              |

| 6   | TC1MCI0_RE_SET | Writing a one sets the corresponding bit in the CNTCON register. | -              |

#### Chapter 37: LPC18xx Event monitor/recorder

# 37.7.1 Event Monitor/Recorder Control Register

The Event Monitor/Recorder Control Register allows setup of the Event Monitor/Recorder and individual control over aspects of each channel's operation.

Table 838. Event Monitor/Recorder Control Register (ERCONTROL - address 0x4004 6084) bit description

| Bit   | Symbol       | Value                                                                                                    | Description                                                                                                                                                                                      | Reset<br>value |

|-------|--------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 0     | INTWAKE_EN0  |                                                                                                          | Interrupt and wakeup enable for channel 0.                                                                                                                                                       | 0              |

|       |              | 0                                                                                                        | No interrupt or wakeup will be generated by event channel 0.                                                                                                                                     |                |

|       |              | 1                                                                                                        | An event in channel 0 will trigger an (RTC) interrupt and a wake-up request.                                                                                                                     |                |

| 1     | GPCLEAR_EN0  |                                                                                                          | Enables automatically clearing the RTC general purpose registers when an event occurs on channel 0.                                                                                              | 0              |

|       |              | 0                                                                                                        | Channel 0 has no influence on the general purpose registers.                                                                                                                                     | _              |

|       |              | 1                                                                                                        | An event in channel 0 will clear the general purpose registers asynchronously.                                                                                                                   |                |

| 2     | POL0         |                                                                                                          | Selects the polarity of an event on input pin WAKEUP0.                                                                                                                                           | 0              |

|       |              | 0                                                                                                        | A channel 0 event is defined as a negative edge on WAKEUP0.                                                                                                                                      | _              |

|       |              | 1                                                                                                        | A channel 0 event is defined as a positive edge on WAKEUP0.                                                                                                                                      | _              |

| 3     | EV0_INPUT_EN | not being used for event detection, particularly if the associated pin is be<br>for some other function. |                                                                                                                                                                                                  | 0              |

|       |              | 0                                                                                                        | Event 0 input is disabled and forced high internally.                                                                                                                                            |                |

|       |              | 1                                                                                                        | Event 0 input is enabled.                                                                                                                                                                        |                |

| 9:4   | -            |                                                                                                          | Reserved. Read value is undefined, only zero should be written.                                                                                                                                  | NA             |

| 10    | INTWAKE_EN1  |                                                                                                          | Interrupt and wakeup enable for channel 1.                                                                                                                                                       | 0              |

|       |              | 0                                                                                                        | No interrupt or wakeup will be generated by event channel 1.                                                                                                                                     |                |

|       |              | 1                                                                                                        | An event in channel 1 will trigger an (RTC) interrupt and a wake-up request.                                                                                                                     |                |

| 11    | GPCLEAR_EN1  |                                                                                                          | Enables automatically clearing the RTC general purpose registers when an event occurs on channel 1.                                                                                              | 0              |

|       |              | 0                                                                                                        | Channel 1 has no influence on the general purpose registers.                                                                                                                                     | _              |

|       |              | 1                                                                                                        | A n event in channel 1 will clear the general purpose registers asynchronously.                                                                                                                  |                |

| 12    | POL1         |                                                                                                          | Selects the polarity of an event on input pin WAKEUP1.                                                                                                                                           | 0              |

|       |              | 0                                                                                                        | A channel 1 event is defined as a negative edge on WAKEUP1.                                                                                                                                      |                |

|       |              | 1                                                                                                        | A channel 1 event is defined as a positive edge on WAKEUP1.                                                                                                                                      |                |

| 13    | EV1_INPUT_EN |                                                                                                          | Event enable control for channel 1. Event Inputs should remain DISABLED when<br>not being used for event detection, particularly if the associated pin is being used<br>for some other function. | 0              |

|       |              | 0                                                                                                        | Event 1 input is disabled and forced high internally.                                                                                                                                            |                |

|       |              | 1                                                                                                        | Event 1 input is enabled.                                                                                                                                                                        |                |

| 19:14 | -            |                                                                                                          | Reserved. Read value is undefined, only zero should be written.                                                                                                                                  | NA             |

| 20    | INTWAKE_EN2  |                                                                                                          | Interrupt and wakeup enable for channel 2.                                                                                                                                                       |                |

|       |              | 0                                                                                                        | No interrupt or wakeup will be generated by event channel 2.                                                                                                                                     | _              |

|       |              | 1                                                                                                        | An event in channel 2 will trigger an (RTC) interrupt and a wake-up request.                                                                                                                     |                |

# UM10430

#### Chapter 37: LPC18xx Event monitor/recorder

| Bit   | Symbol       | Value | Description                                                                                                                                                                                                                                                                                         | Reset<br>value |

|-------|--------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 21    | GPCLEAR_EN2  |       | Enables automatically clearing the RTC general purpose registers when an event occurs on channel 2.                                                                                                                                                                                                 | 0              |

|       |              | 0     | Channel 2 has no influence on the general purpose registers.                                                                                                                                                                                                                                        | _              |

|       |              | 1     | An event in channel 2 will clear the general purpose registers asynchronously.                                                                                                                                                                                                                      | _              |

| 22    | POL2         |       | Selects the polarity of an event on input pin WAKEUP2.                                                                                                                                                                                                                                              | 0              |

|       |              | 0     | A channel 2 event is defined as a negative edge on WAKEUP2.                                                                                                                                                                                                                                         | _              |

|       |              | 1     | A channel 2 event is defined as a positive edge on WAKEUP2.                                                                                                                                                                                                                                         | _              |

| 23    | EV2_INPUT_EN |       | Event enable control for channel 2. Event Inputs should remain DISABLED when<br>not being used for event detection, particularly if the associated pin is being used<br>for some other function.                                                                                                    | 0              |

|       |              | 0     | Event 2 input is disabled and forced high internally.                                                                                                                                                                                                                                               | _              |

|       |              | 1     | Event 2 input is enabled.                                                                                                                                                                                                                                                                           |                |

| 29:24 | -            |       | Reserved. Read value is undefined, only zero should be written.                                                                                                                                                                                                                                     | NA             |