# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, UART/USART                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                     |

| Number of I/O              | 11                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                            |

| Supplier Device Package    | ·                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0411hh020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

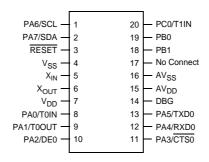

Figure 4. The Z8F0811 and Z8F0411 MCUs in 20-Pin SSOP and PDIP Packages

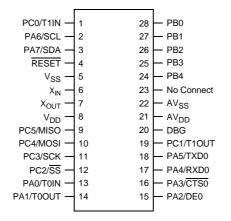

Figure 5. The Z8F0812 and Z8F0412 MCUs in 28-Pin SOIC and PDIP Packages

## Embedded in Life An LIXYS Company 32

## Port A–C Address Registers

The Port A–C Address registers, shown in Table 14, select the GPIO port functionality accessible through the Port A–C Control registers. The Port A–C Address and Control registers combine to provide access to all GPIO port control.

#### Table 14. Port A–C GPIO Address Registers (PxADDR)

| Bit     | 7          | 6 | 5 | 4        | 3        | 2 | 1 | 0 |

|---------|------------|---|---|----------|----------|---|---|---|

| Field   | PADDR[7:0] |   |   |          |          |   |   |   |

| RESET   | 00H        |   |   |          |          |   |   |   |

| R/W     | R/W        |   |   |          |          |   |   |   |

| Address |            |   |   | FD0H, FD | 4H, FD8H |   |   |   |

| Bit            | Description                                                                                                                                                                                                                                                                                                                                                  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]<br>PADDR | Port Address         The Port Address selects one of the subregisters accessible through the Port Control Register.         00H = No function. Provides some protection against accidental port reconfiguration.         01H = Data Direction.         02H = Alternate Function.         03H = Output Control (Open-Drain).         04H = High Drive Enable. |

|                | 05H = Stop Mode Recovery Source Enable.<br>06H = Pull-up Enable.                                                                                                                                                                                                                                                                                             |

|                | 07H–FFH = no function.                                                                                                                                                                                                                                                                                                                                       |

• Writing a 1 to the IRQE bit in the Interrupt Control Register

Interrupts are globally disabled by any of the following actions:

- Execution of a Disable Interrupt (DI) instruction

- eZ8 CPU acknowledgement of an interrupt service request from the interrupt controller

- Writing a 0 to the IRQE bit in the Interrupt Control Register

- Reset

- Execution of a trap instruction

- Illegal instruction trap

## **Interrupt Vectors and Priority**

The interrupt controller supports three levels of interrupt priority. Level 3 is the highest priority, Level 2 is the second highest priority, and Level 1 is the lowest priority. If all of the interrupts were enabled with identical interrupt priority (all as Level 2 interrupts), then interrupt priority would be assigned from highest to lowest as specified in <u>Table 24</u>. Level 3 interrupts always have higher priority than Level 2 interrupts which in turn always have higher priority than Level 1 interrupt priority level (Level 1, Level 2, or Level 3), priority is assigned as specified in <u>Table 24</u>. A Reset, WDT interrupt (if enabled), and an Illegal Instruction Trap will always have the highest priority.

## **Interrupt Assertion**

Interrupt sources assert their interrupt requests for only a single system clock period (single pulse). When the interrupt request is acknowledged by the eZ8 CPU, the corresponding bit in the Interrupt Request Register is cleared until the next interrupt occurs. Writing a 0 to the corresponding bit in the Interrupt Request Register likewise clears the interrupt request.

**Caution:** Zilog recommends not using a coding style that clears bits in the Interrupt Request registers. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost. See Example 1, which follows.

**Example 1.** A poor coding style that can result in lost interrupt requests:

LDX r0, IRQ0 AND r0, MASK LDX IRQ0, r0

# Embedded in Life

| Bit           | Description                                                                                                                                                                                                                                                                                                                                                                             |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]         | Pulse-Width Modulator High and Low Bytes                                                                                                                                                                                                                                                                                                                                                |

| PWMH,<br>PWML | These two bytes, {PWMH[7:0], PWML[7:0], form a 16-bit value that is compared to the current 16-bit timer count. When a match occurs, the PWM output changes state. The PWM output value is set by the TPOL bit in the Timer Control (TxCTL) Register.<br>The TxPWMH and TxPWML registers also store the 16-bit captured timer value when operating in CAPTURE or CAPTURE/COMPARE modes. |

## Timer 0–3 Control 0 Registers

The Timer 0–3 Control 0 (TxCTL0) registers, shown in Table 45, allow cascading of the Timers.

| Bit        | 7                                                                                                                                                                                                  | 6                      | 5            | 4          | 3            | 2         | 1     | 0 |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------|------------|--------------|-----------|-------|---|

| Field      |                                                                                                                                                                                                    | Reserved               |              | CSC        |              | Rese      | erved |   |

| RESET      |                                                                                                                                                                                                    |                        |              | (          | )            |           |       |   |

| R/W        |                                                                                                                                                                                                    | R/W                    |              |            |              |           |       |   |

| Address    |                                                                                                                                                                                                    | F06H, F0EH, F16H, F1EH |              |            |              |           |       |   |

| Bit        | Description                                                                                                                                                                                        |                        |              |            |              |           |       |   |

| [7:5]      | Reserved<br>These bits are reserved and must be programmed to 000.                                                                                                                                 |                        |              |            |              |           |       |   |

| [4]<br>CSC | Cascade Timers<br>0 = Timer Input signal comes from the pin.<br>1 = For Timer 0, input signal is connected to Timer 1 output. For Timer 1, the input signal is<br>connected to the Timer 0 output. |                        |              |            |              | signal is |       |   |

| [3:0]      | Reserved<br>These bits a                                                                                                                                                                           | are reserved           | l and must b | e programn | ned to 0000. |           |       |   |

#### Table 45. Timer 0–3 Control 0 Registers (TxCTL0)

67

ilog<sup>®</sup> Embedded in Life An⊡IXYS Company **74**

#### Table 48. Watchdog Timer Control Register (WDTCTL)

| Bit         | 7                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6               | 5            | 4           | 3           | 2                                  | 1                          | 0         |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------|-------------|-------------|------------------------------------|----------------------------|-----------|

| Field       | POR                                                                                                                                                                                                                                                                                                                                                                                                                                    | STOP            | WDT          | EXT         | Reserved    |                                    |                            |           |

| RESET       |                                                                                                                                                                                                                                                                                                                                                                                                                                        | See Table 49. 0 |              |             |             |                                    |                            |           |

| R/W         |                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 |              | I           | ۲           |                                    |                            |           |

| Address     |                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 |              | FF          | ЮH          |                                    |                            |           |

| Bit         | Descriptio                                                                                                                                                                                                                                                                                                                                                                                                                             | Description     |              |             |             |                                    |                            |           |

| [7]<br>POR  | If this bit is                                                                                                                                                                                                                                                                                                                                                                                                                         |                 | OR event o   |             |             | t to 0, if a WI<br>e register is r |                            | t or Stop |

| [6]<br>STOP | Stop Mode Recovery Indicator<br>If this bit is set to 1, a Stop Mode Recovery occurred. If the STOP and WDT bits are both set to<br>1, the Stop Mode Recovery occurred due to a WDT time-out. If the stop bit is 1 and the WDT bits<br>is 0, the Stop Mode Recovery was not caused by a WDT time-out. This bit is reset by a POR of<br>a WDT time-out that occurred while not in STOP Mode. Reading this register also resets this bit |                 |              |             |             |                                    | the WDT bit<br>by a POR or |           |

| [5]<br>WDT  | Watchdog Timer Time-Out Indicator<br>If this bit is set to 1, a WDT time-out occurred. A POR resets this pin. A Stop Mode Recovery<br>due a change in an input pin also resets this bit. Reading this register resets this bit.                                                                                                                                                                                                        |                 |              |             |             |                                    |                            |           |

| [4]<br>EXT  | External Reset Indicator<br>If this bit is set to 1, a Reset initiated by the external RESET pin occurred. A POR or a Stop<br>Mode Recovery from a change in an input pin resets this bit. Reading this register resets this b                                                                                                                                                                                                         |                 |              |             |             |                                    |                            |           |

| [3:0]       | Reserved<br>These bits                                                                                                                                                                                                                                                                                                                                                                                                                 | are reserved    | d and must b | be programn | ned to 0000 |                                    |                            |           |

## Table 49. Watchdog Timer Events

| Reset or Stop Mode Recovery Event                   | POR | STOP | WDT | EXT |

|-----------------------------------------------------|-----|------|-----|-----|

| Power-On Reset                                      | 1   | 0    | 0   | 0   |

| Reset through RESET pin assertion                   | 0   | 0    | 0   | 1   |

| Reset through WDT time-out                          | 0   | 0    | 1   | 0   |

| Reset through the OCD (OCTCTL[1] set to 1)          | 1   | 0    | 0   | 0   |

| Reset from STOP Mode through the DBG Pin driven Low | 1   | 0    | 0   | 0   |

| Stop Mode Recovery through GPIO pin transition      | 0   | 1    | 0   | 0   |

| Stop Mode Recovery through WDT time-out             | 0   | 1    | 1   | 0   |

#### ilog Embedded in Life An IXYS Company

87

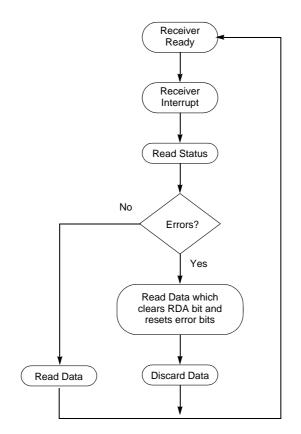

## **UART Data and Error Handling Procedure**

Figure 16 displays the recommended procedure for UART receiver ISRs.

## **Baud Rate Generator Interrupts**

If the BRG interrupt enable is set, the UART Receiver interrupt asserts when the UART Baud Rate Generator reloads. This action allows the BRG to function as an additional counter if the UART functionality is not employed.

Figure 16. UART Receiver Interrupt Service Routine Flow

## Embedded in Life An TIXYS Company 108

## **SPI Interrupts**

When SPI interrupts are enabled, the SPI generates an interrupt after character transmission/reception completes in both Master and Slave modes. A character is defined to be 1 through 8 bits by the NUMBITS field in the SPI Mode Register. In SLAVE Mode it is not necessary for  $\overline{SS}$  to deassert between characters to generate the interrupt. The SPI in SLAVE Mode also generates an interrupt if the  $\overline{SS}$  signal deasserts prior to transfer of all of the bits in a character (see the previous paragraph). Writing a 1 to the IRQ bit in the SPI Status Register clears the pending SPI interrupt request. The IRQ bit must be cleared to 0 by the ISR to generate future interrupts. To start the transfer process, an SPI interrupt can be forced by software writing a 1 to the STR bit in the SPICTL Register.

If the SPI is disabled, an SPI interrupt can be generated by a BRG time-out. This timer function must be enabled by setting the BIRQ bit in the SPICTL Register. This BRG time-out does not set the IRQ bit in the SPISTAT Register, just the SPI interrupt bit in the interrupt controller.

## **SPI Baud Rate Generator**

In SPI MASTER Mode, the BRG creates a lower frequency serial clock (SCK) for data transmission synchronization between the Master and the external Slave. The input to the BRG is the system clock. The SPI Baud Rate High and Low Byte registers combine to form a 16-bit reload value, BRG[15:0], for the SPI Baud Rate Generator. The SPI baud rate is calculated using the following equation:

SPI Baud Rate (bits/s) = <u>System Clock Frequency (Hz)</u> 2xBRG[15:0]

The minimum baud rate is obtained by setting BRG[15:0] to 0000H for a clock divisor value of (2 x 65536 = 131072).

When the SPI is disabled, BRG functions as a basic 16-bit timer with interrupt upon timeout. Observe the following procedure to configure BRG as a timer with interrupt upon time-out:

- 1. Disable the SPI by clearing the SPIEN bit in the SPI Control Register to 0.

- 2. Load the appropriate 16-bit count value into the SPI Baud Rate High and Low Byte registers.

- 3. Enable BRG timer function and associated interrupt by setting the BIRQ bit in the SPI Control Register to 1.

When configured as a general-purpose timer, the interrupt interval is calculated using the following equation:

Interrupt Interval (s) = System Clock Period (s) ×BRG[15:0]]

#### ilog° Embedded in Life An∎IXYS Company

130

| Bit         | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [5]<br>ACK  | Acknowledge<br>This bit indicates the status of the Acknowledge for the last byte transmitted or received. When<br>set, this bit indicates that an Acknowledge occurred for the last byte transmitted or received.<br>This bit is cleared when IEN = 0 or when a Not Acknowledge occurred for the last byte trans-<br>mitted or received. It is not reset at the beginning of each transaction and is not reset when this<br>register is read.                                                                                                                                                                                                                                                         |

|             | <b>Caution:</b> When making decisions based on this bit within a transaction, software cannot determine when the bit is updated by hardware. In the case of write transactions, the $1^{2}$ C pauses at the beginning of the Acknowledge cycle if the next transmit data or address byte has not been written (TDRE = 1) and STOP and start = 0. In this case the ACK bit is not updated until the transmit interrupt is serviced and the Acknowledge cycle for the previous byte completes. For examples on usage of the ACK bit, see the <u>Address Only Transaction with a 7-Bit Address</u> section on page 120 and the <u>Address-Only Transaction with a 10-Bit Address</u> section on page 122. |

| [4]         | <b>10-Bit Address</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 10B         | This bit indicates whether a 10-bit or 7-bit address is being transmitted. After the start bit is set, if the five most-significant bits of the address are 11110B, this bit is set. When set, it is reset after the first byte of the address has been sent.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| [3]         | <b>Read</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RD          | This bit indicates the direction of transfer of the data. It is active High during a read. The status of this bit is determined by the least-significant bit of the I <sup>2</sup> C Shift Register after the start bit is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| [2]         | <b>Transmit Address State</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| TAS         | This bit is active High while the address is being shifted out of the I <sup>2</sup> C Shift Register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| [1]         | <b>Data Shift State</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DSS         | This bit is active High while data is being shifted to or from the I <sup>2</sup> C Shift Register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| [0]<br>NCKI | <b>NACK Interrupt</b><br>This bit is set High when a Not Acknowledge condition is received or sent and neither the start<br>nor the stop bit is active. When set, this bit generates an interrupt that can only be cleared by<br>setting the start or stop bit, allowing you to specify whether you want to perform a stop or a<br>repeated start.                                                                                                                                                                                                                                                                                                                                                     |

- 2. Write to the ADC Control Register to configure the ADC for continuous conversion. The bit fields in the ADC Control Register can be written simultaneously:

- Write to the ANAIN[3:0] field to select one of the 5 analog input sources.

- Set CONT to 1 to select continuous conversion.

- Write to the VREF bit to enable or disable the internal voltage reference generator.

- Set CEN to 1 to start the conversions.

- 3. When the first conversion in continuous operation is complete (after 5129 system clock cycles, plus the 40 cycles for power-up, if necessary), the ADC control logic performs the following operations:

- CEN resets to 0 to indicate the first conversion is complete. CEN remains 0 for all subsequent conversions in continuous operation.

- An interrupt request is sent to the Interrupt Controller to indicate the conversion is complete.

- Thereafter, the ADC writes a new 10-bit data result to {ADCD\_H[7:0], ADCD\_L[7:6]} every 256 system clock cycles. An interrupt request is sent to the Interrupt Controller when each conversion is complete.

- 5. To disable continuous conversion, clear the CONT bit in the ADC Control Register to 0.

## **ADC Control Register Definitions**

This section defines the features of the following ADC Control registers.

ADC Control Register: see page 139

ADC Data High Byte Register: see page 141

ADC Data Low Bits Register: see page 142

## **ADC Control Register**

The ADC Control Register, shown in Table 78, selects the analog input channel and initiates the analog-to-digital conversion.

| Bit     | 7   | 6        | 5    | 4    | 3  | 2    | 1      | 0 |

|---------|-----|----------|------|------|----|------|--------|---|

| Field   | CEN | Reserved | VREF | CONT |    | ANAI | N[3:0] |   |

| RESET   | (   | 0        | 1    |      |    | 0    |        |   |

| R/W     |     |          |      | R/   | W  |      |        |   |

| Address |     |          |      | F7   | OH |      |        |   |

| Table 78. | ADC Control | Register | (ADCCTL) |

|-----------|-------------|----------|----------|

|-----------|-------------|----------|----------|

## Flash Memory

The products in the Z8 Encore! XP<sup>®</sup> F0822 Series feature either 8KB (8192) or 4KB (4096) bytes of Flash memory with Read/Write/Erase capability. Flash memory is programmed and erased in-circuit by either user code or through the OCD.

The Flash memory array is arranged in 512-byte per page. The 512-byte page is the minimum Flash block size that can be erased. Flash memory is divided into eight sectors which is protected from programming and erase operations on a per sector basis.

Table 81 describes the Flash memory configuration for each device in the Z8F082xfamily. Table 82 lists the sector address ranges. Figure 33 displays the Flash memory arrangement.

| Part Number | Flash Size | Number<br>of Pages | Flash Memory<br>Addresses | Sector Size | Number of<br>Sectors | Pages<br>per<br>Sector |

|-------------|------------|--------------------|---------------------------|-------------|----------------------|------------------------|

| Z8F08xx     | 8KB (8192) | 16                 | 0000H-1FFFH               | 1 KB (1024) | 8                    | 2                      |

| Z8F04xx     | 4KB (4096) | 8                  | 0000H-0FFFH               | 0.5KB (512) | 8                    | 1                      |

Table 82. Flash Memory Sector Addresses

#### Table 81. Flash Memory Configurations

|               | Flash Sector Address Range |             |  |  |  |

|---------------|----------------------------|-------------|--|--|--|

| Sector Number | Z8F04xx                    | Z8F08xx     |  |  |  |

| 0             | 0000H-01FFH                | 0000H-03FFH |  |  |  |

| 1             | 0200H-03FFH                | 0400H–07FFH |  |  |  |

| 2             | 0400H-05FFH                | 0800H-0BFFH |  |  |  |

| 3             | 0600H-07FFH                | 0C00H-0FFFH |  |  |  |

| 4             | 0800H-09FFH                | 1000H–13FFH |  |  |  |

| 5             | 0A00H-0BFFH                | 1400H–17FFH |  |  |  |

| 6             | 0C00H-0DFFH                | 1800H–1BFFH |  |  |  |

| 7             | 0E00H-0FFFH                | 1C00H-1FFFH |  |  |  |

143

nbedded in Life

nbedded in Life

152

## Page Select Register

The Page Select (FPS) Register, shown in Table 86, selects the Flash memory page to be erased or programmed. Each Flash page contains 512 bytes of Flash memory. During a Page Erase operation, all Flash memory locations with the 7 most significant bits of the address provided by the PAGE field are erased to FFH.

The Page Select Register shares its Register File address with the Flash Sector Protect Register. The Page Select Register cannot be accessed when the Flash Sector Protect Register is enabled.

| Bit     | 7       | 6           | 5 | 4  | 3  | 2 | 1 | 0 |

|---------|---------|-------------|---|----|----|---|---|---|

| Field   | INFO_EN | NFO_EN PAGE |   |    |    |   |   |   |

| RESET   |         | 0           |   |    |    |   |   |   |

| R/W     |         | R/W         |   |    |    |   |   |   |

| Address |         |             |   | FF | 9H |   |   |   |

| Table 86. P | Page Select | Register ( | (FPS) |

|-------------|-------------|------------|-------|

|-------------|-------------|------------|-------|

| Bit     | Description                                                                                                                                                |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]     | Information Area Enable                                                                                                                                    |

| INFO_EN | 0 = Information Area is not selected.                                                                                                                      |

|         | <ol> <li>Information Area is selected. The Information area is mapped into the Flash memory<br/>address space at addresses FE00H through FFFFH.</li> </ol> |

| [6:0]   | Page Select                                                                                                                                                |

| PAGE    | This 7-bit field selects the Flash memory page for Programming and Page Erase operations.<br>Flash memory address[15:9] = PAGE[6:0].                       |

## **Flash Sector Protect Register**

The Flash Sector Protect Register, shown in Table 87, protects Flash memory sectors from being programmed or erased from user code. The Flash Sector Protect Register shares its Register File address with the Page Select Register. The Flash Sector Protect Register can be accessed only after writing the Flash Control Register with 5EH.

User code can only write bits in this register to 1 (bits cannot be cleared to 0 by user code). To determine the appropriate Flash memory sector address range and sector number for your F0822 Series product, please refer to <u>Table 82</u> on page 143.

> ilog mbedded in Life

S Company

171

## **OCD Status Register**

The OCD Status Register, shown in Table 95, reports status information about the current state of the debugger and the system.

## Table 95. OCD Status Register (OCDSTAT)

| Bit   | 7    | 6    | 5    | 4 | 3 | 2        | 1 | 0 |

|-------|------|------|------|---|---|----------|---|---|

| Field | IDLE | HALT | RPEN |   |   | Reserved |   |   |

| RESET |      | 0    |      |   |   |          |   |   |

| R/W   | R    |      |      |   |   |          |   |   |

|       |      |      |      |   |   |          |   |   |

| Bit         | Description                                                                                                                                                                                                                                                                                                                                                            |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>IDLE | <ul> <li>CPU Idling</li> <li>This bit is set if the part is in DEBUG Mode (DBGMODE is 1), or if a BRK instruction occurred since the last time OCDCTL was written. This can be used to determine if the CPU is running or if it is idling.</li> <li>0 = The eZ8 CPU is running.</li> <li>1 = The eZ8 CPU is either stopped or looping on a BRK instruction.</li> </ul> |

| [6]<br>HALT | HALT Mode         0 = The device is not in HALT Mode.         1 = The device is in HALT Mode.                                                                                                                                                                                                                                                                          |

| [5]<br>RPEN | Read Protect Option Bit Enabled0 = The Read Protect option bit is disabled (1).1 = The Read Protect option bit is enabled (0), disabling many OCD commands.                                                                                                                                                                                                            |

| [4:0]       | <b>Reserved</b><br>These bits are reserved and must be programmed to 00000.                                                                                                                                                                                                                                                                                            |

181

С

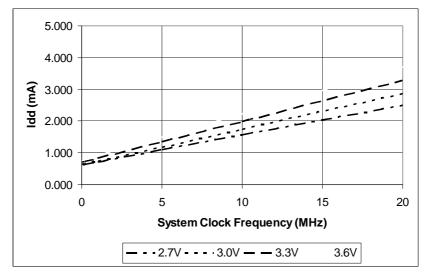

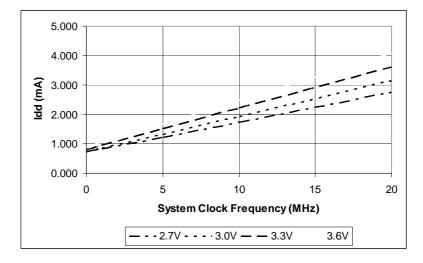

Figure 43 displays the typical current consumption in HALT Mode while operating at 25°C plotted opposite the system clock frequency. All GPIO pins are configured as outputs and driven High.

Figure 43. Typical HALT Mode  $I_{\text{DD}}$  vs. System Clock Frequency

182

С

Figure 44 displays the maximum HALT Mode current consumption across the entire operating temperature range of the device and plotted opposite the system clock frequency. All GPIO pins are configured as outputs and driven High.

Figure 44. Maximum HALT Mode  $I_{CC}$  vs. System Clock Frequency

183

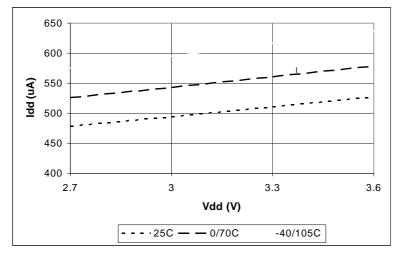

Figure 45 displays the maximum current consumption in STOP Mode with the VBO and Watchdog Timer enabled plotted opposite the power supply voltage. All GPIO pins are configured as outputs and driven High.

Figure 45. Maximum STOP Mode  $\mathrm{I}_{\mathrm{DD}}$  with VBO Enabled vs. Power Supply Voltage

dded in Life

An IXYS Company

191

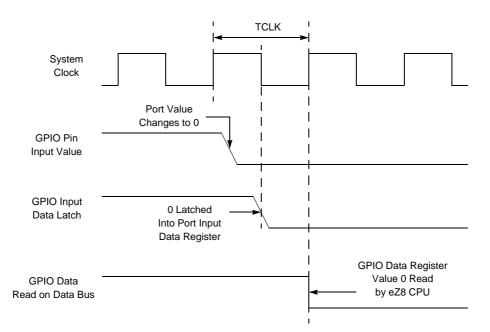

## General Purpose I/O Port Input Data Sample Timing

Figure 48 displays timing of the GPIO Port input sampling. Table 106 lists the GPIO port input timing.

#### Figure 48. Port Input Sample Timing

#### Table 106. GPIO Port Input Timing

|                     |                                                                                                    | Delay (ns) |         |  |

|---------------------|----------------------------------------------------------------------------------------------------|------------|---------|--|

| Parameter           | Abbreviation                                                                                       | Minimum    | Maximum |  |

| T <sub>S_PORT</sub> | Port Input Transition to X <sub>IN</sub> Fall Setup Time (not pictured)                            | 5          | -       |  |

| T <sub>H_PORT</sub> | X <sub>IN</sub> Fall to Port Input Transition Hold Time (not pictured)                             | 5          | -       |  |

| T <sub>SMR</sub>    | GPIO Port Pin Pulse Width to Insure Stop Mode Recovery (for GPIO port pins enabled as SMR sources) | 1µs        |         |  |

198

С

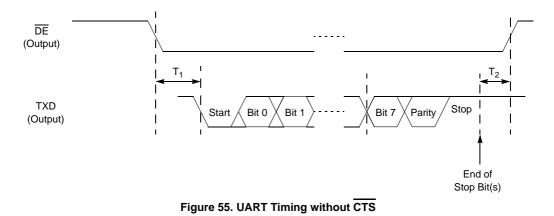

resented here by  $\overline{DE}$ .  $\overline{DE}$  asserts after the UART Transmit Data Register has been written.  $\overline{DE}$  remains asserted for multiple characters as long as the Transmit Data Register is written with the next character before the current character has completed.

|                |                                                | Delay (ns)                 |                                              |  |

|----------------|------------------------------------------------|----------------------------|----------------------------------------------|--|

| Parameter      | Abbreviation                                   | Minimum                    | Maximum                                      |  |

| T <sub>1</sub> | DE Assertion to TXD Falling Edge (Start) Delay | 1 Bit period               | 1 Bit period +<br>1 * X <sub>IN</sub> period |  |

| T <sub>2</sub> | End of Stop Bit(s) to DE Deassertion Delay     | 1 * X <sub>IN</sub> period | 2 * X <sub>IN</sub> period                   |  |

00

217

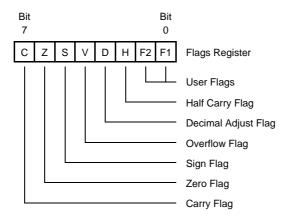

## **Flags Register**

The Flags Register contains the status information regarding the most recent arithmetic, logical, bit manipulation or rotate and shift operation. The Flags Register contains six bits of status information that are set or cleared by CPU operations. Four of the bits (C, V, Z and S) can be tested with conditional jump instructions. Two flags (H and D) cannot be tested and are used for Binary-Coded Decimal (BCD) arithmetic.

The two remaining bits, User Flags (F1 and F2), are available as general-purpose status bits. User Flags are unaffected by arithmetic operations and must be set or cleared by instructions. The User Flags cannot be used with conditional Jumps. They are undefined at initial power-up and are unaffected by Reset. Figure 56 illustrates the flags and their bit positions in the Flags Register.

Figure 56. Flags Register

Interrupts, the Software Trap (TRAP) instruction, and Illegal Instruction Traps all write the value of the Flags Register to the stack. Executing an Interrupt Return (IRET) instruction restores the value saved on the stack into the Flags Register.

| Z8 Encore! XP® | F0822  | Series  |

|----------------|--------|---------|

| Product        | Specif | ication |

226

## Hex Address: F01

## Table 131. Timer 0–1 Low Byte Register (TxL)

| Bit     | 7   | 6          | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|-----|------------|---|---|---|---|---|---|

| Field   | TL  |            |   |   |   |   |   |   |

| RESET   | 0 1 |            |   |   |   |   |   | 1 |

| R/W     | R/W |            |   |   |   |   |   |   |

| Address |     | F01H, F09H |   |   |   |   |   |   |

## Hex Address: F02

#### Table 132. Timer 0–1 Reload High Byte Register (TxRH)

| Bit     | 7   | 6   | 5 | 4     | 3    | 2 | 1 | 0 |

|---------|-----|-----|---|-------|------|---|---|---|

| Field   |     | TRH |   |       |      |   |   |   |

| RESET   | 1   |     |   |       |      |   |   |   |

| R/W     | R/W |     |   |       |      |   |   |   |

| Address |     |     |   | F02H, | F0AH |   |   |   |

## Hex Address: F03

### Table 133. Timer 0–1 Reload Low Byte Register (TxRL)

| Bit     | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|------------|---|---|---|---|---|---|---|

| Field   | TRL        |   |   |   |   |   |   |   |

| RESET   | 1          |   |   |   |   |   |   |   |

| R/W     | R/W        |   |   |   |   |   |   |   |

| Address | F03H, F0BH |   |   |   |   |   |   |   |

#### ilog<sup>\*</sup> Embedded in Life An LIXYS Company 235

#### Hex Addresses: F57-F5F

This address range is reserved.

## **SPI Control Registers**

For more information about the SPI registers, see the <u>SPI Control Register Definitions</u> section on page 109.

#### Hex Address: F60

#### Bit 7 6 5 2 1 4 3 0 Field DATA RESET Х R/W R/W Address F60H

#### Table 162. SPI Data Register (SPIDATA)

### Hex Address: F61

#### Table 163. SPI Control Register (SPICTL)

| Bit     | 7    | 6   | 5    | 4     | 3      | 2   | 1    | 0     |

|---------|------|-----|------|-------|--------|-----|------|-------|

| Field   | IRQE | STR | BIRQ | PHASE | CLKPOL | WOR | MMEN | SPIEN |

| RESET   | 0    |     |      |       |        |     |      |       |

| R/W     | R/W  |     |      |       |        |     |      |       |

| Address | F61H |     |      |       |        |     |      |       |

## Hex Address: F62

#### Table 164. SPI Status Register (SPISTAT)

| Bit                                                        | 7    | 6   | 5   | 4   | 3        | 2 | 1    | 0    |

|------------------------------------------------------------|------|-----|-----|-----|----------|---|------|------|

| Field                                                      | IRQ  | OVR | COL | ABT | Reserved |   | TXST | SLAS |

| RESET                                                      | 0 1  |     |     |     |          |   |      |      |

| R/W                                                        | R/W* |     |     |     | R        |   |      |      |

| Address                                                    | F62H |     |     |     |          |   |      |      |

| Note: *R/W = read access; write a 1 to clear the bit to 0. |      |     |     |     |          |   |      |      |