# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, UART/USART                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                     |

| Number of I/O              | 11                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | ·                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0411hh020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

ILO G

13

## **Pin Characteristics**

Table 4 provides detailed information about the characteristics for each pin available on Z8 Encore!  $XP^{\textcircled{B}}$  F0822 Series products. The data in Table 4 is sorted alphabetically by pin symbol mnemonic.

| Symbol<br>Mnemonic | Direction | Reset<br>Direction | Active<br>Low or<br>Active<br>High | Tri-State<br>Output | Internal<br>Pull-Up or<br>Pull-Down | Schmitt-Trigger<br>Input | Open Drain<br>Output   |

|--------------------|-----------|--------------------|------------------------------------|---------------------|-------------------------------------|--------------------------|------------------------|

| AV <sub>DD</sub>   | N/A       | N/A                | N/A                                | N/A                 | No                                  | No                       | N/A                    |

| AV <sub>SS</sub>   | N/A       | N/A                | N/A                                | N/A                 | No                                  | No                       | N/A                    |

| DBG                | I/O       | I                  | N/A                                | Yes                 | No                                  | Yes                      | Yes                    |

| PA[7:0]            | I/O       | I                  | N/A                                | Yes                 | Programma-<br>ble pull-up           | Yes                      | Yes, pro-<br>grammable |

| PB[4:0]            | I/O       | I                  | N/A                                | Yes                 | Programma-<br>ble pull-up           | Yes                      | Yes, pro-<br>grammable |

| PC[5:0]            | I/O       | I                  | N/A                                | Yes                 | Programma-<br>ble pull-up           | Yes                      | Yes, pro-<br>grammable |

| RESET              | I         | I                  | Low                                | N/A                 | Pull-up                             | Yes                      | N/A                    |

| V <sub>DD</sub>    | N/A       | N/A                | N/A                                | N/A                 | No                                  | No                       | N/A                    |

| V <sub>REF</sub>   | Analog    | N/A                | N/A                                | N/A                 | No                                  | No                       | N/A                    |

| V <sub>SS</sub>    | N/A       | N/A                | N/A                                | N/A                 | No                                  | No                       | N/A                    |

| X <sub>IN</sub>    | I         | I                  | N/A                                | N/A                 | No                                  | No                       | N/A                    |

| X <sub>OUT</sub>   | 0         | 0                  | N/A                                | No                  | No                                  | No                       | No                     |

#### **Table 4. Pin Characteristics**

ILOG nbedded in Life IXYS Company

25

clock cycles, the device progresses through the System Reset sequence. While the  $\overline{\text{RESET}}$  input pin is asserted Low, Z8 Encore! XP<sup>®</sup> F0822 Series device continues to be held in the Reset state. If the  $\overline{\text{RESET}}$  pin is held Low beyond the System Reset time-out, the device exits the Reset state immediately following  $\overline{\text{RESET}}$  pin deassertion. Following a System Reset initiated by the external  $\overline{\text{RESET}}$  pin, the EXT status bit in the Watchdog Timer Control Register (WDTCTL) is set to 1.

## **On-Chip Debugger Initiated Reset**

A POR is initiated using the OCD by setting the RST bit in the OCD Control Register. The OCD block is not reset but the rest of the chip goes through a normal system reset. The RST bit automatically clears during the system reset. Following the system reset, the POR bit in the WDT Control Register is set.

## **Stop Mode Recovery**

STOP Mode is entered by execution of a stop instruction by the eZ8 CPU. For detailed information about STOP Mode, see the <u>Low-Power Modes</u> chapter on page 27. During Stop Mode Recovery, the device is held in reset for 66 cycles of the WDT oscillator followed by 16 cycles of the system clock. Stop Mode Recovery only affects the contents of the WDT Control Register and does not affect any other values in the Register File including the Stack Pointer, Register Pointer, Flags, Peripheral Control registers, and General-Purpose RAM.

The eZ8 CPU fetches the Reset vector at Program memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vector address. Following Stop Mode Recovery, the stop bit in the WDT Control Register is set to 1. Table 10 lists the Stop Mode Recovery sources and resulting actions. The text following provides more detailed information about each of the Stop Mode Recovery sources.

| Operating Mode | Stop Mode Recovery Source                                                      | Action                                                               |

|----------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------|

| STOP Mode      | WDT time-out when configured for Reset                                         | Stop Mode Recovery                                                   |

|                | WDT time-out when configured for inter-<br>rupt                                | Stop Mode Recovery followed by interrupt (if interrupts are enabled) |

|                | Data transition on any GPIO Port pin<br>enabled as a Stop Mode Recovery source | Stop Mode Recovery                                                   |

| Table 10. Stop Mode Recover | Sources and Resulting Action |

|-----------------------------|------------------------------|

|-----------------------------|------------------------------|

- System clock is enabled and continues to operate

- eZ8 CPU is stopped

- Program counter stops incrementing

- WDT's internal RC oscillator continues to operate

- If enabled, the WDT continues to operate

- All other on-chip peripherals continue to operate

The eZ8 CPU can be brought out of HALT Mode by any of the following operations:

- Interrupt

- WDT time-out (interrupt or reset)

- Power-On Reset

- Voltage Brown-Out reset

- External **RESET** pin assertion

To minimize current in HALT Mode, all GPIO pins which are configured as inputs must be driven to one of the supply rails ( $V_{CC}$  or GND).

#### Table 42. Timer 0–1 Reload Low Byte Register (TxRL)

| Bit     | 7   | 6 | 5 | 4     | 3    | 2 | 1 | 0 |  |  |  |

|---------|-----|---|---|-------|------|---|---|---|--|--|--|

| Field   | TRL |   |   |       |      |   |   |   |  |  |  |

| RESET   | 1   |   |   |       |      |   |   |   |  |  |  |

| R/W     | R/W |   |   |       |      |   |   |   |  |  |  |

| Address |     |   |   | F03H, | F0BH |   |   |   |  |  |  |

| Bit  | Description                                                                                   |

|------|-----------------------------------------------------------------------------------------------|

| [7]  | Timer Reload Register High and Low                                                            |

| TRH, | These two bytes form the 16-bit reload value, {TRH[7:0], TRL[7:0]}. This value sets the maxi- |

| TRL  | mum count value which initiates a timer reload to 0001H. In COMPARE Mode, these two bytes     |

|      | form the 16-bit Compare value.                                                                |

### Timer 0–1 PWM High and Low Byte Registers

The Timer 0–1 PWM High and Low Byte (TxPWMH and TxPWML) registers, shown in Tables 43 and 44, are used for Pulse-Width Modulator (PWM) operations. These registers also store the Capture values for the CAPTURE and CAPTURE/COMPARE modes.

#### Table 43. Timer 0–1 PWM High Byte Register (TxPWMH)

| Bit     | 7    | 6 | 5 | 4     | 3    | 2 | 1 | 0 |  |  |  |

|---------|------|---|---|-------|------|---|---|---|--|--|--|

| Field   | PWMH |   |   |       |      |   |   |   |  |  |  |

| RESET   | 0    |   |   |       |      |   |   |   |  |  |  |

| R/W     | R/W  |   |   |       |      |   |   |   |  |  |  |

| Address |      |   |   | F04H, | F0CH |   |   |   |  |  |  |

#### Table 44. Timer 0–1 PWM Low Byte Register (TxPWML)

| Bit     | 7    | 6 | 5 | 4     | 3    | 2 | 1 | 0 |  |  |

|---------|------|---|---|-------|------|---|---|---|--|--|

| Field   | PWML |   |   |       |      |   |   |   |  |  |

| RESET   | 0    |   |   |       |      |   |   |   |  |  |

| R/W     | R/W  |   |   |       |      |   |   |   |  |  |

| Address |      |   |   | F05H, | F0DH |   |   |   |  |  |

## Watchdog Timer Reload Upper, High and Low Byte Registers

The Watchdog Timer Reload Upper, High and Low Byte (WDTU, WDTH, WDTL) registers, shown in Tables 50 through 52, form the 24-bit reload value that is loaded into the WDT, when a WDT instruction executes. The 24-bit reload value is {WDTU[7:0], WDTH[7:0], WDTL[7:0]}. Writing to these registers sets the required reload value. Reading from these registers returns the current WDT count value.

**Caution:** The 24-bit WDT reload value must not be set to a value less than 000004H.

| Bit        | 7                                                                                                   | 6    | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|------------|-----------------------------------------------------------------------------------------------------|------|---|---|---|---|---|---|--|--|--|

| Field      |                                                                                                     | WDTU |   |   |   |   |   |   |  |  |  |

| RESET      |                                                                                                     | 1    |   |   |   |   |   |   |  |  |  |

| R/W        |                                                                                                     | R/W* |   |   |   |   |   |   |  |  |  |

| Address    |                                                                                                     | FF1H |   |   |   |   |   |   |  |  |  |

| Note: *R/\ | Note: *R/W = a read returns the current WDT count value; a write sets the appropriate reload value. |      |   |   |   |   |   |   |  |  |  |

#### Table 50. Watchdog Timer Reload Upper Byte Register (WDTU)

| Bit   | Description                                                               |

|-------|---------------------------------------------------------------------------|

| [7:0] | WDT Reload Upper Byte                                                     |

| WDTU  | Most significant byte (MSB), bits [23:16] of the 24-bit WDT reload value. |

|       |                                                                           |

| Table 51. | Watchdog   | Timer    | Reload | Hiah | Bvte | Register | (WDTH) |

|-----------|------------|----------|--------|------|------|----------|--------|

|           | materialog | 1 111101 | noiouu |      | 5,00 | regiotei | (      |

| Bit        | 7             | 6              | 5           | 4              | 3              | 2              | 1          | 0 |  |  |

|------------|---------------|----------------|-------------|----------------|----------------|----------------|------------|---|--|--|

| Field      | WDTH          |                |             |                |                |                |            |   |  |  |

| RESET      |               | 1              |             |                |                |                |            |   |  |  |

| R/W        |               | R/W*           |             |                |                |                |            |   |  |  |

| Address    |               | FF2H           |             |                |                |                |            |   |  |  |

| Note: *R/\ | N = a read re | turns the curr | ent WDT cou | nt value; a wi | ite sets the a | ppropriate rel | oad value. |   |  |  |

| Bit   | Description                                              |

|-------|----------------------------------------------------------|

| [7:0] | WDT Reload High Byte                                     |

| WDTH  | Middle byte, bits [15:8] of the 24-bit WDT reload value. |

75

ILO<u>G</u> abedded in Life

Z8 Encore! XP<sup>®</sup> F0822 Series

**Product Specification**

## **UART Status 0 Register**

The UART Status 0 and Status 1 registers, shown in Tables 55 and 56, identify the current UART operating configuration and status.

#### Table 55. UART Status 0 Register (U0STAT0)

| Bit         | 7                                                          | 6                                                                                                                                                                                                                                                                                                                                               | 5                                         | 4                   | 3          | 2             | 1            | 0        |  |  |  |

|-------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|---------------------|------------|---------------|--------------|----------|--|--|--|

| Field       | RDA                                                        | PE                                                                                                                                                                                                                                                                                                                                              | OE                                        | FE                  | BRKD       | TDRE          | TXE          | CTS      |  |  |  |

| RESET       |                                                            | 0 1 X                                                                                                                                                                                                                                                                                                                                           |                                           |                     |            |               |              |          |  |  |  |

| R/W         |                                                            |                                                                                                                                                                                                                                                                                                                                                 |                                           | I                   | २          |               |              |          |  |  |  |

| Address     |                                                            |                                                                                                                                                                                                                                                                                                                                                 |                                           | F4                  | 1H         |               |              |          |  |  |  |

| Bit         | Descriptio                                                 | n                                                                                                                                                                                                                                                                                                                                               |                                           |                     |            |               |              |          |  |  |  |

|             |                                                            | n<br>ata Availabl                                                                                                                                                                                                                                                                                                                               | •                                         |                     |            |               |              |          |  |  |  |

| [7]<br>RDA  | This bit indi<br>Receive Da<br>0 = The UA                  | icates that that that Register<br>RT Receive<br>s a byte in th                                                                                                                                                                                                                                                                                  | he UART Re<br>clears this b<br>Data Regis | it.<br>ter is empty |            | s received da | ata. Reading | the UART |  |  |  |

| [6]<br>PE   | clears this b<br>0 = No pari                               | icates that a                                                                                                                                                                                                                                                                                                                                   | occurred.                                 | has occurre         | d. Reading | the UART R    | eceive Data  | Register |  |  |  |

| [5]<br>OE   | This bit indi<br>received an<br>then readin<br>0 = No over | <b>Overrun Error</b><br>This bit indicates that an overrun error has occurred. An overrun occurs when new data is received and the UART Receive Data Register has not been read. If the RDA bit is reset to 0, then reading the UART Receive Data Register clears this bit.<br>0 = No overrun error occurred.<br>1 = An overrun error occurred. |                                           |                     |            |               |              |          |  |  |  |

| [4]<br>FE   | This bit indi<br>ing the UAF<br>0 = No fram                | Framing Error<br>This bit indicates that a framing error (no stop bit following data reception) was detected. Read-<br>ing the UART Receive Data Register clears this bit.<br>0 = No framing error occurred.<br>1 = A framing error occurred.                                                                                                   |                                           |                     |            |               |              |          |  |  |  |

| [3]<br>BRKD | This bit indi<br>are all zero<br>0 = No brea               | <ul> <li>A framing error occurred.</li> <li>Break Detect</li> <li>This bit indicates that a break occurred. If the data bits, parity/multiprocessor bit, and stop bit(s) are all zeros then this bit is set to 1. Reading the UART Receive Data Register clears this bit.</li> <li>No break occurred.</li> <li>A break occurred.</li> </ul>     |                                           |                     |            |               |              |          |  |  |  |

| [2]<br>TDRE |                                                            |                                                                                                                                                                                                                                                                                                                                                 |                                           |                     |            |               |              |          |  |  |  |

90

ILO G

## Embedded in Life An LIXYS Company

## Serial Peripheral Interface

The Serial Peripheral Interface (SPI) is a synchronous interface allowing several SPI-type devices to be interconnected. SPI-compatible devices include EEPROMs, Analog-to-Digital Converters, and ISDN devices. Features of the SPI include:

- · Full-duplex, synchronous, and character-oriented communication

- Four-wire interface

- Data transfers rates up to a maximum of one-half the system clock frequency

- Error detection

- Dedicated Baud Rate Generator

The SPI is not available in 20-pin package devices

## Architecture

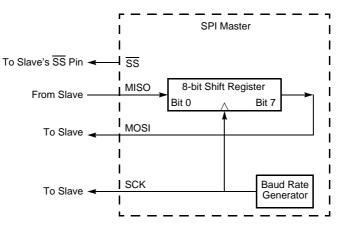

The SPI is be configured as either a Master (in single- or multiple-master systems) or a Slave, as shown in Figures 20 through 22.

Figure 20. SPI Configured as a Master in a Single Master, Single Slave System

## Embedded in Life An TXYS Company 106

#### **Transfer Format PHASE is 1**

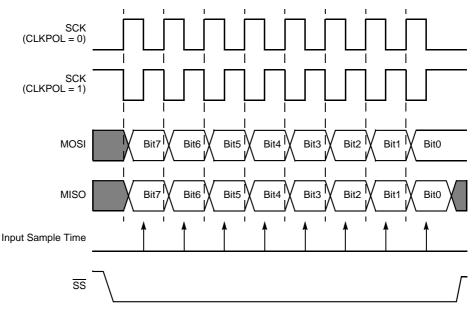

Figure 24 displays the timing diagram for an SPI transfer in which PHASE is one. Two waveforms are depicted for SCK, one for CLKPOL reset to 0 and another for CLKPOL set to 1.

Figure 24. SPI Timing When PHASE is 1

#### **Multimaster Operation**

In a multimaster SPI system, all SCK pins are tied together, all MOSI pins are tied together and all MISO pins are tied together. All SPI pins must then be configured in OPEN-DRAIN Mode to prevent bus contention. At any one time, only one SPI device is configured as the Master and all other SPI devices on the bus are configured as Slaves. The Master enables a single Slave by asserting the  $\overline{SS}$  pin on that Slave only. Then, the single Master drives data out its SCK and MOSI pins to the SCK and MOSI pins on the Slaves (including those which are not enabled). The enabled Slave drives data out its MISO pin to the MISO Master pin.

For a Master device operating in a multimaster system, if the  $\overline{SS}$  pin is configured as an input and is driven Low by another Master, the COL bit is set to 1 in the SPI Status Register. The COL bit indicates the occurrence of a multimaster collision (mode fault error condition).

## **SPI Control Register**

The SPI Control Register, shown in Table 65, configures the SPI for transmit and receive operations.

#### Table 65. SPI Control Register (SPICTL)

| Bit           | 7                                                  | 6                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5           | 4     | 3                              | 2   | 1    | 0     |  |  |  |

|---------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------|--------------------------------|-----|------|-------|--|--|--|

| Field         | IRQE                                               | STR                                                                                                                                                                                                                                                                                                                                                                                                                                 | BIRQ        | PHASE | CLKPOL                         | WOR | MMEN | SPIEN |  |  |  |

| RESET         |                                                    | 0                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |       |                                |     |      |       |  |  |  |

| R/W           |                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                     |             | R     | W                              |     |      |       |  |  |  |

| Address       |                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                     |             | F6    | 1H                             |     |      |       |  |  |  |

| Bit           | Descriptio                                         | n                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |       |                                |     |      |       |  |  |  |

| [7]<br>IRQE   | Interrupt R<br>0 = SPI inte                        | equest Ena                                                                                                                                                                                                                                                                                                                                                                                                                          | isabled. No |       | quests are sent t              |     |      |       |  |  |  |

| [6]<br>STR    | 0 = No effe<br>1 = Setting<br>forces t<br>software | <ul> <li>Start an SPI Interrupt Request</li> <li>0 = No effect.</li> <li>1 = Setting this bit to 1 also sets the IRQ bit in the SPI Status Register to 1. Setting this bit forces the SPI to send an interrupt request to the Interrupt Control. This bit can be used by software for a function similar to transmit buffer empty in a UART. Writing a 1 to the IRQ bit in the SPI Status Register clears this bit to 0.</li> </ul> |             |       |                                |     |      |       |  |  |  |

| [5]<br>BIRQ   | If the SPI is<br>0 = BRG tir                       | <b>BRG Timer Interrupt Request</b><br>If the SPI is enabled, this bit has no effect. If the SPI is disabled:<br>0 = BRG timer function is disabled.<br>1 = BRG timer function and time-out interrupt are enabled.                                                                                                                                                                                                                   |             |       |                                |     |      |       |  |  |  |

| [4]<br>PHASE  |                                                    | ase relation                                                                                                                                                                                                                                                                                                                                                                                                                        |             |       | lock. For mo<br>Polarity Conti |     |      |       |  |  |  |

| [3]<br>CLKPOL | 0 = SCK idl                                        | the PHASE bit, see the <u>SPI Clock Phase and Polarity Control</u> section on page 104.<br><b>Clock Polarity</b><br>0 = SCK idles Low (0).<br>1 = SCK idle High (1).                                                                                                                                                                                                                                                                |             |       |                                |     |      |       |  |  |  |

| [2]<br>WOR    | 0 = SPI signal 1 = AII four                        | <ul> <li>Wire-OR (Open-Drain) Mode Enabled</li> <li>0 = SPI signal pins not configured for open-drain.</li> <li>1 = All four SPI signal pins (SCK, SS, MISO, MOSI) configured for open-drain function. This setting is typically used for multimaster and/or multislave configurations.</li> </ul>                                                                                                                                  |             |       |                                |     |      |       |  |  |  |

| [1]<br>MMEN   | 0 = SPI cor                                        | ER Mode Er<br>nfigured in S<br>nfigured in N                                                                                                                                                                                                                                                                                                                                                                                        | LAVE Mode   |       |                                |     |      |       |  |  |  |

| [0]<br>SPIEN  | <b>SPI Enable</b><br>0 = SPI disa<br>1 = SPI ena   | abled.                                                                                                                                                                                                                                                                                                                                                                                                                              |             |       |                                |     |      |       |  |  |  |

ilog<sup>®</sup> Embedded in Life

An IXYS Company

## Embedded in Life An UXYS Company 132

| Bit           | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                        |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [1]<br>FLUSH  | <b>Flush Data</b><br>Setting this bit to 1 clears the $I^2C$ Data Register and sets the TDRE bit to 1. This bit allows flushing of the $I^2C$ Data Register when a Not Acknowledge interrupt is received after the data has been sent to the $I^2C$ Data Register. Reading this bit always returns 0.                                                                                          |

| [0]<br>FILTEN | <ul> <li>I<sup>2</sup>C Signal Filter Enable</li> <li>This bit enables low-pass digital filters on the SDA and SCL input signals. These filters reject any input pulse with periods less than a full system clock cycle. The filters introduce a 3-system clock cycle latency on the inputs.</li> <li>1 = Low-pass filters are enabled.</li> <li>0 = Low-pass filters are disabled.</li> </ul> |

## I<sup>2</sup>C Baud Rate High and Low Byte Registers

The I<sup>2</sup>C Baud Rate High and Low Byte registers, shown in Tables 74 and 75, combine to form a 16-bit reload value, BRG[15:0], for the I<sup>2</sup>C Baud Rate Generator. When configured as a general purpose timer, the interrupt interval is calculated using the following equation:

Interrupt Interval (s) = System Clock Period (s) ×BRG[15:0]

|  | Table 74. I <sup>2</sup> C Baud | Rate High B | yte Register ( | (I2CBRH) |

|--|---------------------------------|-------------|----------------|----------|

|--|---------------------------------|-------------|----------------|----------|

| Bit     | 7   | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|---------|-----|---|---|----|----|---|---|---|

| Field   |     |   |   | BF | RH |   |   |   |

| RESET   | FFH |   |   |    |    |   |   |   |

| R/W     |     |   |   | R/ | W  |   |   |   |

| Address |     |   |   | F5 | 3H |   |   |   |

Bit Description

#### [7:0] I<sup>2</sup>C Baud Rate High Byte

BRH Most significant byte, BRG[15:8], of the I<sup>2</sup>C Baud Rate Generator's reload value.

**Note:** If the DIAG bit in the  $I^2C$  Diagnostic Control Register is set to 1, a read of the I2CBRH Register returns the current value of the  $I^2C$  Baud Rate Counter[15:8].

134

| Bit       | Description (Continued) |                                                                      |  |  |  |  |  |

|-----------|-------------------------|----------------------------------------------------------------------|--|--|--|--|--|

| [4:0]     | Internal State          |                                                                      |  |  |  |  |  |

| TXRXSTATE | Value of the int        | ternal I <sup>2</sup> C state machine.                               |  |  |  |  |  |

|           | TXRXSTATE               | State Description                                                    |  |  |  |  |  |

|           | 0_000                   | Idle State.                                                          |  |  |  |  |  |

|           | 0_0001                  | Start State.                                                         |  |  |  |  |  |

|           | 0_0010                  | Send/Receive data bit 7.                                             |  |  |  |  |  |

|           | 0_0011                  | Send/Receive data bit 6.                                             |  |  |  |  |  |

|           | 0_0100                  | Send/Receive data bit 5.                                             |  |  |  |  |  |

|           | 0_0101                  | Send/Receive data bit 4.                                             |  |  |  |  |  |

|           | 0_0110                  | Send/Receive data bit 3.                                             |  |  |  |  |  |

|           | 0_0111                  | Send/Receive data bit 2.                                             |  |  |  |  |  |

|           | 0_1000                  | Send/Receive data bit 1.                                             |  |  |  |  |  |

|           | 0_1001                  | Send/Receive data bit 0.                                             |  |  |  |  |  |

|           | 0_1010                  | Data Acknowledge State.                                              |  |  |  |  |  |

|           | 0_1011                  | Second half of data Acknowledge State used only for not acknowledge. |  |  |  |  |  |

|           | 0_1100                  | First part of stop state.                                            |  |  |  |  |  |

|           | 0_1101                  | Second part of stop state.                                           |  |  |  |  |  |

|           | 0_1110                  | 10-bit addressing: Acknowledge State for 2nd address byte;           |  |  |  |  |  |

|           |                         | 7-bit addressing: Address Acknowledge State.                         |  |  |  |  |  |

|           | 0_1111                  | 10-bit address: Bit 0 (Least significant bit) of 2nd address byte;   |  |  |  |  |  |

|           |                         | 7-bit address: Bit 0 (Least significant bit) (R/W) of address byte.  |  |  |  |  |  |

|           | 1_0000                  | 10-bit addressing: Bit 7 (Most significant bit) of 1st address byte. |  |  |  |  |  |

|           | 1_0001                  | 10-bit addressing: Bit 6 of 1st address byte.                        |  |  |  |  |  |

|           | 1_0010                  | 10-bit addressing: Bit 5 of 1st address byte.                        |  |  |  |  |  |

|           | 1_0011                  | 10-bit addressing: Bit 4 of 1st address byte.                        |  |  |  |  |  |

|           | 1_0100                  | 10-bit addressing: Bit 3 of 1st address byte.                        |  |  |  |  |  |

|           | 1_0101                  | 10-bit addressing: Bit 2 of 1st address byte.                        |  |  |  |  |  |

|           | 1_0110                  | 10-bit addressing: Bit 1 of 1st address byte.                        |  |  |  |  |  |

|           | 1_0111                  | 10-bit addressing: Bit 0 (R/W) of 1st address byte.                  |  |  |  |  |  |

|           | 1_1000                  | 10-bit addressing: Acknowledge state for 1st address byte.           |  |  |  |  |  |

|           | 1_1001                  | 10-bit addressing: Bit 7 of 2nd address byte;                        |  |  |  |  |  |

|           |                         | 7-bit addressing: Bit 7 of address byte.                             |  |  |  |  |  |

|           | 1_1010                  | 10-bit addressing: Bit 6 of 2nd address byte;                        |  |  |  |  |  |

|           |                         | 7-bit addressing: Bit 6 of address byte.                             |  |  |  |  |  |

|           | 1_1011                  | 10-bit addressing: Bit 5 of 2nd address byte;                        |  |  |  |  |  |

|           |                         | 7-bit addressing: Bit 5 of address byte.                             |  |  |  |  |  |

|           | 1_1100                  | 10-bit addressing: Bit 4 of 2nd address byte;                        |  |  |  |  |  |

|           |                         | 7-bit addressing: Bit 4 of address byte.                             |  |  |  |  |  |

|           | 1_1101                  | 10-bit addressing: Bit 3 of 2nd address byte;                        |  |  |  |  |  |

|           |                         | 7-bit addressing: Bit 3 of address byte.                             |  |  |  |  |  |

|           | 1_1110                  | 10-bit addressing: Bit 2 of 2nd address byte;                        |  |  |  |  |  |

|           |                         | 7-bit addressing: Bit 2 of address byte.                             |  |  |  |  |  |

|           | 1_1111                  | 10-bit addressing: Bit 1 of 2nd address byte;                        |  |  |  |  |  |

|           |                         | 7-bit addressing: Bit 1 of address byte.                             |  |  |  |  |  |

145

#### Table 83. Z8 Encore! XP<sup>®</sup> F0822 Series Information Area Map

| Flash Memory<br>Address (Hex) | Function                                                                                    |

|-------------------------------|---------------------------------------------------------------------------------------------|

| FE00H–FE3FH                   | Reserved                                                                                    |

| FE40H–FE53H                   | Part Number<br>20-character ASCII alphanumeric code<br>Left-justified and filled with zeros |

| FE54H–FFFFH                   | Reserved                                                                                    |

## Operation

The Flash Controller provides the proper signals and timing for the Byte Programming, Page Erase, and Mass Erase functions within Flash memory. The Flash Controller contains a protection mechanism, using the Flash Control Register (FCTL), to prevent accidental programming or erasure. The following subsections provide details about the various operations (Lock, Unlock, Sector Protect, Byte Programming, Page Erase and Mass Erase).

### **Timing Using the Flash Frequency Registers**

Before performing a program or erase operation in Flash memory, you must first configure the Flash Frequency High and Low Byte registers. The Flash Frequency registers allow programming and erasure of Flash memory with system clock frequencies ranging from 20kHz through 20MHz (the valid range is limited to the device operating frequencies).

The Flash Frequency High and Low Byte registers combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit Flash Frequency value must contain the system clock frequency in kHz. This value is calculated using the following equation:

FFREQ[15:0] = System Clock Frequency (Hz) 1000

**Caution:** Flash programming and erasure are not supported for system clock frequencies below 20kHz, above 20MHz, or outside of the device operating frequency range. The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure proper Flash programming and erase operations.

## **Flash Control Register**

The Flash Control Register, shown in Table 84, is used to unlock the Flash Controller for programming and erase operations, or to select the Flash Sector Protect Register. The write-only Flash Control Register shares its Register File address with the read-only Flash Status Register.

| Bit     | 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|---------|---|---|---|----|----|---|---|---|

| Field   |   |   |   | FC | MD |   |   |   |

| RESET   |   |   |   | (  | )  |   |   |   |

| R/W     |   |   |   | ٧  | V  |   |   |   |

| Address |   |   |   | FF | 8H |   |   |   |

#### Table 84. Flash Control Register (FCTL)

| Bit      | Description                                                                    |  |

|----------|--------------------------------------------------------------------------------|--|

| [7:0]    | Flash Command*                                                                 |  |

| FCMD     | 73H = First unlock command.                                                    |  |

|          | 8CH = Second unlock command.                                                   |  |

|          | 95H = Page erase command.                                                      |  |

|          | 63H = Mass erase command.                                                      |  |

|          | 5EH = Flash Sector Protect Register select.                                    |  |

| Note: *A | All other commands, or any command out of sequence, lock the Flash Controller. |  |

Iloq

#### ilog Embedded in Life An TIXYS Company 161

#### **Exiting Debug Mode**

The device exits DEBUG Mode following any of the following operations:

- Clearing the DBGMODE bit in the OCD Control Register to 0

- Power-On Reset

- Voltage Brown-Out reset

- Asserting the RESET pin Low to initiate a Reset

- Driving the DBG pin Low while the device is in STOP Mode initiates a System Reset

#### **OCD Data Format**

The OCD interface uses the asynchronous data format defined for RS-232. Each character is transmitted as 1 start bit, 8 data bits (least-significant bit first), and 1 stop bit; see Figure 37.

| START | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | STOP |

|-------|----|----|----|----|----|----|----|----|------|

|-------|----|----|----|----|----|----|----|----|------|

#### Figure 37. OCD Data Format

#### **OCD** Autobaud Detector/Generator

To run over a range of baud rates (bits per second) with various system clock frequencies, the OCD contains an Autobaud Detector/Generator. After a reset, the OCD is idle until it receives data. The OCD requires that the first character sent from the host is the character 80H. The character 80H has eight continuous bits Low (one start bit plus 7 data bits). The Autobaud Detector measures this period and sets the OCD Baud Rate Generator accordingly.

The Autobaud Detector/Generator is clocked by the system clock. The minimum baud rate is the system clock frequency divided by 512. For optimal operation, the maximum recommended baud rate is the system clock frequency divided by 8. The theoretical maximum baud rate is the system clock frequency divided by 4. This theoretical maximum is possible for low-noise designs with clean signals. Table 92 lists minimum and recommended maximum baud rates for sample crystal frequencies.

#### ilog Embedded in Life An IXYS Company 176

## **Electrical Characteristics**

The data in this chapter represents all known data prior to qualification and characterization of the Z8 Encore!  $XP^{\textcircled{B}}$  F0822 Series of products, and is therefore subject to change. Additional electrical characteristics may be found in the individual chapters of this document.

## **Absolute Maximum Ratings**

These ratings are stress ratings only. Operation of the device at any condition outside those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods can affect device reliability. For improved reliability, unused inputs must be tied to one of the supply voltages ( $V_{DD}$  or  $V_{SS}$ ).

**Caution:** Stresses greater than those listed in Table 97 can cause permanent damage to the device.

|                                                          |         | -       |       |       |

|----------------------------------------------------------|---------|---------|-------|-------|

| Parameter                                                | Minimum | Maximum | Units | Notes |

| Ambient temperature under bias                           | -40     | +105    | °C    | 1     |

| Storage temperature                                      | -65     | +150    | °C    |       |

| Voltage on any pin with respect to V <sub>SS</sub>       | -0.3    | +5.5    | V     | 2     |

| Voltage on AV <sub>SS</sub> pin with respect to $V_{SS}$ | -0.3    | +0.3    | V     | 2     |

| Voltage on $V_{DD}$ pin with respect to $V_{SS}$         | -0.3    | +3.6    | V     |       |

| Voltage on $AV_{DD}$ pin with respect to $V_{DD}$        | -0.3    | +0.3    | V     |       |

| Maximum current on input and/or inactive output pin      | -5      | +5      | μA    |       |

| Maximum output current from active output pin            | -25     | +25     | mA    |       |

| 20-pin SSOP Package Maximum Ratings at -40°C to          | o 70°C  |         |       |       |

| Total power dissipation                                  |         | 430     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$         |         | 120     | mA    |       |

|                                                          |         |         |       |       |

#### Table 97. Absolute Maximum Ratings

Note: This voltage applies to all pins except the following: V<sub>DD</sub>, AV<sub>DD</sub>, V<sub>REF</sub>, pins that support analog input (Port B), and where otherwise noted.

> ilog mbedded in Life

185

## **AC Characteristics**

Table 99 provides information about the AC characteristics and timing. All AC timing information assumes a standard load of  $50 \mathrm{pF}$  on all outputs.

|                     |                                   |                 | 2.7–3.6V<br>C to 105°C |       |                                                                                                            |  |  |

|---------------------|-----------------------------------|-----------------|------------------------|-------|------------------------------------------------------------------------------------------------------------|--|--|

| Symbol              | Parameter                         | Minimum Maximum |                        | Units | Conditions                                                                                                 |  |  |

| F <sub>SYSCLK</sub> | System Clock Frequency (ROM)      | -               | 20.0                   | MHz   |                                                                                                            |  |  |

| F <sub>SYSCLK</sub> | System Clock Frequency<br>(Flash) | -               | 20.0                   | MHz   | Read-only from Flash mem-<br>ory.                                                                          |  |  |

|                     |                                   | 0.032768        | 20.0                   | MHz   | Program or erasure of Flash memory.                                                                        |  |  |

| F <sub>XTAL</sub>   | Crystal Oscillator Frequency      | 0.032768        | 20.0                   | MHz   | System clock frequencies<br>below the crystal oscillator<br>minimum require an exter-<br>nal clock driver. |  |  |

| T <sub>XIN</sub>    | System Clock Period               | 50              | -                      | ns    | $T_{CLK} = 1/F_{SYSCLK}$                                                                                   |  |  |

| T <sub>XINH</sub>   | System Clock High Time            | 20              | 30                     | ns    | T <sub>CLK</sub> = 50ns                                                                                    |  |  |

| T <sub>XINL</sub>   | System Clock Low Time             | 20              | 30                     | ns    | T <sub>CLK</sub> = 50ns                                                                                    |  |  |

#### Table 99. AC Characteristics

## eZ8 CPU Instruction Set

This chapter describes the following features of the eZ8 CPU instruction set: <u>Assembly Language Programming Introduction</u>: see page 199 <u>Assembly Language Syntax</u>: see page 200 <u>eZ8 CPU Instruction Notation</u>: see page 201 <u>eZ8 CPU Instruction Classes</u>: see page 204 <u>eZ8 CPU Instruction Summary</u>: see page 208 <u>Flags Register</u>: see page 217

## **Assembly Language Programming Introduction**

The eZ8 CPU assembly language provides a means for writing an application program without having to be concerned with actual memory addresses or machine instruction formats. A program written in assembly language is called a source program. Assembly language allows the use of symbolic addresses to identify memory locations. It also allows mnemonic codes (op codes and operands) to represent the instructions themselves. The op codes identify the instruction while the operands represent memory locations, registers, or immediate data values.

Each assembly language program consists of a series of symbolic commands called statements. Each statement can contain labels, operations, operands and comments.

Labels can be assigned to a particular instruction step in a source program. The label identifies that step in the program as an entry point for use by other instructions.

The assembly language also includes assembler directives that supplement the machine instruction. The assembler directives, or pseudo-ops, are not translated into a machine instruction. Rather, the pseudo-ops are interpreted as directives that control or assist the assembly process.

The source program is processed (assembled) by the assembler to obtain a machine language program called the object code. The object code is executed by the eZ8 CPU. An example segment of an assembly language program is detailed in the following example.

205

#### Table 119. Arithmetic Instructions (Continued)

| Mnemonic | Operands | Instruction                                   |

|----------|----------|-----------------------------------------------|

| MULT     | dst      | Multiply                                      |

| SBC      | dst, src | Subtract with Carry                           |

| SBCX     | dst, src | Subtract with Carry using Extended Addressing |

| SUB      | dst, src | Subtract                                      |

| SUBX     | dst, src | Subtract using Extended Addressing            |

#### Table 120. Bit Manipulation Instructions

| Mnemonic | Operands    | Instruction                                          |

|----------|-------------|------------------------------------------------------|

| BCLR     | bit, dst    | Bit Clear                                            |

| BIT      | p, bit, dst | Bit Set or Clear                                     |

| BSET     | bit, dst    | Bit Set                                              |

| BSWAP    | dst         | Bit Swap                                             |

| CCF      | _           | Complement Carry Flag                                |

| RCF      | _           | Reset Carry Flag                                     |

| SCF      | _           | Set Carry Flag                                       |

| ТСМ      | dst, src    | Test Complement Under Mask                           |

| TCMX     | dst, src    | Test Complement Under Mask using Extended Addressing |

| ТМ       | dst, src    | Test Under Mask                                      |

| ТМХ      | dst, src    | Test Under Mask using Extended Addressing            |

#### Table 121. Block Transfer Instructions

| Mnemonic | Operands | Instruction                                                             |

|----------|----------|-------------------------------------------------------------------------|

| LDCI     | dst, src | Load Constant to/from Program memory and Auto-<br>Increment Addresses   |

| LDEI     | dst, src | Load External Data to/from Data Memory and Auto-<br>Increment Addresses |

Embedded in Life

215

| Assembly      | Symbolic                            | Address<br>Mode |     | Op<br>Code(s) | Flags |   |   |   |   | Fetch | Instr. |        |

|---------------|-------------------------------------|-----------------|-----|---------------|-------|---|---|---|---|-------|--------|--------|

| Mnemonic      | Operation                           | dst             | src | (Hex)         | С     | Ζ | S | v | D | н     | Cycles | Cycles |

| SRL dst       | → D7 D6 D5 D4 D3 D2 D1 D0 → C       | R               |     | 1F C0         | *     | * | 0 | * | - | -     | 3      | 2      |

|               | dst                                 | IR              |     | 1F C1         | -     |   |   |   |   |       | 3      | 3      |

| SRP src       | $RP \gets src$                      |                 | IM  | 01            | -     | - | - | - | - | -     | 2      | 2      |

| STOP          | STOP Mode                           |                 |     | 6F            | -     | - | - | - | - | -     | 1      | 2      |

| SUB dst, src  | $dst \gets dst - src$               | r               | r   | 22            | *     | * | * | * | 1 | *     | 2      | 3      |

|               | -                                   | r               | Ir  | 23            | -     |   |   |   |   |       | 2      | 4      |

|               | -                                   | R               | R   | 24            | -     |   |   |   |   |       | 3      | 3      |

|               | -                                   | R               | IR  | 25            | -     |   |   |   |   |       | 3      | 4      |

|               | -                                   | R               | IM  | 26            | -     |   |   |   |   |       | 3      | 3      |

|               | -                                   | IR              | IM  | 27            | -     |   |   |   |   |       | 3      | 4      |

| SUBX dst, src | $dst \gets dst - src$               | ER              | ER  | 28            | *     | * | * | * | 1 | *     | 4      | 3      |

|               | -                                   | ER              | IM  | 29            | -     |   |   |   |   |       | 4      | 3      |

| SWAP dst      | $dst[7:4] \leftrightarrow dst[3:0]$ | R               |     | F0            | Х     | * | * | Х | - | -     | 2      | 2      |

|               | -                                   | IR              |     | F1            | -     |   |   |   |   |       | 2      | 3      |

| TCM dst, src  | (NOT dst) AND src                   | r               | r   | 62            | -     | * | * | 0 | - | -     | 2      | 3      |

|               | -                                   | r               | Ir  | 63            | -     |   |   |   |   |       | 2      | 4      |

|               | -                                   | R               | R   | 64            | -     |   |   |   |   |       | 3      | 3      |

|               | -                                   | R               | IR  | 65            | -     |   |   |   |   |       | 3      | 4      |

|               | -                                   | R               | IM  | 66            | -     |   |   |   |   |       | 3      | 3      |

|               | -                                   | IR              | IM  | 67            | -     |   |   |   |   |       | 3      | 4      |

| TCMX dst, src | (NOT dst) AND src                   | ER              | ER  | 68            | -     | * | * | 0 | - | -     | 4      | 3      |

|               | -                                   | ER              | IM  | 69            | -     |   |   |   |   |       | 4      | 3      |

#### Table 127. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

| Z8 Encore! XP | <sup>®</sup> F0822 Series |

|---------------|---------------------------|

| Produc        | t Specification           |

236

#### Hex Address: F63

#### Table 165. SPI Mode Register (SPIMODE)

| Bit     | 7    | 6     | 5    | 4 | 3           | 2    | 1   | 0 |  |

|---------|------|-------|------|---|-------------|------|-----|---|--|

| Field   | Rese | erved | DIAG | Ν | IUMBITS[2:0 | SSIO | SSV |   |  |

| RESET   |      | 0     |      |   |             |      |     |   |  |

| R/W     | F    | २     | R/W  |   |             |      |     |   |  |

| Address | F63H |       |      |   |             |      |     |   |  |

#### Hex Address: F64

#### Table 166. SPI Diagnostic State Register (SPIDST)

| Bit     | 7     | 6     | 5 | 4        | 3 | 2 | 1 | 0 |  |  |

|---------|-------|-------|---|----------|---|---|---|---|--|--|

| Field   | SCKEN | TCKEN |   | SPISTATE |   |   |   |   |  |  |

| RESET   |       | 0     |   |          |   |   |   |   |  |  |

| R/W     |       | R     |   |          |   |   |   |   |  |  |

| Address |       | F64H  |   |          |   |   |   |   |  |  |

#### Hex Address: F65

This address is reserved.

#### Hex Address: F66

#### Table 167. SPI Baud Rate High Byte Register (SPIBRH)

| Bit     | 7    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|------|---|---|---|---|---|---|---|--|

| Field   | BRH  |   |   |   |   |   |   |   |  |

| RESET   | 1    |   |   |   |   |   |   |   |  |

| R/W     | R/W  |   |   |   |   |   |   |   |  |

| Address | F66H |   |   |   |   |   |   |   |  |